# A Robust High-Q Micromachined RF Inductor for RFIC Applications

Jr-Wei Lin, C. C. Chen, and Yu-Ting Cheng, Member, IEEE

Abstract—In this paper, a robust micromachined spiral inductor with a cross-shaped sandwich membrane support is proposed and fabricated with fully CMOS compatible post-processes for radio frequency integrated circuit (RFIC) applications. Via the incorporation of a sandwich dielectric membrane (0.7  $\mu$ m SiO<sub>2</sub>/0.7  $\mu$ m Si<sub>3</sub>N<sub>4</sub>/0.7  $\mu$ m TEOS) to enhance the structure rigidity, the inductor can have better signal stability. In comparison, the new design of a ~5-nH micromachined inductor can have 45% less inductance variation than the one without the dielectric support while both devices are operated with 10 m/s<sup>2</sup> acceleration. Meanwhile, using a cross shape instead of blanket membrane can also effectively eliminate the inductance variation induced by the working temperature change (20 °C to 75 °C). The measurement results show the robust inductor can have similar electrical performance to the as-fabricated freely suspended inductor, which has five times Q (quality factor) improvement than the inductor without the substrate removal. It is our belief that the new micromachined inductors can have not only high-Q performance but also better signal stability suitable for wide-range RFIC applications.

Index Terms—Accelerative and thermal disturbance system, high-Q micromachined inductor, radio frequency integrated circuit (RFIC), robust design, signal stability.

#### I. INTRODUCTION

ECENT advancement in the design of personal wireless communication systems is aimed for wide bandwidth applications [1], [2]. In order to accomplish the goal, the carrier frequency of the system must shift to 5-10-GHz range or even higher and low-energy-loss passive components, such as inductor, capacitor, and transmission line, have to be implemented in the front-end RF circuitry for excellent signal integrity and low power consumption requirements. The on-chip micromachined spiral inductors [3]–[5] are one of the components developed for the purpose. For a conventional on-chip spiral inductor, the quality factor Q can be depicted as the following equation using a lumped physical model [6]:

$$Q = \frac{\omega L_s}{R_s} \cdot \frac{R_p}{R_p + [(\omega L_s/R_s)^2 + 1]R_s} \cdot \left[1 - \frac{R_s^2(C_s + C_p)}{L_s} - \omega^2 L_s(C_s + C_p)\right] \quad (1)$$

Manuscript received January 31, 2005; revised April 8, 2005. This work was supported by the National Science Council of Taiwan, R.O.C. under Contract 92-2220-E-009-006 Project and in part by the MediaTek Research Center 92Q029 Project. The review of this paper was arranged by Editor J. N. Burghartz.

The authors are with the Microsystems Integration Laboratory, Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: ytcheng@mail.nctu.edu.tw).

Digital Object Identifier 10.1109/TED.2005.850612

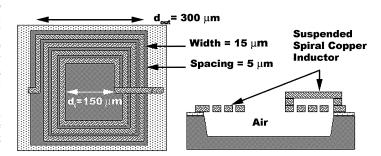

Fig. 1. Layout of the micromachined inductor for the mechanical disturbances analysis (a) top view and (b) cross-sectional view. The inductor is free suspended.

where  $L_s, R_s, C_s, C_p, R_p$ , and  $\omega$  are the inductance, series resistance, and series feed forward capacitance of the inductor, parasitic shunt capacitance, resistance, and signal frequency, respectively. Via the removal of the silicon substrate underneath the inductor, induced eddy current in the substrate  $(R_p \to \infty)$  can be effectively prohibited. The inhibition will result in the Q enhancement of the inductors at high frequency regime. Meanwhile, the parasitic shunt capacitance between the inductor and the substrate can be also reduced  $(C_p \to 0)$  in terms of the increase of mutual distance. Such a reduction makes the self resonant frequency of the inductor move toward a higher value and makes the inductor suitable for high frequency operation.

However, the micromachined inductors also raise several mechanical reliability issues. A suspended structure of the inductors could suffer from the air pressure disturbance, mechanical thermal force disturbance or force from gravity and mechanical shock [7]-[9]. Dahlmann and Yeatman [7] have investigated the mechanically induced noise power effects onto the micromachined inductor due to these disturbances and found that the noise should not be neglected and could be greater than the background thermal noise once the RF signal power levels is above approximately 1 mW. Since this type of the inductor is still with a primitive design, more studies must be done for its potential applications. Thus, in this paper, we will further investigate the electric performance of the suspended inductor under accelerative and thermal disturbances and discuss the related influence to RF circuits using the contemporary simulators, ANSYS and Ansoft-HFSS [10], [11]. Finally, based on the simulation results, an optimized micromachined inductor is proposed and fabricated with a fully CMOS compatible post-process for radio frequency integrated circuit (RFIC) applications.

| Material                                      | Cυ                   | SiO <sub>2</sub>     | Si <sub>3</sub> N <sub>4</sub> |

|-----------------------------------------------|----------------------|----------------------|--------------------------------|

| Thermal<br>Expansion<br>Coefficient<br>(1/°C) | 1.6x10 <sup>-5</sup> | 5.5x10 <sup>-7</sup> | 3.3x10 <sup>-6</sup>           |

| Young's<br>modulus<br>(GPa)                   | 125                  | 73                   | 310                            |

| Density<br>(kg/m³)                            | 8900                 | 2200                 | 3290                           |

| Poisson Ratio                                 | 0.32                 | 0.17                 | 0.27                           |

TABLE I

MECHANICAL PROPERTIES OF THE SIMULATED MATERIALS

#### II. RELIABILITY ISSUES OF THE MICROMACHINED INDUCTOR

It is necessary to realize the mechanical disturbance effects for the optimum design of the micromachined inductor. In this study, a rectangular shaped copper spiral inductor with an airbridge shown in Fig. 1 is chosen since it has already been widely used in the contemporary RFICs. It is a 3.5-turn square spiral inductor with the geometric parameters detailed in Fig. 1. The silicon substrate underneath the inductor is removed using either wet or dry chemical etching processes to form the suspended structure. Under normal operation conditions, such inductors in the RFICs for portable applications are generally susceptible to two kinds of environmental condition changes that are 10 m/s² acceleration (about 1 G shock) and 55 °C working temperature variation (R.T.,  $\sim$ 20 °C, to 75 °C), respectively.

Regarding the mechanical deformation analysis of the suspended inductor caused by the environmental changes, the ANSYS simulator is utilized to monitor the inductor behavior. The solid/thermal tetrahedron mesh is applied for the finite element analysis in the simulator with the suitable boundary conditions and the material properties listed on Table I. Once the deformation is determined by adding gravity shock or thermal stress on the device, the electrical model of the deformed spiral inductor is then built up in the HFSS simulator in terms of the nodal coordinates.

Skin effect and substrate loss are two main factors to determine the inductor performance. For the micromachined inductor, substrate loss mechanism is eliminated due to the high electrical resistivity of air. However, the skin depth of an inductor is inversely proportional to the square root of its driving frequency and material conductivity. In order to reduce the ohmic loss induced by the skin effect, the inductor thickness is generally designated larger than the skin depth. For instance, the skin depth of copper metal changes from 2.3 to 0.7  $\mu$ m while the driving frequency increases from 1 to 10 GHz. Therefore, in this paper, the inductors with two different kinds of thickness designs, 5 and 10  $\mu$ m, are chosen for the investigation in terms of their wide-band applications. In addition, for comparison purpose, the substrate parameters used in the simulator will be the same as that of the silicon substrate we utilize for the micromachined inductor fabrication. It is a 4" p-type boron doped (100) silicon substrate with the resistivity of 1–100  $\Omega$ -cm.

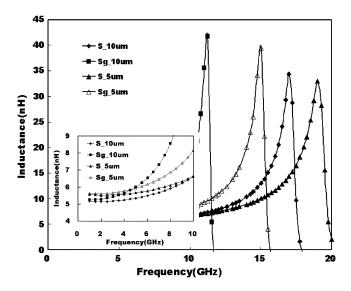

Fig. 2. Comparisons of the frequency dependence of the inductance between the original and that under the 10 m/s² acceleration. S\_5  $\mu$ m and S\_10  $\mu$ m represent the 5- and 10- $\mu$ m thick suspended spiral inductors, respectively. The figure on the lower left-hand side is an enlarge view of the frequency dependence of the inductance in the range of 1 to 10 GHz.

### A. Acceleration Influence

The average simulated nodal displacements ( $\delta$ ) in three dimensions of the inductors under 10 m/s<sup>2</sup> acceleration force along the perpendicular direction (z-direction) to the inductor plane are summarized on Table II, which are defined by the following relationship:

Avg

$$(\delta_i)|_{i=x,y,\text{or }z}$$

$$= \sqrt{\frac{1}{n} \sum_{j=1}^{n} (i_{j,\text{after\_deformation}} - i_{j,\text{original}})^2} \quad (2)$$

where n is the total number of nodes and i represents the coordinate of each node in the inductor. According to the inductance variations simulated by the HFSS for the two inductors, it is found that the deformation of the inductors will result in the resonant frequency shift toward lower value as shown in Fig. 2. In addition, for 1- to 10-GHz applications, the inductor with thinner thickness will have less acceleration influence as shown in the inset of Fig. 2.

## B. Thermal Influence

In general, the working temperature of a personal communication system could vary from 20  $^{\circ}$  C to 75  $^{\circ}$ C or even higher due to the power dissipation from the circuits or surrounding temperature variation. Such a temperature change can also result in the structural deformation of the suspended inductor via the thermal expansion of material. The average simulated nodal displacements of the suspended inductors due to the thermal deformation are also summarized in Table II. According to the HFSS analysis, the deformation will also result in the inductance change similar to the case of acceleration influence as shown in Fig. 3. In the simulation, because the thermal expansion coefficient of copper  $(17 \times 10^{-6} {\rm C}^{-1})$  is about an order magnitude

| Symbol                                 | x-direction            | y-direction            | z-direction            |

|----------------------------------------|------------------------|------------------------|------------------------|

| 5μm Inductor<br>(Sg_5μm <sup>1</sup> ) | 5.45x10 <sup>-2</sup>  | 3.96 x10 <sup>-2</sup> | 1.33 x10 <sup>-2</sup> |

| 10μm Inductor<br>(Sg_10μm²)            | 5.91x10 <sup>-2</sup>  | 4.38 x10 <sup>-2</sup> | 1.18 x10 <sup>-2</sup> |

| 5μm Inductor<br>(St_5μm <sup>1</sup> ) | 1.20 x10 <sup>-1</sup> | 8.71 x10 <sup>-2</sup> | 2.94 x10 <sup>-2</sup> |

| 10µm Inductor                          | 1.29 x10 <sup>-1</sup> | 9.53 x10 <sup>-2</sup> | 2.58 x10 <sup>-2</sup> |

TABLE II Summary of the Average Nodal Displacement ( $\mu$ m) of the Suspended Inductors With 5- and 10- $\mu$ m Thickness, Respectively

<sup>&</sup>lt;sup>2</sup>Sg\_10μm and St\_10μm represent the 10μm thick suspended spiral inductors under 1G-acceleration change and 55°C working temperature variation, respectively.

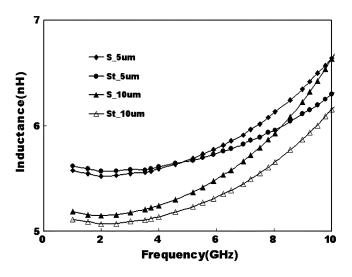

Fig. 3. Frequency dependence of the inductance between the original and that under 55 °C temperature change.

larger than that of silicon  $(2.6 \times 10^{-6})^{\circ}$  C<sup>-1</sup>, we neglect the substrate effect resulted from the thermal expansion of the silicon and only constrain the ends of the inductor for simplicity.

#### C. Influence on RF Circuitry

In RF front-end circuits, such as LNA, bandpass filter, and LC-tuned voltage controlled oscillator (VCO), lumped inductor is required for the network matching purposes. For VCO design, the oscillation frequency and phase noise described in (3) and (4) are strongly related to the inductance variation of inductors (dL/L) [12]

$$\omega_{\text{oscillator}} = \frac{1}{2\pi\sqrt{L_{\text{inductor}} \cdot C}}$$

(3)

$$\omega_{\text{oscillator}} = \frac{1}{2\pi\sqrt{L_{\text{inductor}} \cdot C}}$$

$$PN(\omega_m) = \frac{2kT \cdot R_{\text{eff}} \cdot F}{V_{\text{amp}}^2} \left(\frac{\omega_{\text{oscillator}}}{\omega_m}\right)^2$$

(4)

where  $L_{\text{inductor}}$ , C,  $R_{\text{eff}}$ ,  $V_{\text{amp}}$ ,  $\omega_m$ , and F are the inductance of inductor, the capacitance of resonator (mainly variable capacitance), the parasitic resistance of resonator, the oscillation amplitude of VCO, the offset frequency from the center frequency and the noise figure of VCO circuit, respectively. In general

$$dPN(\omega_m)\alpha \frac{dL}{L^2}. (5)$$

It indicates that the phase noise variation of a VCO circuit can have up to 2-dB difference at 8 GHz since a 10- $\mu$ m-thick micromachined inductor with 1-G shock has the inductance change from 5.17 to 8.02 nH. In addition to VCO, inductance variation could also cause the detrimental effects on LNA performance due to the network impedance mismatches.

#### III. ROBUST DESIGN AND FABRICATION

Based on the previous investigation, a robust design of the micromachined inductor has to rely on the success of the structural rigidity enhancement that can have less inductance variation while the device suffers the accelerative disturbance or thermal deformation. On the other hand, the enhancement should not sacrifice the electrical performance of the inductor. Hence, we propose a sandwich (SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>) type membrane to strengthen the inductor based on the following reasons: 1) both SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> dielectric materials have excellent mechanical properties and have been widely used in CMOS circuitry; 2) low electromagnetic energy loss in the dielectric membrane due to their low conductivity and loss tangent; and 3) although the Young's modulus of Si<sub>3</sub>N<sub>4</sub> is five times higher than that of SiO<sub>2</sub> as listed in Table I, Si<sub>3</sub>N<sub>4</sub> has much higher residual stress with the silicon substrate in comparison with SiO<sub>2</sub>. The sandwich (SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>) type membrane is proposed to resolve the stress issue. Via the double oxide layers, the nitride stress can be effectively released.

In the design, the dielectric membrane consists of 700-nm thermal oxide, 700-nm LPCVD Si<sub>3</sub>N<sub>4</sub>, and 700-nm TEOS oxide. According to the simulation results as listed in Table III, such a sandwich membrane can provide enough rigidity to the suspended inductor and make it less susceptible to the acceleration force. In comparison with the  $10-\mu$ m-thick suspended inductor, the average nodal displacements in the inductor with such a sandwich membrane support can be reduced in one order magnitude as shown in Table III. Table III shows simulation results of the average nodal displacement ( $\mu$ m) of the 10- $\mu$ m-thick inductors with different structural designs. The HFSS analysis also shows the improvement in the inductance variation from 45% down to 0.001%, as shown in Fig. 4. The inductance variation is defined as the inductance difference due

<sup>&</sup>lt;sup>1</sup>Sg\_5μm and St\_5μm represent the 5μm thick suspended spiral inductors under 1G-acceleration change and 55°C working temperature variation, respectively.

| Symbol                                   | x-direction            | y-direction            | z-direction            |

|------------------------------------------|------------------------|------------------------|------------------------|

| 10μm Inductor<br>(Sg_10μm <sup>1</sup> ) | 5.91 x10 <sup>-2</sup> | 4.38 x10 <sup>-2</sup> | 1.18 x10 <sup>-2</sup> |

| 10μm Inductor<br>(Mg_10μm²)              | 5.28 x10 <sup>-3</sup> | 4.28 x10 <sup>-3</sup> | 7.56 x10 <sup>-3</sup> |

| 10μm Inductor<br>(Mt 10μm <sup>3</sup> ) | 1.16 x10 <sup>-2</sup> | 9.41 x10 <sup>-3</sup> | 1.66 x10 <sup>-2</sup> |

TABLE III Summary of the Average Nodal Displacement ( $\mu$ m) of the 10- $\mu$ m-Thick Inductors With Different Structural Designs

<sup>&</sup>lt;sup>3</sup>Mt\_10μm represents the 10μm thick spiral inductors with a SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> membrane under 55°C working temperature change.

Fig. 4. Summary of the frequency dependence of the inductance variation for the  $10\text{-}\mu\,\text{m}\text{-}\text{thick}$  inductors with different structural designs that under either  $10\,\text{m/s}^2$  acceleration or  $55\,^{\circ}\text{C}$  working temperature change. CMt\_10  $\mu\,\text{m}$  represents the  $10\text{-}\mu\,\text{m}\text{-}\text{thick}$  spiral inductors with a cross-shaped SiO<sub>2</sub>/Si $_3$ N<sub>4</sub>/SiO<sub>2</sub> membrane under  $55\,^{\circ}\text{C}$  working temperature change.

to the environmental change divided by the original inductance of the inductor.

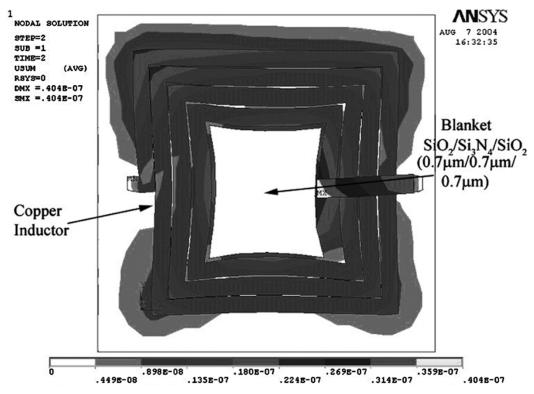

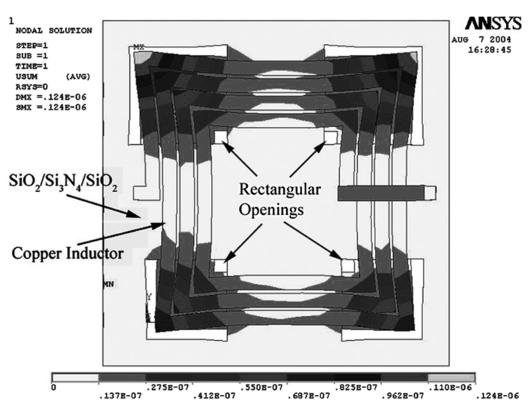

Although adding a dielectric supporting membrane to the suspended inductor could be a good method, it might lead to another reliability issue. The structural enhancement via the incorporation of a dielectric membrane could create another reliability problem due to the stress originated from material's coefficient of thermal expansion (CTE) mismatch. According to the Table III, 55 °C temperature change can deform the inductor with the blanket sandwich membrane support. Fig. 5 shows the simulated contour map of the 10- $\mu$ m-thick inductor with the blanket dielectric membrane support. It shows that, with 55 °C temperature change, the thermal deformation mainly distributes in the central coil region. Such a deformation results in more than 5% inductance variance of the 10- $\mu$ m-thick inductor as shown in Fig. 4 while it is operated in the frequency range of 1 to 8 GHz.

In order to reduce the thermal influence, we propose a crossshaped membrane structure to replace the blanket support. For an inductor, its total inductance comes from the contribution of the self-inductance of the metal coils and the mutual inductance between the coils. The inductance can be calculated as the following (6):

$$L_{\text{total}} = \sum_{i=1}^{n} L_i + \sum_{i=1}^{n} \sum_{j=1, j \neq i}^{n} M_{i,j}$$

(6)

where the first part in this equation is the self-inductance from the coil segments of the inductor and the second part is mainly originated from the negative and positive mutual inductances between the segments. From Neumann theory [13]

$$M_{12} = \frac{\mu}{4\pi} \oint \int \frac{dl_1 \cdot dl_2}{r_{12}} \tag{7}$$

where  $dl_1, dl_2$ , and  $r_{12}$  denote the vector current elements and the distance between the elements, respectively. When the current elements are parallel to each other with the current flow in the same direction, the magnetic fields of the segments are positively coupled; the maximum mutual inductance occurs between them. On the contrary, while the current flows in opposite directions, the magnetic fields are counteracted and result in a negative mutual inductance. In addition, when the current elements are orthogonal to each other, no mutual inductance contributes to the total inductance of the inductor. Thus, for an on-chip spiral inductor, since stronger EM field coupling exists in the lateral region than the corner one and slight deformation in the lateral region could result in the large inductance change, using a cross-shaped membrane support might be a good way not only to provide enough structure rigidity to the suspended inductor but also to have less thermal deformation in the lateral region.

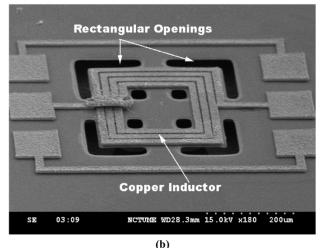

Fig. 6 shows the contour map of the 5  $\mu$ m thick inductor with the cross-shaped dielectric membrane support. The distribution of the thermal deformation has shifted to the corner regions of the inductor in terms of the less physical constraints in the four corners of the inductor as predicted. For 55 °C temperature change, the HFSS simulation shows that the cross-shaped membrane supported 5- $\mu$ m-thick inductor can have 17% inductance variation less than the blanket one while they both operate at 8 GHz. Similar phenomenon also occurs in the 10  $\mu$ m thick inductor as shown in Fig. 4. The inductor designed with the cross-shaped sandwich dielectric membrane support is less susceptible to the thermal influence in comparison with that using the blanket membrane support.

<sup>&</sup>lt;sup>1</sup>Sg\_10μm represents the 10μm thick suspended spiral inductors under 1G-acceleration.

$<sup>^2</sup>Mg\_10\mu m$  represents the  $10\mu m$  thick spiral inductors with a  $SiO_2/Si_3N_4/SiO_2$  membrane support under 1G-acceleration.

Fig. 5. Simulated contour map of the 10-\mu m-thick inductor with the blanket dielectric membrane support under 55 °C temperature change.

Fig. 6. Simulated contour map of the 10-μm-thick inductor with the cross-shaped dielectric membrane support under 55 °C temperature change.

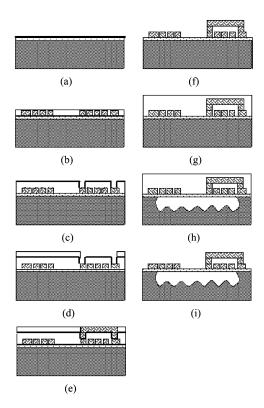

Fig. 7 illustrates the fabrication process of the robust high performance and reliable micromachined inductor. It begins with wet oxidation at 980 °C for 700 nm of thermal oxide, followed by 700-nm LPCVD nitride and 700-nm TEOS oxide depositions on the p-type silicon substrate as shown in Fig. 7(a). Fig. 7(b)

shows that the first thin Ti/Cu (10 nm/120 nm) adhesion/seed layer is sputtered onto the silicon substrate, then patterned with a 6  $\mu$ m thick AZ 4620 photo-resist to define the region for the fabrication of the coil part of the spiral inductor using copper electroplating. After the first layer of copper is plated, a 10- $\mu$ m layer

Fig. 7. Scheme of the inductor fabrication processes (a)  $SiO_2/Si_3N_4/SiO_2$  (0.7  $\mu$ m/0.7  $\mu$ m/0.7  $\mu$ m) sandwich membrane and Ti/Cu(100 Å/1200 Å) seed/adhesion layer deposition. (b) First copper plating for the coil part of the inductor. (c) Air-bridge seed layer deposition. (d) Air-bridge patterning. (e) Air-bridge and via plating. (f) Seed layer removal. (g) dielectric patterning. (h) Substrate removal using the  $XeF_2$  gas. (i) PR mask removal.

of AZ4620 is spin-coated, patterned, and sputtered with another 100 nm copper seed layer on the same substrate as shown in Fig. 7(c) for the air-bridge copper via filling. Figs. 7(d) and (e) illustrate that, after the via filling, another 10- $\mu$ m AZ4620 is spun onto the plated structure, patterned to define the air-bridge beam, and plated with 5  $\mu$ m copper to form the air bridge. Finally, the fabrication of the spiral inductor is done after lifting off the copper seed layer and chemically etching away the first seed/adhesion layer using CR-7T, as shown in Fig. 7(f).

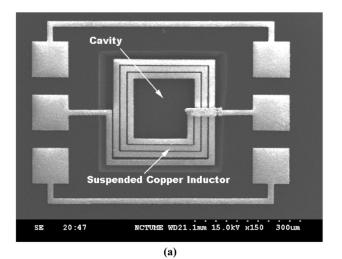

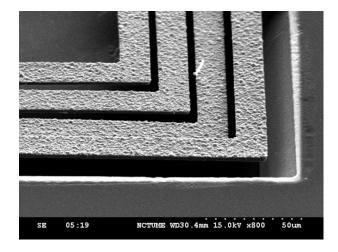

Once the inductor is fabricated, the membrane is reactive ion etched (RIE) away to define the corner regions as illustrated in Fig. 7(g). Since the XeF<sub>2</sub> gas has excellent etching selectivity to silicon, the dielectric membrane or copper can be utilized as the mask and the opened area around the four corners or the adjacent region of the suspended inductor provide the path for the etchant to isotropically remove the silicon substrate as shown in Fig. 7(h). Finally, the photo-resist mask is stripped by acetone as shown in Fig. 7(i). Fig. 8 shows the as-fabricated on-chip spiral inductors, which are the conventional suspended inductor and the proposed robust inductor, respectively. It is noted that the residual stress has been effectively compensated using the sandwich structure as shown in Fig. 8(b). No buckling phenomenon is found in the inductor.

# IV. EXPERIMENTAL RESULTS AND DISCUSSIONS

In the experiment, the two-port S-parameters of the inductors are measured using the HP8510C Network Analyzer and

Fig. 8. SEM micrographs of the as-fabricated on-chip spiral inductor. (a) Suspended inductor. (b) Robust inductor.

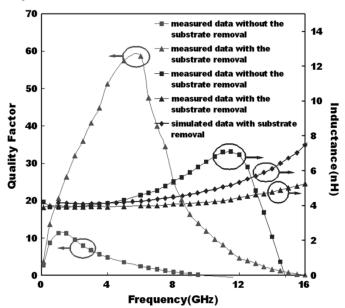

Fig. 9. Measurement and simulation results of the as-fabricated 5- $\mu$ m-thick suspended inductor.

the cascade Micro-tech coplanar ground-signal-ground probe in the frequency range of 0.1 to 20 GHz. The parasitic parallel capacitance and series contact resistance between the substrate

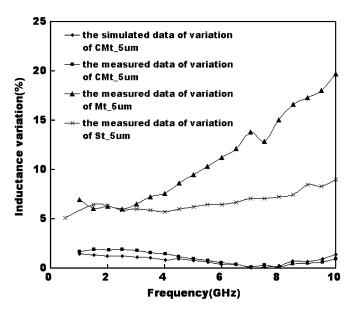

Fig. 10. Measurement and simulation results of the  $5-\mu$ m-thick inductors with three different structural designs for 55 °C variation.

and the contact pads of the inductor are de-embedded via the measurement using well-designed dummy patterns [14]. The de-embedded S-parameters are then transformed into Y-parameters from which the inductance (L) and Q factor of the inductor can be calculated based on the following equations [15], respectively:

$$L = \text{Im}(1/Y_{11})/2\pi f \tag{8}$$

$$Q = \text{Im}(1/Y_{11})/\text{Re}(1/Y_{11})$$

(9)

where f is the signal frequency. The overall measurements are accomplished at the R.T. and 75 °C, respectively. Fig. 9 shows the measurement results of the as-fabricated 5- $\mu$ m-thick suspended inductors. With the silicon substrate removal, the self resonant frequency and the Q factor of the micromachined inductor move toward higher values simultaneously in comparison with the conventional on-chip one. The five times Q factor improvement reveals its potential applications as we expected. In addition, the HFSS simulation results of the micromachined inductor as shown in the figure are closely fitted with the measurement data up to 8 GHz.

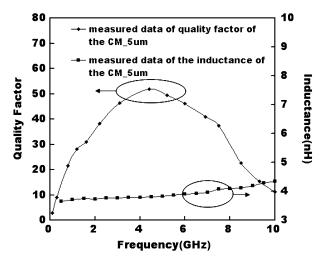

In order to further verify the influence of temperature variation on the inductor performance, the inductance of the 5-\$\mu\$m-thick inductors with three different designs, which are suspended, blanket membranes, and cross-shaped membrane support, respectively, are measured with 55 °C temperature change. Fig. 10 shows the inductance change can be effectively reduced to less than 3% inductance variation as the prediction when the inductor is deigned with the cross-shaped membrane support. Meanwhile, the results also confirm that the inductor with a blanket membrane support is the most susceptible to thermal effects in these structures though it has the best structural rigidity. Fig. 11 shows the inductance performance of the as-fabricated 5-\$\mu\$m-thick inductor with the cross-shaped membrane support. The high-\$Q\$ (>50) performance can also be realized in the design.

A variety of micromachined inductors have been proposed. However, every micromachined inductor design has its unique

Fig. 11. Measurement results of the as-fabricated 5- $\mu$ m-thick inductor with the cross-shaped membrane support.

Fig. 12. SEM micrograph of the enlarged view on the corner region of the inductor with the substrate removal.

structure and specific applications. For instance, although the design discussed here is only one of them, it can provide excellent performance for the high frequency RFIC applications such as 3-8 GHz ultra wideband (UWB) systems for data-communication because there is no dielectric in the structure which results in the resonance frequency shift of the inductor up to 17–20 GHz. In Lakdawala et al.'s design [3], there are dielectric layers within the copper layers like a composite structure, parasitic capacitance is relatively high, and the self resonant frequency becomes lower (i.e., <11 GHz). Since the inductors used for RFICs should operate in the region well below its resonant frequency for stability, the design is not suitable for such applications. The end of each coil of the inductor is supported by a suspended beam (i.e., the return line) for better structural rigidity, but it is still experienced with severe thermal stress problem due to its composite structure. In addition, Abid et al. has proposed another design of micromachined inductor [5]. Although there is a dielectric support underneath the inductor, the geometry of the dielectric layer has not been optimized. The openings are utilized for rapid removal of the silicon substrate so the design is still with thermal stress problem. Since gravity, shock, and thermal influence would result in different deformation in each

case, more investigations are required and the paper can provide a method for the analysis and optimum design of the other types of micromachined inductors.

In the analysis, the simulated inductance values are slightly larger than the actual values in both cases as shown in Fig. 9. The deviation could be resulted from the material characteristic, the process variation, and the gravity effect on the device. For instance, the spacing of the inductor coil is defined by the photo-resist mold, which is affected by the surface morphology of device substrate. Since no CMP technique is utilized for the fabrication of the inductors, the process exactness could not be achieved in this case. Meanwhile, Fig. 12 shows the SEM micrograph of the enlarged view on the corner region of the free suspended inductor. Gravity force deforms the inductor to form a nonplanar structure that could also result in the inductance change. Finally, the detail of thermal-mechanical behavior of the material is very important to the accuracy of the device modeling and simulation. The related investigation on the nonideal effects and material characterization are required for the further improvement in the simulation accuracy.

#### V. CONCLUSION

A new kind of high-performance micromachined inductor supported with a cross-shaped sandwich membrane has been successfully proposed and fabricated. Two major simulators, ANSYS and Ansoft HFSS, are utilized for the robust design and stability investigation of the micromachined inductors. Both simulation and experimental results indicate mechanical disturbances like acceleration and thermal stress can easily cause conventional micromachined inductors with unstable performance that can be resolved using the new robust design.

#### REFERENCES

- [1] R. M. Schmalenberger and M. G. Edrich, "Channel modeling for wideband data communication in a maritime mobile environment," in *Proc. IEEE/AFCEA EUROCOMM 2000*, May 2000, pp. 150–154. Information Systems for Enhanced Public Safety and Security..

- [2] J. C. Adams, W. Gregorwich, L. Capots, and D. Liccardo, "Ultra wideband for navigation and communications," in *Proc. IEEE Aerospace Conf.*, vol. 2, Mar. 2001, pp. 785–792.

- [3] H. Lakdawala, X. Zhu, X. H. Luo, S. Santhanam, L. R. Carley, and G. K. Fedder, "Micromachined high-Q inductors in a 0.18-μm copper interconnect low-k dielectric CMOS process," *IEEE J. Solid-State Circuits*, vol. 37, no. 3, pp. 394–403, Mar. 2002.

- [4] J. Hongrui, Y. Wang, J.-L. A. Yeh, and N. C. Tien, "On-chip spiral inductors suspended over deep copper-lined cavities," *IEEE Microwave Theory Tech.*, vol. 48, no. 12, pp. 2415–2423, Dec. 2000.

- [5] A. A. Abid and J. Y.-C. Chang, "Monolithic Passive Component," U.S. Patent 5 539 241, 1996.

- [6] C. Y. Yue and S. S. Wong, "On-chip spiral inductors with patterned ground shields for Si-based RFICs," *IEEE J. Solid-State Circuits*, vol. 33, no. 5, pp. 743–753, May 1998.

- [7] G. W. Dahimann and E. M. Yeatman, "Microwave characteristics of meander inductors fabricated by 3-D self-assembly," in *Proc. 8th IEEE Int. Symp. High Performance Electron Devices for Microwave and Optoelectronic Applications*, Nov. 2000, pp. 128–133.

- [8] G. M. Rebeiz, "Phase-noise analysis of MEMS-based circuits and phase shifters," *IEEE Trans. Microwave Theory Tech.*, vol. 50, no. 5, pp. 1316–1323, May 2002.

- [9] D. J. Young, "Micromachined RF voltage-controlled oscillator with phase noise characterization," in *Proc. 9th Int. Conf. Electronics*, *Circuits, and Systems*, vol. 1, Sep. 2002, pp. 295–298.

- [10] ANSYS [Online]. Available: http://www.ansys.com

- [11] Ansoft HFSS, http://www.ansoft.com/products/hf/hfss. 9.0 version.

- [12] J. Craninckx and M. S. J. Steyaert, "A fully integrated CMOS DCS-1800 frequency synthesizer," *IEEE J. Solid-State Circuits*, vol. 33, no. 12, pp. 2054–2065, Dec. 1998.

- [13] S. Jenei, B. K. J. C. Nauwelaers, and S. Decoutere, "Physics-based closed-form inductance expression for compact modeling of integrated spiral inductors," *IEEE J. Solid-State Circuits*, vol. 37, no. 1, pp. 77–80, Jan. 2002.

- [14] T. E. Kolding, "A four step method for de-embedding gigahertz on-wafer CMOS measurements," *IEEE Trans. Electron Devices*, vol. 47, no. 4, pp. 734–740, Apr. 2000.

- [15] I. J. Bahl, "High-performance inductors," *IEEE Trans. Microwave Theory Tech.*, vol. 49, no. 4, pp. 654–664, Apr. 2001.

Jr-Wei Lin was born in Taiwan, R.O.C. He received the B.S. degree in physics from National Central University in 2001 and the M.S. degree in electrical engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 2004. His thesis was entitled "An Optimum Design of The Micromachined RF Inductor".

Currently, he is an Engineer with the Central Research Division at United Microelectronics Corporation (UMC). His current work focuses on the development of deep submicron device modeling.

C. C. Chen was born in Taiwan, R.O.C. He received the B.S. degree in physics from National Central University in 2002. He is currently pursuing the Ph.D. degree in the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan, where he is working on solid-state theory for RF device modeling.

Yu-Ting Cheng (M'01) was born in Taiwan, R.O.C. He received the B.S. and M.S. degrees in materials science and engineering from National Tsing Hua University, Hsinchu, Taiwan, in 1991 and 1993, respectively, the M.S. degree from Carnegie Mellon University, Pittsburgh, PA, and the Ph.D. degree in electrical engineering from the University of Michigan, Ann Arbor, in 2000. His dissertation was on the development of novel vacuum packaging technique for MEMS applications.

He spent two years in the Taiwan army service and later joined IBM Watson Research Center, Yorktown Heights, NY, as a Research Staff Member, involved in several system-on-package (SOP) projects. Since 2002, he has been an Assistant Professor in the Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan. His research interests include the fundamental study of materials for microsystems integration and MEMS applications, SOP, and microsensors and microactuators.

Dr. Cheng is a member of the IOP and Phi Tau Phi.