# High-Performance Nonvolatile HfO<sub>2</sub> Nanocrystal Memory

Yu-Hsien Lin, Student Member, IEEE, Chao-Hsin Chien, Ching-Tzung Lin, Chun-Yen Chang, Fellow, IEEE, and Tan-Fu Lei

Abstract—In this letter, we demonstrate high-performance non-volatile HfO2 nanocrystal memory utilizing spinodal phase separation of Hf-silicate thin film by 900 °C rapid thermal annealing. With this technique, a remarkably high nanocrystal density of as high as  $0.9\sim1.9\times10^{12}~\rm cm^{-2}$  with an average size <10 nm can be easily achieved. Because HfO2 nanocrystals are well embedded inside an SiO2-rich matrix and due to their sufficiently deep energy level, we, for the first time, have demonstrated superior characteristics of the nanocrystal memories in terms of a considerably large memory window, high-speed program/erase (P/E) (1  $\mu s/0.1~\rm ms$ ), long retention time greater than  $10^8~\rm s$  for  $10\%~\rm charge$  loss, and excellent endurance after  $10^6~\rm P/E$  cycles.

Index Terms—Hafnium oxide, nanocrystals, nonvolatile memories, phase separation.

## I. INTRODUCTION

CCORDING to the International Technology Roadmap for Semiconductors, there are critical limitations for aggressively scaling the conventional nonvolatile floating-gate memories below sub-70-nm node [1]. Therefore, the poly-silicon-oxide-nitride-oxide-silicon (SONOS)-type structure memories including nitride memories and nanocrystal memories have recently attracted much attention for the application in the next-generation nonvolatile memories [2]-[11] because of their great potential for achieving high program/erase (P/E) speed, low programming voltage and low power performance. However, many concerning issues are still presented for both types of memories. For conventional SONOS, erase saturation and vertical stored charge migration [8], [9] are the major drawbacks; while for nanocrystal memories good enough charge keeping capability of the discrete storage nodes and the formation of nanocrystals with constant size, high density and uniform distribution are the extremely challenging issues [10]. In recent years, many papers have ever shown Al<sub>2</sub>O<sub>3</sub> trapping layer as the potential candidate for replacing Si<sub>3</sub>N<sub>4</sub> [11] and also demonstrated different kinds of nanocrystals to provide charge storage for the nonvolatile memories, such as Si nanocrystals, germanium (Ge) nanocrystals, and metal nanocrystals [2]-[7].

Manuscript received November 12, 2004. This project was sponsored by the National Science Council, Taiwan, R.O.C. under Contract 93A0500001. The review of this letter was arranged by Editor C.-P. Chang.

Y.-H. Lin, C.-T. Lin, C.-Y. Chang, and T.-F. Lei are with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C.

C.-H. Chien is with the National Nano Device Laboratory, Hsinchu 300, Taiwan, R.O.C. (e-mail: chchien@ndl.gov.tw).

Digital Object Identifier 10.1109/LED.2004.842727

In this letter, we explore a novel technique, which is fully compatible to current CMOS technologies, to form the very local HfO<sub>2</sub> nanocrystals for the application of the nonvolatile flash memories utilizing spinodal decomposition of hafnium silicate after sufficiently high temperature rapid thermal annealing (RTA) treatment [12]. With this technique, we can well isolate the HfO<sub>2</sub> nanocrystals from each other with SiO<sub>2</sub>-rich matrix. Combining with the effect of large band gap offset between HfO<sub>2</sub> and SiO<sub>2</sub>, we have successfully achieved the nanocrystal memories with superior characteristics in terms of considerably large memory window, high speed P/E, long retention time, and excellent endurance.

### II. DEVICES FABRICATION

The fabrication process of the HfO<sub>2</sub> nanocrystal memory devices was demonstrated with LOCOS isolation process on a p-type 5–10  $\Omega$  · cm (100) 150-mm silicon substrates. First, a 2-nm tunnel oxide was thermally grown at 1000 °C in vertical furnace system. Next, a 12-nm amorphous HfSiOx silicate layer was deposited by co-sputtering method with pure Silicon (99.999% pure) and pure Hafnium (99.9% pure) targets in the oxygen gas ambient. The co-sputtering process was performed at  $7.6 \times 10^{-3}$  torr with precursors of  $O_2$  (3 sccm), Ar (24 sccm) and the both dc sputter power was set to 150 W at the room temperature. After that, the samples went through RTA treatment in O<sub>2</sub> ambient at 900 °C for 1 min in order to convert  $HfSiO_x$  silicate film into the separated  $HfO_2$  and  $SiO_2$  phases which compositions were identified both by energy dispersive spectrometer (EDS) and X-ray photoelectron spectroscopy (not shown). A blocking oxide of about 8 nm was then deposited by high-density plasma chemical vapor deposition followed by 900 °C 1 min N<sub>2</sub> densification process. Then, poly-Si deposition, gate patterning, source/drain (S/D) implant, and the rest of the subsequent standard CMOS procedure were complete for fabricating the HfO<sub>2</sub> nanocrystal memory devices.

## III. CHARACTERIZATION RESULTS AND DISCUSSION

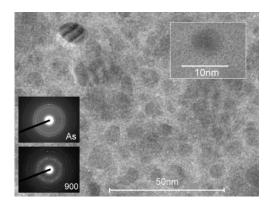

Fig. 1 shows the plane-view high-resolution transmission microscopy (HRTEM) images of the HfO $_2$  nanocrystals. The average nanocrystal size is around 5–8 nm and the density can be as high as  $0.9 \sim 1.9 \times 10^{12}$  cm $^{-2}$ . Clearly, they are well separated with an average distance >5 nm in two-dimensional with SiO $_2$ . This leads to the well isolation of nanocrystals from each other and effectively prevents formation of good conductive paths between the adjacent nodes. The mechanism responsible for the formation of HfO $_2$  nanocrystals is well

Fig. 1. Plane-view HRTEM image of the HfO<sub>2</sub> nanocrystals. The size is about 5–8 nm and the dot density is  $0.9-1.9\times10^{12}$  cm<sup>-2</sup>. The inset show the diffraction patterns of as-deposited and 900 °C RTA-treated samples.

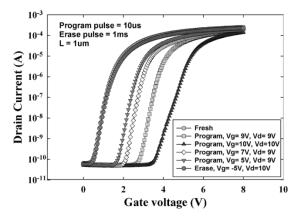

Fig. 2.  $I_{\rm ds}-V_{\rm gs}$  curves of programmed memories with different programming conditions. The programming time is  $10~\mu \rm s$ . A memory window of larger than  $3~\rm V$  can be achieved with  $V_g=V_d=10~\rm V$  programming operation.

known to be the transformation of hafnium silicate into a phase separated microstructure [13]. Basically, compositions within metastable extensions of the spinodal are unstable and will spontaneously unmix in the amorphous phase upon cooling from RTA processing. The atomic concentrations in the as-deposition HfSiOx layer examined by EDS analysis are 12.61%, 18.99%, and 68.40% for Hf, Si, and O, respectively. With this element composition, we can easily and reproducibly produce high density HfO<sub>2</sub> nanocrystal dots embodied by an SiO<sub>2</sub>-rich matrix after RTA in O<sub>2</sub> ambient. In addition, from the diffraction patterns, it is clearly observed that the as-deposited film is amorphous and the sample that is subject to RTA is polycrystalline. The crystalline structure of HfO<sub>2</sub> nanocrystal is monoclinic.

Fig. 2 shows the  $I_{\rm ds}$ – $V_{\rm gs}$  curves of the HfO<sub>2</sub> nanocrystal memory devices with programming time of 10  $\mu$ s for different programming conditions. Channel hot-electron injections and band-to-band hot-hole injections were employed for programming and erasing, respectively. A relatively large memory window of about 3 V can be achieved at the  $V_g = V_d = 10$  V program operation. Program characteristics as a function of pulsewidth for different operation conditions are shown in Fig. 3(a). Both source and substrate terminals were biased at 0 V. The " $V_t$  shift" is defined as the threshold voltage change of a device between the written and the erased states. With

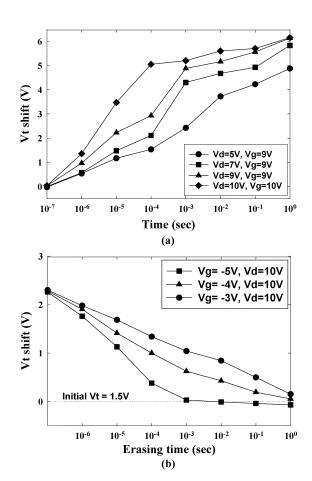

Fig. 3. (a) Program characteristics of HfO $_2$  nanocrystal memory devices with different programming conditions. A memory window of about 5 V can be achieved with  $V_g=V_d=10$  V, and time  $=100~\mu s$  programming operation. (b). Erase characteristics of HfO $_2$  nanocrystal memory devices with different erasing voltages.

$V_d = V_g = 9$  V, relatively high speed (10  $\mu$ s) programming performance can be achieved with a memory window of about 2.2 V. Meanwhile, Fig. 3(b) displays the erase characteristics as a function of various operation voltages. Again, excellent erase speed of around 0.1 ms can be obtained. More important, there is only a very small amount of overerase observed. The reason is owing to the fact that the vertical electric field decreases with decreasing amount of trapped electrons in the nanocrystals during erasing and the hole injection into the nanocrystals will reduce significantly due to the higher hole tunneling barrier presented in HfO<sub>2</sub>/SiO<sub>2</sub> stack after all programmed charges are removed [14].

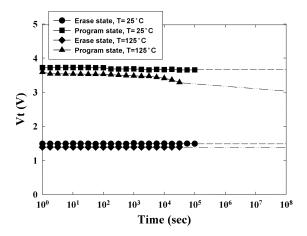

The retention characteristics of the HfO<sub>2</sub> nanocrystal memory devices at both room temperature ( $T=25\,^{\circ}\mathrm{C}$ ) and higher temperature ( $T=125\,^{\circ}\mathrm{C}$ ) are illustrated in Fig. 4. The retention time can be up to  $10^{8}$  seconds for 10% charge loss at room temperature. Only slight charge loss has been seen even at the temperature up to  $125\,^{\circ}\mathrm{C}$ . We ascribe these results to the combining effects of the tight embrace of HfO<sub>2</sub> nanocrystals by SiO<sub>2</sub>-rich matrix and the sufficiently deep trap energy level [14]. The extracted activation energy lies in the range of around  $2.1\sim3.3\,\mathrm{eV}$  for our memories, which is obviously higher than that reported in the previous work for the conventional SONOS memories [15]. Therefore, albeit with a tunnel oxide down to

Fig. 4. Retention characteristics of HfO $_2$  nanocrystal memory devices at  $T=25~^{\circ}\mathrm{C}$  and 125  $^{\circ}\mathrm{C}$ . Very low charge loss is seen even after  $10^5~\mathrm{s}$ .

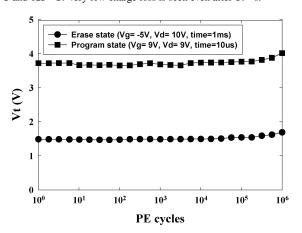

Fig. 5. Endurance characteristics of  $HfO_2$  nanocrystal memory devices. Negligible degradation is found even after  $10^6$  P/E cycles.

2 nm in thickness, no significant lateral and vertical charge migrations occurred. As a result, superior retention characteristic of the charge storage can be procured. The endurance characteristics after  $10^6$  P/E cycles are also shown in Fig. 5. The programming and erasing conditions are  $V_g = V_d = 9$  V for  $10~\mu s$  and  $V_g = -5$  V,  $V_d = 10$  V for 1 ms, respectively. No detectable memory window narrowing has been displayed. Moreover, the individual threshold voltage shifts in program and erase states only become visible after  $10^5$  cycles. This trend indicates that the amount of operation-induced trapped electrons is very tiny. Certainly, this is intimately related to the use of ultra-thin tunnel oxide and very minute amount of residual charges in the HfO2 nanocrystals after cycling.

# IV. CONCLUSION

In this letter, we have proposed a novel simple, reproducible, reliable technique for preparation of high density HfO<sub>2</sub>

nanocrystals using spinodal decomposition of hafnium silicate and achieved nanocrystal memories with superior characteristics in terms of large memory windows, high speed P/E, long retention time, and excellent endurance.

### REFERENCES

- [1] Test and test equipment, in The International Technology Roadmap for Semiconductors, San Jose, CA, pp. 27–28, 2001.

- [2] R. Ohba, N. Sugiyama, K. Uchida, J. Koga, and A. Toriumi, "Non-volatile Si quantum memory with self-aligned doubly-stacked dots," *IEEE Trans. Electron Devices*, vol. 49, no. 8, pp. 1392–1398, Aug. 2002.

- [3] R. Muralidhar, R. F. Steimle, M. Sadd, R. Rao, C. T. Swift, E. J. Prinz, J. Yater, L. Grieve, K. Harber, B. Hradsky, S. Straub, B. Acred, W. Paulson, W. Chen, L. Parker, S. G. H. Anderson, M. Rossow, T. Merchant, M. Paransky, T. Huynh, D. Hadad, K.-M. Chang, and B. E. White, Jr., "A 6 V embedded 90 nm silicon nanocrystal nonvolatile memory," in *IEDM Tech. Dig.*, 2003, pp. 601–605.

- [4] T. Baron, B. Pellissier, L. Perniola, F. Mazen, J. M. Hartmann, and G. Polland, "Chemical vapor deposition of Ge nanocrystals on SiO2," *Appl. Phys. Lett.*, vol. 83, pp. 1444–1446, 2003.

- [5] Q. Wan, C. L. Lin, W. L. Liu, and T. H. Wang, "Structural and electrical characteristics of Ge nanoclusters embedded in Al<sub>2</sub>O<sub>3</sub> gate dielectric," *Appl. Phys. Lett.*, vol. 82, pp. 4708–4710, 2003.

- [6] C. Lee, A. Gorur-Seetharam, and E. C. Kan, "Operational and reliability comparison of discrete-storage nonvolatile memories: Advantages of single- and double-layer metal nanocrystals," in *IEDM Tech. Dig.*, 2003, pp. 557–561.

- [7] M. Takata, S. Kondoh, T. Sakaguchi, H. Choi, J.-C. Shim, H. Kurino, and M. Koyanagi, "New nonvolatile memory with extremely high density metal nano-dots," in *IEDM Tech. Dig.*, 2003, pp. 553–557.

- [8] P. Xuan, M. She, B. Harteneck, A. Liddle, J. Bokor, and T.-J. King, "FinFET SONOS flash memory for embedded applications," in *IEDM Tech. Dig.*, 2003, pp. 609–613.

- [9] T. Sugizaki, M. Kobayashi, M. Ishidao, H. Minakata, M. Yamaguchi, Y. Tamura, Y. Sugiyama, T. Nakanishi, and H. Tanaka, "Novel multi-bit SONOS type flash memory using a high-κ charge trapping layer," in *Proc. VLSI Symp. Tech. Dig.*, 2003, pp. 27–28.

- [10] M. L. Ostraat, J. W. De Blauwe, M. L. Green, L. D. Bell, M. L. Brongersma, J. Casperson, R. C. Flagan, and H. A. Atwater, "Synthesis and characterization of aerosol silicon nanocrystal nonvolatile floating-gate memory devices," *Appl. Phys. Lett.*, vol. 79, pp. 433–435, 2001.

- [11] T. Sugizaki, M. Kobayashi, H. Minakata, M. Yamaguchi, Y. Tamura, Y. Sugiyama, H. Tanaka, T. Nakanishi, and Y. Nara, "New 2-bit/Tr MONOS type flash memory using Al<sub>2</sub>O<sub>3</sub> as charge trapping layer," in Proc. IEEE Non-Volatile Semiconductor Memory Workshop, Feb. 2003, pp. 60–61.

- [12] S. Stemmer, Z. Chen, C. G. Levi, P. S. Lysaght, B. Foran, J. A. Gisby, and J. R. Taylor, "Application of metastable phase diagrams to silicate thin films for alternative gate dielectrics," *Jpn. J. Appl. Phys.*, vol. 42, pp. 3593–3597, 2003.

- [13] S. Saito, Y. Matsui, K. Torii, Y. Shimamoto, M. Hiratani, and S. Kimura, "Inversion electron mobility affected by phase separation in high-permittivity gate dielectrics," *Jpn. J. Appl. Phys.*, vol. 42, pp. L1425–L1428, 2003

- [14] W. J. Zhu, T.-P. Ma, T. Tamagawa, J. Kim, and Y. Di, "Current transport in metal/hafnium oxide-silicon structure," *IEEE Electron Device Lett.*, vol. 23, no. 2, pp. 97–99, Feb. 2002.

- [15] B. De Salvo, G. Ghibaudo, G. Pananakakis, G. Reimbold, F. Mondond, B. Guillaumot, and P. Candelier, "Experimental and theoretical investigation of nonvolatile memory data-retention," *IEEE Trans. Electron Devices*, vol. 46, no. 7, pp. 1518–1524, Jul. 1999.