# Formation of Cobalt Silicided Shallow Junction Using Implant Into/Through Silicide Technology and Low Temperature Furnace Annealing

Bin-Shing Chen and Mao-Chieh Chen

Abstract-This work investigates the shallow CoSi2 contacted junctions formed by BF<sub>2</sub><sup>+</sup> and As<sup>+</sup> implantation, respectively, into/through cobalt silicide followed by low temperature furnace annealing. For  $p^+n$  junctions fabricated by 20 keV BF<sub>2</sub><sup>+</sup> implantation to a dose of  $5 \times 10^{15}$  cm<sup>-2</sup>, diodes with a leakage current density less than 2 nA/cm<sup>2</sup> at 5 V reverse bias can be achieved by a 700°C/60 min annealing. This diode has a junction depth less than 0.08  $\mu$ m measured from the original silicon surface. For  $n^+p$  junctions fabricated by 40 keV As<sup>+</sup> implantation to a dose of  $5 \times 10^{15}~\text{cm}^{-2}$ , diodes with a leakage current density less than 5 nA/cm<sup>2</sup> at 5 V reverse bias can be achieved by a 700°C/90 min annealing; the junction depth is about 0.1  $\mu$ m measured from the original silicon surface. Since the As+ implanted silicide film exhibited degraded characteristics, an additional fluorine implantation was conducted to improve the stability of the thin silicide film. The fluorine implantation can improve the silicide/silicon interface morphology, but it also introduces extra defects. Thus, one should determine a tradeoff between junction characteristics, silicide film resistivity, and annealing temperature.

# I. INTRODUCTION

THE rapid advance of integrated circuit technology has moved the minimum feature size into submicrometer range. The vertical dimension also needs to be shrunk so as to improve the device's characteristics. Thus, reducing the junction depth becomes critical for advanced CMOS devices. Shallow junctions are hard to achieve because the ion implantation process will produce the implanted dopant profile to a given depth. Furthermore, the lateral spreading resistance and contact resistance of a shallow junction are often too large [1]; as a result, the device's speed may be slowed down by the parasitic resistance. This problem can be alleviated by metallizing the source/drain junction with silicide [2]-[5]. However, the quarter-micron device requires a junction depth of less than 0.1  $\mu$ m and the silicidation of such a shallow source/drain junction will consume a good part of the high doping regions. The major obstacle for the silicidation of ultra shallow junctions comes from the nonuniform silicide/silicon

Manuscript received April 5, 1994; revised August 28, 1995. The review of this paper was arranged by Associate Editor G. W. Neudeck. This work was supported by the National Science Council of the Republic of China under contract NSC-83-0404-E009-018.

B. S. Chen was with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan 300, R.O.C. He is now with Winbond Electronic Corp., Hsinchu, Taiwan, R.O.C.

M. C. Chen is with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan 300, R.O.C. Publisher Item Identifier S 0018-9383(96)01079-9. interface which may lead to local spiking of the junction [6]; consequently, the junction leakage may increase enormously after the silicidation process. To avoid this problem, the silicide film must be much thinner than the junction depth.

A silicide selected for source/drain metallization needs to fulfill many requirements: low resistivity, good chemical stability, excellent high temperature stability, no lateral growth problem, and no reaction with dopant. Cobalt silicide is one of the silicides that satisfy most of the requirements. However, cobalt silicide consumes a large amount of silicon during silicidation. Thus, the deposited cobalt film for source/drain metallization must be very thin. To prevent excessive junction leakage resulting from the silicidation process, one of the effective approaches is to form the contact silicide layer in the first place before conducting the ion implantation for junction formation [7]-[16]. In this scheme, the silicide film serves as an energy barrier and damage basin for ion implantation. Because most of the damage is located in the silicide film, the annealing temperature can be greatly reduced and the lowest process temperature will be determined by the dopant activation level. If the implantation energy is low enough so that all the implanted dopant is placed within the silicide film. the silicide film will further serve as a dopant diffusion source. In this work, we investigate the formation of a CoSi<sub>2</sub> contacted shallow junction using a thin cobalt film of 100 Å thickness to fulfill the requirement of 0.1  $\mu m$  junction depth. First, the thin cobalt film was transformed into cobalt silicide; shallow junctions were then fabricated by implanting an appropriate dopant, BF<sub>2</sub><sup>+</sup> for  $p^+n$  junction and As<sup>+</sup> for  $n^+p$  junction, into/through the cobalt silicide followed by furnace annealing with flowing nitrogen. Part of the  $n^+p$  junction received an additional fluorine implantation to improve the thermal stability of the thin silicide film. The electrical characteristics of  $p^+n$  and  $n^+p$  junctions were investigated and the optimal process windows were determined.

# II. EXPERIMENTAL

Samples were fabricated on n-type and p-type (100)-oriented silicon wafers with 1–2  $\Omega$ -cm nominal resistivity. After standard RCA cleaning,  $5\,000\,\text{\AA}\,$  SiO $_2$  was thermally grown by pyrogenic oxidation. Square active regions with areas of  $2.5\times10^{-3}\,\text{cm}^2$  were defined by the photolithography method followed by the wet etching technique. A cobalt film of 100  $\text{Å}\,$  thickness was then deposited in an e-beam evaporation

TABLE I

SUMMARY OF THE SAMPLE IDENTIFICATION

NUMBER AND THE KEY IMPLANTATION CONDITIONS

| As-1  | As+ 20 keV/5×10 <sup>15</sup> cm <sup>-2</sup>                                                                   |

|-------|------------------------------------------------------------------------------------------------------------------|

| As-2  | As+ 40 keV/5×10 <sup>15</sup> cm <sup>-2</sup>                                                                   |

| AsF-1 | As+ 20 keV/5×10 <sup>15</sup> cm <sup>-2</sup> followed by F+ 30 keV/2×10 <sup>15</sup> cm <sup>-2</sup>         |

| AsF-2 | As+ 20 keV/5×10 $^{15}$ cm $^2$ followed by F+ 30 keV/4×10 $^{15}$ cm $^2$                                       |

| AsF-3 | As $^{+}$ 40 keV/5×10 <sup>15</sup> cm <sup>-2</sup> followed by F+ 30 keV/4×10 <sup>15</sup> cm <sup>-2</sup> . |

system with a base pressure of less than  $5 \times 10^{-6}$  torr and a deposition rate of 1 Å/sec. Without breaking the vacuum, a 400 Å thickness of molybdenum film was deposited on top of the cobalt film to serve as a passivation film to prevent the cobalt from reacting with oxygen during the cobalt silicide formation. The samples were then annealed at 550°C for 30 min in N<sub>2</sub> ambient to form cobalt disilicide (CoSi<sub>2</sub>). Following this annealing, Mo and the unreacted Co were selectively etched in a 5:1:1 mixture of H<sub>2</sub>O:H<sub>2</sub>O<sub>2</sub>:NH<sub>4</sub>OH (HHN) and a 6:1:1 mixture of H<sub>2</sub>O:H<sub>2</sub>O<sub>2</sub>:HCl (HCL), respectively, at 70–85°C. It has been reported that the Mo passivation film can be completely removed by HHN and HCL solutions, and the resulting silicide film is a pure cobalt disilicide film [17]. Part of the samples did not receive the following implantation process, and they are referred to as the control sample hereafter.

The  $p^+n$  junctions were formed by BF<sub>2</sub><sup>+</sup> implantation into/through cobalt silicide at an energy of 20 or 40 keV to a dose of  $5 \times 10^{15}$  cm<sup>-2</sup> followed by annealing in N<sub>2</sub> ambient at temperatures ranging from 600 to 900°C. The annealing time was 60 min for annealing temperatures from 600 to 800°C and was 30 min for the 900°C annealing based on the results of a previous study [15]. For the  $n^+p$  junction formation, As<sup>+</sup> was implanted at an energy of 20 (sample As-1) or 40 keV (sample As-2) to a dose of  $5 \times 10^{15}$  cm<sup>-2</sup>. Part of the 20 keV implanted samples were further implanted with F<sup>+</sup> ion at an energy of 30 keV to a dose of  $2 \times 10^{15}$  (sample AsF-1) or  $4 \times 10^{15}$  cm<sup>-2</sup> (sample AsF-2); and part of the 40 keV implanted samples were further implanted with F+ ion at an energy of 30 keV to a dose of  $4 \times 10^{15}$  cm<sup>-2</sup> (sample AsF-3). The detailed implantation conditions are summarized in Table I. It has been reported that the presence of fluorine can promote the thermal stability of thin cobalt silicide and platinum silicide films [18–20]; thus, the F<sup>+</sup> implantation was designed to improve the high temperature stability of the As<sup>+</sup> implanted cobalt silicide film. All the As<sup>+</sup> and/or F<sup>+</sup> implanted samples were then annealed in N<sub>2</sub> ambient at temperatures ranging from 600 to 900°C. The annealing time was 90 min for the annealing at temperatures from 600 to 800°C and was 30 min for the 900°C annealing based on the results of a previous study [16].

The as-implanted impurity profiles were estimated by TRIM simulation program. Sheet resistance was measured by four point probe (FPP) on the unpatterned area. Secondary ion mass spectrometry (SIMS) was used to determine the dopant concentration profiles. The current-voltage (I-V) characteristics of the junctions were measured by a PC-controlled semiconductor

parameter analyzer HP-4145B and the measurements were conducted at room temperature unless indicated otherwise. The open circuit leakage current of the measuring system was kept below 0.5 pA.

# III. RESULTS AND DISCUSSION

# A. TRIM Simulation

Dopants were implanted after the cobalt silicidation process in this study. In this case, the silicide film serves as an energy barrier for ion implantation because the mass of cobalt is heavier than silicon and the density of cobalt disilicide  $(4.95 \text{ g/cm}^3)$  is much higher than that of silicon  $(2.32 \text{ g/cm}^3)$ . For both  $p^+n$  and  $n^+p$  junctions, two implantation energies were selected: one is to make all the As-implanted dopant within the silicide film and the other to have the implantation tail region penetrated into the silicon substrate. For the former case, the silicon substrate had nearly no implant related defects; for the latter case, some end-of-range defects may exist in the substrate.

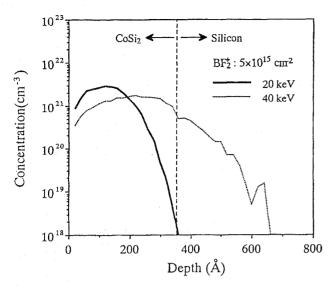

1)  $p^+n$  junction: Fig. 1 shows the TRIM simulation results of the boron profiles for BF<sub>2</sub><sup>+</sup> implantation at 20 and 40 keV to a dose of  $5 \times 10^{15}$  cm<sup>-2</sup>. For the 20 keV implantation, practically no as-implanted boron is placed in the silicon substrate so cobalt silicide has to act as a boron diffusion source in this case. Boron in the silicide layer has to diffuse into the silicon substrate and become electrically activated to form a good junction. Boron has a very high lattice diffusion coefficient in cobalt silicide [21], [22], so it is able to uniformly accumulate to a high concentration at the silicide/silicon interface at low process temperature. Moreover, boron can be electrically activated at a temperature as low as 550°C [23]; thus, using cobalt silicide as a boron diffusion source is possible at low processing temperature. For the 40 keV implantation, the interface boron concentration is about  $5 \times 10^{20}$  cm<sup>-3</sup>, which is high enough to form a good silicided  $p^+n$  junction provided that sufficient dopant can become electrically activated and most of the end-of-range defects can be annealed out.

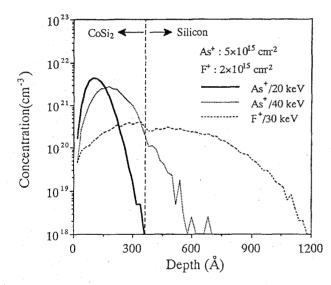

2)  $n^+p$  junction: Fig. 2 illustrates the TRIM simulation results of arsenic profiles for As+ implantation at 20 and 40 keV to a dose of  $5 \times 10^{15}$  cm<sup>-2</sup>. The illustration also shows the simulation result of fluorine profile for F+ implantation at 30 keV to a dose of  $2 \times 10^{15}$  cm<sup>-2</sup>. For the 20 keV As<sup>+</sup> implanted sample, all the as-implanted ions are confined within the silicide layer, and they have to diffuse into the silicon substrate and become electrically activated to form a good junction. However, the lattice diffusivity of arsenic in cobalt silicide is fairly low compared to the high grain boundary diffusivity [22]; thus, it is questionable whether arsenic is able to uniformly distribute at the silicide/silicon interface after the subsequent annealing treatment. For the 40 keV As<sup>+</sup> implanted sample, the interface arsenic concentration is higher than  $1 \times 10^{20}$  cm<sup>-3</sup>, which is high enough to form a good silicided  $n^+p$  provided that sufficient dopant can be electrically activated and most of the end-of-range defects can be annealed out. Since the As+ implanted silicide film tends to show

Fig. 1. The as-implanted boron profiles obtained by TRIM simulation for a silicide film of 350 Å in thickness.

Fig. 2. The as-implanted arsenic and fluorine profiles obtained by TRIM simulation for a silicide film of 350 Å in thickness.

higher sheet resistance than the control sample and degrades quickly at high temperature, the As<sup>+</sup> implanted samples were further implanted with F<sup>+</sup> ions in order to improve the thermal stability of the thin silicide film. This measure is based on the results of a previous study [20], in which we found that the presence of fluorine can improve the thermal stability of a cobalt silicide thin film during high temperature annealing and that the optimal condition for the F<sup>+</sup> implantation is to have the projected range of fluorine ions close to the silicide/silicon interface. The fluorine implantation of 30 keV was chosen to meet the requirement of optimal effect.

# B. Sheet Resistance

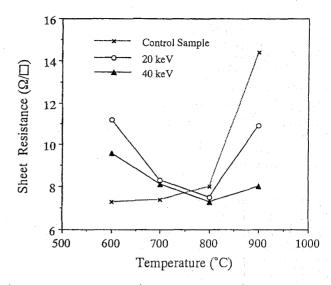

1)  $p^+n$  junction: Fig. 3 illustrates the sheet resistance versus annealing temperature for the control and BF $_2^+$  implanted

Fig. 3. Sheet resistance of  $\mathrm{BF}_2^+$ -implanted  $\mathrm{CoSi}_2$  (350 Å)/Si structure versus annealing temperature. Data for the control sample are also included for comparison.

CoSi<sub>2</sub>/Si samples. Higher sheet resistance of the implanted samples annealed at 600 and 700°C is believed to be due to implantation induced damage and impurity incorporation, which introduced more scattering centers in the silicide. The damage can be recovered by high temperature annealing; thus the sheet resistance is lowered. Sheet resistance of the implanted samples reached their respective minimum values after 800°C annealing, and started to increase at 900°C. In contrast, the control sample exhibited degradation in sheet resistance at 800°C annealing and the silicide film agglomerated into discrete islands at 900°C. The increased stability of silicide film was attributed to the increase of interface energy [20].

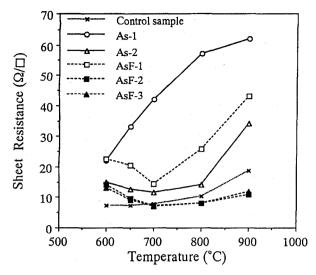

2)  $n^+p$  junction: Fig. 4 shows the sheet resistance for the control and various As+ implanted and As+/F+ dual implanted CoSi<sub>2</sub>/Si samples at various annealing temperatures. Except the sample As-1, sheet resistance of the implanted samples decreased with increasing annealing temperature from 600 to 700°C and reached their respective minimum values at 700°C. It slightly increased at 800°C and further increased by varying degrees at 900°C depending on the implantation condition. The large increase of sheet resistance indicated that the silicide film had started to degrade. Sheet resistance of the samples As-1 and As-2, which did not receive F<sup>+</sup> implantation, was always higher than that of control sample. Sheet resistance of the sample As-1 degraded with increasing annealing temperature, while that of the sample As-2 remained fairly stable up to 800°C. The As+/F+ dual implanted sample AsF-1 exhibited lower resistivity than the As<sup>+</sup> implanted sample As-1 at temperatures higher than 650°C. The improvement can be attributed to fluorine incorporation, which increases the silicide/silicon interface energy and thus retards the agglomeration of cobalt silicide. The As<sup>+</sup>/F<sup>+</sup> dual implanted sample AsF-2, which received a higher dose of fluorine implantation than the sample AsF-1, showed further improvement in silicide film resistivity; in fact, it became more stable than the control sample after 800 and 900°C annealing.

Fig. 4. Sheet resistance versus annealing temperatures for the control and various  $As^+$  implanted and  $As^+/F^+$  dual implanted  $CoSi_2(350\mbox{ Å})/Si$  samples. The implantation conditions for the samples are summarized in Table I

Sample AsF-3 exhibited comparable sheet resistance with sample AsF-2.

# C. SIMS Measurement

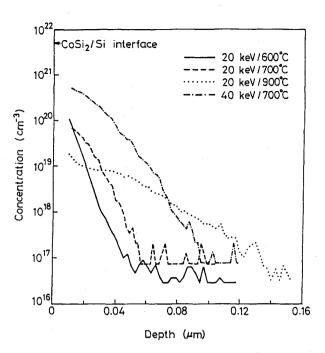

1)  $p^+n$  junction: The dopant concentration profile was determined by SIMS measurements. Fig. 5 shows the boron concentration profiles for the samples implanted with BF<sub>2</sub><sup>+</sup> ions at 20 and 40 keV to a dose of  $5 \times 10^{15}$  cm<sup>-2</sup> followed by annealing at various temperatures. The silicide film was removed before the SIMS analysis. Note that the surface effects during measurement distort the SIMS depth profile at the surface and they often cause a surface peak in the measured profile [24]. Thus, the surface pre-equilibrium region is not shown in Fig. 5 to prevent misunderstanding in determining the dopant concentration near the silicide/silicon interface. For the 20 keV implanted sample, boron concentration near the silicide/Si interface was about  $1 \times 10^{20}~\mathrm{cm^{-3}}$  after  $600^{\circ}\mathrm{C}$ annealing; it decreased slightly to  $7 \times 10^{19}$  cm<sup>-3</sup> after 700°C annealing. The junction depth measured at  $5 \times 10^{17}$  cm<sup>-3</sup> is less than 0.04  $\mu m$  for the 600°C annealed sample and is about 0.05  $\mu$ m for the 700°C annealed sample. The 20 keV implantation did not place as-implanted boron ions in the silicon substrate; nonetheless, a low temperature annealing was able to accumulate the boron concentration near the silicide/silicon interface up to a very high value. At 900°C annealing, the boron concentration at silicide/Si interface decreased to about  $2 \times 10^{19}$  cm<sup>-3</sup> and significant boron diffusion was observed. The decrease in boron concentration near the silicide/Si interface with increasing annealing temperature might be attributed to dopant evaporation from the silicide surface. For the 40 keV implanted sample annealed at 700°C, the boron concentration near the silicide/Si interface is about  $5 \times 10^{20}$  cm<sup>-3</sup>, which is very close to the TRIM simulation results, and the junction depth measured at  $5 \times 10^{17} \ \mathrm{cm}^{-3}$ is about 0.08 µm. Excellent consistency between the TRIM

Fig. 5. Boron concentration profiles obtained by SIMS measurement for the samples implanted with BF $_2^+$  ions at 20 and 40 keV to a dose of  $5\times 10^{15}$  cm $^{-2}$  followed by annealing at various temperatures. The silicide film has been removed before the measurement.

and SIMS results suggests that the boron concentration in the silicon substrate was determined by the As-implanted dopant rather than the dopant building up during anneal.

The SIMS analysis results may overestimate the junction depth; that is, the real junction may be shallower than the result of SIMS measurement. This conjecture arises from the following considerations. First, not all the boron concentration obtained from the SIMS analysis was electrically activated because of the fairly low annealing temperature. Second, the silicide/silicon interface always shows a certain degree of undulation because the cobalt silicide film is grown via diffusion associated with the nucleation controlled process [25]. The uneven interface can cause considerable broadening of the measured SIMS profiles [24]. Third, the ion mixing effect can broaden the measured profile, especially for a light atomic mass element such as boron. Consequently, the actual junction depth should be somewhat less than the measured value.

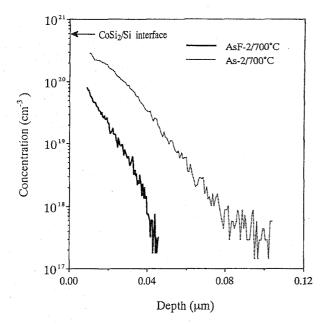

2)  $n^+p$  junction: Fig. 6 shows the arsenic concentration profiles for the 700°C annealed As-2 and AsF-2 samples where the silicide films have been removed before the SIMS analysis. The surface pre-equilibrium region of the SIMS profile is not plotted in the figure. For the 700°C annealed sample As-2, the arsenic concentration near the silicide/silicon interface is about  $3 \times 10^{20}$  cm<sup>-3</sup>, and the junction depth measured at  $1 \times 10^{18}$  cm<sup>-3</sup> is about 0.07  $\mu$ m. For the sample AsF-2, the arsenic concentration near the silicide/silicon interface is about  $8 \times 10^{19}$  cm<sup>-3</sup> and the junction depth measured at  $1 \times 10^{18}$  cm<sup>-3</sup> is about 0.04  $\mu$ m. Since the 20 keV As<sup>+</sup> implantation confined all the implanted dopants within the silicide layer, arsenic in the silicon substrate was built up

Fig. 6. Arsenic concentration profiles for the 700°C annealed AsF-2 and As-2 samples obtained by SIMS measurement. The silicide film has been removed before the measurement.

during the low temperature annealing. It should be also noted that the SIMS analysis may overestimate the junction depth.

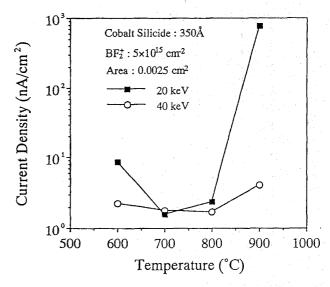

# D. Electrical Characteristics

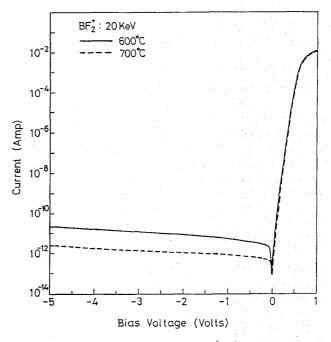

I)  $p^+n$  junction: Fig. 7 shows the reverse leakage current density measured at 5 V reverse bias for the  $p^+n$  junctions fabricated by various implantation and annealing conditions. The leakage current density measured at 5 V reverse bias was less than 10 nA/cm² for both the 20 and 40 keV implanted junctions annealed at temperatures from 600 to 800°C, but it increased to more than 700 nA/cm² for the 20 keV implanted junction annealed at 900°C. Fig. 8 illustrates the typical current-voltage characteristics for the 20 keV implanted junction annealed at 600 and 700°C.

For the 20 keV implanted CoSi<sub>2</sub>/Si junction, the electrical characteristics were very sensitive to silicide film integrity, dopant activation level, and the amount of boron accumulated around the silicide/silicon interface. At 600°C annealing, the dopant activation level was presumably too low; although the interface boron concentration was high enough, the electrically activated dopant concentration was still slightly insufficient. After 700°C annealing, the activation level increased and the junction characteristics improved. The slightly increased leakage for the 800°C annealed sample is believed to be due to the continual decrease of interface boron concentration, which outweighed the effect of increased dopant activation level. Further increasing the annealing temperature led to severe dopant evaporation from the silicide surface and the deficiency in boron concentration resulted in poor junction characteristics. In addition, silicide film agglomeration further worsened the results [20].

On the other hand, the 40 keV implanted junction exhibited much improved leakage behavior. The leakage current density

Fig. 7. Reverse leakage current density versus annealing temperatures for the  $BF_2^+$  implanted  $CoSi_2$  (350 Å)/ $p^+n$  junction. The reverse bias is 5 V and the junction area is 0.0025 cm<sup>2</sup>.

Fig. 8. Typical I-V characteristics of  $CoSi_2$  (350 Å)/ $p^+n$  junction fabricated by BF<sub>2</sub><sup>+</sup> implantation at 20 keV to a dose of  $5 \times 10^{15}$  cm<sup>-2</sup> followed by 600 or 700°C annealing for 60 min. The junction area is 0.0025 cm<sup>2</sup>.

gently decreased from 600 to 800°C and somewhat increased after 900°C annealing. For the implantation at 40 keV, a large amount of boron was already placed in the silicon substrate, and thus dopant evaporation from the silicide surface had only a minor effect on the electrical characteristics, especially at low annealing temperature. However, the implantation tail introduced end-of-range defects, the elimination of which required high temperature annealing. Thus, the junction leakage current decreased with increased annealing temperature before the silicide film started to degrade because of higher dopant

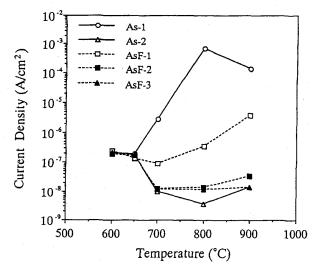

Fig. 9. Reverse leakage current density versus annealing temperatures for the As<sup>+</sup> implanted and As<sup>+</sup>/F<sup>+</sup> dual implanted CoSi<sub>2</sub> (350 Å)/ $n^+p$  junction. The reverse bias is 5 V and the junction area is 0.0025 cm<sup>2</sup>.

activation level and lesser end-of-range defects at elevated annealing temperature. At 900°C annealing, the 40 keV implanted junction exhibited much less degradation in leakage current compared to the 20 keV implanted junction because the 40 keV implanted sample had a deeper junction and a much stable silicide film.

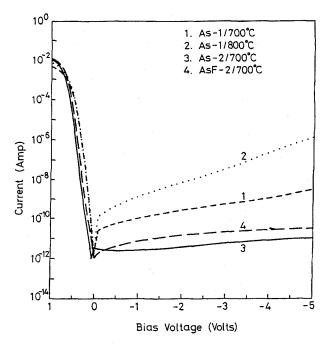

2)  $n^+p$  junction: Fig. 9 shows the reverse leakage current density measured for the As+ implanted and As+/F+ dual implanted  $CoSi_2/n^+p$  junctions annealed at various temperatures. The leakage current density for samples As-2, AsF-2, and AsF-3 was less than 20 nA/cm<sup>2</sup> from 700 to 800°C annealing; a minimum leakage current density of 4 nA/cm<sup>2</sup> was obtained for the 800°C annealed sample As-2. For the samples As-1 and AsF-1, the leakage current density was larger than 90 nA/cm<sup>2</sup> irrespective of the annealing temperature. The typical I-V characteristics for the samples As-1, As-2 and AsF-2 are illustrated in Fig. 10. For the sample As-1 annealed at 700 and 800°C, leakage current increased with increasing reverse bias. Since the sheet resistance of sample As-1 increased with increasing annealing temperature in the range of 700 to 800°C, as shown in Fig. 4, the agglomeration process of silicide film was probably in progress. The film agglomeration always leads to rugged silicide/silicon interface, which in turn may produce an ultra shallow junction in some localized regions. The dopant concentration at those local regions could be very low, which makes the junction leakage current dependent on the reverse bias [15].

The electrical characteristics of  $n^+p$  junctions depend on several factors including silicide film integrity, damage recovery level, dopant activation level, and the arsenic concentration at the silicide/silicon interface. At 600 and 650°C annealing, the damage recovery level, dopant activation level, and interface arsenic concentration were all presumably too low; moreover, the end-of-range defects were not completely annihilated. Thus, the electrically activated arsenic concentration in the silicon substrate was insufficient and numerous

Fig. 10. Typical I-V characteristics for the samples As-1, As-2, and AsF-2 annealed at 700 or 800°C temperature. The junction area is 0.0025 cm<sup>2</sup>.

generation-recombination centers in the substrate led to high reverse bias leakage. This was confirmed by the observed leakage current density as follows. In Fig. 9, it is observed that all the samples annealed at 600 and 650°C exhibit a leakage current density larger than 100 nA/cm<sup>2</sup> including the samples As-2 and AsF-3, whose as-implanted arsenic concentration at the silicide/silicon interface was estimated to be higher than  $1 \times 10^{20}$  cm<sup>-3</sup>. After annealing at temperatures above 700°C. the increased activation level, damage recovery level, and interface arsenic concentration should all have contributed to better junction characteristics, provided the integrity of silicide film was preserved. Unfortunately, the silicide films in most of the As<sup>+</sup> implanted samples only remained stable up to 700°C and degraded after 800°C annealing, as indicated by the results of sheet resistance measurement shown in Fig. 4. Thus, the optimum annealing temperature lies between 700 and 800°C depending on the implantation condition. Deeper junctions are less sensitive to silicide film degradation and thereby are expected to have a better thermal stability. This was confirmed by the observation that the 800°C annealed sample As-2 exhibited lowest leakage, because the As-2 junction was formed by 40 keV As+ implantation and thus had the deepest junction among all the samples at a given annealing temperature. The leakage current of samples As-2 and AsF-3, both formed by 40 keV As<sup>+</sup> implantation, only increased slightly at 900°C annealing. In contrast, the junction leakage of all other samples, which were formed by 20 keV As<sup>+</sup> implantation, started to increase at 800°C annealing and further increased at 900°C annealing.

Fluorine implantation can improve junction characteristics as well as thermal stability of the silicide film. Implantation, however, also introduces damage in the silicon substrate. The damage will contribute to the junction leakage. The sample AsF-1 (2  $\times$  10<sup>15</sup> cm<sup>-2</sup> dose of F<sup>+</sup> implantation) exhibited better junction characteristics than the sample As-1 (no fluorine implantation) after annealing at temperatures above 700°C, but the reverse leakage current was still too high. This was due to limited improvement in sheet resistance by F<sup>+</sup> implantation; in other words, the quality of silicide film was still not well preserved. By increasing the implanted dose of F<sup>+</sup> ions, we had considerably reduced the reverse leakage current density to around 10 nA/cm<sup>2</sup> for the 700°C annealed sample AsF-2 ( $4 \times 10^{15}$  cm<sup>-2</sup> dose of F<sup>+</sup> implantation). As for the sample AsF-3 and As-2, both of them formed by 40 keV As+ implantation, the As+/F+ dual implanted junction AsF-3 showed a slightly higher leakage than the As+ implanted junction As-2. This was presumably due to the implantation defects introduced by F<sup>+</sup> implantation. It should be noted that the silicide films on samples AsF-2 and AsF-3 were the most stable ones among all the samples, but their leakage currents were still higher than that of sample As-2.

# E. Activation Energy Measurement

I)  $p^+n$  junction: The temperature dependence of reverse junction current  $I_r$  can provide insight into the leakage mechanism. The temperature dependence of reverse current  $I_r$  is given by

$$I_r \propto T^3 \exp(-E_a/kT) \tag{1}$$

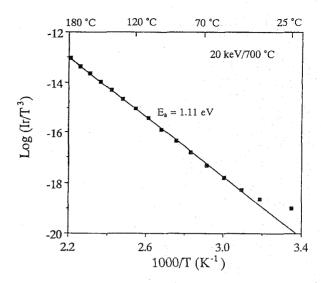

where  $E_a$  is the activation energy of the junction. The value of  $E_a$  is close to the bandgap of silicon  $E_g$  when the reverse current is dominated by the diffusion current and will be close to  $E_g/2$  when the reverse current is dominated by the generation current. Fig. 11 shows the Arrhenius plot for the 20 keV implanted sample annealed at  $700^{\circ}$ C. The measurement was conducted at 5 V reverse bias. The activation energy was found to be 1.11 eV, which is very close to the silicon bandgap of 1.12 eV. This result clearly indicates that the reverse leakage current was dominated by the minority carrier diffusion current at temperatures from 50 to  $180^{\circ}$ C.

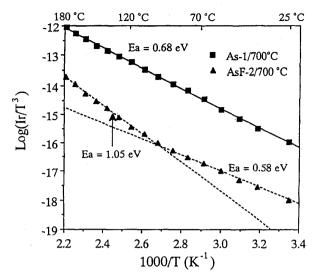

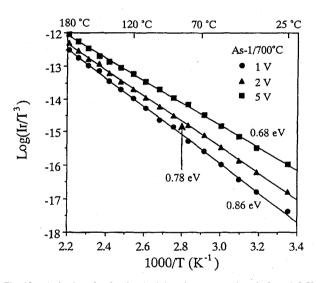

2)  $n^+p$  junction: Fig. 12 shows the Arrhenius plot for the samples As-1 and AsF-2 measured at 5 V reverse bias. The junctions of samples AsF-2 and As-1 were formed by As<sup>+</sup>/F<sup>+</sup> dual implantation and As<sup>+</sup> implantation, respectively, followed by 700°C annealing. It should be noted that both samples received the same arsenic implantation condition (at energy 20 keV to a dose of  $5 \times 10^{15}$  cm<sup>-2</sup>). For the sample AsF-2, the activation energy was found to be 0.58 eV from 25 to 90°C and 1.05 eV from 110 to 180°C. Since the additional fluorine implantation may have introduced defects in silicon substrate and a low temperature annealing such as 700°C cannot anneal out all the defects, the generation current still dominated the reverse current at temperatures below 90°C. However, the activation energy of 1.05 eV at temperatures above 110°C indicates that the junction still preserved the basic property of a deep junction. It also suggests that the 700°C annealing activated the implanted arsenic to a reasonable activation level. For the sample AsF-2 annealed at 800°C, similar results were observed; that is, the activation

Fig. 11. Arrhenius plot for  $\text{CoSi}_2(350 \text{ Å})/p^+n$  junction fabricated by  $\text{BF}_2^+$  implantation at 20 keV to a dose of  $5 \times 10^{15} \text{ cm}^{-2}$  followed by  $700^\circ\text{C}$  annealing for 60 min. The measurement was conducted at 5 V reverse bias.

energy is 0.57 eV from 25 to 90°C and 1.05 eV from 110 to 180°C. For the sample As-1, the activation energy was found to be 0.68 eV from 25 to 180°C. The low activation energy may be due to defects in the silicon substrate or the formation of a localized quasi-Schottky contact [6], [26]. Since the implantation energy of 20 keV would confine all the implanted arsenic within the silicide film, and only a few defects would be generated in the silicon substrate, the implantation related defects can hardly account for the low activation energy. Instead of the implantation defects. a localized quasi-Schottky contact in the As-1 sample, as discussed previously, may account for the low activation energy. The effective barrier height of the quasi-Schottky contact should be higher than that of a real Schottky contact and should be dependent on the bias voltage because an increase of bias voltage increases the depletion region width, which in turn would increase the localized quasi-Schottky contact area; consequently, the reverse bias leakage current of sample As-1 significantly increased with increasing bias voltage, as shown in Fig. 10. The Arrhenius plot for the sample As-1 measured at various bias voltages is illustrated in Fig. 13. The activation energies were 0.86, 0.78, and 0.68 eV corresponding to 1, 2, and 5 V reverse bias, respectively. These values are all higher than the Schottky barrier height of 0.48 eV for CoSi<sub>2</sub> on a p-type silicon substrate. Since the reverse current of a Schottky junction is dominated by the exponential term which is dependent on reciprocal temperature 1/T, the activation energy should be very close to the effective barrier height. The fact the activation energy for the sample AsF-2 can reach 1.05 eV further supports the concept that the contact of sample As-1 contained a localized Schottky contact. Therefore, we infer that the leakage current arising from localized quasi-Schottky contact area dominated the reverse leakage current and that the ion implantation increased its effective barrier height. The high activation energy of sample AsF-2 also indicates that this sample had a better

Fig. 12. Arrhenius plot for the samples As-1 and AsF-2, the junctions of which were formed by As<sup>+</sup> implantation and As<sup>+</sup>/F<sup>+</sup> dual implantation, respectively, followed by 700°C annealing for 90 min. The As<sup>+</sup> implantation was conducted at 20 keV to a dose of  $5\times10^{15}$  cm<sup>-2</sup>, and the F<sup>+</sup> implantation was conducted at 30 keV to a dose of  $5\times10^{15}$  cm<sup>-2</sup>. The measurement was conducted at 5 V reverse bias.

Fig. 13. Arrhenius plot for the As-1 junction measured at 1, 2, and 5 V reverse bias. The As-1 junction was formed by As $^+$  implantation at 20 keV to a dose of  $5 \times 10^{15} \ {\rm cm}^{-2}$  followed by  $700^{\circ}{\rm C}$  annealing.

silicide/silicon interface morphology than the sample As-1. Apparently, the silicide/silicon interface morphology can be effectively improved by fluorine implantation. The fluorine ion implantation also had the effect of reducing diffusion enhancement of arsenic [27].

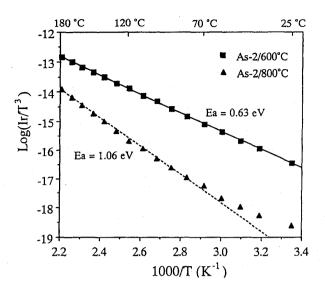

Fig. 14 shows the Arrhenius plot for sample As-2 annealed at 600 and 800°C. For the junction formed at 600°C annealing, we believe that the low activation energy of 0.63 eV was due to insufficient electrically activated dopant concentration underneath the silicide layer rather than due to implantation damage. This argument can be further supported by the fact that the activation energies of samples As-1, AsF-1, AsF-2, and

Fig. 14. Arrhenius plot for the As-2 samples annealed at 600 and  $800^{\circ}$ C. The As-2 junction was formed by As<sup>+</sup> implantation at 40 keV to a dose of  $5 \times 10^{15}$  cm<sup>-2</sup> followed by furnace annealing. The measurement was conducted at 5 V reverse bias.

AsF-3 annealed at 600°C were all around 0.65 eV from 25 to 180°C. For sample As-2 annealed at 800°C, the reverse current was fully dominated by the diffusion current at temperatures higher than 70°C.

# IV. CONCLUSION

We have investigated the shallow cobalt silicided  $p^+n$ and  $n^+p$  junctions fabricated by BF<sub>2</sub><sup>+</sup> and As<sup>+</sup> implantation, respectively, into/through a silicide film followed by low temperature furnace annealing. The  $p^+n$  junctions were more easily fabricated than the  $n^+p$  junctions and the allowable process temperature lay between 600 to 800°C. The  $n^+p$ junctions were much more difficult to fabricate, because As<sup>+</sup> implantation aggravated the degradation of the cobalt silicide film. Increasing the As+ implantation energy reduced the silicide film degradation and improved junction characteristics, but the increasing implantation energy led to deeper junctions. An additional F<sup>+</sup> implantation retarded silicide film degradation, but also introduced extra implantation related defects; with this additional implantation, the junction characteristics were improved depending on the As<sup>+</sup> implantation energy. One should determine the trade-off between junction characteristics, junction depth, and the sheet resistance of silicide film.

# REFERENCES

- K. K. Ng and W. T. Lynch, "The impact of intrinsic series resistance on MOSFET scaling," *IEEE Trans. Electron Devices*, vol. 34, p. 503, 1987.

- [2] L. Van den hove, R. Wolters, K. Maex, R. F. De Keersmaecker, and G. J. Declerck, "A self-aligned CoSi<sub>2</sub> interconnection and contact technology for VLSI applications," *IEEE Trans. Electron Devices*, vol. 34, p. 554, 1987

- [3] S. P. Murarka, D. B. Fraser, A. K. Sinha, H. J. Levinstein, E. J. Lloyd, R. Liu, D. S. Williams, and S. J. Hillenius, "Self-aligned cobalt disilicide for gate and interconnection and contacts to shallow junctions," *IEEE Trans. Electron Devices*, vol. 34, p. 2108, 1987.

[4] C. Y. Lu, J. J. Sung, H. C. Kirsch, N. S. Tsai, R. Liu, A. S. Manocha, and S. J. Hillenius, "High-performance salicide shallow-junction CMOS devices for submicrometer VLSI applications in twin-tub VI," IEEE Trans. Electron Devices, vol. 36, p. 2530, 1989.

[5] C. M. Osburn, Q. F. Wang, M. Kellam, C. Canovai, P. L. Smith,

G. E. McGuire, Z. G. Xiao, and G. A. Rozgonyi, "Incorporation of metal silicides and refractory metals in VLSI technology," Appl. Surf.

Sci., vol. 53, p. 291, 1991.

[6] L. Van den hove, K. Maex, L. Hobbs, P. Lippens, R. De Keersmaecker, V. Probst, and H. Schaber, "Comparison between CoSi2 and TiSi2 as dopant source for shallow silicided junction formation," Appl. Surf.

Sci., vol. 38, p. 430, 1989.

[7] R. Liu, D. S. Williams, and W. T. Lynch, "A study of the leakage mechanisms of silicided  $n^+/p$  junctions," J. Appl. Phys., vol. 63,

p. 1990, 1988.

- [8] D. L. Kwong, T. H. Ku, S. K. Lee, E. Louis, N. S. Alvi, and P. Chu, "Silicided shallow junction formation by ion implantation of impurity ions into silicide layers and subsequent drive-in," J. Appl. Phys., vol. 61, p. 5084, 1987.

- [9] B. Y. Tsui and M. C. Chen, "Formation and characterization of a PtSi contacted  $n^+p$  shallow junction," *J. Appl. Phys.*, vol. 68, p. 2265, 1990. [10] B. Y. Tsui, J. Y. Tsai, and M. C. Chen, "Formation of PtSi-contacted

- $p^+n$  shallow junctions by  $\mathrm{BF}_2^+$  implantation and low-temperature furnace annealing," J. Appl. Phys., vol. 69, p. 4354, 1991.

[11] Y. H. Ku, S. K. Lee, and D. L. Kwong, "The application of ion beam

- mixing, doped silicide, and rapid thermal processing to self-aligned silicide technology," J. Electrochem. Soc., vol. 137, p. 728, 1990.

- [12] H. Jiang, C. M. Osburn, Z. G. Xiao, G. McGuire, and G. A. Rozgonyi, 'Ultra shallow junction formation using diffusion from silicides: III. Diffusion into silicon, thermal stability of silicides, and junction integrity," J. Electrochem. Soc., vol. 139, p. 211, 1992.

[13] Q. Wang, C. M. Osburn, and C. A. Canovai, "Ultra-shallow junction

- formation using silicide as diffusion source and low thermal budget,"

- IEEE Trans. Electron Devices, vol. 39, p. 2486, 1992. V. Probst, H. Schaber, A. Mitwalsky, H. Kabza, L. Van den hove, and K. Maex, "WiSi2 and CoSi2 as diffusion sources for shallow-junction formation in silicon," J. Appl. Phys., vol. 70, p. 708, 1991.

- [15] B. S. Chen and M. C. Chen, "Formation of cobalt-silicided  $p^+n$ junctions using implant through silicide technology," J. Appl. Phys., vol. 72, p. 4619, 1992.

- Formation of  $n^+p$  shallow junctions by As<sup>+</sup> implantation through CoSi<sub>2</sub> film," J. Appl. Phys., vol. 74, p. 3605, 1993.

[17] F. M. Yang and M. C. Chen, "Formation of cobalt silicide under a

- passivating film of molybdenum or tungsten," J. Vac. Sci. Technol. B, vol. 9, p. 1497, 1991.

- [18] Q. F. Wang, J. Y. Tsai, C. M. Osburn, R. Chapman, and G. E. McGuire, "Improved stability of thin cobalt disilicide films using BF2 implantation," Appl. Phys. Lett., vol. 61, p. 2920, 1992. [19] B. Y. Tsui, J. Y. Tsai, T. S. Wu, and M. C. Chen, "Effect of fluorine

- incorporation on the thermal stability of PtSi/Si structure," IEEE Trans. Electron Devices, vol. 40, p. 54, 1993.

[20] B. S. Chen and M. C. Chen, "Thermal stability of cobalt silicide thin

- films on Si(100)," J. Appl. Phys., vol. 74, p. 1035, 1993.

- C. Zaring, P. Gas, B. G. Svensson, M. Ostling and H. J. Whitlow, "Lattice diffusion of boron in bulk cobalt disilicide," Thin Solid Films, vols. 193/194, p. 244, 1990.

- [22] O. Thomas, P. Gas, A. Charai, F. K. LeGoues, A. Michel, G. Scilla, and F. M. d'Heurle, "The diffusion of elements implanted in films of cobalt disilicide," *J. Appl. Phys.*, vol. 64, p. 2973, 1988.

[23] M. Y. Tsai and B. G. Streetman, "Recrystallization of implanted

- amorphous silicon layer: I. Electrical properties of silicon implanted with BF<sub>2</sub> or Si<sup>+</sup>+B<sup>+</sup>," *J. Appl. Phys.*, vol. 50, p. 183, 1979.

R. G. Wilson, F. A. Stevie, and C. W. Magee, *Secondary Ion Mass*

- Spectrometry. New York: Wiley, 1989.

[25] F. M. d'Heurle and C. S. Peterson, "Formation of thin films of CoSi<sub>2</sub>:

- Nucleation and diffusion mechanisms," Thin Solid Films, vol. 128, p. 283, 1985.

- [26] J. M Shannon, "Control of Schottky barrier height using highly doped silicon surface layer," Solid State Electronics, vol. 19, p. 537, 1976.

- [27] J. Kato, "The effect of fluorine atoms in high-dose arsenic or phosphorus ion implanted silicon," J. Electrochem. Soc., vol. 137, p. 1918, 1990.

Bin-Shing Chen was born in Tainan, Taiwan, on July 19, 1966. He received the B.S. degree in electrical engineering from National Cheng-Kung University, Tainan, Taiwan, in 1988, and the M.S. and the Ph.D. degrees in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 1990 and 1994, respectively. His dissertation investigated the self-aligned silicidation technologies, gate oxide reliability, and shallow junction

In 1994, he joined the Winbond Electronics Corp., Hsinchu, Taiwan, to work on the development of 0.8-, 0.6-, and 0.5- $\mu m$  Flash E2PROM technologies

Dr. Chen is a member of Phi Tau Phi.

Mao-Chieh Chen was born in Tainan Hsien, Taiwan, in 1939. He received the B.S. degree from the National Taiwan University, Taipei, Taiwan, in 1961, the M.S. degree from the National Chiao-Tung University, Hsinchu, Taiwan, in 1963, and the Ph.D. degree from Carnegie-Mellon University, Pittsburgh, PA, in 1969, all in electrical engineering.

In 1969, he joined the General Motors Research Laboratories, Warren, MI, where his work had been concerned with research and development of semiconductor devices. In 1973, he was appointed as a

professor at the Department of Material Science and Engineering, National Tsing Hua University. In 1974, he joined the faculty of the National Chiao-Tung University as a professor in the Department of Electronics Engineering. He is presently interested in the studies of CVD tungsten and CVD copper as well as metal silicides relevant to VLSI application. In addition, he also served as a Visiting Scientist at the IBM Thomas J. Watson Research Center, Yorktown Heights, NY (1977-1978), and the Microelectronic Center of North Carolina, Research Triangle Park, (1985-1986).