# A Sub-mW All-Digital Signal Component Separator With Branch Mismatch Compensation for OFDM LINC Transmitters

Tsan-Wen Chen, Ping-Yuan Tsai, Jui-Yuan Yu, and Chen-Yi Lee, Member, IEEE

Abstract—Linear amplification with nonlinear components (LINC) is an attractive technique for achieving linear amplification with high efficiency. This paper presents a sub-mW all-digital signal component separator (SCS) design for OFDM LINC transmitters, including a phase calculator and a digital-control phase shifter (DCPS) pair. In addition, a digital mismatch compensation scheme is proposed and integrated into the SCS to reduce the design complexity of the power amplifier. This chip is manufactured in a 90 nm standard CMOS process with an active area of 0.06 mm<sup>2</sup>. The DCPS can generate phase-modulated signals at 100 MHz with 8-bit resolution and RMS error 9.33 ps (0.34°). The phase calculation can be performed at a maximum speed of 50 MHz using a 0.5 V supply voltage, resulting in a 73.88% power reduction. Comparing to state-of-the-art, the power consumption of the overall SCS is only 949.5  $\mu$ W which minimizes the power overhead for an LINC transmitter. This SCS with the branch mismatch compensation provides a 0.02 dB gain and 0.15° phase fine-tune resolution without adding additional front-end circuits. Considering 1 dB gain and 10° phase mismatch, the system EVM of -29.81 dB and ACPR of -34.56 dB can still be achieved for 5 MHz bandwidth 64-QAM OFDM signals.

*Index Terms*—Branch imbalance, efficiency, LINC, mismatch, OFDM, outphasing, SCS.

## I. INTRODUCTION

RTHOGONAL frequency division multiplexing (OFDM) is an attractive technique for robust and high-speed data transmission in the multipath fading channel, and has been applied for several broadband wireless applications such as wireless local area networks (WLANs). However, OFDM signals suffer from large envelope variations when a number of independently modulated subcarriers are summed coherently. To avoid distortion during the amplification, the linear power amplifier (PA) is required to back off the operation point, resulting in considerable efficiency degradation. Accordingly, the transmitter is required to dissipate more DC power to achieve a specified transmitted power level. Linear amplification by nonlinear components (LINC) [1], also called

Manuscript received February 23, 2011; revised May 09, 2011; accepted July 13, 2011. Date of publication September 12, 2011; date of current version October 26, 2011. This paper was approved by Guest Editor Muneo Fukaishi. This work was supported in part by NSC and by MOEA of Taiwan, R.O.C., under Grant 98-EC-17-A-03-S1-005.

The authors are with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 30010, Taiwan (e-mail: goodidea@si2lab.org; bubblegame@si2lab.org; blues@si2lab.org; cylee@si2lab.org).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2011.2164133

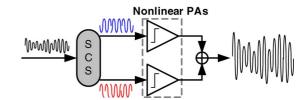

Fig. 1. LINC schematic.

outphasing [2], has been proposed to maintain the PA efficiency along with high quality linearity. As shown in Fig. 1, the basic concept of LINC involves converting the phase-and-amplitude-modulated signal to two phase-only-modulated signals by a signal component separator (SCS), which is then amplified using two high efficiency nonlinear PAs. Finally, the original signal can be reconstructed by combining these two amplified signals.

Although LINC can improve the amplification efficiency, it requires an additional function block, SCS, and the power overhead and separation accuracy become additional design challenges. To separate accurately, digital implementation [3], [4] is assumed the most favorable choice. However, an LINC transmitter with the digital baseband SCS requires four digital-to-analog converters (DAC), and both digital calculations and DACs are operated with higher frequency due to the nonlinear separation process [5], resulting in considerable power dissipation. Several analog designs have been proposed to reduce power consumption [6]-[8], but demonstrate difficulty realizing accurate nonlinear mathematical functions and are sensitive to operation conditions. In addition, those published chips still cost tens-mW-order power consumption, a significant overhead for the transmitter. This work presents a sub-mW and all-digital SCS design for LINC transmitters. Instead of four DACs, this paper proposes two digital-control phase shifters (DCPS) with an automatic calibration to generate the phase-modulated signals. To reduce the digital signal processing (DSP) power, this chip can be globally operated at 0.5 V to save a large amount of power dissipation. Therefore, the proposed SCS solution can achieve both accurate separation and low power consumption for LINC transmitters.

Another limitation of LINC is the tight tolerance of the branch imbalance, resulting in unacceptable out-of-band radiation and in-band signal quality. The system requirements have been discussed by several authors [9], [10]. Approximate gain imbalance of 0.3–0.4 dB and phase imbalance of 2–3° can still be

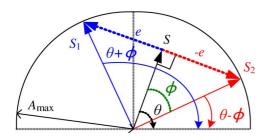

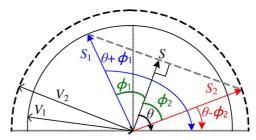

Fig. 2. Vector representation of the SCS.

tolerated, but are nearly impossible for practical implementations. Fortunately, several calibration schemes have been proposed to detect the gain and phase mismatch information accurately by digital processing [10], [11]; the mismatches can then be compensated for before the normal transmission. The phase mismatch can be compensated for by DSP functions or by adding delays to another branch. However, changing the magnitude before a nonlinear PA is useless because only the phase information can be recognized. Adding a high-resolution, gain adjustable capability for PA is required, resulting in higher design complexity and more efficiency loss. Accordingly, a compensation method to balance both gain and phase mismatches by assigning specified phases only is proposed [12], [13]. This work provides more performance analysis and integrates the digital compensation scheme in the SCS, extending the mismatch tolerance and reducing PA design complexity.

This paper is organized as follows. Section II introduces the basic LINC principle and the proposed SCS operation. In Section III, the branch mismatch compensation scheme in the SCS is provided. Chip implementation details are then described in Section IV. Section V shows the chip experimental results and performance comparisons, followed by the conclusion in Section VI.

## II. LINC SCS OVERVIEW

## A. SCS Principle

Denote the baseband signal as  $S_b(t) = S_i(t) + jS_q(t)$ , then the transmitted signal can be generally expressed as

$$S(t) = \operatorname{Re}\left\{ \left( S_i(t) + j S_q(t) \right) e^{j w_c t} \right\} = A(t) \cos \left( w_c t + \theta(t) \right) \tag{1}$$

where A(t) and  $\theta(t)$  are the envelope and phase given by

$$A(t) = \sqrt{S_i^2(t) + S_q^2(t)}$$

(2)

and

$$\theta(t) = \tan^{-1}\left(S_q(t)/S_i(t)\right) \tag{3}$$

respectively. Fig. 2 shows the vector representation of the separation process. One of the separation methods involves calculating the quadrature vector  $\boldsymbol{e}(t)$  by the following equation:

$$e(t) = -jS_b(t)\sqrt{\frac{A_{\text{max}}^2}{A^2(t)}} - 1$$

(4)

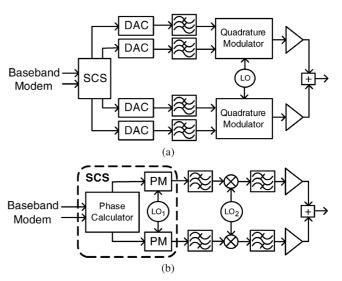

Fig. 3. LINC transmitter architecture with the digital SCS. (a) Direct up-conversion with baseband SCS. (b) Two-stage up-conversion with the phase-modulated based SCS.

where  $A_{\text{max}}$  is the peak amplitude of the signal envelope. The original baseband signal can then be expressed by the summation of two constant-envelope signals  $S_{1b}(t)$  and  $S_{2b}(t)$ :

$$S_{1b}(t) = 0.5 (S(t) + e(t))$$

$$S_{2b}(t) = 0.5 (S(t) - e(t)).$$

(5)

Another separation type is the phase-modulated method. The signal S(t) can be separated into two phase-modulated signals  $S_1(t)$  and  $S_2(t)$ :

$$S_1(t) = 0.5A_{\text{max}}\cos(w_c t + \theta(t) + \phi(t))$$

$$S_2(t) = 0.5A_{\text{max}}\cos(w_c t + \theta(t) - \phi(t))$$

(6)

where

$$\phi(t) = \cos^{-1}(A(t)/A_{\text{max}}).$$

(7)

Because these two signals contain only phase information, they can be generated by two phase modulators (PMs) directly with the calculated phases,  $\theta(t) + \phi(t)$  and  $\theta(t) - \phi(t)$ .

## B. Proposed LINC System

The quadrature signal e(t) can be calculated by a digital implementation with excellent accuracy, and the architecture is shown in Fig. 3(a). After separation in the SCS, two DACs and a quadrature modulator are used on each branch to transfer the digital SCS outputs from digital to analog domains and then up-converted to the radio frequency. However, the LINC system performance is sensitive to the I-Q mismatch and the DC offset of the nonideal quadrature modulators [14]. Therefore, the phase-modulated method is adopted in this work to avoid the need for nonideal quadrature modulators. The proposed LINC architecture with the digital SCS is shown in Fig. 3(b). The phases are calculated by the digital phase calculator and then through a digital-control PM pair. Note

that both quadrature modulators and DACs are not required in the proposed architecture. To achieve low power consumption with adequate phase resolution, this work proposes using two-stage up-conversion architecture. Instead of up-converting to the radio frequency directly, the phase-modulated signals are first generated by a digital-control PM pair at an intermediate frequency (IF) 100 MHz. These two output signals can then be up-converted to the desired radio frequency by two up-mixers. Finally, the signals can be amplified by two efficient PAs and then recombined.

Based on the OFDM-based baseband modem of our previous work for the wireless body area network (WBAN) application [15], a QPSK 64-point OFDM signal with 5 MHz bandwidth is adopted as the signal source in this paper. For performance comparisons and more general applications, the IEEE 802.11a/g 64-QAM 64-point OFDM signal format, having a stricter requirement for the transmitted signal quality, is also considered as the baseband input, except for the 1/4 scaled bandwidth in the following evaluations. Furthermore, the system specification is also referred to the standard, such as the error vector magnitude (EVM) –25 dB and the adjacent-channel power ratio (ACPR) –27 dB.

Because  $S_1(t)$  and  $S_2(t)$  are constant-envelope signals, the required bandwidth is much larger than the original baseband signal (more than  $8\times$ ) [5]. Assuming the baseband signal is interpolated before the signal separation, the proposed digital phase calculator can be operated at a maximal 50 MHz, implying that the SCS outputs with 50 MHz bandwidth ( $10\times$  the original signal bandwidth) can be obtained.

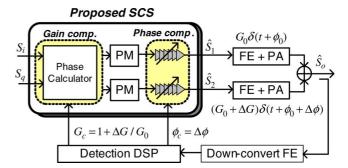

## III. BRANCH MISMATCH COMPENSATION

The branch mismatch (including gain mismatch  $\Delta G$  and phase mismatch  $\Delta \phi$ ) introduces unacceptable in-band and out-band distortions [10]. Accordingly, several methods have been proposed to detect such mismatches [10], [11]. By sending specified testing patterns and adding a low-cost feedback down-converting path, the mismatch information can be calculated by simple digital process. The mismatch can then be eliminated by multiplying a complex scaling in a digital domain. However, scaling the signal magnitude for gain compensation only applies to linear PAs. To achieve higher amplification efficiency, LINC often chooses switching-mode PAs, but such PAs can only recognize the phase information. An extra high-resolution gain adjustment, such as a tunable supply voltage or bias voltage, is required, increasing the hardware cost and power dissipation. Consequently, this work proposes an SCS with a mismatch compensation capability, as shown in Fig. 4. Assuming the mismatch values can be detected accurately, this work integrates a digital compensation scheme with high tuning resolution into the SCS to balance both gain and phase mismatches by assigning specified phases, such that the PA mismatch tolerance can be extended and design complexity can be reduced.

To compensate for the phase mismatch caused by imbalanced FE circuits and PAs, a tunable delay chain on each branch is added to generate a specified delay difference in the SCS. According to a phase mismatch  $\Delta \phi$ , we add a specified codeword offset on one of the delay chains to generate a delay difference

Fig. 4. Proposed SCS design with the branch mismatch compensation capability

Fig. 5. Vector representation of the SCS with the gain compensation ( $V_1=A_{\rm max},V_2=A_{\rm max}G_c$ ).

$\phi_c=\Delta\phi$  between these two delay chains. Then the summation of the phase delays caused by the SCS, FE circuits, and PA on both branches can be balanced completely. Using Fig. 4 as an example, the phase delay of the lower branch is longer than that of the upper branch with  $\Delta\phi$  difference; therefore, we can assign a larger codeword of the upper delay chain to introduce a longer delay to the SCS.

For gain compensation, the gain mismatch information provides feedback to the phase calculator and is balanced by assigning the specified phases. First, the representation of  $S_1(t)$  and  $S_2(t)$  in (6) is modified by adding two phase variables  $\phi_1(t)$  and  $\phi_2(t)$ :

$$S_1(t) = 0.5A_{\text{max}}\cos(w_c t + \theta(t) + \phi_1(t))$$

$$S_2(t) = 0.5A_{\text{max}}\cos(w_c t + \theta(t) - \phi_2(t)).$$

(8)

Denote the gain ratio of two branches denoted as  $G_c = 1 + \Delta G/G_0$ ; the gain mismatch problem can then be considered during the signal separation to satisfy the following quality:

$$S_1(t) + G_c S_2(t) = S(t).$$

(9)

The vector representation of (9) is shown in Fig. 5. Defining  $V_1 = A_{\max}$  and  $V_2 = A_{\max}G_c$ , we can obtain following equations:

$$\begin{cases} V_1 \cos \phi_1(t) + V_2 \cos \phi_2(t) = 2A(t), \\ -V_1 \sin \phi_1(t) + V_2 \sin \phi_2(t) = 0. \end{cases}$$

(10)

By solving the equation, the closed-form expression of  $\phi_1(t)$  and  $\phi_2(t)$  can be derived:

$$\phi_1(t) = \cos^{-1}\left(\frac{V_1^2 + 4A^2(t) - V_2^2}{4A(t)V_1}\right)$$

$$\phi_2(t) = \cos^{-1}\left(\frac{V_2^2 + 4A^2(t) - V_1^2}{4A(t)V_2}\right). \tag{11}$$

Denote  $\hat{S}_1(t)$  and  $\hat{S}_2(t)$  as the signals after both gain and phase mismatch compensation:

$$\hat{S}_1(t) = 0.5 A_{\text{max}} \cos(w_c t + \theta(t) + \phi_1(t) + \phi_c)$$

$$\hat{S}_2(t) = 0.5 A_{\text{max}} \cos(w_c t + \theta(t) - \phi_2(t)). \tag{12}$$

The amplified signal with the proposed compensation denoted as  $\hat{S}_o(t)$  can then be verified:

$$\hat{S}_{o}(t) = G_{0}\hat{S}_{1}(t + \phi_{0}) + (G_{0} + \Delta G)\hat{S}_{2}(t + \phi_{0} + \Delta \phi)$$

$$= G_{0}\left[S_{1}(t + \phi_{0} + \phi_{c}) + G_{c}S_{2}(t + \phi_{0} + \Delta \phi)\right]$$

$$= G_{0}S\left(t + \phi_{0}^{*}\right), \tag{13}$$

which is the desired signal with a constant delay  $\phi'_0 = \phi_0 + \Delta \phi$ . Therefore, the branch mismatch can be balanced by the proposed SCS design.

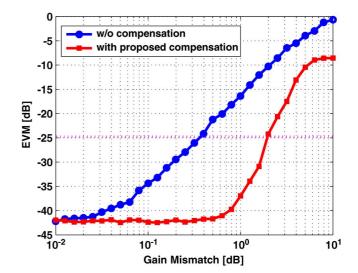

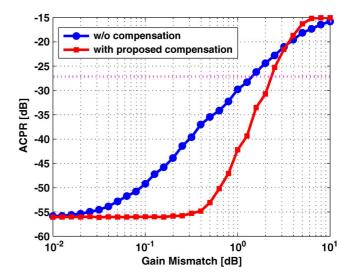

The only limitation of our compensation scheme is that the gain compensation occurring on signal magnitude A(t) is less than  $|V_2-V_1|$ ; but the mismatch effect can still be minimized by setting two vectors in opposite directions. If  $V_2>V_1$ , we can set  $\phi_1=\pi$  and  $\phi_2=0$ . Similarly, we set  $\phi_1=0$  and  $\phi_2=\pi$  when  $V_1>V_2$ . The remaining error signal is then  $(|V_2-V_1|-A(t))e^{j\theta(t)}$ . Fig. 6 and Fig. 7 show the system EVM and ACPR for 8-bit quantized 64-QAM OFDM signals with gain mismatch effect, respectively. To satisfy the specification, the EVM performance is the main limitation. The performance is almost identical to the ideal case when the gain mismatch is less than 0.7 dB, and the tolerance can be extended from 0.4 dB to 2 dB without violating the specification by applying the proposed compensation scheme.

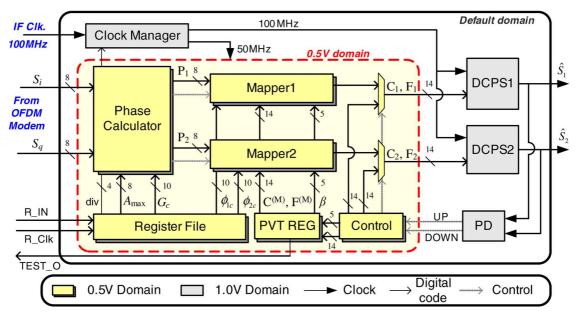

## IV. CHIP IMPLEMENTATION

Fig. 8 presents the chip block diagram and detailed signal paths. The source signal from the baseband modem is  $10\times$  interpolated and quantized to 8 bits before the SCS. The phase calculator then receives the baseband source and calculates the 8-bit phase codeword  $P_1$  and  $P_2$  with 50 MHz operation speed. The mapper is then used to transfer the 8-bit phase codewords to 14-bit control codewords for the DCPS, which behaves as a PM to generate the phase-modulated signal at 100 MHz.

The register file is used to store some parameters and gain mismatch information that are assumed to be decided before system operation. With the branch mismatch values, the phase calculator and the DCPS can provide high-resolution gain and phase compensation capability, respectively. Furthermore, another PVT register is used to store the required parameters detected by an embedded automatic calibrator for the DCPS mapper.

# A. Power Domain Partitions and Voltage Scaling

Due to the high operation speed of DSP functions, the dynamic power proportional to the operating frequency is significant. This work applies the voltage scaling scheme on all DSP functions to reduce the power dissipation. To achieve low power and accurate SCS simultaneously, this chip is partitioned into two independent power domains with different supply voltages. As shown in Fig. 8, the default domain uses 1.0 V to interface

Fig. 6. EVM performance with the gain mismatch effect.

Fig. 7. ACPR performance with the gain mismatch effect.

with IO pads, and the DCPS pair also uses 1.0 V to achieve accurate results. All DSP functions, including the phase calculator, codeword mappers, registers, and controller, are operated with 0.5 V supply voltage to save power consumption. Level shifters are added on all paths that cross the 0.5 V domain to the default domain.

To apply the voltage scaling scheme in the standard-cell-based design procedure, the cell behavior and timing information under 0.5 V supply voltage are simulated and re-calibrated. The cell library is reconstructed after picking out the cells that can work normally. With the reconstructed 0.5 V cell library, the proposed SCS design can be implemented by exploiting a standard-cell-based design procedure to ensure that the circuit is reliable.

# B. Phase Calculator

The phase calculator realizes the nonlinear mathematical calculations of the  $\theta(t)$ ,  $\phi_1(t)$ , and  $\phi_2(t)$  which are described in the previous sections. For the gain compensation, this work uses 10 bits to express the gain mismatch value  $G_c$ , providing a minimal

Fig. 8. Proposed SCS chip design with power domain partitions.

0.02 dB gain compensation resolution. Another system parameter for the phase calculation is the  $A_{\rm max}$  value, which is decided by the trade-off between the clipped signal distortion and the combiner efficiency. Although the nonlinear PA achieves high efficiency, the overall amplification efficiency is still affected by the combiner efficiency related to the phase distribution of  $\phi_1(t)$  and  $\phi_2(t)$  [16]. Larger  $A_{\rm max}$  value can avoid the signal clipping, but also increases the probability of small  $\phi_1(t)$  values and sacrifices the average combiner efficiency. This design provides flexible  $A_{\rm max}$  values for different system requirements and applications. Both  $G_c$  and  $A_{\rm max}$  can be stored in the register file before the SCS operation; the SCS then computes the corresponding  $V_1$  and  $V_2$  values immediately for the phase calculation block.

Considering the increased transition time when using 0.5 V supply voltage, complex computations are difficult in meeting the timing requirement. For the phase calculation in (3) and (11), the critical path occurs on the long-bit divisions. Therefore, we use another expression to avoid the division operations to apply the voltage scaling scheme:

$$\theta(t) = \tan^{-1} \exp\left(\log S_q(t) - \log S_i(t)\right)$$

$$\phi_1(t) = \cos^{-1} \exp\left(\log\left(V_1^2 + 4A^2(t) - V_2^2\right) - \log\left(4A(t)V_1\right)\right)$$

$$\phi_2(t) = \cos^{-1} \exp\left(\log\left(V_2^2 + 4A^2(t) - V_1^2\right) - \log\left(4A(t)V_2\right)\right). \tag{14}$$

All of the divisions can then be replaced by the logarithm table to meet the 50 MHz operation requirement with 0.5 V supply voltage. Using an 8-bit division in  $\theta(t)$  as an example, the synthesized propagation delay and area comparison is shown in Table I. The propagation delay of the division is over the target operation period of 20 ns when scaling to 0.5 V supply voltage. Using the modified expression, the propagation delay of the logarithm table is only 6.53 ns within allowable

TABLE I COMPARISONS BETWEEN DIVISION AND LOGARITHM TABLE

|            | 1.0 V      |             | 0.5 V      |             |

|------------|------------|-------------|------------|-------------|

|            | Gate Count | Propagation | Gate Count | Propagation |

| Division   | 152        | 5.74 ns     | 152        | 22.49 ns    |

| Log. table | 279        | 1.82 ns     | 282        | 6.53 ns     |

gate count increases. The other nonlinear operations, such as arctangent-exponential and arc-cosine-exponential functions, are also implemented by a reference table to reduce the propagation duration and computation complexity.

## C. DCPS and Mapper Design

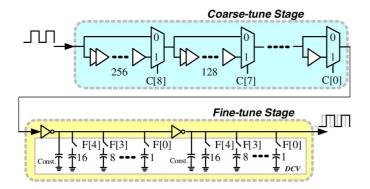

Close-loop circuits have restrictions in achieving the multiphase generation with high-speed phase changing rate due to the long convergence duration. Therefore, an open-loop, digital-control delay line is suggested to provide the specific phases without convergence cycles. Fig. 9 shows the proposed DCPS structure. To achieve adequate delay range and fine-tune resolution under all processes, voltages, and temperature (PVT) conditions, the proposed delay lines use more control bits to achieve the requirement. This DCPS design contains two-stage delay-lines with a 9-bit coarse-tune codeword C and a 5-bit fine-tune codeword F to achieve adequate delay range and accuracy; and the delay-line is based on power-of-two architecture to avoid needing a complex codeword encoder. The digitally controlled varactors (DCV) [17] are applied to the fine-tune stage to generate ps-level resolution by adding small capacitance loading.

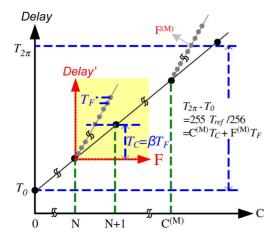

The relationship between the generated delay and two-stage codeword is shown in Fig. 10. With the phase codeword P=k, the output delay of DCPS can be expressed by  $T_0+kT_{ref}/256$ ,  $k=0,1,\ldots,255$ , where  $T_0$  is the constant delay and  $T_{ref}$  is the IF clock period. Denote the two-stage codewords corresponding to the delay  $T_{2\pi}=T_0+255T_{ref}/256$  as  $C^{(M)}$  and  $F^{(M)}$ , and the ratio of coarse-tune resolution  $T_C$  and fine-tune resolution

Fig. 9. Proposed DCPS design based on power-of-two architecture.

Fig. 10. Relationship between the output delay and the two-stage codewords C and F.

$T_F$  as  $\beta$ . To generate the desired phase  $2k\pi/256$ , the mapper provides the DCPS coarse-tune codeword as

$$C = \left\lfloor \frac{C^{(M)}k}{256} \right\rfloor \tag{15}$$

and the fine-tune codeword as

$$F = \left[ \left( \frac{C^{(M)}k}{256} - \left\lfloor \frac{C^{(M)}k}{256} \right\rfloor \right) \beta + \frac{F^{(M)}k}{256} \right]$$

(16)

where the first term is the compensation of the fractional part of coarse-tune codeword for delay accuracy enhancement.

Because the division with denominator 256 can be implemented by shifters, the complexity of the mapper is low. However, the  $C^{(M)}$ ,  $F^{(M)}$ , and  $\beta$  values are influenced by PVT variations; therefore, a detection scheme to detect this information for the mapper before the normal operation is introduced in a later section.

The DCPS is delay-line based and can provide phase compensation capability. With the phase mismatch information, the DCPS pair can add the specified phase difference by adding a constant codeword offset on one of the branches to eliminate the phase delay imbalance. Additionally, high phase compensation resolution can be achieved according to the ps-level fine-tune capability of the DCPS.

Fig. 11. (a) Proposed pre-calibration block diagram and (b) the behavior time-line

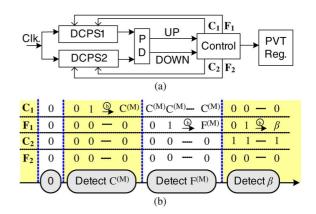

## D. DCPS Automatic Calibration Scheme

To detect the mapper parameters automatically, a calibration scheme is proposed. Taking advantage of the same property in the dual DCPSs, only an extra phase detector (PD) [18] is added to construct a delay-locked-loop (DLL) architecture, and the simplified block diagram is shown in Fig. 11(a).

The proposed scheme has three main states for  $C^{(M)}$ ,  $F^{(M)}$ , and  $\beta$  value detection, respectively. The behavior timeline and corresponding codewords are shown in Fig. 11(b). For  $C^{(M)}$  detection, we first set  $C_2 = 0$  and  $F_2 = 0$  such that the output delay of DCPS2 is  $T_0$ ; we then increase  $C_1$  until the PD outputs "UP" and "DOWN" rise alternately, implying that the DLL converges. After that,  $C^{(M)} = C_1$  can be decided. Similarly,  $F^{(M)}$ can also be detected by the same procedure. To detect  $\beta$  value, we set  $C_2 = 1$  and  $F_2 = 0$ , to ensure that DCPS2 output delay is  $T_0 + T_C$ . Then, increasing  $F_1$  from 0 with fixed  $C_1 = 0$ , the DCPS1 output delay can be expressed as  $T_0 + F_1T_F$ . When  ${

m F_1}={

m F^{(C)}}$  and PD outputs "UP" and "DOWN" rise alternately,  $T_0+T_C=T_0+{

m F^{(C)}}T_F$  is implied. Because  $T_C={

m F^{(C)}}T_F$ ,  $\beta = F^{(C)}$  can be concluded. Therefore, the required parameters can be detected by the proposed method with low extra overhead. The PVT is time varying; therefore, this calibration can be repeated before each transmission. To reduce the convergent cycles of the codeword tracking, the binary search scheme [18] is applied in this work. The required detection cycles of  $C^{(M)}$ ,  $F^{(M)}$ , and  $\beta$  are 18, 10, and 10 in the worst case respectively, so the overall automatic calibration can be finished with less than 38 cycles.

#### V. SIMULATION AND EXPERIMENTAL RESULTS

The proposed SCS chip was fabricated using a 90 nm 1P9M standard CMOS process. Chips with three different process corners (FF, TT, and SS) specified by the factory were measured to verify the behavior. For the experimental environment, the measurement instruments included a LeCroy 4000A oscilloscope and a current-meter with a resolution of 100 pA. For further performance analysis, we used MATLAB and ADS to construct a simulation platform including the behavior model of FE components.

| Corner                 | FF case  | TT case  | SS case  |

|------------------------|----------|----------|----------|

| Constant delay         | 3.27 ns  | 3.63 ns  | 4.22 ns  |

| Max. Coarse-tune Delay | 14.90 ns | 18.73 ns | 22.23 ns |

| Max. Fine-tune Delay   | 0.09 ns  | 0.13 ns  | 0.17 ns  |

| Coarse-tune Resolution | 29.51 ps | 37.76 ps | 43.85 ps |

| Fine-tune Resolution   | 3.06 ps  | 4 21 ns  | 5.42 ns  |

TABLE II

DCPS COARSE-TUNE AND FINE-TUNE OUTPUT DELAY

| 15<br>14<br>13<br>12<br>2 11                         |                                                               |

|------------------------------------------------------|---------------------------------------------------------------|

| Measured Results  Measured Results  Measured Results |                                                               |

| 2 O N                                                | Simulation Measurement (FF) Measurement (TT) Measurement (SS) |

| 0 32 64 96 128 16<br>Phase Codeword                  |                                                               |

Fig. 12. DCPS output delay with different codeword P (target IF clock period 10 ns).

To verify the DCPS delay range, three different process corners chips were measured. The two-stage output delay and resolution are clearly shown in Table II. The maximal output delay of the coarse-tune range in three corners could cover the target IF clock period of 10 ns, and the fine-tune delay range could also cover the coarse-tune resolution. The average resolution of FF, TT, and SS cases were ps-level, not only helping more accurate codeword-to-delay mapping but also providing ps-level phase offset capability. Using the TT case operating at 100 MHz for example, the coarse-tune and fine-tune stages of the DCPS could provide additional maximal delays of 18.73 ns and 0.13 ns with a constant delay of 3.63 ns. The average resolutions of each stage were 37.76 ps and 4.21 ps, respectively, and the measured RMS jitter was 8.57 ps. The output delay could be fine-tuned by adding a specified codeword offset for phase compensation, and the minimal resolution of the DCPS implied a 0.15° phase adjustment capability.

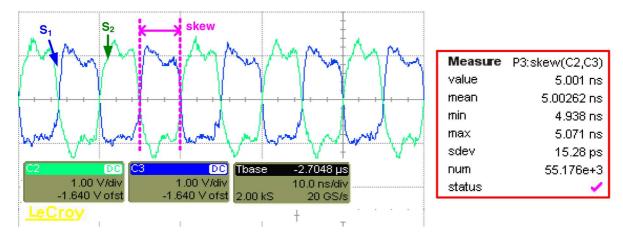

By applying the proposed automatic detection scheme, the required parameters  $C^{(M)}$ ,  $F^{(M)}$ , and  $\beta$  could be obtained and stored for mapper calculation. The measured DCPS output delay with the different codeword P is shown in Fig. 12 where 8-bit resolution with RMS error 9.33 ps (0.34°) could be achieved. The measured results are consistent with the simulation result except for the larger constant delay, because the IO pad delay was not considered during the simulation. The power consumption of the DCPS pair and PD was 912.9  $\mu$ W at 100 MHz IF with 1 V supply voltage. Fig. 13 shows the measured output waveforms example when the baseband input is zero. The ideal

output signal should be two vectors with opposite directions, indicating the 180° phase difference. The measured SCS correctly output the waveforms with a 180° phase difference between the two branches, and the phase difference was 5.003 ns which is close to the ideal value 5 ns.

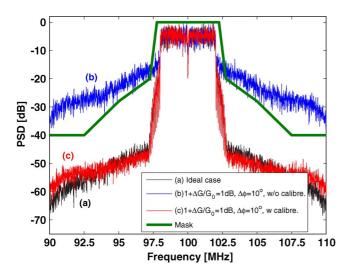

To verify the LINC behavior with the proposed SCS chip and compensation scheme, the characteristic of the measured output waveform was fed back to an FE circuit model (including the filters and a nonlinear PA). Fig. 14 shows the simulated system spectrum at IF considering the branch mismatch effect; the spectrum without mismatch calibration is over the mask due to incomplete outphasing signal cancellation. With the proposed SCS and mismatch compensation scheme, the spectrum can pass the 1/4 scaled 802.11a mask due to the adopted 5 MHz symbol rate in this work. Both EVM -29.81 dB and ACPR -34.56 dB could be achieved, which satisfy the standard requirements of -25 dB and -27 dB, respectively.

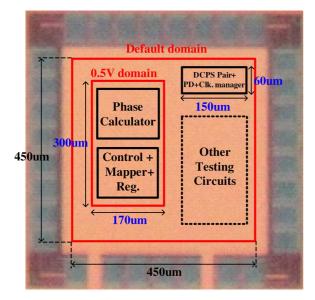

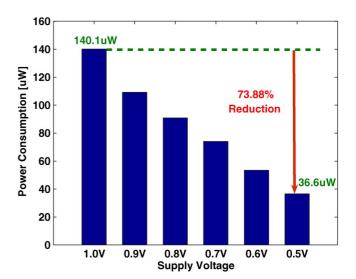

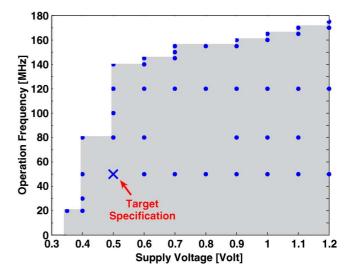

Fig. 15 shows the microchip photo with power domain notations, and the active area of the DCP functions and the DCPS pair is only  $0.06~\rm mm^2$ . The power pads of the default domain and  $0.5~\rm V$  domain are separate; therefore, the power dissipation of the individual domain could be measured independently. The power consumption of the DSP blocks with 50 MHz operation speed is shown in Fig. 16. Note that the power dissipation was reduced from  $140.1~\mu W$  to  $36.6~\mu W$  by scaling the supply voltage to  $0.5~\rm V$ , resulting in 73.88% power reduction. The shmoo plot of the digital processing is shown in Fig. 17, demonstrating that the higher frequency is achievable as the supply voltage increases. Our target specification involves operating at 50 MHz with  $0.5~\rm V$  supply voltage.

The chip summary and comparisons are shown in Table III. The comparison does not include the digital SCSs [3] and [4] because they are implemented by field-programmable gate arrays (FPGA). This work proposes an all-digital and standard-cell-based design. Using a low-complexity DCPS pair instead of DACs, and scaling the supply voltage for DSP blocks, the overall chip consumes only 949.5  $\mu$ W, a significant improvement compared to state-of-the-art chip solutions. For a fair comparison of the power consumption with different technologies, a normalized power factor  $P_{\rm nor}$  is defined as

$$P_{\rm nor} = \frac{P_{\rm ori}}{V_{cc}^2} \tag{17}$$

where  $P_{\rm ori}$  is the reported power before the normalization and  $V_{cc}$  is the supply voltage. As shown in the table, the normalized power factor of the proposed design is still the smallest compared to the state-of-the-art solutions. With the advantages of both technology scaling and low circuits complexity, the active area is also the smallest. The EVM performance is lower than [8] because we further consider the 8-bit baseband quantization error and branch mismatch effect. However, the EVM performance is still acceptable for the demonstrator systems.

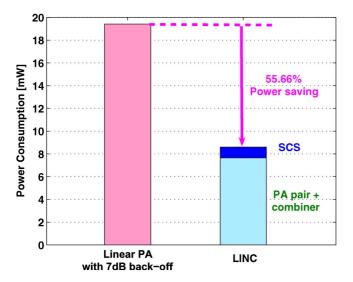

Considering low power applications, such as the WBAN system in [12], we compare the power amplification cost of the conventional transmitter using a linear amplifier (Class-A) and the LINC technique. The circuits of a basic linear PA and Class-D PAs are implemented in ADS for performance

Fig. 13. Measured SCS output waveforms when the baseband input is zero

Fig. 14. Output signal spectrum.

Fig. 15. Chip photograph.

Fig. 16. Measured DSP blocks power with different supply voltages.

Fig. 17. Shmoo plot of the DSP blocks.

of the Class-A PA is only 5.15%, implying a 19.42 mW average power dissipation on the linear PA, dominating the overall transmitter power. For the LINC technique, the average

|                                | [6]           | [7]          | [8]          | This work     |

|--------------------------------|---------------|--------------|--------------|---------------|

| Technology                     | 0.8 um BiCMOS | 0.35 um CMOS | 0.25 um CMOS | 90 nm CMOS    |

| Design                         | Analog        | Analog       | Analog       | All digital,  |

| Strategy                       |               |              |              | Standard-cell |

| Supply Voltage                 | 5.0 V         | 5.0 V        | 2.5 V        | 1.0 V/0.5 V   |

| Operation                      | 200 MHz       | 100 MHz      | Baseband     | 100 MHz IF    |

| Frequency                      | IF            | IF           |              | (50 MHz DSP)  |

| Power Consumption              | 100 mW        | 80 mW        | 45 mW        | 0.95 mW       |

| Normalized                     | 4             | 3.2          | 7.2          | 1.05          |

| Power Factor                   |               |              |              |               |

| Signal                         | DQPSK         | DQPSK/       | 64QAM        | 64QAM         |

| Source                         |               | OQPSK        | OFDM         | OFDM          |

| EVM                            | N/A           | N/A          | -34 dB       | -29.81 dB     |

| Mismatch                       | No            | No           | No           | Yes           |

| Compensation                   |               |              |              |               |

| Active Area (mm <sup>2</sup> ) | 2.66(*)       | 0.61(*)      | 0.09         | 0.06          |

TABLE III

CHIP SUMMARY AND COMPARISONS

Fig. 18. Power consumption comparison of amplification blocks between conventional linear PA and LINC with the proposed SCS.

efficiency can be improved to 13.08%, leading to a power saving of 11.76 mW from the amplification blocks. Because the SCS is an additional overhead in the LINC transmitter, the power dissipation should also be considered, especially for the applications with low transmitted power. The power overhead of the state-of-the-art SCS designs in [6]–[8] are larger than the power saved. Because the proposed SCS costs less than 1 mW, the overall power saving of 10.81 mW can be achieved when applying the LINC technique with the proposed SCS design, resulting in a 55.66% power reduction, as shown in Fig. 18.

## VI. CONCLUSION

An all-digital SCS design is presented in this work, and a branch mismatch compensation scheme is integrated to release the FE circuits and PA design complexity. The proposed low-complexity DCPS pair with an automatic calibration scheme can generate phase-modulated signals without DACs, and also provides high-resolution phase compensation capability. Moreover, the DSP circuits can achieve accurate nonlinear calculation and the power consumption is reduced by applying the voltage scaling. Therefore, a sub-mW and accurate LINC SCS

can be achieved and applied to general OFDM systems to enhance amplification efficiency while maintaining similar link performance.

#### ACKNOWLEDGMENT

The authors would like to thank UMC for the University Shuttle Program in fabricating the test chip and CIC for EDA tool supports. Part of this work was supported by the NSC and MOE ATU programs.

#### REFERENCES

- [1] D. C. Cox, "Linear amplification with nonlinear components," *IEEE Trans. Commun.*, vol. COM-22, no. 12, pp. 1942–1945, Dec. 1974.

- [2] H. Chireix, "High power outphasing modulation," in *Proc. Inst. Radio Eng.*, Nov. 1935, vol. 23, no. 11, pp. 1370–1392.

- [3] S. A. Hetzel, A. Bateman, and J. P. McGeehan, "A LINC transmitter," in *Proc. IEEE Vehicular Technology Conf.*, St. Louis, MO, May 19–22, 1991, pp. 133–137.

- [4] W. Gerhard and R. H. Knoechel, "LINC digital component separator for single and multicarrier W-CDMA signals," *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 1, pp. 274–282, Jan. 2005.

- [5] L. Sundström, "Effects of reconstruction filters and sampling rate for a digital signal component separator on LINC transmitter performance," *Electron. Lett.*, vol. 31, no. 14, pp. 1124–1125, Jul. 1995.

- [6] B. Shi and L. Sundström, "A 200-MHz IF BiCMOS signal component separator for linear LINC transmitters," *IEEE J. Solid-State Circuits*, vol. 35, no. 7, pp. 987–993, Jul. 2000.

- [7] B. Shi and L. Sundström, "An IF CMOS signal component separator chip for LINC transmitters," in *Proc. IEEE Custom Integrated Circuits Conf. (CICC)*, May 2001, pp. 49–52.

- [8] L. Panseri, L. Romanò, S. Levantino, C. Samori, and A. L. Lacaita, "Low-power signal component separator for a 64-QAM 802.11 LINC transmitter," *IEEE J. Solid-State Circuits*, vol. 43, no. 5, pp. 1274–1286. May 2008.

- [9] L. Romanò, L. Panseri, C. Samori, and A. L. Lacaita, "Matching requirements in LINC transmitters for OFDM signals," *IEEE Trans. Circuits Syst. I*, vol. 53, no. 7, pp. 1572–1578, Jul. 2006.

- [10] X. Zhang and L. E. Larson, "Gain and phase error-free LINC transmitter," *IEEE Trans. Veh. Technol.*, vol. 49, no. 5, pp. 1986–1994, Sep. 2000.

- [11] S.-S. Myoung, I.-K. Lee, J.-G. Yook, K. Lim, and J. Laskar, "Mismatch detection and compensation method for the LINC system using a closed-form expression," *IEEE Trans. Microw. Theory Tech.*, vol. 56, no. 12, pp. 3050–3057, Dec. 2008.

- [12] T.-W. Chen, P.-Y. Tsai, J.-Y. Yu, and C.-Y. Lee, "A sub-mW all digital signal component separator with branch mismatch compensation for OFDM LINC transmitters," in *Proc. IEEE Asian Solid-State Circuits Conf. (ASSCC)*, 2010, pp. 209–212.

- [13] J. Hur, K.-W. Kim, K. Lim, and J. Laskar, "A novel unbalanced phase calibration technique for the LINC transmitter," in *Proc. IEEE Radio* and Wireless Symp. (RWS), 2010, pp. 181–191.

- [14] L. Sundström, "Spectral sensitivity of LINC transmitters to quadrature modulator misalignments," *IEEE Trans. Veh. Technol.*, vol. 49, no. 4, pp. 1474–1487, Jul. 2000.

- [15] T.-W. Chen, J.-Y. Yu, C.-Y. Yu, and C.-Y. Lee, "A 0.5 V 4.85 Mbps dual-Mode baseband transceiver with extended frequency calibration for biotelemetry applications," *IEEE J. Solid-State Circuits*, vol. 44, no. 11, pp. 2966–2976, Nov. 2009.

- [16] K.-Y. Jheng, Y.-J. Chen, and A.-Y. Wu, "Multilevel LINC system designs for power efficiency enhancement of transmitters," *IEEE J. Sel. Top. Signal Process.*, vol. 3, no. 3, pp. 523–532, Jun. 2009.

- [17] P.-L. Chen, C.-C. Chung, and C.-Y. Lee, "A portable digitally controlled oscillator using novel varactors," *IEEE Trans. Circuits Syst. II*, vol. 52, no. 5, pp. 233–237, May 2005.

- [18] C.-C. Chung and C.-Y. Lee, "An all-digital phase-locked loop for high speed clock generation," *IEEE J. Solid-State Circuits*, vol. 38, no. 2, pp. 347–351, Feb. 2003.

design

**Tsan-Wen Chen** was born in Taipei City, Taiwan, in 1984. He received the B.S. degree in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 2006. He is currently working toward the Ph.D. degree in electronics engineering at the same university.

His research interests include blind equalization algorithm, VLSI architecture, low-power SoC, low-power WBAN system, OFDM transmitter architecture, and wireless communication systems, especially in OFDM-based baseband transceiver

**Ping-Yuan Tsai** was born in Taipei City, Taiwan, in 1987. He received the B.S. degree in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 2009. He is currently working toward the Ph.D. degree in electronics engineering at the same university.

His research interests include VLSI architecture, low-power SoC, OFDM transmitter architecture, and wireless communication systems, especially in LINC transmitter design.

**Jui-Yuan Yu** was born in Taipei City, Taiwan, in 1979. He received the B.S. and Ph.D. degrees in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 2002 and 2008, respectively.

He is currently serving as a post-doctorate researcher in the same university. His research interests include VLSI architecture, low-power SoC, and wireless communication systems, especially in OFDM-based baseband transceivers for high-speed WLAN, ultra-wideband (UWB) systems, and

low-power WBAN systems.

Chen-Yi Lee (M'01) received the B.S. degree from National Chiao Tung University, Hsinchu, Taiwan, in 1982, and the M.S. and Ph.D. degrees from Katholieke University Leuven (K.U.Leuven), Leuven, Belgium, in 1986 and 1990, respectively, all in electrical engineering.

From 1986 to 1990, he was with IMEC/VSDM, working in the area of architecture synthesis for DSP. In February 1991, he joined the faculty of the Electronics Engineering Department, National Chiao Tung University, Hsinchu, Taiwan, where he

is currently a Professor. His research interests mainly include VLSI algorithms and architectures for high-throughput DSP applications. He is also active in various aspects of high-speed networking, system-on-chip design technology, very low-power designs, and multimedia signal processing. In these areas, he has authored or coauthored more than 180 papers and holds many patents.

Dr. Lee served as the Director of Chip Implementation Center (CIC), an organization for IC design promotion in Taiwan (2000/8–2003/12), and the microelectronics program coordinator of the Engineering Division under the National Science Council of Taiwan (2003/1–2005/12). He was the former IEEE Circuits and Systems Society Taipei Chapter Chair.