# Observation of Extreme-Ultraviolet-Irradiation-Induced Damages on High-Dielectric-Constant Dielectrics

Bing-Yue Tsui, Senior Member, IEEE, Po-Hsueh Li, and Chih-Chan Yen

Abstract—Extreme ultraviolet (EUV) irradiation may induce damages on high-dielectric-constant (high-k) dielectrics. In this letter, the EUV-irradiation-induced damages on HfSiO, HfAlO, and  $Al_2O_3$  are investigated. After EUV irradiation, hole traps, border traps, and interface traps are all increased. All of the three high-k dielectrics exhibit poorer immunity to the EUV irradiation than  $SiO_2$ . The oxide traps scale down with the dielectric thickness. Interfacial layer plays an important role in the increase of border traps and interface traps. Therefore, high-quality SiO-like interfacial layer is critical for radiation-hard devices.

*Index Terms*—Border traps, extreme ultraviolet (EUV), high-dielectric-constant dielectrics, hole traps, interface states.

### I. Introduction

ECENTLY, extreme ultraviolet (EUV) lithography K (EUVL) technology has achieved great progress. It has been seriously considered as the most promising nextgeneration lithography technology. Several full-field EUVL technologies have been demonstrated [1]-[3], and several preproduction EUV tools are installed at main research sites and chip makers. Most of the works on EUVL focused on the lithography issues, including photoresist, optics, masks, and mask inspection technologies. However, it should be noted that the 13.5-nm wavelength of EUV translates the energy of 91.85 eV. This energy is higher than the bonding energies and energy band gaps of all dielectrics. EUV irradiation during processing may result in reliability issue. Recently, we have reported the impact of EUV irradiation on a SONOS memory cell and observed that each layer in the ONO stack would be damaged by the EUV irradiation [4].

High-k dielectric with metal gate is the standard gate structure for high-performance MOSFETs after 45-nm technology node. Although radiation damages on Hf-based high-k dielectrics have been reported in the literature [5], EUV was not employed. In this letter, we evaluate the EUV-irradiation-induced damages on various high-k dielectrics, including HfSiO, HfAlO, and Al<sub>2</sub>O<sub>3</sub>.

Manuscript received July 15, 2011; revised August 8, 2011; accepted August 13, 2011. Date of publication September 25, 2011; date of current version October 26, 2011. This work was supported in part by the Ministry of Education in Taiwan under the ATU Program and in part by the National Science Council, Taiwan, under Contract NSC 97-2120-M-009-007. The review of this letter was arranged by Editor L. Selmi.

The authors are with the Department of Electronics Engineering and the Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: bytsui@mail.nctu.edu.tw).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2011.2165521

# II. EXPERIMENTAL PROCEDURE

A simple metal-insulator-Si (MIS) capacitor structure is used in this letter. The devices were fabricated on p-type Si wafers with a resistivity of 1-10  $\Omega \cdot \text{cm}$ . A metal-organic chemical vapor deposition (MOCVD) system was used to deposit the HfSiO, HfAlO, and Al<sub>2</sub>O<sub>3</sub> films at 500 °C using Hf(Otbu)<sub>2</sub>(mmp)<sub>2</sub>, Si(Otbu)<sub>2</sub>(mmp)<sub>2</sub>, and Al(isopropoxide)<sub>3</sub> as precursors, respectively. An Al<sub>2</sub>O<sub>3</sub> film was also deposited by an atomic layer deposition (ALD) system at 300 °C using  $Al(CH_3)_3$  (TMA) and  $H_2O$  as precursors. All of the high-k films are 15 nm thick. No postdeposition annealing was performed. A 15-nm-thick SiO<sub>2</sub> was thermally grown at 900 °C as the reference sample. The purpose of using the relatively thick dielectric is to detect all of the possible damages either in the bulk of the dielectric or at the dielectric/Si interface from the simple MIS structure. The metal gate is a 40-nm-thick TiN and was deposited by a sputtering system and patterned by a reactive ion etching system. The gate electrode is in circular shape and has a diameter of 275  $\mu$ m. The back side of the samples was deposited by an Al film in an e-gun system as the back-side contact. After a 300 °C/30 min annealing process, the MIS capacitor samples were finished.

The EUV light source comes from the beamline 08A1 constructed at the National Synchrotron Radiation Research Center, Taiwan. The flux is  $1\times 10^{12}$  photons/s, and the spot size is about 0.016 cm². The EUV irradiation times for high-k samples are 60 and 300 s which are equal to 55 and 275 mJ/cm², respectively. The 40-nm-thick TiN layer adsorbs 52% of the EUV dose. The doses used in this letter are higher than that of the expected EUVL in order to magnify the effects. Because SiO<sub>2</sub> is more immune to radiation damages than the high-k dielectrics, the doses used for the SiO<sub>2</sub> sample are 444 and 1880 mJ/cm² in this letter.

# III. RESULTS AND DISCUSSION

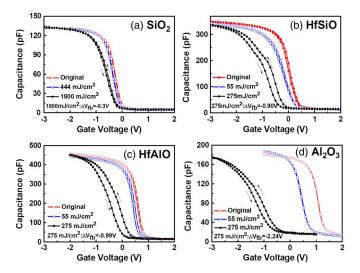

Fig. 1 shows the C-V characteristics of the SiO<sub>2</sub>, HfSiO, HfAlO, and Al<sub>2</sub>O<sub>3</sub> samples before and after EUV irradiation. After the MIS capacitors are irradiated by EUV, the C-V curves of all samples shift toward the negative voltage direction; this means that net positive charges are produced in the dielectrics. Hole trap is the most probable explanation. When the irradiation time is longer, the C-V curves shift more negatively. The C-V shift of the SiO<sub>2</sub> sample is smaller than that of the high-k samples even if the irradiation dose on the SiO<sub>2</sub> sample is much higher.

Fig. 1. Capacitance–voltage characteristics of the (a)  $SiO_2$ , (b) HfSiO, (c) HfAlO, and (d)  $Al_2O_3$  samples before and after EUV irradiation. The three high-k dielectrics were deposited by MOCVD at  $500\,^{\circ}$ C. Hysteresis is observed on all samples.

As the irradiation dose increases, it is observed that the hysteresis gets worse. Not only the high-k samples but also the SiO<sub>2</sub> sample exhibits hysteresis phenomenon. This observation suggests that EUV irradiation may generate border traps at the dielectric/Si interface [6]. These traps may be charged and discharged when the gate bias changes to cause the hysteresis of the C-V curve. It is also observed that more border traps are generated in the high-k samples than in the SiO<sub>2</sub> sample. C-V curve distortion is also observed when the samples receive high-dose irradiation. The distortion is more pronounced at the gate voltage close to accumulation, which implies that lower band donorlike interface states  $(N_{\rm it})$  were generated. The SiO<sub>2</sub> sample exhibits the least C–V distortion. It is not surprising that every kind of the known radiation damages in dielectric occurs after EUV irradiation in all of the four dielectrics studied in this letter. Among them, the SiO<sub>2</sub> sample exhibits the strongest immunity against EUV irradiation.

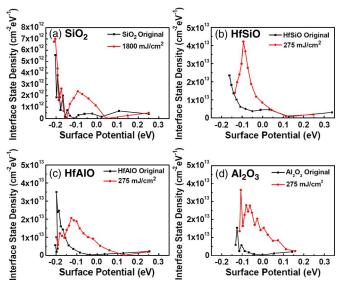

A high-frequency method was used to extract the interface state density  $(D_{\rm it})$  [7]. Fig. 2 shows the energy distribution of the  $D_{\rm it}$  of all samples before and after EUV irradiation. It is clearly observed that, after EUV irradiation, the  $D_{\rm it}$  of all samples increases more than one order of magnitude. It is confirmed that the  $N_{\rm it}$  generated by EUV irradiation is locate at the lower half of the energy gap of Si. Again, SiO<sub>2</sub> is still the most radiation-hard dielectric.

Since the EUV-generated interface states are predominately donorlike in the lower half of the band gap, the EUV-generated oxide trapped charge  $(N_{\rm ot})$  can be extracted by the midgap voltage  $(V_{\rm mg})$  method [8]. The shift of midgap voltage  $(\Delta V_{\rm mg})$  and the shift of flat-band voltage  $(\Delta V_{\rm fb})$  are defined as

$$\Delta V_{\rm mg} = V_{\rm mg2} - V_{\rm mg1} \tag{1}$$

$$\Delta V_{\rm fb} = V_{\rm fb2} - V_{\rm fb1} \tag{2}$$

where  $V_{\rm mg1}$  and  $V_{\rm mg2}$  stand for the midgap voltages before and after EUV irradiation, respectively, and  $V_{\rm fb1}$  and  $V_{\rm fb2}$  are the flat-band voltages before and after EUV irradiation, respectively. As the gate voltage is at  $V_{\rm mg}$ , the EUV-generated donorlike interface states are filled by electrons and are in

Fig. 2 Interface state density of the (a)  $SiO_2$ , (b) HfSiO, (c) HfAlO, and (d)  $Al_2O_3$  samples before and after EUV irradiation. The three high-k dielectrics were deposited by MOCVD at  $500\,^{\circ}$ C.

TABLE I EXTRACTED FLAT-BAND VOLTAGE SHIFT  $(\Delta V_{\mathrm{fb}})$ , Increase of Hysteresis ( $\Delta \mathrm{Hysteresis}$ ), Increase of Oxide Traps  $(\Delta N_{\mathrm{ot}})$ , and Increase of Interface Traps  $(\Delta N_{\mathrm{it}})$  After EUV Irradiation of All Samples Prepared in This Work. Results Are Relevant to the Highest Irradiation Dose

|                                      | SiO <sub>2</sub><br>(440mJ/cm <sup>2</sup> ) | HfSiO<br>(275 mJ/cm <sup>2</sup> ) | HfAIO<br>(275 mJ/cm <sup>2</sup> ) | Al <sub>2</sub> O <sub>3</sub><br>(275 mJ/cm <sup>2</sup> ) | ALD Al <sub>2</sub> O <sub>3</sub><br>(275 mJ/cm <sup>2</sup> ) |

|--------------------------------------|----------------------------------------------|------------------------------------|------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------|

| $\Delta V_{fb}(V)$                   | -0.08                                        | -0.9                               | -0.99                              | -2.39                                                       | -1.92                                                           |

| ∆Hysteresis (V)                      | 0.018                                        | 0.193                              | 0.282                              | 0.216                                                       | 0.353                                                           |

| ΔN <sub>ot</sub> (cm <sup>-2</sup> ) | 1.13x10 <sup>11</sup>                        | 3.64x10 <sup>12</sup>              | 4.32x10 <sup>12</sup>              | 4.48x10 <sup>12</sup>                                       | 3.37x10 <sup>12</sup>                                           |

| ΔN <sub>it</sub> (cm <sup>-2</sup> ) | 9.4x10 <sup>10</sup>                         | 2.73x10 <sup>11</sup>              | 2.64x10 <sup>11</sup>              | 3.9x10 <sup>11</sup>                                        | 7.2x10 <sup>11</sup>                                            |

charge neutrality. Only the change of oxide traps  $(\Delta N_{\rm ot})$  affects the  $\Delta V_{\rm mg}$ , while both  $N_{\rm ot}$  and  $N_{\rm it}$  would affect the flat band voltage shift  $(\Delta V_{\rm fb})$ . Therefore,  $\Delta N_{\rm ot}$  and  $\Delta N_{\rm it}$  can be easily separated by the following equations:

$$\Delta N_{\rm ot} = -\frac{C_{\rm ox} \Delta V_{\rm mg}}{qA} \tag{3}$$

$$\Delta N_{\rm it} = -\frac{C_{\rm ox}(\Delta V_{\rm fb} - \Delta V_{\rm mg})}{qA} \tag{4}$$

where  $C_{\rm ox}$  is the accumulation capacitance, A is the gate area, and q is the electron charge.

After EUV irradiation, the shift of flat-band voltage, the increase of hysteresis voltage, the increase of oxide trap, and the increase of interface state are summarized in Table I. Different dielectrics have different responses to the EUV irradiation. Among these dielectrics,  $SiO_2$  has the best radiation immunity. This result can be explained by several reasons. First, the absorption coefficient of EUV in  $SiO_2$  ( $\sim 10~\mu m^{-1}$ ) is about 3–5 times smaller than that in the other dielectrics ( $35~\mu m^{-1}$  in HfAlO and  $50~\mu m^{-1}$  in HfSiO) [9]. Owing to the longest attenuation length,  $SiO_2$  absorbs less energy from EUV, and then, less e–h pairs are generated. Second,  $SiO_2$  has the widest band gap among these dielectrics. This property also makes the e–h pairs generated in  $SiO_2$  less than those in the other dielectrics. Third, the growth temperature of  $SiO_2$  is 900~C, which is much

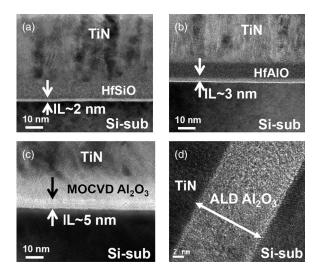

Fig. 3. Interface structure of the (a) MOCVD HfSiO, (b) MOCVD HfAlO, (c) MOCVD Al $_2$ O $_3$ , and (d) ALD Al $_2$ O $_3$  samples inspected by high-resolution transmitted electron microscope.

higher than the deposition temperatures of the other dielectrics. The higher process temperature results in less original trap density in the dielectric. Finally, the strong Si–O bond and low-stress SiO $_2$ /Si interface result in less  $\Delta$ Hysteresis and  $\Delta N_{it}$ .

For the high-k dielectrics, it is hard to predict their radiation hardness from a single factor. Factors such as the amount of e-h pairs generated by EUV irradiation, the total energy absorbed by dielectric, band gap, and bonding energy, etc., all affect the radiation hardness. As we know, the band gap of  $Al_2O_3$  (8.8 eV) is higher than the band gaps of HfAlO ( $\sim$ 6 eV) and HfSiO ( $\sim$ 6 eV) [10]. When the same dose of EUV irradiates on these high-k samples, the energy absorptions by these high-k dielectrics are similar because they have similar absorption coefficients from 35 to 50  $\mu$ m<sup>-1</sup>. The similar  $\Delta N_{\rm ot}$  in these dielectrics implies that these high-k dielectrics have similar bulk trap densities. The largest  $\Delta V_{\rm fb}$  on the  $Al_2O_3$  sample is the consequence of the largest  $\Delta N_{\rm it}$  and the thickest effective oxide thickness.

The  $\Delta N_{\rm it}$  values of the MOCVD samples are similar, but the ALD Al<sub>2</sub>O<sub>3</sub> sample exhibits  $\Delta N_{\rm it}$  twice higher than that of the MOCVD Al<sub>2</sub>O<sub>3</sub> sample. Fig. 3 shows the transmission-electron-microscopy micrographs of the HfSiO, HfAlO, MOCVD Al<sub>2</sub>O<sub>3</sub>, and ALD Al<sub>2</sub>O<sub>3</sub> samples. A 2–5-nm interfacial layer is observed on all of the three MOCVD samples while almost no interfacial layer exists on the ALD Al<sub>2</sub>O<sub>3</sub> sample. It is suspected that the interfacial layer is SiO<sub>2</sub>-like and was formed during the 500 °C MOCVD process [11]. The 300 °C ALD process did not produce an interfacial layer. Because the SiO<sub>2</sub> sample exhibits the best radiation hardness, the SiO-like interfacial layer might explain the reason why the  $\Delta N_{\rm it}$ 's of the MOCVD samples are similar and are lower than that of the ALD Al<sub>2</sub>O<sub>3</sub> sample but higher than that of the SiO<sub>2</sub> sample.

It should be noted that the  $\Delta N_{\rm it}$  is independent of the dielectric thickness. The  $\Delta N_{\rm it}$  of the Hf-based dielectric is around  $2.7 \times 10^{11}$  cm<sup>-2</sup> after EUV irradiation to a dose of 275 mJ/cm<sup>-2</sup>. As the dielectric thickness decreases by ten times, the  $\Delta N_{\rm ot}$  is expected to decrease from  $4 \times 10^{12}$  to  $4 \times 10^{11}$  cm<sup>-2</sup>. Thus, the  $\Delta V_{\rm th}$  is estimated to be  $\sim$ 30 mV

as the effective oxide thickness is 1 nm. Considering that the realistic EUV dose is 10–20 mJ/cm $^2$ , the  $\Delta V_{\rm th}$  is predicted to be less than 10 mV on true devices.

# IV. SUMMARY

In this letter, it has been demonstrated that the EUV irradiation has strong effects on the high-k/metal gate MIS capacitors. Hole traps, border traps, and interface traps would increase after EUV irradiation. Different gate dielectrics have different responses to the EUV irradiation. While the hole traps are the inherent properties of the bulk high-k dielectric, the border traps and interface traps are strongly dependent on the interfacial layer high-k and Si substrate. High-quality SiO<sub>2</sub>-like interfacial layer can improve the radiation hardness. Even if the whole gate dielectric is not exposed to EUV, the gate dielectric at the gate edge would be irradiated by EUV during gate patterning. Therefore, reliability issues must be investigated, and the EUVL process should be designed carefully.

### ACKNOWLEDGMENT

The authors would like to thank the National Nano Device Laboratory and the Nano Facility Center at the National Chiao Tung University for the processing environment. The beamline used is at the National Synchrotron Radiation Research Center, Hsinchu, Taiwan.

## REFERENCES

- [1] A. Veloso *et al.*, "Demonstration of scaled 0.099 μm<sup>2</sup> FinFET 6T-SRAM cell using full-field EUV lithography for sub-22 nm node single-patterning technology," in *IEDM Tech. Dig.*, 2009, pp. 301–304.

- [2] N. Nakamura, N. Oda, E. Soda, N. Hosoi, A. Gawase, H. Aoyama, Y. Tanaka, D. Kawamura, S. Chikaki, M. Shiohara, N. Tarumi, S. Kondo, I. Mori, and S. Saito, "Feasibility study of 70 nm pitch Cu/porous low-k D/D integration featuring EUV lithography toward 22 nm generation," in *IEDM Tech. Dig.*, 2009, pp. 875–878.

- [3] K. Kim, "From the future Si technology perspective: Challenges and opportunities," in *IEDM Tech. Dig.*, 2010, pp. 1–9.

- [4] B. Y. Tsui, C. C. Yen, P. H. Li, and J. Y. Lai, "Effects of extreme ultra-violet irradiation on poly-Si SONOS non-volatile memory," *IEEE Electron Device Lett.*, vol. 32, no. 5, pp. 614–616, 2011.

- [5] J. A. Felix, D. M. Fleetwood, R. D. Schrimpf, J. G. Hong, G. Lucovsky, J. R. Schwank, and M. R. Shaneyfelt, "Total-dose radiation response of hafnium-silicate capacitors," *IEEE Trans. Nuclear Science*, vol. 49, no. 6, pp. 3191–3196, 2002.

- [6] W. Kesternich, "Search for radiation-induced electrical degradation in ion irradiated sapphire and polycrystalline Al<sub>2</sub>O<sub>3</sub>," *J. Appl. Phys.*, vol. 85, no. 2, pp. 748–752, 1999.

- [7] L. M. Terman, "An investigation of surface states at a silicon/silicon oxide interface employing metal-oxide-silicon diodes," *Solid-State Electronics*, vol. 5, no. 5, pp. 285–2992, 1962.

- [8] P. S. Winokur, J. R. Schwank, P. J. McWhorter, P. V. Dressendorfer, and D. C. Turpin, "Correlating the radiation response of MOS capacitors and transistors," *IEEE Trans. Nucl. Sci.NS-31*, pp. 1453–1460, 1984.

- [9] B. L. Henke, E. M. Gullikson, and J. C. Davis, "X-ray interactions: photoabsorption, scattering, transmission, and reflection at  $E=50-30\,000$  eV, Z=1-92," *Atomic Data and Nuclear Data Tables*, vol. 54, no. 2, pp. 181–342, Jul. 1993.

- [10] J. Robertson, "Band offsets of wide-band-gap oxides and implications for future electronic devices," *J. Vac. Sci. Technol. B*, vol. 18, no. 3, pp. 1785– 1791, 2000.

- [11] M. Yamaguchi, T. Sakoda, H. Minakata, S. Xiao, Y. Morisaki, K. Ikeda, and Y. Mishima, "Formation of HfSiON/SiO<sub>2</sub>/Si-substrate gate stack with low leakage current for high-performance high-κ MISFETs," *IEEE Trans. Electron Devices*, vol. 53, no. 4, pp. 923–925, 2006.