# Numerical Analysis of Frequency Dispersion of Transconductance in GaAs MESFET's

Shih-Hsien Lo and Chien-Ping Lee, Senior Member, IEEE

Abstract—A fully two-dimensional numerical model for the transconductance dispersion in GaAs MESFET's is presented. According to simulated results, the dominating surface traps belong to the hole trap type in order to obtain consistent results with reported measurements. The AC frequency-dependent modulation of negative surface charge can explain this anomalous phenomenon. The holes injecting from and emitting out of the gate metal electrode interact with the surface hole traps, and result in the change of the gate-to-source and the gate-to-drain resistances, which in turn cause the change in transconductance. The gate voltage and the gate length effects on the dispersion are also considered. Good agreement with reported results is obtained.

#### I. INTRODUCTION

It is often observed that the small-signal extrinsic transconductance,  $g_m$ , and its phase angle in GaAs MESFET's and JFET's exhibits significant low-frequency dispersion [1]–[7]. The transconductance measured at very low frequencies (usually  $\leq 10$  Hz) is larger than at high frequencies ( $\geq 1$  kHz). The phase angle also has a dip appearing around the transition frequency. The transition frequencies typically range from few 10's Hz to few 10's kHz. Moreover, different surface treatment, gate voltage, temperature, and device structures (such as gate length) also have a strong influence on this transconductance dispersion. The low frequency dispersion of  $g_m$  has a profound effect on the microwave behavior of FET-based MMIC's [8]. To understand and to control this effect is essential in obtaining reliable and controllable device performance.

It has been shown in the past, the charge exchange via surface states existing at the ungated surface region is responsible for the observed dispersion. This was first shown by Ozeki *et al.* [1] and later verified by Wallis *et al.* [4] and Blight *et al.* [5]. Up to now, there have been many reports concerned with the analytical modeling of the transconductance dispersion. Ladbrooks *et al.* [6] proposed a model based on uniform depletion at the ungated surface region due to surface states. Kachwalla [9] applied this model to study surface state energy levels. Kawasaki *et al.* [7] extended the uniform depletion assumption and used two types of fitting parameters to model the dispersion in an ion-implanted GaAs FET's. Zhao *et*

Manuscript received April 5, 1994; revised June 7, 1995. The review of this paper was arranged by Associate Editor J. Xu. This work was supported by the National Science Council under Contract NSC82-0404-E009-381.

S. H. Lo is with the National Nano Device Laboratory, Hsinchu, Taiwan, R.O.C. He is currently on leave with the IBM T. J. Watson Research Center, Yorktown Heights, NY 10598 USA.

C. P. Lee is with the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, R.O.C.

Publisher Item Identifier S 0018-9383(96)01072-6.

al. [10] assumed the surface states at the ungated surface region capture electrons injected from the gate metal and presented a model which correlates the peak frequency in the transconductance dispersion spectrum and the characteristic frequency of the surface states.

There are still remaining questions not well understood. In many conductance-mode DLTS (Deep-Level-Transient-Spectroscopy) experiments on short-gate devices [5], DLTS spectra with signals corresponds to hole traps were observed. But the trap type, i.e., hole trap or electron trap, cannot be directly given from these measured results. Most people thought this anomalous "hole trap signal" is caused by the reinjection of electrons into surface states, since the generation of holes is not normally expected in an n-channel FET [5], [10]. So, the relationship between transconductance dispersion and hole-trap DLTS signal is not yet clarified. In this paper, we present a fully two-dimensional numerical model for the transconductance dispersion. Both the surface and the bulk traps are taken into account. The type of the surface traps and the mechanisms for the low frequency-dispersive transconductance are studied. The effect of gate voltage and gate length on transconductance dispersion are also considered.

# II. PHYSICAL MODELS AND NUMERICAL METHODS

# A. Device Structures

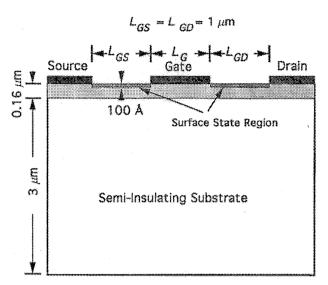

The GaAs MESFET structure used in the simulation is shown in Fig. 1. the n-type channel beneath the gate is 0.16  $\mu$ m thick and is uniformly doped with a concentration of  $1\times10^{17}$  cm<sup>-3</sup>. Both the source-gate and the gate-drain spacing are 1.0  $\mu$ m. The gate length chosen in this calculation are 0.5, 1, 2, 3, 4  $\mu$ m. The threshold voltage is about -1.0 V.

The bulk EL2 concentration  $N_{{\rm TB},D}$  and the shallow-acceptor concentration  $N_A$  in the semi-insulating substrate beneath the channel layer are chosen to be  $1\times 10^{16}$  and  $1\times 10^{15}$  cm<sup>-3</sup>, respectively. Both  $N_{{\rm TB},D}$  and  $N_A$  assumed in this study are typical values found in normal undoped LEC substrates [11], [12]. The total depth simulated is 3.16  $\mu$ m which is deep enough to encompass all physical phenomena. The work function difference of the gate metal-semiconductor contact is assumed to be 0.8 eV. Current transport across the Schottky-barrier junction is described by the thermionic emission-diffusion theory.

#### B. Surface and Bulk Trap Models

The emission and the capture of free carriers for donor-type bulk traps (EL2) in the substrate follow the Shockley-Read-

Fig. 1. A device structure used in the simulation. The surface states are uniformly distributed to a depth of 100 Å.

Hall model. The energy difference between the conduction band edge and the EL2 level,  $E_{\rm CT,B}$ , is assumed to be 0.69 eV at room temperature [13]. The electron and the hole capture cross sections,  $\sigma_{nB,D}$  and  $\sigma_{pB,D}$ , are  $3.5683 \times 10^{-15}$  and  $1 \times 10^{-18}$  cm², respectively [14]. The rate equation for the ionized EL2 traps can be described as

$$-\frac{\partial N_{\text{TB},D}^{+}}{\partial t} = \left[c_{nB,D}N_{\text{TB},D}^{+}n - e_{nB,D}(N_{\text{TB},D} - N_{\text{TB},D}^{+})\right] - \left[c_{pB,D}(N_{\text{TB},D} - N_{\text{TB},D}^{+})p - e_{pB,D}N_{\text{TB},D}^{+}\right]$$

(1)

where  $c_{nB,D}$  and  $e_{nB,D}$  are the capture and the emission rates for electrons, and  $c_{pB,D}$  and  $e_{pB,D}$  are the capture and the emission rates for holes. The relationships between  $c_{pB,D}$  and  $e_{pB,D}$  and between  $c_{nB,D}$  and  $e_{nB,D}$  can be expressed as

$$c_{nB,D} = \sigma_{nB,D} v_{n,\text{th}}$$

$$c_{pB,D} = \sigma_{pB,D} v_{p,\text{th}}$$

$$e_{nB,D} = c_{nB,D} N_C e^{-E_{\text{CT},B}/kT}$$

$$e_{pB,D} = c_{pB,D} N_V e^{-(E_G - E_{\text{CT},B})/kT}$$

(2)

where  $v_{n,\rm th}$  and  $v_{p,\rm th}$  are the thermal velocities of electrons and holes, respectively.

The surface model used in this study was based on Spicer's unified defect model [15]. Two surface deep states were assumed in Spicer's model, i.e., a single donor-type trap,  $E_{\mathrm{CT},S,D}=0.925$  eV, below the conduction band edge and a single acceptor-type trap,  $E_{\mathrm{TV},S,A}=0.8$  eV, above the valence band edge. The energy level of donor-type surface traps is 0.301 eV below that of acceptor type surface traps. At steady state, the ionized donor-type surface charge density is less than one-tenth of occupied acceptor-type surface trap density [16]. It can be expected that the contribution of donor-type surface traps to the electrical characteristics can be negligible, so the donor-type surface traps are neglected in our calculation. For an n-type semiconductor with a doping

concentration of  $1 \times 10^{17}$  cm<sup>-3</sup>, a surface state density of greater than  $2 \times 10^{12}$  cm<sup>-2</sup> is required to pin the surface Fermi level at the position of the defect states [17]. Experimentally, it has been shown that the traps at and beneath the metal-semiconductor interface have little contribution to the dispersion of transconductance [4], [5]. Therefore, they are not considered in the simulation. In this study, the surface states are uniformly distributed to a depth of 100 Å from the ungated surface as shown in Fig. 1. The surface state density is  $5 \times 10^{13}$  cm<sup>-2</sup> in the study and the calculated volume density of the surface traps is  $5 \times 10^{19}$  cm<sup>-3</sup>. In our 2-D numerical analysis, a very small vertical grid spacing of 20 Åis used near the surface region. At thermal equilibrium, the surface Fermi level at the ungated region is calculated to be pinned by the surface states at 0.7 eV below the conduction band edge, which agrees with the measured result. The electron and the hole emission rates for surface traps,  $e_{nS,A}$  and  $e_{nS,A}$ , are two important physical parameters determining the charge trapping and emitting rates for surface traps. From the conductance DLTS experiments on MESFET's performed by Zylbersztein et al. [2] and Blight et al. [5], a large hole trap peak with an emission rate of several 100's s<sup>-1</sup> appears around room temperature. From another conductance DLTS experiments by Harrang et al. [18], with the rate window varied from 8.656 ms to 0.4431 s, a large peak corresponding in sign to "holetrap-like" also appears at around room temperature. Therefore, it is reasonable to assume the carrier emission rate for the dominating surface traps is  $100 \text{ s}^{-1}$ . Only by the conductance DLTS, we cannot directly judge if the dominating acceptortype surface traps are hole traps  $(e_{pS,A} > e_{nS,A})$  or electron traps  $(e_{pS,A} < e_{nS,A})$ . Since the type of the dominating surface traps is unknown, we consider three cases: (1) for hole trap,  $e_{pS,A} = 100 \text{ s}^{-1}$  and  $e_{nS,A} = 0.01 e_{pS,A}$ , (2) for electron trap,  $e_{nS,A} = 100 \text{ s}^{-1}$  and  $e_{pS,A} = 0.01e_{nS,A}$ , and (3) no surface trap, i.e.,  $N_{\rm TS}=0$ .

According to the Shockley-Read-Hall model, the rate equation for surface acceptor traps can be expressed as

$$\frac{\partial N_{\text{TS},A}^{-}}{\partial t} = [c_{nS,A}(N_{\text{TS},A} - N_{\text{TS},A}^{-})n - e_{nS,A}N_{\text{TS},A}^{-}] - [c_{pS,A}N_{\text{TS},A}^{-}p - e_{pS,A}(N_{\text{TS},A} - N_{\text{TS},A}^{-})]$$

(3)

where  $N_{{

m TS},A}$  and  $N_{{

m TS},A}^-$  denotes the total and the occupied acceptor-type surface state densities, respectively. The  $c_{pS,A}$  and the  $c_{nS,A}$ , respectively, are the hole and the electron capture rates for the acceptor-type surface traps. The relationships between  $c_{pS,A}$  and  $e_{pS,A}$  and between  $c_{nS,A}$  and  $e_{nS,A}$  can be expressed as

$$\begin{split} c_{nS,A} &= \sigma_{nS,A} v_{n,\text{th}} \\ c_{pS,A} &= \sigma_{pS,A} v_{p,\text{th}} \\ e_{nS,A} &= c_{nS,A} N_C e^{-(E_G - E_{\text{TV},s,A})/kT} \\ e_{pS,A} &= c_{pS,A} N_V e^{-E_{\text{TV},s,A}/kT}. \end{split} \tag{4}$$

For case (1),  $\sigma_{pS,A}=3.9\times 10^{-11}~{\rm cm}^2$  and  $\sigma_{nS,A}=6.4\times 10^{-15}~{\rm cm}^2$ , and for case (2),  $\sigma_{pS,A}=3.9\times 10^{-13}~{\rm cm}^2$  and  $\sigma_{nS,A}=6.4\times 10^{-13}~{\rm cm}^2$ .

The Poission equation is described as

$$\nabla^{2}\psi + \frac{q}{\varepsilon}(-n + p + N_{D} - N_{A} + N_{\text{TB},D}^{+} - N_{\text{TS},A}^{-}) = 0$$

(5)

where  $\psi$ , q and  $\varepsilon$  are the electrostatic potential, the electron charge and the permittivity of GaAs, respectively. The current continuity equations for electrons and holes are given by

$$\frac{1}{q} \nabla \cdot \vec{J}_{n} - [c_{nB,D} N_{\text{TB},D}^{+} n - e_{nB,D} (N_{\text{TB},D} - N_{\text{TB},D}^{+})]

- [c_{nS,A} (N_{\text{TS},A} - N_{\text{TS},A}^{-}) n - e_{nS,A} N_{\text{TS},A}^{-}] = \frac{\partial n}{\partial t} \quad (6)

- \frac{1}{q} \nabla \cdot \vec{J}_{p} - [c_{pB,D} (N_{\text{TB},D} - N_{\text{TB},D}^{+}) p - e_{pB,D} N_{\text{TB},D}^{+}]

- [c_{pS,A} N_{\text{TS},A}^{-} p - e_{pS,A} (N_{\text{TS},A} - N_{\text{TS},A}^{-})] = \frac{\partial p}{\partial t} \quad (7)$$

where the low field mobility's for electrons and holes are assumed to be  $5\,000$  and  $800~\text{cm}^2/\text{V}\cdot\text{s}$ , respectively.

#### C. Numerical Methods

For small signal simulation, a two-dimensional, two-carrier device simulation program based on the drift-diffusion formulation was developed. Before the small signal analysis, a DC solution for the coupled equations, (1)–(7), needs to be first obtained. The Newton's method is used in our calculation. Then a small-signal analysis described by S. E. Laux [19] is used to calculate the small-signal transconductance value. The AC input gate voltage and the AC solutions are expressed as  $v_G e^{j\omega t}$  and  $\tilde{\psi} e^{j\omega t}$ ,  $\tilde{n} e^{j\omega t}$ ,  $\tilde{p} e^{j\omega t}$ ,  $\tilde{N}_{TB,D}^+ e^{j\omega t}$  and  $\tilde{N}_{TS,A}^- e^{j\omega t}$ , where variables with  $\sim$  above are the complex AC solutions.

The small-signal extrinsic transconductance is defined as

$$\tilde{g}_m = g_m \angle \theta = \frac{\tilde{i}_D(=i_D \angle \theta)}{v_G} \tag{8}$$

where  $g_m$  and  $\theta$  are the magnitude and the phase angle of the small-signal transconductance, respectively, and  $i_D$  is the AC drain current. The AC gate voltage  $v_G$  is 0.05 V in our calculation.

#### III. EXPLANATION OF FREQUENCY DISPERSION

#### A. Trap Type Effect

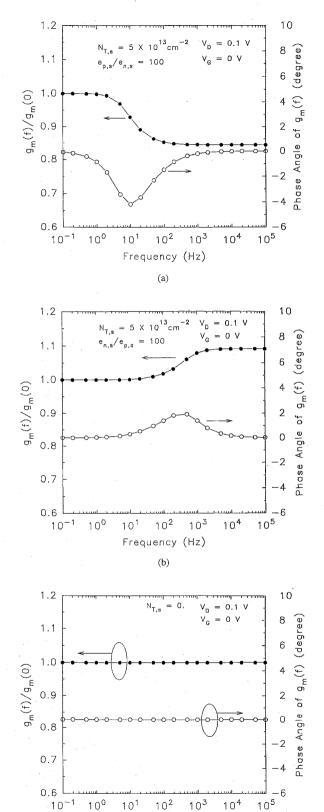

For the three cases defined in Section II, the calculated small-signal transconductance and the phase angle versus frequency are shown in Fig. 2(a)–(c). The FET's gate length is 1  $\mu$ m, the surface state density is  $5 \times 10^{13}$  cm<sup>-2</sup> and the DC drain and the DC gate voltages are 0.1 V and 0 V, respectively. For the hole trap case, as shown in Fig. 2(a), the transconductance at low frequencies is larger than at high frequencies. The transition frequency is around 10 Hz. The percentage shift of  $g_m$ , which is defined as  $(g_m(0) - g_m(f))/g_m(0)$ , is about 15.6%. A maximum dip of phase angle  $\theta$ , which is about  $-4.2^{\circ}$ , is found also at about 10 Hz. This result agrees with all the reported experimental results. But for the electron trap case, as shown in Fig. 2(b), the simulated frequency dispersions are just opposite to the reported experimental results: the transconductance is larger

rather than smaller at high frequencies and a maximum positive  $\theta$  rather than negative  $\theta$  appears at the transition frequency. For the case without surface trap, as shown in Fig. 2(c), no transconductance dispersion and phase angle dip are found. Since the bulk EL2 traps are included in all our calculations, this result indicates that the bulk traps beneath the channel region are not responsible for the transconductance dispersion.

Because the simulated results for the case with surface electron traps are opposite to the measured results, our simulation excludes any close relationship between the surface electron traps and the common observed transconductance dispersion. If the dominating surface traps are hole traps, consistent results with experiments are obtained. Therefore, Our simulation supports that the type of the dominating surface traps are hole trap, i.e.,  $e_{pS}, A > e_{nS}, A$ . Because the holes in an n-channel MESFET are minority carriers, the origin of these holes which interact with surface hole traps still remains to be a question and we discuss it later.

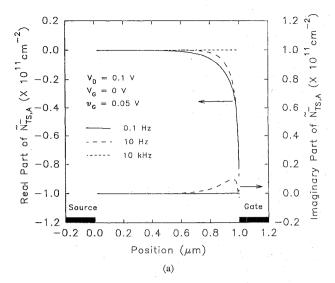

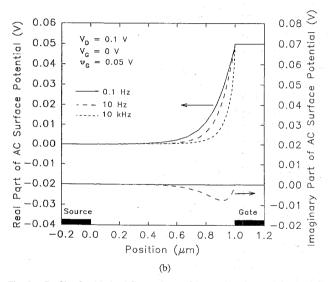

After identifying the trap type of dominating surface states, the following studies are concentrated on the hole trap case. To see the frequency response of surface traps to the AC gate voltage, the AC negative surface trap density and the AC surface potential along the ungated surface region are plotted in Fig. 3(a) and (b), respectively. The calculated frequencies are 0.1 Hz, 10 Hz and 10 kHz. As shown in Fig. 3(a), the AC modulation of  $N_{{

m TS},A}^-$  appears in the region near the gate edge and gradually decays toward the source edge. The AC magnitude of negative surface trap densities decreases with increasing frequency. The real part of AC negative surface charge density,  $\mathrm{Re}(\tilde{N}_{\mathrm{TS},A}^{-})$ , is negative, which means the negative surface trap density decreases at positive cycle of AC gate voltage. As shown in Fig. 3(b), the real part of AC surface potential,  $Re(\psi)$ , is positive and the modulation of surface potential increases with decreasing frequency due to the decrease of  $N_{TS,A}^-$  at low frequencies (shown in Fig. 3(a)). It is noted that the imaginary parts of  $\tilde{N}_{\mathrm{TS},A}^-$  and  $\tilde{\psi}$  are near zero at 0.1 Hz and 10 kHz but significant at 10 Hz, which corresponds to the dip in phase angle at f = 10 Hz (see Fig. 2(a)). From Fig. 3(a) and (b), both the profiles of  $\hat{N}_{\mathrm{TS},A}^-$  and  $\hat{\psi}$  are functions of the distance from the gate edge indicating the surface depletion is not uniform, which is different from the assumption of uniform depletion used by other authors.

It can be expected that the channel depletion due to the modulation of surface negative potential will be quite different. Fig. 4(a) and (b) show the three dimensional plots for the real part of AC free electron concentration at f=0.1 Hz and f=10 kHz, respectively. At both frequencies, the imaginary part of the AC free electron concentration,  $\text{Im}(\tilde{n})$ , is less than one-tenth of the real part,  $\text{Re}(\tilde{n})$ , so  $\text{Im}(\tilde{n})$  is negligible. As shown in Fig. 4(a) and (b),  $\text{Re}(\tilde{n})$  under the gate electrode and at the ungated region is positive, which means the electron concentration increases during the positive cycle of AC gate voltage. Comparing Fig. 4(a) with (b), we can find that the modulated length of ungated surface region due to AC gate voltage is longer at low frequency. It implies that the gate-to-source resistance is frequency-dependent and smaller at lower frequencies. That can be explained by the

Fig. 2. Calculated transconductance dispersion versus frequency for (a) the hole trap case,  $e_{pS}/e_{nS}=100$ , (b) the electron trapcase,  $e_{nS}/e_{pS}=100$  and (c) no surface trap.

Frequency (Hz)

(c)

Fig. 3. Profiles for (a) the AC negative surface trap density, and (b) the AC surface potential along the ungated surface region. The frequencies are 0.1 Hz, 10 Hz and 10 kHz.

frequency-dependent surface potential near the gate edge. At low frequencies, the length of modulated surface region is longer and during the positive cycle of AC gate voltage, the AC positive potential become larger (see Fig. 3(a) and (b)). Therefore, the channel depletion width due to negative surface potential is smaller, i.e., the parasitic source-to-gate resistance is smaller. Moreover, it is expected the gate-to-drain resistance is also smaller at low frequencies as the gate-to-source resistance. So, the extrinsic transconductance is larger at low frequencies due to the two smaller parasitic resistance's.

# B. Origin of Carriers Interacting with Surface States

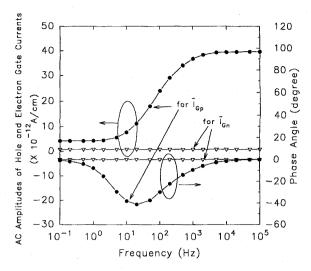

To clarify the origin of the carriers interacting with the surface hole traps, the AC amplitudes and the phase angles of the electron and hole currents flowing into gate electrode are shown in Fig. 5. The AC electron gate current,  $\tilde{I}_{Gn}$ , is negligible compared to that of AC hole current and its phase

Fig. 4. Three dimensional plots for the real part of AC free electron concentration at (a)  $f=0.1~{\rm Hz}$ , and (b)  $f=10~{\rm kHz}$ .

angle is near zero from f = 0.1 Hz to f = 100 kHz. For the AC hole gate current,  $\tilde{I}_{Gp}$ , its magnitude increases very slightly before 5 Hz but undergoes a drastic increase between 5 Hz and 1 kHz. After that it saturates at its maximum value at 1 kHz. A dip of phase angle also appears at about 10 Hz. Compared to the other components of the gate conductance, the real part of the AC hole gate current dominates for the frequency range of 0.1 Hz to 100 kHz. In other words, the gate conductance also increases with frequency, which agrees with the measured results of Ozeki et al. [1] and Zylbersztejn [20]. This anomalous frequency dispersion of  $I_{Gp}$ just corresponds to the transconductance dispersion shown in Fig. 2(a). Because of the large recombination rate through the high-density surface states at the ungated surface region, a lot of holes can flow into the surface region by thermionicemssion-diffussion transport and be captured there, causing the large AC hole gate current. The AC hole gate current increases about one order when the frequency increases from 0.1 Hz to 0.1 MHz.

The frequency dependence of the AC surface charge density and surface potential near the gate edge can be well explained by the slow trapping behavior of the surface states and the hole leakage current through the gate electrode. The physical mechanisms during the positive and the negative cycles of AC gate voltage swing, such as the sign of AC hole current and the interaction processes between holes and traps, are opposite to each other. Here only the positive cycle is discussed. The holes are injected from the gate electrode by thermionic-emssion-diffusion transport. The source and the drain hole currents

Fig. 5. Calculated AC amplitudes and phase angles of hole and electron gate currents flowing into the gate electrode.

from f = 0.1 Hz to f = 100 kHz have been calculated, and found to be negligible compared to the gate hole current. Therefore, the injected holes are unable to reach the source contact. They are captured by the surface traps at the ungated region near the gate edge. At low frequencies, the trapping behavior of the surface states can follow the slow AC voltage swing. Consequently the negative surface charge densities are effectively reduced (see Fig. 3(a) for f = 0.1 Hz), causing the AC surface potential to be higher and the AC electric field parallel to the ungated surface to be lower (see Fig. 3(b) for f = 0.1 Hz). At high frequencies, the trapping behavior of the surface states cannot follow the fast AC voltage swing and consequently the negative surface charge densities are less modulated. Therefore, the AC surface potential at the ungated surface is lower and the AC parallel electrical field is larger (see Fig. 3(b) for f = 100 kHz). The increase of the AC electrical field near the gate edge at high frequencies explains why the AC gate hole current increases with the frequencies (see Fig. 5). The number of injected holes through the gate is approximately proportional to the product of the AC hole gate current and the period time of the AC gate voltage swing, i.e.,  $\tilde{I}_{Gp} \times 1/f$ . Because  $\tilde{I}_{Gp}$  increases slowly with the frequency (see Fig. 5, for six orders of magnitude increase in frequency there is only 10 times increase in  $I_{Gp}$ ), the number of injected holes through the gate is approximately inversely proportional to the frequency. At high frequencies, less holes are injected and captured by the surface traps at the ungated surface near the gate edge. Therefore, the modulation of the surface potential is negligibly affected by the injected holes.

# IV. GATE BIAS AND GATE LENGTH EFFECTS

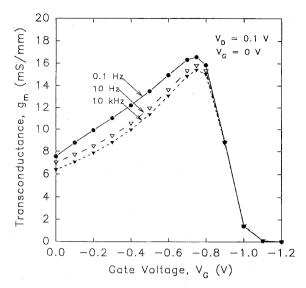

Experimentally, the magnitude of the transconductance dispersion in MESFET's and JFET's strongly depends on DC gate bias and gate length [4], [5], [7]. To confirm the validity of our numerical model, we also apply our model to study the transconductance dispersion with different DC gate biases and gate length. The transconductance versus the DC gate

Fig. 6. Calculated normalized shift of transconductance versus gate voltage as a function of frequency. The frequencies are 0.1 Hz, 10 Hz and 10 kHz.

voltage at f=0.1 Hz, 10 Hz and 10 kHz is shown in Fig. 6. Evidently, the dispersion is noticeable near  $V_{\rm GS}=0$  V and negligible near pinch off ( $\cong$ -1 V). Our results agree with Wallis's [4] and Blight's [5]. At pinch-off, the channel beneath the gate is almost depleted, so the channel width can not be effectively modulated by the AC gate voltage and the transconductance is very small. Although the two parasitic resistances at the ungated region are frequency-dependent, they cannot cause any significant transconductance dispersion.

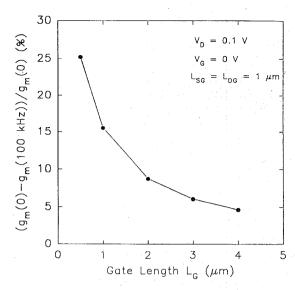

Fig. 7 shows the  $g_m$  dispersion versus gate length. The  $L_{\rm GS}$  and the  $L_{\rm GD}$  are 1  $\mu{\rm m}$  for all calculation. The normalized shift of transconductance decreases monotonically with an increase in the gate length. Our calculated results agree with Wallis's [4] and Kawasaki's [7]. This dependence of  $g_m$  on gate length can be explained by the ratio of the modulated length of surface region (see Fig. 3(a) and (b)) to the gate length. As the gate length increases, the ratio becomes smaller, so the modulation of surface charge has less influence on the transconductance.

# V. CONCLUSION

The frequency dispersion of the small-signal transconductance for GaAs MESFET's is analyzed using 2-D numerical simulation. It is confirmed that the bulk traps beneath the n channel are not responsible for the dispersion. The surface traps at the ungated surface are the cause of this phenomenon. We have also found that the dominating surface traps are hole traps. The calculated results agree with experimental findings which show higher transconductances at lower frequencies and a dip in the phase angle at the transition frequency. This result can be explained by the frequency-dependent modulation of the gate-to-source and the gate-to-drain resistances caused by the slow behavior of the charge exchange via the surface states at the ungated surface region near the gate edge. At positive cycle of AC gate voltage, holes can inject into the

Fig. 7. Calculated normalized shift of transconductance versus gate length. Both the gate-to-source and the gate-to-drain distances are 1  $\mu$ m.

surface region from the gate electrode by thermionic-diffusionemission transport. Due to frequency-dependent potential at the ungated region near the gate edge, the AC hole gate current also exhibits frequency dispersion behavior corresponding to the transconductance dispersion. Gate bias and gate length effects on the transconductance dispersion are also considered. Agreement with reported measurements is obtained.

#### REFERENCES

M. Ozeki, K. Kodama, and A. Shibatomi, "Surface analysis in GaAs MESFET's by g<sub>rn</sub> frequency dispersion measurement," in *Int. Symp. GaAs and Related Compounds*, Japan, 1981, pp. 323–328.

[2] A. Zylbersztejn, G. Bert, and G. Nuzillat, "Hole traps and their effects in GaAs MESFET's," Inst. Phys. Conf. Ser., no. 45, Chap. 4, pp. 315–325.

[3] M. Rocchi, "Status of the surface and bulk parasitic effects limiting the performances of GaAs IC's," *Physica*, vol. 129B, pp. 119–138, 1985.

[4] R. H. Wallis, A. Faucher, D. Pons, and P. R. Jay, "Surface and bulk traps in GaAs MESFET's," Inst. Phys. Conf. Ser., 1985, no. 74, pp. 287–292.

[5] S. R. Blight, R. H. Wallis, and H. Thomas, "Surface influence on the conductance DLTS spectra of GaAs MESFET's," *IEEE Trans. Electron Devices*, vol. ED-33, no. 10, pp. 1447–1453, 1986.

[6] P. H. Ladbrooke and S. R. Blight, "Low-field low-frequency dispersion of transconductance in GaAs MESFET's with implications for other rate-dependent anomalies," *IEEE Trans. Electron Devices*, vol. 35, no. 3, pp. 257-267, 1988.

[7] H. Kawasaki and J. Kasahara, "Low-frequency dispersion of transconductance in GaAs JFET's and MESFET's with an ion-implanted channel layer," *IEEE Trans. Electron Devices*, vol. 37, no. 8, pp. 1789–1795, 1990

[8] P. H. Ladbrooke, MMIC Design: GaAs FET's and HEMTs. Norwood, MA: Artech, 1989, ch. 6.

[9] Z. Kachwalla, "Characterizing traps in MESFET's using internal transconductance  $(g_m)$  frequency dispersion," *Solid-State Electron.*, vol. 31, no. 8, pp. 1315–1320, 1988.

[10] J. H. Zhao, R. Hwang, and S. Chang, "On the characterization of surface states and deep traps in GaAs MESFET's," *Solid-State Electron.*, vol. 36, no. 12, pp. 1665–1672, 1993.

[11] D. E. Holmes, R. T. Chen, K. R. Elliott, C. G. Kirkpatrick, and P. W. Yu, "Compensation mechanism in liquid encapsulated Czochralski GaAs: Importance of melt stoichiometry," *IEEE Trans. Electron Devices*, vol. ED-29, pp. 1045–1051, 1982.

[12] U. Kaufmann, J. Windscheif, M. Baeumler, J. Schneider and F. Kohl, "Concentration and thermal stability of AsGa in GaAs: Correlation with EL2," in *Proc. 3rd Semi-Insulating III-V Materials Conf.*, 1984, pp. 246–251.

- [13] S. Makram-Ebeid, P. Langlade, and G. M. Martin, "Nature of EL2: The main native midgap electron trap in VPE and bulk GaAs," in *Proc. 3rd Semi-Insulating III-V Materials Conf.*, 1984, pp. 222–230.

- [14] G. M. Martin, A. Mitonneau, D. Pons, A. Mircea, and D. W. Woodard, "Detailed electrical characterisation of the deep Cr acceptor in GaAs," J. Phys. C., vol. 13, pp. 3855–3882, 1980.

- [15] W. E. Spicer, P. W. Chye, P. R. Skeath, C. Y. Su, and I. Lindau, "New and unified model for Schottky barrier and III-V insulator interface states formation," J. Vac. Sci. Technol., vol. 16, no. 5, pp. 1422–1433, 1979.

- [16] S. H. Lo and C. P. Lee, "Analysis of surface state effect on gate lag phenomena in GaAs MESFET's," *IEEE Trans. Electron Devices*, vol. 41, no. 9, pp. 1504–1512, 1994.

[17] J. Y. F. Tang and J. L. Freeouf, "Nonuniform surface potential and their

- [17] J. Y. F. Tang and J. L. Freeouf, "Nonuniform surface potential and their observation by surface sensitive techniques," J. Vac. Sci. Technol., vol. B2, no. 3, pp. 459–464, 1984.

- [18] J. P. Harrang, A. Tardella, M. Rosso, and P. Alnot, "Conductance transient spectroscopy of metal-semiconductor field effect transistors," J. Appl. Phys., vol. 6, no. 5, pp. 1931–1936, 1987.

- J. Appl. Phys., vol. 6, no. 5, pp. 1931–1936, 1987.

[19] S. E. Laux, "Techniques for small-signal analysis of semiconductor devices," *IEEE Trans. Electron Devices*, vol. 32, no. 10, pp. 2028–2037, 1985.

- [20] A. Zylbersztejn, "The effects of deep levels in GaAs MESFET's," Physica, vol. 117B and 118B, pp. 44-49, 1983.

Shih-Hsien Lo was born in Taiwan, R.O.C., in 1964. He received the B.S. degree in electrical engineering from the National Cheng-Kung University in 1986, and the M.S. and Ph.D. degrees in electronics engineering from the National Chiao-Tung University in 1988 and 1991, respectively.

After serving two years in the military, he joined the National Nano Device Laboratory as an associate researcher in 1993. In 1995, he did his Postdoctoral research in the Exploratory Devices and Circuits Group of the Silicon Technology De-

partment at IBM's Thomas J. Watson Research Center. His research interests are in the areas of thin oxide reliability characterization, and numerical modeling and electrical characterization of Si- and GaAs-based small geometry devices

Chien-Ping Lee (M'80-SM'94) received the B.S. degree in physics from the National Taiwan University in 1971, and the Ph.D. degree in applied physics from the California Institute of Technology, Pasadena, in 1978. While at Caltech, he worked on GaAs-based integrated optics. He was credited with the design and fabrication of several important optoelectronic components, including the first integrated optoelectronic circuit, which consists of a laser and a Gunn device fabricated on a same substrate.

After graduation, he joined Bell Laboratories, where he worked on integrated optics and semiconductor lasers. He joined Rockwell International in 1979 and worked on GaAs integrated circuits. He did extensive work on substrate related effects such as the orientation effect and the backgating effect. In 1987, he joined National Chiao-Tung University, Taiwan, as professor and director of the semiconductor research center. In 1990, he went back to Rockwell, where he was manager of the advanced device concept department. He came back to Taiwan in 1992 and is currently professor in the Institute of Electronics, National Chiao-Tung University. His research interests are in the areas of III-V optoelectronic devices, MBE technology, GaAs IC's, heterostructure devices and physics, and device simulation.

Dr. Lee received the Engineer of the Year award in 1982 for his contribution in GaAs IC and HEMT technologies, the best teacher award from the Ministry of Education in 1993, and the outstanding research award from National Science Council in 1994.