# Suppression of the Boron Penetration Induced Dielectric Degradation by Using a Stacked-Amorphous-Silicon Film as the Gate Structure for pMOSFET

Shye Lin Wu, Member, IEEE, Chung Len Lee, Senior Member, IEEE, and Tan Fu Lei

Abstract— This work proposes a stacked-amorphous-silicon (SAS) film as the gate structure of the  $p^+$  poly-Si gate pMOSFET to suppress boron penetration into the thin gate oxide. Due to the stacked structure, a large amount of boron and fluorine piled up at the stacked-Si layer boundaries and at the poly-Si/SiO<sub>2</sub> interface during the annealing process, thus the penetration of boron and fluorine into the thin gate oxide is greatly reduced. Although the grain size of the SAS film is smaller than that of the as deposited polysilicon (ADP) film, the boron penetration can be suppressed even when the annealing temperature is higher than 950°C. In addition, the mobile ion contamination can be significantly reduced by using this SAS gate structure. This results in the SAS gate capacitor having a smaller flat-band voltage shift, a less charge trapping and interface state generation rate, and a larger charge-to-breakdown than the ADP gate capacitor. Also the Si/SiO<sub>2</sub> interface of the  $p^+$  SAS gate capacitor is much smoother than that of the  $p^+$  SAS gate capacitor.

### I. INTRODUCTION

**R**ECENTLY,  $p^+$  polycrystalline silicon (poly-Si) has been widely used as the gate material of pMOSFET to eliminate the short-channel effects [1]–[3]. In addition to the reliable process control for subthreshold characteristics and the threshold voltage adjustment, the  $p^+$  poly-Si gate pMOSFET is also more resistant to the hot carrier induced instability than is the  $n^+$  poly-Si gate pMOSFET [4].

The BF<sub>2</sub> implantation is typically used to form the  $p^+$  poly-Si gate as well as the shallow  $p^+$ -n junction [5]. Unfortunately, the F-incorporated  $p^+$  poly-Si gate can not only enhance the boron penetration through the thin gate oxide into the Si substrate but also cause the generation of negative-charge interface states [5]–[8]. This results in a large threshold voltage shift, a large charge trapping rate and a poor reliability of device [5]–[8]. It has also indicated that the more fluorine atoms pile up at the poly-Si/SiO<sub>2</sub> and Si/SiO<sub>2</sub> interfaces, the more serious the boron penetration occurs [9]. Moreover, the  $p^+$  poly-Si gate MOS devices are more susceptible to

Manuscript received July 11, 1994; revised July 12, 1995. The review of this paper was arranged by Associate Editor G. W. Neudeck. This work was supported by the National Science Council of R.O.C. through Research Contract NSC 82-0404-E009-190.

S. L. Wu is with the Vanguard International Semiconductor Corporation, Hsinchu 300, Taiwan, R.O.C.

C. L. Lee and T. F. Lei are with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, R.O.C.

Publisher Item Identifier S 0018-9383(96)01098-2.

the mobile ion contamination than are the  $n^+$  poly-Si gate MOS devices [10]. To avoid the boron penetration effect and simultaneously to form a shallow  $p^+$ -n junction, the post-implantation annealing must be performed at a lower temperature, e.g. 850°C, for a short time [11]. However, under such a thermal cycle, it is difficult to sufficiently activate the dopant to degenerate the poly-Si film, especially as a silicide is formed on the poly-Si film [12], [13]. This will cause a depletion effect in the poly-Si film and result in a significant degradation in the device performance [11]-[13].

Recently, it has been reported that the boron penetration effects can be suppressed by using a stacked-amorphoussilicon (SAS) film as the gate structure for pMOSFET [14]. Due to the stacked structure, a large amount of dopants segregate at stacked-Si layer boundaries and at poly-Si/SiO<sub>2</sub> interface during the annealing process [14]-[16]. Although the grain size of the SAS film is smaller than that of the ADP film, the boron penetration size of the SAS film is smaller than that of the ADP film, the boron penetration effects can be exactly suppressed even when the annealing temperature is higher than 950°C [14]. In this paper, the characteristics of the  $p^+$  SAS gate capacitor are systematically investigated in terms of the amount boron and fluorine penetration into the thin gate oxide, the flat-band voltage shift  $(\Delta V_{\rm fb})$ , the dielectric breakdown field  $(E_{\rm bd})$ , the charge trapping rate, the interface state generation rate, and the time dependent dielectric breakdown  $(Q_{\rm bd})$ . A physical model for suppression of the boron and fluorine penetration into the thin gate oxide with the SAS structure is also proposed.

### II. EXPERIMENTAL PROCEDURES

In this study,  $p^+$  poly-Si gate MOS capacitors were fabricated on n-type (100) Si wafers with the resistivity of 5–20  $\Omega$ -cm. After a standard RCA cleaning process, all wafers were dipped in a diluted HF solution (1:50) to remove the native oxide. Then, the thin oxides of 70 Å and 130 Å were grown at 900°C and 950°C in a dry  $O_2$  ambient, respectively. The post-oxidation annealing of all samples were performed at the oxidation temperature for 15 min in an  $N_2$  ambient. An LPCVD  $\alpha$ -Si film with total thickness of about 3 000 Å was subsequently deposited onto the wafers at 550°C in three steps [16]. The deposition pressure and deposition rate were controlled at 140–160 mtorr and 20 Å/min respectively.

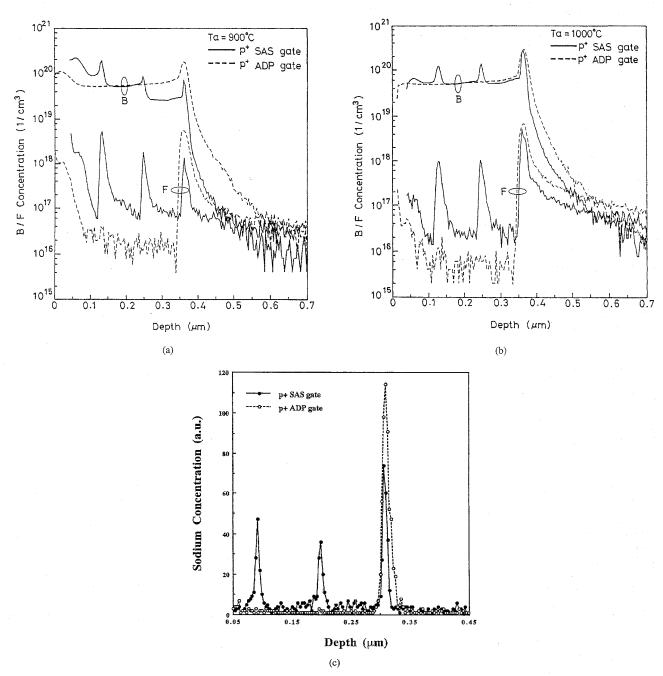

Fig. 1. The SIMS profiles of implanted boron and fluorine of the  $p^+$  SAS and ADP gate capacitors annealed at (a) 900°C and (b) 1000°C, respectively. The initial oxide thickness is 130 Å. (c) The SIMS profiles of sodium ion of the 900°C-annealing  $p^+$  SAS (solid line) and ADP (dashed line) gate capacitors with the gate oxide thickness of 130 Å.

The thickness of each  $\alpha$ -Si layer was about 1000 Å. During the stacked-Si layer deposition, the LPCVD system was not interrupted. After the first  $\alpha$ -Si layer deposition, the SiH<sub>4</sub> gas was removed and replaced by an N<sub>2</sub> gas to purge the LPCVD system for a period of 30 min. By using the same steps, the second and the third  $\alpha$ -Si layers were deposited on the wafers. During this deposition process, a layer boundary existed between two adjacent  $\alpha$ -Si layers [16]. To make a comparison, the ADP film of 3000 Å was deposited at 625°C in one step. The deposition pressure and the deposition rate were 180–220 mtorr and 100 Å/min, respectively. Then, BF<sub>2</sub>

ion implantation was performed at 50 keV with a dose of  $6\times10^{15}~{\rm cm^{-2}}$  and annealed at 800°C for 30 min in a dry  $O_2$  ambient followed by driving-in at 850, 900, 950, and  $1\,000^{\circ}{\rm C}$  for 15 min in an  $N_2$  ambient. After aluminum metallization, all samples were sintered at 400°C for 20 min in an  $N_2$  ambient to form a good ohmic contact.

The I-V characteristics and the time-dependent-dielectric-breakdown (TDDB) characteristics of the  $p^+$  poly-Si gate capacitors were measured by using an HP4145B semiconductor parameter analyzer. A constant Fowler-Nordheim (FN) tunneling current stressing was used to study reliability of

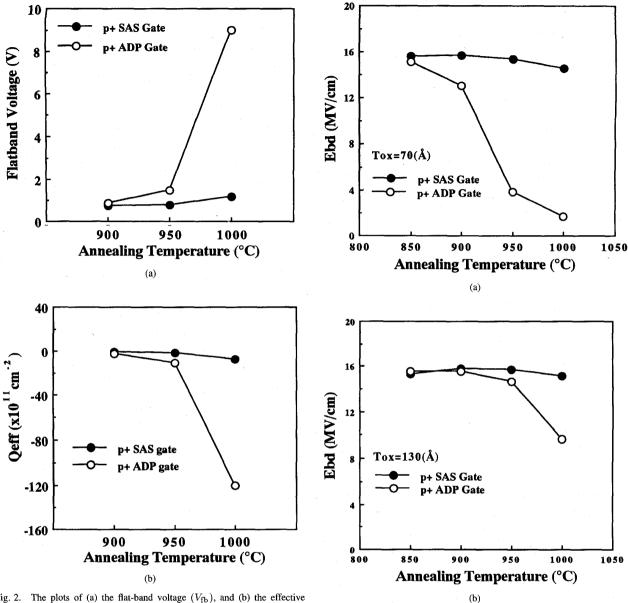

Fig. 2. The plots of (a) the flat-band voltage  $(V_{\rm fb})$ , and (b) the effective oxide charge  $(Q_{\rm eff})$  versus the annealing temperature from 900°C to 1000°C for both the  $p^+$  SAS and ADP gate capacitors with the oxide thickness of 130 Å, respectively.  $Q_{\rm eff}$  is equal to  $C_{\rm ox}(\phi$  ms- $V_{\rm fb}$ ), and  $\phi$  ms is the work function difference between the poly-Si gate and Si substrate.

$_{\rm x}$  ( $\phi$  ms- $V_{\rm fb}$ ), and  $\phi$  ms is the work gate and Si substrate. ing temperature for  $p^+$  SAS and ADP gate capacitors with the initial oxide thickness of (a) 70 Å, and (b) 130 Å, respectively.

the thin oxide capacitors. The oxide thickness and the flatband voltage shift of the  $p^+$  poly-Si capacitors before and after a constant current stressing were monitored by the high-frequency C-V (HFCV) measurements by using the Keithley 590/595 C-V analyzer. The impurity profiles were analyzed by using a VG Ionex SIMS tool with an  $O_2^+$  beam for boron, fluorine and sodium analyses.

### III. RESULTS AND DISCUSSION

### A. SIMS Profiles of the $p^+$ SAS and ADP Gate Capacitors

Fig. 1(a) and (b) compare the SIMS profiles of implanted boron and fluorine of the  $p^+$  SAS and ADP gate capacitors

annealed at 900°C and 1000°C, respectively. Fig. 1(c) shows the sodium profiles of the 900°C annealing  $p^+$  SAS (solid line) and ADP (dashed line) gate capacitors, respectively. For these capacitors, the initial thickness of the gate oxide was about 130 Å. It is seen that the  $p^+$  SAS gate capacitors exhibit three boron and fluorine segregation peaks at the stacked-Si layer boundaries and at the poly-Si/SiO<sub>2</sub> interface, while for the  $p^+$  ADP gate capacitors, there exists only one peak at the poly-Si/SiO<sub>2</sub> interface. The dopant segregation of the  $p^+$  SAS gate capacitors are similar to that of the SAS and SPS (stacked-polycrystalline-silicon) emitter contacted  $p^+$ -n shallow junction diodes [15]. For the  $p^+$  SAS gate capacitors, due to the dopant segregation at the stacked-Si/SiO<sub>2</sub> interface

Fig. 3. The plots of the dielectric breakdown field  $(E_{\rm bd})$  versus the anneal-

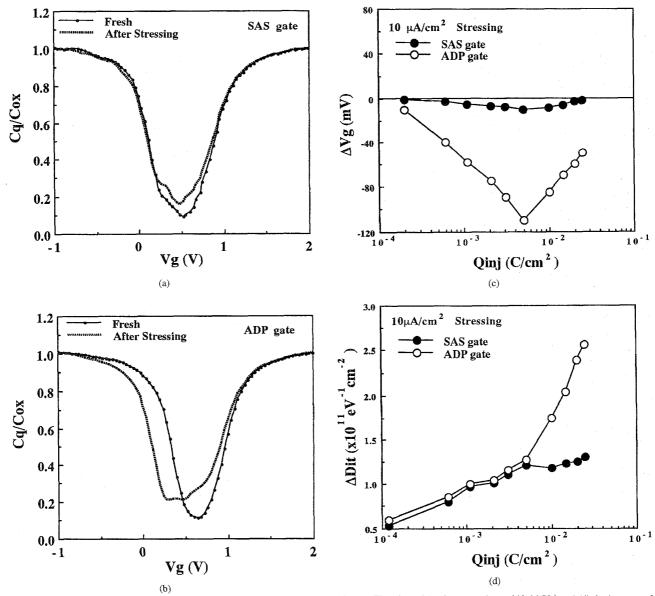

Fig. 4. The quasistatic C-V characteristics of (a) the  $p^+$  SAS gate capacitor and (b) the  $p^+$  ADP gate capacitor before and after a constant current of 10  $\mu$ A/cm<sup>2</sup> stressing for 2000 s, respectively. The initial gate oxide thickness is 130 Å and the dopant is driven-in at 900°C.

Fig. 4. The plots of (c) the gate voltage shift  $(\Delta V_g)$  and (d) the increase of interface state density  $(\Delta D_{\rm it})$  versus the injection charge  $(Q_{\rm inj})$  of the  $p^+$  SAS gate capacitor and the  $p^+$  ADP gate capacitor, respectively.

are less than that of the  $p^+$  ADP gate capacitors. This in turn causes the boron and fuorine penetration through the thin gate oxide into the Si substrate for the  $p^+$  SAS gate capacitors to be less than that of the  $p^+$  ADP gate capacitor. In addition, the mobile ion contamination can be significantly reduced by using the SAS gate structure, as shown in Fig. 1(c).

# B. Electrical Characteristics of the $p^+$ SAS and ADP Gate Capacitors

As shown in Fig. 1(a) and (b), the amount of boron and fluorine penetration through the thin gate oxide into the Si substrate of the  $p^+$  SAS gate capacitor is less than that of the

$p^+$  ADP gate capacitor even when the annealing temperature of the  $p^+$  SAS gate capacitor is higher. This results in a significant improvement of the flat-band voltage shift, the effective oxide charge, the dielectric breakdown field, the charge trapping rate, the interface state generation rate, and the charge-to-breakdown  $(Q_{\rm bd})$ . This will be discussed in the following

Fig. 2(a) and (b) show the plots of the flat-band voltage and the effective oxide charge versus the annealing temperature from 900°C to 1000°C for both the  $p^+$  SAS and ADP gate capacitors, respectively.  $Q_{\rm eff}$  is equal to  $C_{\rm ox}(\phi \ {\rm ms}{-}V_{\rm fb})$ , and  $\phi$  ms is work function difference between the poly-Si gate and the Si substrate [17], [18]. Due to the suppression of the boron and fluorine penetration into the thin gate oxide, the

oxide thickness is 70 Å.

increasse in flat-band voltage with the annealing temperature can be significantly reduced [5]-[9]. As shown in Fig. 2(a), the  $V_{\mathrm{fb}}$  values of the  $p^+$  SAS gate capacitors annealed at 900°C, 950°C and 1000°C are 0.73 V, 0.78 V and 1.18 V, respectively, while those of the  $p^+$  ADP gate capacitors are 0.86 V, 1.46 V and 9.01 V, respectively. Also the boron penetration induced negative oxide charge generation can be reduced [7], [18], as shown in Fig. 2(b), the  $Q_{\rm eff}$  values of the  $p^+$  SAS gate capacitors are  $-5.3 \times 10^{10}$  C/cm<sup>2</sup>,  $-1.3 \times 10^{11}$  $C/cm^2$  and  $-7.5 \times 10^{11}$   $C/cm^2$  for the annealing temperature of 900°C, 950°C and 1000°C, respectively, while those of the  $p^+$  ADP gate capacitors are  $-2.2 \times 10^{11}$  C/cm<sup>2</sup>,  $-1.1 \times 10^{12}$  $\text{C/cm}^2$  and  $-1.2 \times 10^{13}$   $\text{C/cm}^2$ , respectively.

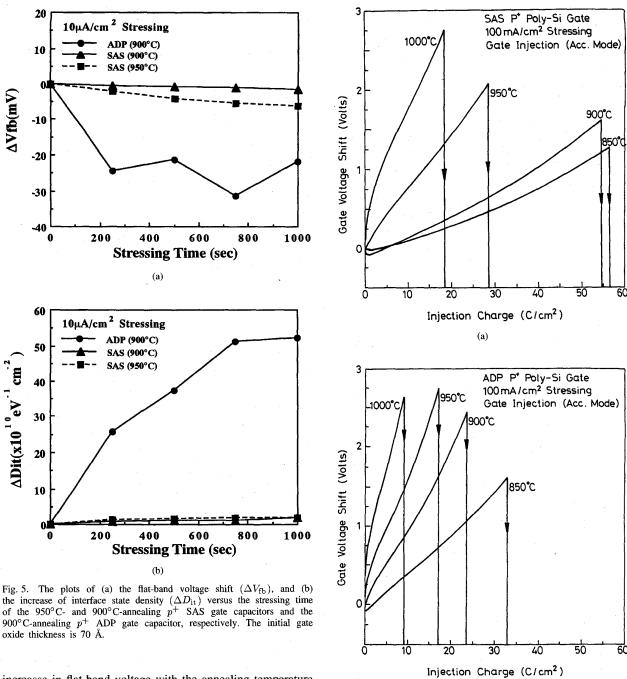

Fig. 6. The curves of gate voltage shift versus the injected charge of (a) the SAS gate capacitors and (b) the  $p^+$  ADP gate capacitors, respectively. The initial gate oxide thickness is about 130 Å and the annealing temperature is from 850°C to 1000°C and the injection current density is 100 mA/cm<sup>2</sup> in the positive gate bias.

The dielectric breakdown field  $(E_{\rm bd})$  is determined by the flat-band voltage  $(V_{\rm fb})$  and the oxide thickness  $(T_{\rm ox})$ , i.e.,  $E_{\mathrm{bd}} = (V_g - V_{\mathrm{fb}})/T_{\mathrm{ox}}$ , where  $V_g$  is the applied gate voltage [19]. Thus, the boron and fluorine penetration induced the increase of the  $V_{\rm fb}$  and  $T_{\rm ox}$  values will cause a reduction in the

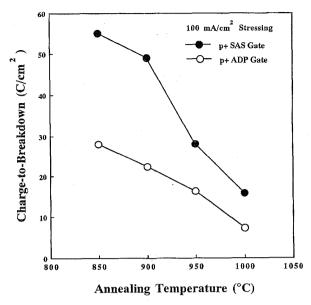

Fig. 7. The plots of the charge-to-breakdown  $(Q_{\rm bd})$  versus the annealing temperature of the  $p^+$  SAS and ADP gate capacitors with the initial oxide thickness of 130 Å. The stressing current density is 100 mA/cm<sup>2</sup> in the positive gate bias.

dielectric breakdown field [5], [15]. Fig. 3(a) and (b) show the plots of the  $E_{\rm bd}$  value versus the annealing temperature for the  $p^+$  SAS and ADP gate capacitors with the oxide thickness of 70 Å and 130 Å, respectively. It is seen that the dielectric breakdwon field of the  $p^+$  SAS gate capacitors are nearly independent of the annealing temperature and the  $E_{\rm bd}$  value of all capacitors are large than 15 MV/cm, which is very lose to the  $E_{\rm bd}$  value of the  $n^+$  poly-Si gate capacitor. However, the  $p^+$  ADP gate capacitors, the  $E_{\rm bd}$  value decreases drastically with the increase of the annealing temperature.

Fig. 4(a) and (b) show the quasistatic C-V (OSCV) characteristics of the 900°C annealing  $p^+$  SAS and ADP gate capacitors with the oxide thickness of about 130 Å before and after a constant current stressing, respectively. Fig. 4(c) and (d) show the curves of the gate voltage shift  $(\Delta V_a)$  and the interface state generation ( $\Delta D_{it}$ ) versus the injection charge of the  $p^+$  SAS and ADP gate capacitors, respectively. In this study, the injection current density was kept at a low level of 10  $\mu$ A/cm<sup>2</sup> to reduce injection-induced electron-trap generation [20]. The area of the capacitor was  $1.16 \times 10^{-3}$ cm<sup>2</sup> and electrons were injected from the Si substrate into the thin gate oxide (in the accumulation mode). It is seen that both capacitors exhibit a positive charge (hole) trapping behavior from the negative  $V_{\rm fb}$  shift, as shown in Fig. 4(a) and (b), and the decrease in  $\Delta V_g$ , as shown in Fig. 4(c). However, the amount of trapped holes of the SAS gate capacitor is much less than that of the ADP gate capacitor. Also, the SAS gate capacitor shows a smaller interface state generation rate, as shown in Fig. 4(d). The reduction in the hole trapping rate and the interface state generation rate for the  $p^+$  SAS gate capacitor is believed due to the suppression of the boron and fluorine penetration into the thin gate oxide [9], [13]. It had been reported that the boron-fluorine complex remaining within the oxide bulk would produce negative charge states at or near the Si/SiO<sub>2</sub> interface [5]-[9]. Although the  $V_{\rm fb}$  values of the 900°C-annealing p+ SAS and ADP gate capacitors derived form C-V curve are 0.73 and 0.86 V, respectively, which indicate that the boron penetration effect for both capacitors can be negligible [6], [11]. However, from the SIMS profiles, the amount of boron and fluorine penetration into the thin gate oxide of the ADP gate capacitor is much larger than that of the SAS gate capacitor. This is the reason that the SAS gate capacitor has a smaller hole trapping rate and interface generation rate than does the ADP gate capacitor [5]-[8]. For the capacitor with an ultra-thin oxide of 70 Å, the boron and fluorine penetration induced hole trapping and interface state generation rate become much more serious. As shown in Fig. 5(a) and (b), the hole trapping rate (negative increase in  $V_{\rm fb}$  value) and the interface state generation rate of the 900°Cannealing p+ ADP gate capacitor under a constant current of 10  $\mu$ A/cm<sup>2</sup> stressing are much larger than those of the 900°C- and 950°C-annealing  $p^+$  SAS gate capacitors. This is believed to be due to much larger amount of boron and fluorine penetration into the ultra-thin oxide of the 900°C-annealing  $p^+$ ADP gate capacitor than into the ultra-thin oxide of the 900°Cor even 950°C-annealing  $p^+$  SAS gate capacitors [13].

In addition to the suppression of the hole trapping and the interface state generation, the electron trapping rate and the charge-to-breakdown  $(Q_{bd})$  are also significantly improved for the  $p^+$  SAS gate structure. Fig. 6(a) and (b) show the curves of the gate voltage shift versus the injection charge of the  $p^+$  SAS and ADP gate capacitors with the oxide thickness of 130 Å annealed at the temperature from 850°C to 1000°C, respectively. Fig. 7 shows the plots of the mean value of  $Q_{\rm bd}$ (more than ten devices) versus the annealing temperature of the  $p^+$  SAS and ADP gate capacitors with the oxide thinkness of 130 Å. The stressing current density was 100 mA/cm<sup>2</sup> and the injection polarity was in the accumulation mode. It is seen that the electron trapping rate increases with the annealing temperature for both type  $p^+$  poly-Si gate capacitors, while the  $Q_{\rm bd}$  values decrease with the increase of the annealing temperature. This is due to the higher temperature annealing resulting in a larger amount of boron and fluorine penetration through the thin gate oxide into the Si substrate [5], [6], [9]. Nevertheless, at the same annealing temperature, the gate voltage shift of the  $p^+$  SAS gate capacitors are much less than that of the  $p^+$  ADP gate capacitors. Also, the  $Q_{\rm bd}$  value of the  $p^+$  SAS gate capacitors are about a factor of two larger than that of the  $p^+$  ADP gate capacitors. It is interesting to note that the 950°C-annealing  $p^+$  SAS gate capacitor has a less electron trapping rate and a larger  $Q_{\rm bd}$  value than the 900°C-annealing  $p^+$  ADP gate capacitor. This is due to the fact that the amount of boron and fluorine penetration into the thin gate oxide of the 950°C-annealing  $p^+$  SAS gate capacitor is still less than that of 900°C-annealing  $p^+$  ADP gate capacitor (see [14]).

## IV. PHYSICAL MODEL

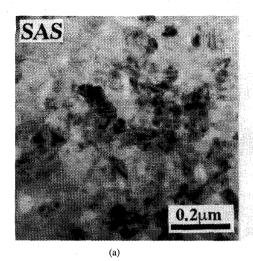

Since the stacked-Si layer boundaries limited the growth of the grain size [21], the final grain size of the SAS gate is smaller than that of the ADP gate, as shown in Fig. 8(a) and

Fig. 8. The plan-view of the TEM micrographs of (a) the  $p^+$  SAS gate structure, and (b) the  $p^+$  ADP gate structure, respectively. The dopant driven-in was performed at  $1000^{\circ}$ C. It is seen that the grain size of the SAS gate is smaller than that of the ADP gate.

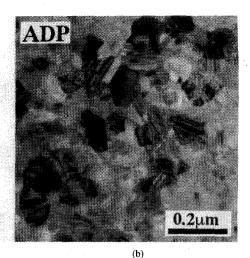

SAS gate structure

Fig. 9. The physical model of boron and fluorine diffusion in (a) the SAS gate, and (b) the ADP gate, respectively. Assume the grain structure is block-like.

(b)

n-Si

(b). Hence, for the  $p^+$  SAS gate structure, the suppression of the boron and fluorine penetration into the thin gate oxide was not caused by the grain size effect [9]. As mentioned above, for the  $p^+$  SAS gate capacitors, due to the dopant segregation at the stacked-Si layer boundaries, the amount of boron and fluorine available for diffusion to the poly-Si/SiO<sub>2</sub> interface

are less than that of the  $p^+$  ADP gate capacitors. Moreover, due to the stacked-Si structure, the total path for boron and fluorine diffusion to the poly-Si/SiO<sub>2</sub> interface becomes longer than the ADP gate, as shown in Fig. 9 (assume the grain structure is block-like). Thus, for the SAS gate structure, the suppression of boron and fluorine penetration through the thin gate oxide into the Si substrate is believed to be due to the dopant segregation at the the stacked-Si layer boundaries and the longer path for dopant diffusion to the poly-Si/SiO<sub>2</sub> interface. It is worthy noting that due to the suppression of boron and fluorine penetration through the thin gate oxide into the Si substrate, the Si/SiO<sub>2</sub> interface of the  $p^+$  SAS gate structure is atomically flat, while that of the  $p^+$  ADP gate structure is relatively rough [14], [22].

### V. CONCLUSION

In this paper, we propose a stacked-amorphous-silicon (SAS) structure as the gate material for pMOSFET to suppress the boron penetration effect. Although the grain size of the SAS film is smaller than that of the ADP film, the boron and fluorine penetration-induced device degradation can be reduced even though the annealing temperature is higher than 950°C. The amount of the boron and fluorine penetration through the thin gate oxide into the Si substrate of the  $p^+$  SAS gate capacitor is less than that of the  $p^+$  ADP gate capacitor, even the annealing temperature of the  $p^+$  SAS gate capacitor is higher. Besides, the mobile ion (Na<sup>+</sup>) contamination can be reduced by using the SAS gate structure. Since the suppression of boron and fluorine penetration into the thin gate oxide, the  $p^+$  SAS gate capacitor has a smaller flat-band voltage shift, a less charge trapping rate, a less interface state generation rate, and a larger  $Q_{\rm bd}$  value than does the  $p^+$  ADP gate capacitor. Also the Si/SiO<sub>2</sub> interface of the  $p^+$  SAS gate capacitor is much smoother than that of the  $p^+$  SAS gate capacitor [14], [21]. The mechanism of the suppression of boron and fluorine penetration effect by using the SAS gate structure is believed to be due to the dopant segregation at the stacked-Si layer boundaries and a longer path for dopant diffusion to the poly-Si/SiO2 interface.

### ACKNOWLEDGMENT

The authors thank C. S. Lai for assistance of some samples preparation and J. F. Chen for TEM micrographs and H. C. Chang for SIMS analysis.

#### REFERENCES

- [1] G. J. Hu and R. H. Bruce, "Design tradeoffs between surface and buriedchannel FET's," IEEE Trans. Electron Devices, vol. ED-32, p. 584, 1985

- [2] J. Y.-C. Sun, Y. Taur, F. H. Dennard, and S. P. Klepner, "Submicrometer-channel CMOS for low-temperature operation,"

- IEEE Trans. Electron Devices, vol. ED-34, p. 19, 1987.

[3] M. P. Brassington and R. R. Razouk, "The relationship between gate bias and hot-carrier-induced instabilities in buried- and surface-channel PMOSFET's," IEEE Trans. Electron Devices, vol. ED-35, p. 726, 1986.

- [4] I. Kato, H. Horie, K. Oikawa, and M. Taguchi, "Distribution of trapped charges in  $SiO_2$  film of a  $p^+$ -gate PMOS structure," IEEE Trans. Electron Devices, vol. 38, p. 1334, 1991.

[5] F. K. Baker, J. R. Pfiester, T. C. Melem, H. H. Tseng, P. J. Tobin,

- J. D. Hayden, C. D. Gunderson, and L. C. Parrillo, "The influence of fluorine on threshold voltage instabilities in  $p^+$ -polysilicon gated p-channel MOSFET's," *IEDM Tech. Dig.*, vol. 443, 1989.

[6] J. M. Sung and C. Y. Lu, "A comprehensive study on p<sup>+</sup> polysilicon-

- gate MOSFET's instability with fluorine incorporation," IEEE Trans.

- Electron Devices, vol. 37, p. 2312, 1990. C. Y. Lu and J. M. Sung, "Negative charge induced degradation of PMOSFET's with BF<sub>2</sub>-implanted  $p^+$ -poly gate," Electron. Lett., vol. 25, p. 1685, 1989.

- [8] G. Q. Lo, D. L. Kwong, and S. Lee, "Anomalous capacitance-voltage characteristics of BF2-implanted and rapid thermal annealed p+ polycrystalline silicon gate metal-oxide-semiconductor structures," Appl. Phy. Lett., vol. 57, p. 2573, 1990.

- [9] H. H. Tseng, M. Orlowski, P. J. Tobin, and R. L. Hance, "Fluorine diffusion on a polysilicon grain boundary network in relation to boron penetration from  $p^+$  gates," IEEE Electron Device Lett., vol. 13, p. 14,

- [10] H. Tanaka, I. Aikawa, and T. Ajioka, "Behavior of Na+ ions in p+ polysilicon gates," *Tech. Dig. Symp. VLSI Technol.*, p. 55, 1988. [11] C. Y. Wong, J. Y.-C. Sun, Y. Taur, C. S. Oh, R. Angelucci, and

- B. Davari, "Doping of  $n^+$  and  $p^+$  polysilicon in a dual-gate CMOS process," *IEDM Tech. Dig.*, p. 238, 1988.

[12] C. Y. Lu, J. M. Sung, H. C. Kirsch, S. J. Hillenius, T. E. Smith, and

- L. Manchanda, "Anomalous C-V characteristics of implanted poly MOS

- structure in  $n^+/p^+$  dual-gate CMOS technology," IEEE Electron Device

- Lett., vol. 10, p. 192, 1989.

[13] H. Hayashida, Y. Toyoshima, Y. Suizu, K. Mitsuhashi, H. Iwai, and K. Maeguchi, "Dopant redistribution in dual gate W-polycide CMOS and its improvement by RTA," in Tech. Dig. Symp. VLSI Technol., 1989, p.

- [14] S. L. Wu, C. L. Lee, and T. F. Lei, "Suppression of boron penetration into an ultra-thin gate oxide (<7 nm) by using a stacked-amorphoussilicon (SAS) film," *IEDM Tech. Dig.*, p. 329, 1993.

[15] S. L. Wu, C. L. Lee, and T. F. Lei, "Characterization of polysilicon

- contacted shallow junction diode formed with a stacked-amorphoussilicon film," IEEE Trans. Electron Devices, vol. 40, p. 1797, 1993.

- [16] S. L. Wu, C. L. Lee, T. F. Lei, T. L. Lee, and L. J. Chen, "Investigation on the interface of the polycrystalline silicon contacted diode formed with a stacked amorphous silicon film," J. Electron. Material, vol. 21, 811, 1992

- [17] N. Lifshitz, "Dependence of the work-function difference between the polysilicon gate and silicon substrate on the doping level in polysilicon,' IEEE Trans. Electron Devices, vol. ED-32, p. 617, 1985.

- [18] H. Fang, K. S. Krisch, B. J. Gross, C. G. Sodini, J. Chung, and D. A. Antoniadis, "Low-temperature furnace-grown reoxidized nitrided oxide gate dielectrics as a barrier to boron penetration," IEEE Electron Device Lett., vol. 13, p. 217, 1992.

- [19] S. M. Sze, Physics of Semiconductor Devices, 2nd ed. New York:

- Wiley, 1981.

[20] M. S. Liang, C. Chang, Y. T. Yeow, C. Hu, and R. W. Brodersen, "MOSFET degradation due to stressing of thin oxide," IEEE Trans. Electron Devices, vol. ED-31, pp. 1238, 1984.

- T. Kamins, Polycrystalline Silicon for Integrated Circuit Applications. Boston: Kluwer Academic, 1988.

- S. L. Wu, C. L. Lee, T. F. Lei, J. F. Chen, and L. J. Chen, "Suppression of the boron penetration induced Si/SiO2 interface degradation by using a stacked-amorphous-silicon film as athe gate structure for pMOSFET, IEEE Electron Device Lett., vol. 15, p. 160, 1994.

Shye Lin Wu, (S'90-M'92) for a photograph and biography, see this issue, p. 294.

Chung Len Lee, (S'70-M'75-M'81-M'88-SM'92) for a photograph and biography, see this issue, p. 294.

Tan Fu Lei, for a photograph and biography, see this issue, p. 294.