# Enhanced Temperature Dependence of Phonon-Scattering-Limited Mobility in Compressively Uniaxial Strained pMOSFETs

William Po-Nien Chen, Jack Jyun-Yan Kuo, Student Member, IEEE, and Pin Su, Member, IEEE

Abstract—This paper investigates the temperature dependence of phonon-scattering-limited mobility  $\mu_{\rm PH}$  for advanced short-channel strained pMOS devices. By using the split CV method and Matthiessen's rule, surface-roughness-limited mobility  $\mu_{\rm SR}$  and  $\mu_{\rm PH}$  are successfully decoupled. This paper indicates that the temperature sensitivity of  $\mu_{\rm PH}$  is proportional to  $T^{-1.75}$  for a neutral stressor and becomes higher when compressive strain is applied. It is explained by the higher optical phonon energy induced by uniaxially compressive strain. Our new findings may also explain the previously reported higher temperature sensitivity of drain current present in uniaxial strained pMOSFETs.

Index Terms—Cryogenic temperature, MOSFET, phonon-scattering-limited mobility, strain silicon, uniaxial.

## I. INTRODUCTION

NIAXIAL strained-Si technology is a key knob to boost transistor performance in state-of-the-art CMOS technology [1], [2]. The temperature dependence of strain-enhanced mobility is of fundamental importance and may provide insights for the underlying mechanisms responsible for performance enhancement. Recently, several studies have revealed that the temperature sensitivity of drain current for pMOSFETs is increased by uniaxially compressive strain [3]–[6]. However, the underlying mechanism is still not clear and merits investigation.

In this paper, through cryogenic temperature measurement to decouple surface-roughness-limited mobility  $\mu_{SR}$  and phonon-scattering-limited mobility  $\mu_{PH}$ , we investigate the impact of uniaxial strain on the temperature dependence of phonon-scattering-limited mobility in nanoscale pMOSFETs.

## II. EXPERIMENTAL

In this paper, pMOSFETs with channel direction  $\langle 110 \rangle$  under neutral and compressive uniaxial contact-etch-stop layer (CESL) [7] were investigated. The compressive strain is  $\sim -2.8$  GPa. The equivalent oxide thickness (EOT) is about

Manuscript received March 27, 2011; accepted August 22, 2011. Date of publication October 10, 2011; date of current version November 23, 2011. This work was supported in part by the National Science Council of Taiwan under Contract NSC99-2221-E009-174 and in part by the Ministry of Education in Taiwan under ATU program. The review of this brief was arranged by Editor A. Schenk.

The authors are with the Department of Electronics Engineering and the Institute of Electronics, National Chiao Tung University, Hsinchu 30010, Taiwan (e-mail: williamchen.ee93g@nctu.edu.tw; pinsu@faculty.nctu.edu.tw).

Color versions of one or more of the figures in this brief are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2011.2167153

17 Å, whereas the electrical EOT taking into account the quantum–mechanical and polydepletion effects is around 23 Å. The carrier mobility of pMOS devices with  $L_{\rm EFF}=95~\rm nm$  and effective channel doping  $\sim 2\times 10^{18}~\rm cm^{-3}$  was examined. The drain bias condition was 5 mV. Since external resistance  $R_{\rm sd}$  is crucial to mobility extraction for short-channel devices [8], [9], the BSIM  $R_{\rm sd}$  method [10] was adopted to extract the external resistance based on the I-V characteristics. The ideal drain current can then be derived from

$$I_d(\text{int}) = \frac{I_d(\text{ext})}{1 - I_d(\text{ext}) \times \frac{R_{\text{sd}}}{V_d}}$$

(1)

where  $I_d(\mathrm{int})$  represents the intrinsic drain current, and  $I_d(\mathrm{ext})$  represents the extrinsic drain current that includes the  $R_{\mathrm{sd}}$  effect.

Physical polygate length  $L_{\mathrm{PHY}}$  was obtained by inline SEM measurement. The LDD overlap region under the gate  $L_{\mathrm{OV}}$  was extracted by the split CV method [11], [17]. Effective channel length  $L_{\mathrm{EFF}}$  can then be derived by subtracting  $L_{\mathrm{OV}}$  from  $L_{\mathrm{PHY}}$ . Finally, the carrier mobility can be extracted.  $E_{\mathrm{EFF}}$  is extracted by

$$E_{\text{eff}} = \frac{Q_b + \eta \cdot Q_{\text{inv}}}{\varepsilon_{\text{Si}}}$$

(2)

where  $\eta$  is equal to 1/3 [16], and  $\varepsilon_{\rm Si}$  is the permittivity of Si.  $Q_{\rm inv}$  and  $Q_b$  can be obtained by integrating the CV curves from the split CV measurement [11]. The applied maximum gate-to-source bias is -2.5 V.

In order to extract surface-roughness mobility  $\mu_{\rm SR}$ , cryogenic temperature measurements were carried out using liquid He as the cooling source. The measurement temperature ranged from 20 K to 300 K. HP4156 and HP4285 were adopted to measure the transistor IV and CV characteristics.

## III. RESULTS AND DISCUSSION

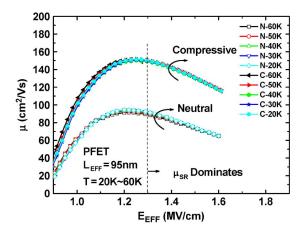

Fig. 1 shows the measured carrier mobility under compressive and neutral uniaxial strain with temperature ranging from 20 K to 60 K. It is known that the phonon-scattering mechanism can be suppressed and the surface-roughness-scattering mechanism may dominate within this temperature range (particularly for  $E_{\rm EFF}>1.3$  MV/cm) [12]. It is shown that  $\mu_{\rm SR}$  shows little temperature dependence, which is consistent with the reported data in the past [12], [13].

Fig. 1. Measured total mobility with temperature ranging from 20 K to 60 K for pMOSFETs with neutral and compressive uniaxial stressors. Surface-roughness mobility  $\mu_{\rm SR}$  tends to dominate as  $E_{\rm EFF}>1.3$  MV/cm and is independent of temperature.

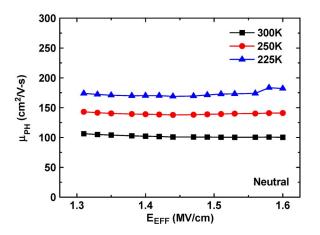

Fig. 2. Extracted phonon-scattering-limited mobility for neutral stressors at  $T=225~\rm K, 250~\rm K,$  and 300 K, respectively.

In order to extract  $\mu_{PH}$ , it is assumed that  $\mu_{SR}$  is independent of temperature [12], [13], and then, the Matthiessen's rule can be adopted, i.e.,

$$\mu_{\rm PH}^{-1}(T) = \mu_{\rm Total}^{-1}(T) - \mu_{\rm SR}^{-1}(T = 20 \ {\rm K}) \eqno(3)$$

where  $\mu_{\rm Total}$  is the total mobility, including impurity, phonon, and surface-roughness-scattering mechanisms, and  $\mu_{\rm SR}$  (20 K) is the surface-roughness mobility at  $E_{\rm EFF}$  larger than 1.3 MV/cm. Fig. 2 shows the extracted  $\mu_{\rm PH}$  at 300 K, 250 K, and 225 K for neutral stressors. It is shown that  $\mu_{\rm PH}$  increases with decreasing temperature because of decreased phonon-scattering rate [12].

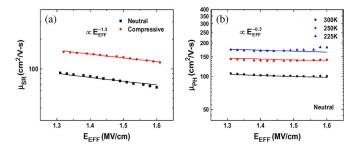

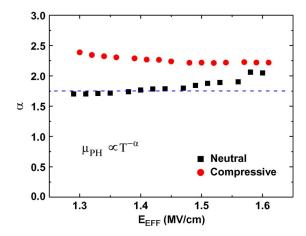

Fig. 3 shows the  $E_{\rm EFF}$  dependence of  $\mu_{\rm PH}$  and  $\mu_{\rm SR}$ . Extracted  $\mu_{\rm PH}$  and  $\mu_{\rm SR}$  are proportional to  $E_{\rm EFF}^{-1.3}$  and  $E_{\rm EFF}^{-0.3}$ , respectively, which is consistent with the reported data in the past [12], [13]. Fig. 4 shows the temperature dependence values of  $\mu_{\rm PH}$  ( $\mu_{\rm PH} \propto T^{-\alpha}$ ) versus  $E_{\rm EFF}$  for neutral and compressive stressors. It is shown that  $\alpha$  is close to 1.75 for the neutral stressor, which is consistent with the reported data in the literature [12]. Fig. 4 also shows that, with compressive uniaxial strain, the temperature sensitivity of  $\mu_{\rm PH}$  is increased ( $\alpha \approx 2.3$ ).

Fig. 3.  $E_{\rm EFF}$  dependence of  $\mu_{\rm SR}$  and  $\mu_{\rm PH}$  in (a) and (b). Extracted  $\mu_{\rm SR}$  and  $\mu_{\rm PH}$  are proportional to  $E_{\rm EFF}^{-1.3}$  and  $E_{\rm EFF}^{-0.3}$ , respectively.

Fig. 4. Temperature dependence of  $\mu_{\rm PH}$  for neutral and compressive stressors. The  $\alpha$  of the neutral stressor is close to 1.75, whereas with the compressive stressor, the  $\alpha$  value further increases to around 2.3 .

It is plausible that the observed strain dependence of  $\alpha$  in Fig. 4 results from strain-engineered intervalley scattering of optical phonons [14], [15]. The temperature dependence of optical phonon mobility can be expressed as [15]

$$\mu_o = A_o T^{-\frac{1}{2}} e^{\frac{\hbar \omega_o}{kT}} \tag{4}$$

where  $A_o$  is a constant, T is the temperature, k is Boltzmann's constant, and  $\hbar\omega_o$  represents the optical phonon energy. By the differentiation of (4) with respect to T

$$\frac{\delta \log \mu_o}{\delta \log T} = -0.5 - \frac{\hbar \omega_o}{kT}.$$

(5)

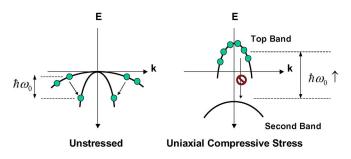

It is shown that the temperature sensitivity of the optical phonon mobility depends on optical phonon energy  $\hbar\omega_o$ . The schematic plot of the E-k band diagram in Fig. 5 shows the impact of uniaxial compressive strain on  $\hbar\omega_o$ . The strain induces the light-hole (LH) and heavy-hole band splits and most of the holes repopulate into the LH band [14]. In other words,  $\hbar\omega_o$  is increased due to band splitting as the compressive strain is applied. Therefore, the  $\alpha$  value is increased (see Fig. 4) for the compressively strained pMOSFETs.

From previous reports [3]–[6], it has been found that the temperature sensitivity of drain current for the compressively strained pFET is larger than that of the unstrained counterpart. Our new finding in this paper, i.e., the strain-enhanced temperature sensitivity of  $\mu_{\rm PH}$ , has suggested a plausible mechanism

Fig. 5. Schematic plot of the E-k energy band diagram under a uniaxial compressive stressor in pFET. Optical phonon energy  $\hbar\omega_0$  may increase when compressive uniaxial strain is applied.

responsible for these observations. It also provides insights for future mobility scaling using advanced strain technologies.

## IV. CONCLUSION

We have investigated the temperature dependence of  $\mu_{\rm PH}$  for advanced short-channel strained pMOS devices. By using the split CV method and Matthiessen's rule,  $\mu_{\rm SR}$  and  $\mu_{\rm PH}$  are successfully decoupled. This paper indicates that the temperature sensitivity of  $\mu_{\rm PH}$  is proportional to  $T^{-1.75}$  for the neutral stressor and becomes higher when compressive strain is applied. It is explained by the higher optical phonon energy induced by uniaxially compressive strain. Our new findings may also explain the previously reported higher temperature sensitivity of drain current present in uniaxial strain pMOSFETs.

#### REFERENCES

- [1] Z. Luo, N. Rovedo, S. Ong, B. Phoong, M. Eller, H. Utomo, C. Ryou, H. Wang, R. Stierstorfer, L. Clevenger, S. Kim, J. Toomey, D. Sciacca, J. Li, W. Wille, L. Zhao, L. Teo, T. Dyer, S. Fang, J. Yan, O. Kwon, D. Park, J. Holt, J. Han, V. Chan, J. Yuan, T. Kebede, H. Lee, S. Kim, S. Lee, A. Vayshenker, Z. Yang, C. Tian, H. Ng, H. Shang, M. Hierlemann, J. Ku, J. Sudijono, and M. Ieong, "High performance transistors featured in an aggressively scaled 45 nm bulk CMOS technology," in VLSI Symp. Tech. Dig., 2007, pp. 16–17.

- [2] F. Andrieu, T. Ernst, F. Lime, F. Rochette, K. Romanjek, S. Barraud, C. Ravit, F. Boeuf, M. Jurczak, M. Casse, O. Weber, L. Brevard, G. Reimbold, G. Ghibaudo, and S. Delenibus, "Experimental and comparative investigation of low and high field transport in substrate- and process-induced strained nanoscaled MOSFETs," in VLSI Symp. Tech. Dig., 2005, pp. 176–177.

- [3] W. Lee, J. Kuo, W. Chen, P. Su, and M. Jeng, "Impact of uniaxial strain on channel backscattering characteristics and drain current variation for nanoscale PMOSFETs," in VLSI Symp. Tech. Dig., 2009, pp. 112–113.

- [4] W. Lee and P. Su, "On the experimental determination of channel backscattering characteristics—Limitation and application for the process monitoring purpose," *IEEE Trans. Electron Devices*, vol. 56, no. 10, pp. 2285–2290, Oct. 2009.

- [5] W. P. N. Chen, J. J.-Y. Kuo, and P. Su, "Impact of process-induced uniaxial strain on the temperature dependence of carrier mobility in nanoscale pMOSFETs," *IEEE Electron Device Lett.*, vol. 31, no. 5, pp. 414–416, May 2010.

- [6] J. J.-Y. Kuo, W. P. N. Chen, and P. Su, "Enhanced carrier-mobility-fluctuations origin low frequency noise in uniaxial strained PMOSFETs," *IEEE Electron Device Lett.*, vol. 31, no. 5, pp. 497–499, May 2010.

- [7] W. P. N. Chen, P. Su, and K. Goto, "Impact of process-induced strain on Coulomb scattering mobility in short-channel n-MOSFETs," *IEEE Electron Device Lett.*, vol. 29, no. 7, pp. 768–770, Jul. 2008.

- [8] S. Severi, L. Pantisano, E. Augendre, E. San Andrés, P. Eyben, and K. De Meyer, "A reliable metric for mobility extraction of short-channel MOSFETs," *IEEE Trans. Electron Devices*, vol. 54, no. 10, pp. 2690– 2698, Oct. 2007.

- [9] D. Fleury, A. Cros, G. Bidal, J. Rosa, and G. Ghibaudo, "A new technique to extract the source/drain series resistance of MOSFETs," *IEEE Electron Device Lett.*, vol. 30, no. 9, pp. 975–977, Sep. 2009.

- [10] W. P. N. Chen, P. Su, K. Goto, and C. Diaz, "Series resistance and mobility extraction method in nanoscale MOSFETs," *J. Electrochem. Soc.*, vol. 156, no. 1, pp. H34–H38, Jan. 2009.

- [11] A. Cros, K. Romanjek, D. Fleury, S. Harrison, R. Cerutti, P. Coronel, B. Dumont, A. Pouydebasque, R. Wacquez, B. Duriez, R. Gwoziecki, F. Boeuf, H. Brut, G. Ghibaudo, and T. Skotnicki, "Unexpected mobility degradation for very short devices: A new challenge for CMOS scaling," in *IEDM Tech. Dig.*, 2006, pp. 1–4.

- [12] S.-I. Takagi, A. Toriumi, M. Iwasw, and H. Tango, "On the universality of inversion layer mobility in Si MOSFETs: Part II—Effects of surface orientation," *IEEE Trans. Electron Devices*, vol. 41, no. 12, pp. 2363– 2368, Dec. 1994.

- [13] K. Lee, J.-S. Choi, S.-P. Sim, and C.-K. Kim, "Physical understanding of low-field carrier mobility in Silicon MOSFET inversion layer," *IEEE Trans. Electron Devices*, vol. 38, no. 8, pp. 1905–1912, Aug. 1991.

- [14] S. E. Thompson, G. Sun, Y. S. Choi, and T. Nishida, "Uniaxial-processinduced strained-Si: Extending the CMOS roadmap," *IEEE Trans. Electron Devices*, vol. 53, no. 5, pp. 1010–1020, May 2006.

- [15] C. T. Sah, Fundamentals of Solid-State Electronics. Singapore: World Scientific, 1991.

- [16] S.-I. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the universality of inversion layer mobility in Si MOSFETs: Part I—Effects of substrate impurity concentration," *IEEE Trans. Electron Devices*, vol. 41, no. 12, pp. 2357–2362, Dec. 1994.

- [17] S.-I. Takagi and M. Takayanagi, "Experimental evidence of inversion-layer mobility lowering in ultrathin gate oxide metal-oxide-semiconductor field-effect-transistors with direct tunneling current," *Jpn. J. Appl. Phys.*, vol. 41, no. 4B, pp. 2348–2352, Apr. 2002.

William Po-Nien Chen received the B.S., M.S., and Ph.D. degrees in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2001, 2003 and 2011, respectively.

His current research interests include physics of semiconductor devices, nanodevice characterizing/modeling, and the carrier transport mechanism.

**Jack Jyun-Yan Kuo** (S'07) received the B.S. and M.S. degrees in 2004 and 2006, respectively, from National Chiao Tung University, Hsinchu, Taiwan, where he is currently working toward the Ph.D. degree in the Institute of Electronics.

His current research interests include characterization and modeling of advanced CMOS devices.

**Pin Su** (S'98–M'02) received the B.S. and M.S. degrees in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, and the Ph.D. degree from the University of California, Berkeley.

From 1997 to 2003, he conducted his doctoral and postdoctoral research in silicon-on-insulator (SOI) devices at Berkeley. He was also one of the major contributors to the unified BSIMSOI model, the first industrial standard SOI MOSFET model for circuit design. Since August 2003, he has been with the Department of Electronics Engineering, National Chiao

Tung University, where he is currently a Full Professor. He has authored or coauthored more than 130 research papers in refereed journals and international conference proceedings related to his areas of interest. His research interests include silicon-based nanoelectronics, modeling and design for exploratory CMOS devices, and device/circuit interaction and co-optimization in nanoscale CMOS.