# Amorphous InGaZnO Thin-Film Transistors Compatible With Roll-to-Roll Fabrication at Room Temperature

Ming-Jiue Yu, Yung-Hui Yeh, Chun-Cheng Cheng, Chang-Yu Lin, Geng-Tai Ho, Benjamin Chih-Ming Lai, Chyi-Ming Leu, Tuo-Hung Hou, and Yi-Jen Chan

Abstract—High-performance amorphous InGaZnO (a-IGZO) thin-film transistors (TFTs) are successfully fabricated on a colorless polyimide substrate using a top-gate self-aligned structure. All thin films are deposited by roll-to-roll-compatible sputtering processes at room temperature. The maximum field-effect mobility is  $18~{\rm cm^2/V\cdot s}$ , the threshold voltage is  $-1.35~{\rm V}$ , the subthreshold slope is 0.1 V/decade, and the on/off current ratio is about  $10^5$ . The results highlight that excellent device performance can be realized in a-IGZO TFTs without compromising manufacturability.

Index Terms—Amorphous InGaZnO, roll-to-roll, thin-film transistor (TFT).

### I. INTRODUCTION

LEXIBLE electronics are becoming increasingly important because of the advantages of flexibility, thin form factor, and light weight. In particular, the roll-to-roll process technology using flexible substrates is the most attractive because of its high-throughput capability and, thereby, very low manufacturing cost [1]. However, the device characteristics of low-temperature organic and a-Si thin-film transistors (TFTs) on flexible substrates of low glass transition temperature are insufficient to meet the requirements of active devices for high-performance applications. Recently, low-temperature amorphous indium—gallium—zinc oxide (a-IGZO) TFTs have attracted much attention for applications on next-generation displays and flexible electronics, owing to their high mobility and transparency [2]. Although excellent electrical character-

Manuscript received August 26, 2011; revised September 12, 2011; accepted September 28, 2011. Date of publication November 7, 2011; date of current version December 23, 2011. The review of this letter was arranged by Editor A. Nathan.

M.-J. Yu is with the Department of Electronics Engineering and the Institute of Electronics, National Chiao Tung University, Hsinchu 30010, Taiwan, and also with the Electronics and Optoelectronics Research Laboratories, Industrial Technology Research Institute, Hsinchu 31040, Taiwan (e-mail: mingjmingj@itri.org.tw).

Y.-H. Yeh, C.-C. Cheng, C.-Y. Lin, G.-T. Ho, B. C.-M. Lai, and Y.-J. Chan are with the Electronics and Optoelectronics Research Laboratories, Industrial Technology Research Institute, Hsinchu 31040, Taiwan (e-mail: yhyeh@itri.org.tw; CC.Cheng@itri.org.tw; CYL@itri.org.tw; gther@itri.org.tw; benjamin\_lai@itri.org.tw; yjchan@itri.org.tw).

C.-M. Leu is with the Material and Chemical Research Laboratories, Industrial Technology Research Institute, Hsinchu 31040, Taiwan (e-mail: ChyimingLeu@itri.org.tw).

T.-H. Hou is with the Department of Electronics Engineering and the Institute of Electronics, National Chiao Tung University, Hsinchu 30010, Taiwan (e-mail: thhou@mail.nctu.edu.tw).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2011.2170809

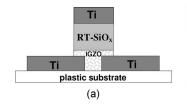

Fig. 1. (a) Device structure of the top-gate self-aligned a-IGZO TFT. (b) Top-gate self-aligned a-IGZO TFT on the PI substrate under bending condition.

istics have been shown in previous studies [3], [4], a-IGZO TFTs often require thermal annealing after device fabrication. The development of a-IGZO TFTs compatible with a room-temperature roll-to-roll process is less addressed.

In this letter, we successfully demonstrate a top-gate self-aligned IGZO TFT on a colorless polyimide (PI) substrate manufactured by a roll-to-roll-compatible process. The multichamber sputter tool that we used to deposit all films at room temperature and the photolithography and etching tools for device fabrication are all capable of continuous roll-to-roll manufacturing for large-size flexible applications. Excellent electrical characteristics applicable for future high-performance flexible electronics are reported for devices fabricated by a complete room-temperature process. In addition, the effects of thermal annealing after device fabrication are also discussed.

## II. EXPERIMENTAL SECTION

A top-gate self-aligned a-IGZO TFT structure shown in Fig. 1(a) was fabricated in this study because of its superior manufacturability [5]. This structure reduces the number of required masks, using only two compared to four in a conventional bottom-gate non-self-aligned structure. First, colorless PI was spin coated on a 6-in glass carrier and baked at 220 °C for 4 h. The prepared PI substrate was 40  $\mu$ m thick with high glass transition temperature (about 350 °C) and excellent transmittance. More details on the preparation of the PI substrate can be found in [6]. Source and drain electrodes were 50 nm of Ti deposited in a multichamber roll-to-roll sputter system, followed by photolithography patterning and wet etching. Then, 40-nm IGZO, 200-nm SiO<sub>2</sub>, and 100-nm Ti were deposited in the same multichamber sputter system at room temperature. A base pressure below  $1 \times 10^{-6}$  torr, a deposition pressure of about 0.5 mtorr, an Ar flow rate of 50 sccm, an O2 flow rate of 10 sccm, and an RF sputter power of 1000 W were used for the IGZO deposition. The composition of the IGZO target was 2:2:1:7 for In:Ga:Zn:O. After gate photolithography, the Ti gate electrode, SiO2, and IGZO films were wet

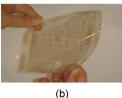

Fig. 2. (a) Optical transmission spectrum of the PI substrate. The inset shows the transparent PI substrate with metal lines on the top. (b) Cross-sectional TEM of the device structure. (c) Electron diffraction pattern of the a-IGZO film.

etched using the same mask in a self-aligned manner until the source/drain metal is exposed. The etchants for Ti, SiO<sub>2</sub>, and IGZO were  $NH_4OH + H_2O_2$ , BOE (20:1), and oxalic acid. The overlap between the gate and source/drain regions was less than  $2 \mu m$ . At last, the PI substrate was debonded from the glass carrier. The I-V electrical characteristics were measured by an Agilent 4156C semiconductor parameter analyzer. Although the present device was fabricated on a small-size glass carrier with a spin-on flexible substrate for convenience, the scaleup to a mass-production roll-to-roll process on other commercial low-temperature flexible substrates such as polyethylene terephthalate would have minimal impact on the a-IGZO TFT characteristics because all process steps mentioned here were done in roll-to-roll-compatible equipment and at room temperature. Fig. 1(b) shows the top-gate self-aligned IGZO TFT on the PI substrate under bending condition.

## III. RESULTS AND DISCUSSION

Fig. 2(a) shows the optical transmission spectrum over the visible light range of the PI substrate. At  $\lambda=550$  nm, the measured transmittance was about 90%. The inset in Fig. 2(a) shows the highly transparent PI substrate with metal lines on the top. Fig. 2(b) shows the cross-sectional TEM of the device structure. An amorphous phase of the IGZO film by room-temperature deposition was conformed by the electron diffraction pattern in Fig. 2(c). The amorphous active channel is preferential for better device uniformity and reproducibility by mitigating the effects of grain boundaries [2].

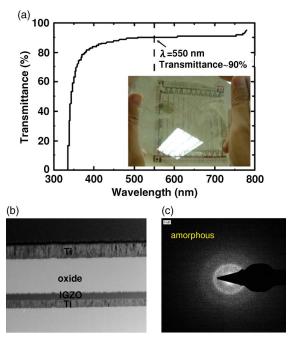

Fig. 3(a) shows the transfer characteristics of the top-gate self-aligned a-IGZO TFT without any thermal annealing. The channel width and length were 20 and 10  $\mu$ m, respectively, and the drain voltage was 1 V. The device had an on/off current ratio of around  $10^5$  at  $V_G = \pm 5$  V, a very steep subthreshold slope of 0.1 V/decade, a threshold voltage of -1.35 V, and a maximum field-effect mobility of 48.5 cm<sup>2</sup>/V·s. The threshold voltage

Fig. 3. Typical (a) transfer and (b) output characteristics of the top-gate self-aligned a-IGZO TFT.

was determined from the maximum  $G_m$  method, while the field-effect mobility was extracted from the linear regime. The channel width of 20  $\mu$ m was defined by the width of the source/drain rather than the width of the IGZO film, which was considerably wider in the self-aligned structure. Therefore, the effective channel width calibrated using devices with various channel widths was larger than 20  $\mu$ m due to the fringing current effect. The mobility after calibration was decreased by 63% to 18 cm²/V·s. Table I compares the important device parameters of the a-IGZO TFT with those on various flexible substrates reported in the literature. The high mobility and steep subthreshold slope in the present work were among the best ever reported. The results highlight the excellent interface quality between the a-IGZO channel and SiO<sub>2</sub> even by a room-temperature roll-to-roll-compatible process.

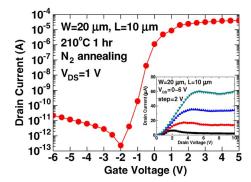

Several aspects of device performance, namely, gate leakage current, contact resistance, and carrier mobility, may be further improved by the additional thermal treatment after device fabrication. Because the gate insulator was deposited by sputtering at room temperature, a large number of defects existed in the oxide film. These defects resulted in an increased off current because of gate leakage. In Fig. 3(a), the off current under negative gate bias was slightly higher, at around 200 pA at  $V_G = -5$  V. Moreover, without any thermal annealing, the nonlinear  $I_{\rm DS}$ – $V_{\rm DS}$  curve at the low- $V_{\rm DS}$  and high- $V_{\rm GS}$  regime in Fig. 3(b) suggests the nonideal Schottky source/drain contact. Extensive conditions of thermal annealing in atmospheres of nitrogen and air and in a vacuum over a range from 150 °C to 230 °C have been investigated. The best result was obtained by using the nitrogen annealing at 210 °C. Fig. 4 shows the transfer and output characteristics of the a-IGZO TFT after annealing. The thermal annealing densified the oxide film and reduced defects. By improving the quality of the gate insulator, the off current was suppressed to 20 pA at  $V_G = -6$  V, as shown in Fig. 4.

|              | Max.<br>Process<br>Temp. | operation<br>voltage<br>(V) | μ<br>(cm <sup>2</sup> /V-s) | $V_{th}\left(V\right)$ | SS<br>(V/decade) | on/off<br>ratio      | substrate     |

|--------------|--------------------------|-----------------------------|-----------------------------|------------------------|------------------|----------------------|---------------|

| this<br>work | RT                       | 5                           | 18                          | -1.35                  | 0.1              | 1×10 <sup>5</sup>    | PI            |

| [3]          | 200 °C                   | 1.5                         | 22.1                        | 0.1                    | 0.18             | $2 \times 10^5$      | PI            |

| [7]          | <100 °C                  | 10                          | 5.3                         | 1.13                   | 0.55             | 8×10 <sup>4</sup>    | PI            |

| [8]          | 90 °C                    | 6                           | 12.1                        | 1.25                   | 0.35             | >10 <sup>5</sup>     | PET           |

| [9]          | RT                       | 6                           | 3.9                         | 1.4                    | 0.2              | 1.7×10 <sup>6</sup>  | PET           |

| [10]         | RT                       | 4                           | 10.86                       | -0.34                  | 0.46             | 4.13×10 <sup>6</sup> | PET           |

| [11]         | RT                       | 20                          | 34                          | 1.9                    | 0.8              | 2.9×10 <sup>4</sup>  | Cellulose     |

| [7]          | RT                       | -                           | 35                          | 3.75                   | 2.4              | 1×10 <sup>4</sup>    | Cellulose     |

| [12]         | 100 °C                   | 10                          | 1.2                         | 1.9                    | 0.65             | 1×10 <sup>4</sup>    | Paper         |

| [13]         | 300 °C                   | 25                          | 15                          | 3                      | 0.5              | >107                 | Metal<br>Foil |

TABLE I COMPARISON OF VARIOUS a-IGZO TFTs FABRICATED ON FLEXIBLE SUBSTRATES

Fig. 4. Typical transfer characteristics of the top-gate self-aligned a-IGZO TFT after nitrogen annealing at 210  $^{\circ}C$  for 1 h. The inset shows the output characteristics.

In addition, the on current increased several times by improving the source/drain contact and increased mobility. Because the source/drain and the IGZO channel were deposited at room temperature, the intermixing of Ti and IGZO was very limited before annealing and resulted in higher contact resistance. The annealing process facilitated the intermixing at the interface and thus improved the contact resistance. The extracted mobility after annealing increased to about  $32\,\mathrm{cm}^2/\mathrm{V}\cdot\mathrm{s}$  after calibrating for the effective channel width. However, the subthreshold slope degraded to  $0.25\,\mathrm{V/decade}$ , possibly due to the interaction between a-IGZO and SiO<sub>2</sub> at the annealing temperature.

#### IV. CONCLUSION

This letter has demonstrated the fabrication of a high-performance top-gate self-aligned a-IGZO TFT on a colorless PI substrate through a room-temperature sputtering process. The TFT has an on/off current ratio of about  $10^5$ , a subthreshold slope of 0.1 V/decade, a threshold voltage of -1.35 V, and a field-effect mobility of  $18 \text{ cm}^2/\text{V} \cdot \text{s}$ . Moreover, all processes are completed using a roll-to-roll-compatible manufacturing facility. This device is suitable for active devices in large-area and low-cost flexible electronics and display applications.

## REFERENCES

- [1] H. Zhang, M. D. Poliks, and B. Sammakia, "A roll-to-roll photolithography process for establishing accurate multilayer registration on large area flexible films," *J. Display Technol.*, vol. 6, no. 11, pp. 571–578, Nov. 2010.

- [2] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors," *Nature*, vol. 432, no. 7016, pp. 488–492, Nov. 2004.

- [3] N. C. Su, S. J. Wang, C. C. Huang, Y. H. Chen, H. Y. Huang, C. K. Chiang, and A. Chin, "Low-voltage-driven flexible InGaZnO thinfilm transistor with small subthreshold swing," *IEEE Electron Device Lett.*, vol. 31, no. 7, pp. 680–682, Jul. 2010.

- [4] P. Barquinha, A. M. Vilà, G. Gonçalves, L. Pereira, R. Martins, J. R. Morante, and E. Fortunato, "Gallium–indium–zinc-oxide-based thin-film transistors: Influence of the source/drain material," *IEEE Trans. Electron Devices*, vol. 55, no. 4, pp. 954–960, Apr. 2008.

- [5] J. Park, I. Song, S. Kim, S. Kim, C. Kim, J. Lee, H. Lee, E. Lee, H. Yin, K.-K. Kim, K.-W. Kwon, and Y. Park, "Self-aligned top-gate amorphous gallium indium zinc oxide thin film transistors," *Appl. Phys. Lett.*, vol. 93, no. 5, p. 053 501, Aug. 2008.

- [6] J.-M. Liu, T. M. Lee, C.-H. Wen, and C.-M. Leu, "High performance organic-inorganic hybrid plastic substrate for flexible display and electronics," in *Proc. SID Dig.*, 2010, pp. 913–916.

- [7] S. J. Pearton, W. Lim, E. Douglas, F. Ren, Y. W. Heo, and D. P. Norton, "Oxide thin film transistors on novel flexible substrates," *Proc. SPIE*, vol. 7603, pp. 760315-1-760315-11, 2010.

- [8] W. Lim, J. H. Jang, S.-H. Kim, D. P. Norton, V. Craciun, S. J. Pearton, F. Ren, and H. Shen, "High performance indium gallium zinc oxide thin film transistor fabricated on polyethylene terephthalate substrate," *Appl. Phys. Lett.*, vol. 93, no. 8, p. 082 102, Aug. 2009.

- [9] H. Kumomi, K. Nomura, T. Kamiya, and H. Hosono, "Amorphous oxide channel TFTs," *Thin Solid Films*, vol. 516, no. 7, pp. 1516–1522, Feb. 2008.

- [10] D. H. Kim, N. G. Cho, H. G. Kim, H. S. Kim, J. M. Hong, and I. D. Kim, "Low voltage operating InGaZnO<sub>4</sub> thin film transistors using high-k MgO-Ba<sub>0.6</sub>Sr<sub>0.4</sub>TiO<sub>3</sub> composite gate dielectric on plastic substrate," Appl. Phys. Lett., vol. 93, no. 3, p. 032 901, Jul. 2008.

- [11] E. Fortunato, N. Correia, P. Barquinha, L. Pereira, G. Goncalves, and R. Martins, "High-performance flexible hybrid field-effect transistors based on cellulose fiber paper," *IEEE Electron Device Lett.*, vol. 29, no. 9, pp. 988–990, Sep. 2008.

- [12] W. Lim, E. A. Douglas, D. P. Norton, S. J. Pearton, F. Ren, Y. W. Heo, S. Y. Son, and J. H. Yuh, "Low-voltage indium gallium zinc oxide thin film transistors on paper substrates," *Appl. Phys. Lett.*, vol. 96, no. 5, p. 053 510, Feb. 2010.

- [13] S. A. Khan, P. C. Kuo, J. R. Abbas, and M. Hatalis, "Effect of uniaxial tensile strain on electrical performance of amorphous IGZO TFTs and circuits on flexible metal foils," in *Proc. IEEE Device Res. Conf.*, 2010, pp. 119–120.