# Self-Assembled Ni Nanodot on SiO<sub>2</sub> Film—A Novel Reactive Ion Etching Mask for Si Nanopillar Formation on Si Substrate

Huang-Shen Lin, Chih-Chiang Kao, Hao-Chung Kuo, Shing-Chung Wang, and Gong-Ru Lin\*

Department of Photonics & Institute of Electric-Optical Engineering, National Chiao Tung University, 1001, Ta Hsueh Road, Hsinchu 300, Taiwan R.O.C. Phone: 886-3-5712121 ext: 56376 Fax: 886-3-5716631

Email: grlin@faculty.nctu.edu.tw

#### **ABSTRACT**

By rapid thermal annealing the Ni film evaporated on thin  $SiO_2$  layer covered Si substrate, we have successfully demonstrated the self-aggregation of two-dimensional randomized Ni nano-dots on Si wafer. The thin oxide layer prevents the formation of  $NiSi_2$  compounds and facilitates the self-assembly of Ni nanodots from retaining the thermal power on  $SiO_2$  layer. This greatly shrinks the annealing time required for metallic nanodot formation from >10 min to <30 sec. With the advantage of the self-assemble  $Ni/SiO_2$  nano-dots based nano-mask, a large-area Si nano-pillar array with rod size of <50 nm can be formatted on Si substrate through the induced coupled plasma reactive ion etching (ICP-RIE) procedure. After removing Ni dots and the  $SiO_2$  film on the Si substrate, both the visible and near infrared photoluminescence from the Si nano-pillar sample were observed and analyzed.

Keywords: Self-assemble, Ni nano-dot, Si nano-pillar, reactive ion etching, mask, SiO<sub>2</sub>, Si.

### 1. INTRODUCTION

A Si nano-pillar array has been shown to have the potential for many applications such as being photonic crystals<sup>1</sup>, data storage<sup>2</sup>, field electron emitter<sup>3</sup>, nanoscale transistors<sup>4, 5</sup> and light emitting devices<sup>6</sup>. In particular, the light emitting efficiency could be enhanced with the aid of the quantum confined Si nano-pillars. Traditional approaches for fabricating sub-micron or nano- Si structures, such as the Si nano-pillars, mainly rely on the electron-beam (E-beam) lithography<sup>1,7-10</sup>, which provides accurate size and shape control. The production of <10-nm nano-pillar array under the assistance of E-beam lithography has been reported by Toshihiko and Papadimitriou. However, it is impractical to employ the E-beam lithography for large-scale fabrication due to its high cost and low writing speed. Nowadays, noble metal (Au or Ag) based nano-dot arrays have been extensively used as nano-masks to replace the E-beam lithography. Recently, Ni has been considered as an alternative to the noble metals. The Ni nano-dot mask is not only easy to control its size but also cheap in its formation process as compared to that of the e-beam lithography. Previously, Yoo et al. made use of Ni nano-dot mask to form Si nano-pillars with diameter and height of about 41nm and 472nm, respectively. Nevertheless, the disadvantage of their results is that the density is too sparse to enhance the luminescence, and the self-aggregation of the Ni nano-dot from a Ni film coated on a Si substrate usually takes up to 10 min even by a rapid thermal annealing (RTA) process at 700°C in the N<sub>2</sub> ambient<sup>11</sup>. This is mainly due to the larger thermal conductivity of the Si substrate that reduces the thermal energy accumulating on the interface of Ni and Si, and due to the relative good adhesion between the Ni and Si interface that slows down the aggregating speed. Besides, such a long-term annealing inevitably leads to an unintentional doping or diffusion of the coated metal into the Si substrate during the self-assembly procedure. To avoid the aforementioned problems, we propose for the first time the quick formation of Ni nano-dots on Si substrate covered with a thin buffered SiO<sub>2</sub> layer, Si<sub>3</sub>N<sub>4</sub> layer <sup>12</sup> or TiN <sup>13, 14</sup>. The thin oxide or nitride layer could prevent the formation of NiSi<sub>2</sub><sup>15</sup> compounds and keep the thermal power on the Si The reactive ion etching and electrochemical etching were employed as two etching procedures to obtain Si nano-pillar array with the aid of self-assembled Ni nano-dot mask patterns. With the novel approach, the formation of the Si nano-pillar array can be mostly realized by the reactive ion etching of oxide-covered Si substrate capped with the mask of self-assembled Ni, Al<sup>16</sup> or Au<sup>17</sup> nano-dot. Afterwards, the luminescent characteristics of the Si nano-pillars or nano-rods generated at the reactive ion etched Si surface are investigated.

Nanophotonics, edited by David L. Andrews, Jean-Michel Nunzi, Andreas Ostendorf, Proc. of SPIE Vol. 6195, 61951W,  $(2006) \cdot 0277-786 \times 06/515 \cdot doi: 10.1117/12.663339$

## 2. EXPERIMENTAL

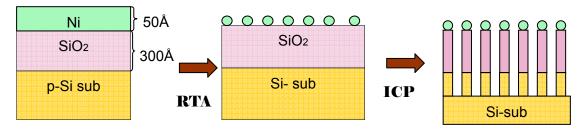

The schematic diagram to perform the experimental steps of the Si nano-pillar formation is shown in Fig. 1, which includes wafer cleaning, SiO<sub>2</sub> deposition, Ni evaporation, rapid thermal annealing for Ni nanodot assembly, ICP dry etching for Si nano-pillar, and wet etching for metal/oxide removal. First of all, the RCA cleaning process is also employed to completely clean the dusty particles and native oxide of a p-type [100] Si wafer, which flushes the Si wafer with DI (de-ion) water, immerse the Si wafer in the H<sub>2</sub>SO<sub>4</sub> based solution to decompose and oxidize the organic compounds, dip it into the HF solution to get rid of chemical oxide, immerse it in NH<sub>4</sub>OH solution to get rid of micro particles, dip it in HCl solution to get rid of alkaline-earth metal, and finally dip it in HF to get rid of chemical oxide.

Fig. 1 Schematic illustration of Si nano-pillar arrays using  $Ni/SiO_2$  as nano-masks formation. The reaction products after RTA and ICP-RIE etching, leading to the formation of Si nano-pillar arrays.

In previous experiment, it is hard to achieve the aggregation of evaporated Ni film on pure Si wafer. This is because the adhesion between Ni and Si is too good to be make Ni self-assembled. Such a problem can be solved by depositing a thin layer of SiO<sub>2</sub> between Ni and Si. In our case, a buffered layer of 200Å-thick SiO<sub>2</sub> is deposited by plasma enhanced chemical vapor deposition (PECVD) under standard recipe. Afterwards, a 50nm-thick Ni film is evaporated on the SiO<sub>2</sub>/Si substrate using an E-beam evaporating system with Ni deposition rate of 0.1 Å/s at an applied current of 70 mA. Subsequently, the rapid thermal annealing (RTA) process at 850°C for 22 seconds under the N<sub>2</sub> flowing gas of 5 sccm is performed to format randomized Ni nanodot pattern on SiO<sub>2</sub>/Si substrate. By using the Ni nano-dot pattern as an etching mask, The Si substrate is dry-etched in a planar type ICP-RIE system (SAMCO ICP-RIE 101iPH) at RF frequency of 13.56 MHz and the ICP/Bias power conditions of 100/50 or 200/100 watts. The ICP has a reactive chamber connected to a load-lock chamber, wherein the etching gas mixture of CF4 and Ar gases were introduced into the reactive chamber through individual electronic mass flow controllers (MFCs). The flowing rate of each gas is adjusted within an accuracy of about a standard cubic centimeter min (sccm). An automatic pressure controller is placed near the exhaust end of the chamber to control the chamber pressure. The gas mixture condition of  $CF_4/Ar = 40/40$  sccm with the ICP/Bias powers set at 100W/50W or 200W/100W and chamber pressure of 0.66 Pa during an etching duration of 5~7 min. If the etching parameters such as source power, bias power, and pressure and gas composition are investigated and optimized, Si nano-pillar arrays with tunable diameters of smaller than 100 nm can be formed. For analyzing the morphology of Ni nano-dot, the dimension and density of the Si nano-pillar array were estimated by the scanning electron microscope (SEM, Hitachi FE-SEM S-5000) and the standard atomic force microscopy (AFM).

## 3. RESULTS AND DISCUSSION

# 3.1 Effect of SiO<sub>2</sub> Buffered Layer

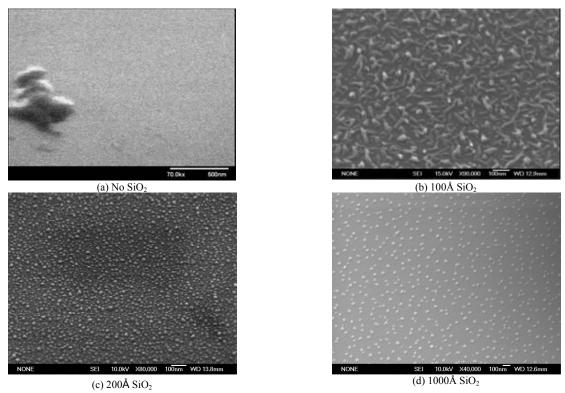

Figure 2 is SEM image of the Ni nano pattern under different thickness of  $SiO_2$  layer when the Ni thickness, annealing temperature and time are 50 Å, 850°C and 2 min, respectively. After RTA, Fig. 2(a) confirms that there is not any aggregation of Ni on pure Si wafer at all. On the contrary, we observe the apparent self-assembled Ni dot on  $SiO_2/Si$  substrate. The image in Fig. 2(b) shows that the Ni layer begins to form a long strip shape on the thin  $SiO_2$  layer after annealing. By increasing the thickness of  $SiO_2$  layer from 100 Å to 200 Å, Fig. 2(c) illustrates a coherent aggregation of Ni nanodots with almost half-sphere morphology. If the thickness of the  $SiO_2$  enlarges to 1000 Å, the size of Ni nanodots becomes larger than those obtained with thinner  $SiO_2$  film covered on the Si substrate, whereas the Ni nanodot

density greatly reduces. It is concluded from the above-mentioned comparison that the congregation of Ni can be more complete as the thickness of  $SiO_2$  increases, which is mainly attributed to the enhanced heat accumulation effect happened in the thicker  $SiO_2$  layer. Apparently the conductivity of Si is better than  $SiO_2$  due to their distinguishable thermal conductivities of 148 and 1.31 W/m-K, respectively<sup>18</sup>. Therefore, the  $SiO_2$  can lay off the thermal diffusion from Ni layer to the bowl and also can accumulate thermal energy dissipated from Ni layer to help Ni self-assembled.

Fig. 2 Aggregation of Ni nanodots on SiO2 layer with different thicknesses ranging from 100Å to 1000Å depositing on Si substrate

## 3.2 Effect of Annealing Temperature and Period

The thin Ni film evaporated on the SiO<sub>2</sub> film can easily to be conglomerated, resulting in the formation of Ni nano-dot array on SiO<sub>2</sub> substrate. Whether we change the annealing temperature or annealing time, both the thermal energy of annealing can be adjusted. From our experimental results, 850°C is the proper temperature for RTA annealing. As if the annealing temperature is too high, the Ni and Si atoms could obtain sufficient power to compose the SiNi<sub>2</sub> compounds<sup>15</sup>. However, if the annealing temperature is too low, it spends more annealing time to congregate Ni film into randomized two-dimensional nanodot array. In the following experiments, we choose to fix the annealing temperature and vary the annealing time during RTA process.

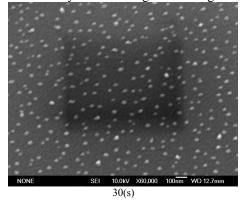

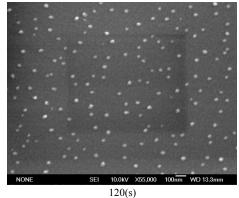

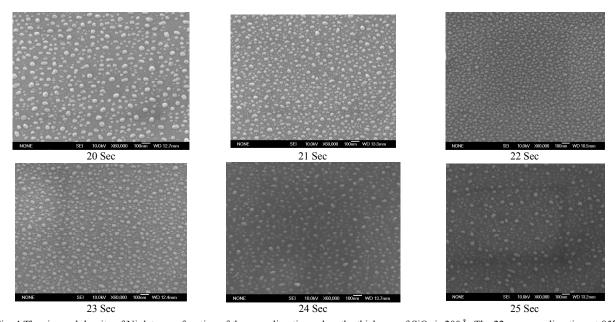

As shown in Fig. 3, we compare the variation in size and density of Ni dots assembling on 1000Å SiO<sub>2</sub> layer under two different annealing time. The average size and density of Ni nanodots annealing at  $850^{\circ}$ C for 30 sec are 37 nm and  $1\times10^{12}$  cm<sup>-2</sup>, respectively. Nonetheless, the average size and density of Ni nanodots annealing at 120 sec significantly increase to 40 nm and  $7\times10^{11}$  cm<sup>-2</sup>. This again confirms the trend of enlarging size and decreasing density under long annealing time. The Ni atoms can get more thermal energy to complete their precipitation process under longer annealing time. However, after rapid thermal annealing at  $850^{\circ}$ C between 20 and 26 sec, the Ni dots were formed on the 200Å SiO<sub>2</sub> film shown in Fig. 4.

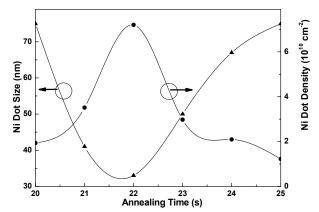

Fig. 4 The size and density of Ni dots as a function of the annealing time when the thickness of  $SiO_2$  is 200Å. The 22 sec annealing time at 850°C is the optimum item for the densest density and the smallest diameter.

The shape of Ni nanodots becomes hemisphere-like with an average diameter varying from 33 nm to 75 nm, respectively. A largest density of  $7.2 \times 10^{12}$  cm<sup>-2</sup> for the Ni nanodot with smallest size of 33 nm can be obtained after annealing at 850°C for 22 sec. Figure 4 interprets the variation SEM image of Ni nanodot self-assembled at gradually lengthened annealing durations. The Ni film initially breaks into large strips and slowly approaches a hemispheric shape with increasing RTA time, eventually these small Ni nanodots would congregate to larger nanodots if the annealing time prolongs to >30 sec. At annealing time between 22 and 26 sec, there is also a similar tendency on the size and density of Ni nanodots as compared to those shown in Fig. 3.

Fig. 5 The size and density of self-aggregated Ni nanodot as a function of RTA annealing time.

In more detail, the size and distribution of the Ni nano-dots on the SiO<sub>2</sub> film are mainly determined by thin oxide film thickness, RTA temperature, RTA time and Ni thickness. From the diagram of curves of Fig. 5, the optimum time is 22 seconds. The optimum annealing condition for Ni nanodot formation with highest density and smallest size are therefore set as 850°C for 22 sec in our RTA annealing process. Such a sample has also been chosen as the Ni nanomask for etching Si-nano-pillars. In addition, we also observe that the diameter of Ni nanodots becomes smaller with a decrease in the thickness of the deposited Ni layer<sup>12</sup>.

## 3.3 Effect of Etching Power

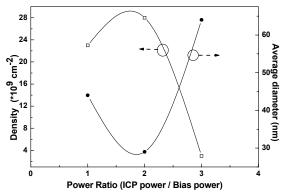

To perform the Si nanopillar formation, we took the Ni nanodots as a nano-scale mask that formed at the annealing 850°C for 22 sec. The average diameter and density are 33nm and  $7.2 \times 10^{12}$  cm<sup>-2</sup>. The effect of processing pressure on the etching characteristics of Si was investigated. The processing pressure was controlled between 6.66 and 0.66 Pa and the other processing parameters are unchanged. Since the chamber with the high processing pressure contains the more reactive gases, the etching rate will be faster than that with lower processing pressure. However, it is difficult to form the Si nanopillars under the high processing pressure. The reason is that the Ni dots were also etched completely. So we always controlled the chamber pressure under 0.66 Pa during the etching.

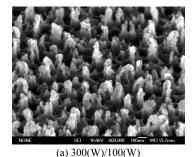

Fig. 6 (a) shows the apparently triangle shape of Si nano-pillar. (b) The sharper sidewall of Si nanopillar. (c) A sharp side-wall of Si pillar with insufficient height.

Figure 6(a) shows that the by-product appears and the shape of Si nano-pillar resembles a pyramid when the ratio is 3. Then the density is the smallest and the diameter is the largest. The cause is isotropic etching erodes the smaller pillar, and the reason for a pyramid shape is that the vertical etching-rate is not bigger than the side etching-rate so the diameter of the pillar becomes bigger after longer etching time. Finally, the etching rate is dominated by the power. So we are sure the ratio of 3 is too big to get a straight pillar. Figure 6(b) shows the success of the formation of Si nano-pillar with a perpendicular sidewall at the ratio of 2. The density and diameter of Si nano-pillars are  $2.8 \times 10^{12}$  cm<sup>-2</sup> and 29 nm. Figure 6(c) shows the straight but short Si nano-pillars at the ratio of 1. This is because the vertical etching is too big to balance the etching selection between Ni and Si, we can see the Ni mask disappeared during the etching.

Fig. 7 Different ratio of ICP power over bias power has different influence on the vertical level of Si pillars' side-wall.

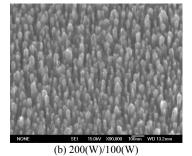

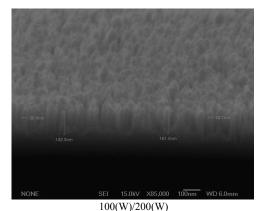

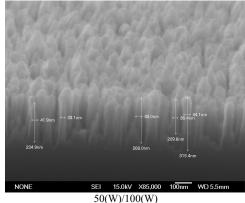

In another word, the appropriate ratio of bias and ICP power is the key point to get sharp sidewall and large height of Si pillar. After analyzing the SEM data in Fig. 7, we can know the ratio of bias power over ICP power had great influence on the character of Si nano-pillars such as the size and the density. In summary, we know that the ratio of 2 is the most suitable for the formation of Si nano-pillar. From Fig. 8 we can know if the magnitude is bigger, the Si nano-pillars will be longer and the size of them will be wider. The average size of bias/ICP power at 100(W)/200(W) is 29 nm and the average one at 50(W)/100(W) is 44nm. The average height of 100(W)/200(W) is 150nm and the one of 50(W)/100(W) is 250nm. And from the cross-session image in Fig. 8, high aspect-ratio of Si nano-pillars was formed at the bias/ICP power of 2.

Fig. 8 The different magnitude of power with the same ratio of bias and ICP power.

As for etchant gas, we chose the  $O_2$ ,  $CF_4$  and Ar at the beginning of experiment.  $CF_4$  is the main gas for etching  $SiO_2$  and Si. Ar is also main gas able to increase the vertical-etching potential. In our opinion,  $O_2$  is the mirror gas which should speed up the etching rate. Nevertheless, the aid of  $O_2$  isn't apparent and the oxygen plasma causes a lot of defects such weak oxygen bond and the neutral oxygen vacancy in the Si nano-pillars analyzed from the photoluminescence. On account of the above reason, we have not used  $O_2$  as etchant gas.

## 3.4 Results of Photoluminescence

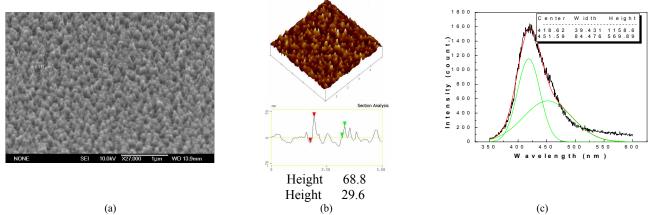

The height of the Si nano-pillars is between 30 and 100 nm shown in Fig. 9(b) and the density of the Si nana-rods is about  $5.4 \times 10^{11}$  cm<sup>-2</sup> shown in Fig. 9(a). Therefore, some Ni dots were eliminated from the surface of the SiO<sub>2</sub> film. The crater on the Si nano-pillars also provides another proof of the Ni-dot elimination. After removing Ni dots and the SiO<sub>2</sub> film on the Si substrate, the visible photoluminescence from the Si nana-rod sample were observed.

Fig. 9 (a) SEM image of Si nano-pillars after removing the Ni and SiO<sub>2</sub> layers at the etching-power ratio of 2 for 3 min. (b) AFM data including 3-D 45°view angle image and the height profile. (c) Photoluminescence of Si nano-pillars in (a) and decomposed by two Gaussion fits at 418 and 451 nm

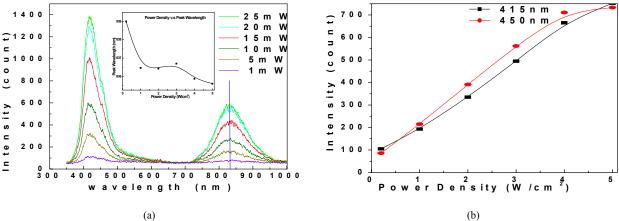

Previously, the luminescent centers in the SiO<sub>2</sub>:Si+ corresponding to the visible PL were comprehensively investigated, which include the weak oxygen bond (WOB), the neutral oxygen vacancy (NOV) defect, the E'\delta defect and the non-bridge oxygen hole center (NBOHC) defects at emitting wavelengths of around, 415 nm, 455 nm, 520 nm, and 630 nm, respectively<sup>19-22</sup>. The Si nano-pillar sample presents a strong and broad PL spectrum between 400 nm and 600 nm. After decomposing with multi-Gaussian function, two principle luminescent centers at 418 and 451 nm with spectra linewidths of 39 and 84 nm, respectively, are demonstrated shown in Fig. 9(c). The strongest PL peaks at 415-455 nm with linewidths of 35-50 nm are very similar to those obtained by Nishikawa *et al.* The luminescence at 455 nm reported by Bae *et al.* has been attributed to the transition between the ground state (singlet) and the elevated state (triplet) of the NOV defects. During the etching process, oxygen atoms generated from the ionized O<sub>2</sub> impact the surface of the Si substrate. Therefore, two oxygen atoms generate the WOB defect. The NOV defect is attributed to the mobile oxygen atom and oxygen vacancy. If we changed the pumping power density, we can observe the changeless peak and the defect peak saturating shown in Fig. 10. This was because the density of the pumped energy level saturated under the high pumping power. This is also a proof that the two Gaussian peaks are from the defects not from the Si quantum confine. According to the information the quantum confine occurred at the size below 10 nano meters. Obviously, we must control the Si nano-pillar size below 10 nm to get quantum effect in the future.

Fig. 10 (a) Photoluminescence of Si nano-pillars for different pumping power densities. (b) Peak intensity for different pumping power densities.

## 3.5 Comparison with another process

The thin film deposition and RTA process is not only an easy and simple technique to control the formation of nano-dot but also an effective process compared to the conventional nano-pattern formation process like electron beam lithography technique. If the annealing temperature is too high, Ni and Si atoms would compose into SiNi<sub>2</sub> compounds<sup>15</sup>. However, longer annealing time is required to congregate Ni film to nanodots if the annealing temperature is too low. 850°C is the most suitable temperature for RTA annealing, and the Ni dot can be formatted just after 20 seconds. In comparison with previous work<sup>11</sup>, the density of Ni dots of our experimental results is  $7.2 \times 10^{12}$  cm<sup>2</sup> that is much higher than those ever reported  $(5 \times 10^{11} \text{ cm}^2)^{11}$ . The average size of 33 nm for the obtained Ni nanodots is also far smaller than the previous record of 60 nm. Moreover, the uniformity of the Ni nanodots obtained from our condition is clearly better than the previous works. Most important, we greatly reduce the annealing time from 10 minutes to 22 seconds with the aid of a buffered SiO<sub>2</sub> layer.

In the ICP-RIE process, the use of  $O_2$  source gas is abandoned in our recipe since which causes the oxygen related defects of such  $O_2$ , oxygen vacancy, weak-oxygen bonds, and non-bridged oxygen hole centers in Si matrix. Although the aspect ratio of our Si nano-pillars is only 5 as compared to the results reported by Homma et al. (up to 7) and Lee et al. (up to 12)<sup>11</sup>. In our case, the high-aspect-ratio selective etching procedure can be improved by increasing the etching time and by optimizing the ratio of bias/RF power and Ar fluence. The average diameters of Si nano-pillars obtained in our results of 29 nm and 54 nm from different recipes is larger than the record of <10 nm by Japan and Korean groups. It tells us our Ni dots don't disappear during the etching and the etching selective is high to get long and small diameter Si nano-pillar. However, the density of our result (a largest density of this process can be nearly  $7 \times 10^{12}$  cm<sup>-2</sup>.) by using the dense Ni nanodots based nano-mask is still larger than the records to date.

#### 4. CONCLUSION

A novel reactive ion etching mask for Si nano-pillar formation on Si Substrate with self-assembled Ni nano-dots on SiO<sub>2</sub> film was successfully investigated. The improvement of this experiment is shortening the annealing time to 20 seconds and increasing the density of nano-pillars by the dense Ni nano-dots. From the above discussion, we can get the control of the density and size of Ni nano-mask by annealing temperature, annealing time, SiO<sub>2</sub> thickness and Ni thickness. If the SiO<sub>2</sub> film is thicker, the larger size and less density of Ni dots will be achieved. However, a thick SiO<sub>2</sub> layer would decrease the effective etching depth of Si nano-pillars. Therefore, 200 Å-SiO<sub>2</sub> is selected to be a buffer layer for Ni assembly. High annealing temperature and long annealing time will cause the large size and less density of Ni dots. Nevertheless, from the beginning of Ni congregation, the maximum density and size of Ni dots are  $7.2 \times 10^{12}$  cm<sup>-2</sup> and 33 nm, respectively. The optimum annealing temperature and time are 850°C and 22 seconds for Ni congregation. The optimum ICP-RIE recipes for the densest and highest aspect-ratio Si nano-pillar are 0.66 pa and 2 of the low chamber pressure and the ratio of RF power over bias power. The largest density and the average size of Si nano-pillar are  $7 \times 10^{12}$  cm<sup>-2</sup> and 50nm, respectively. The average height of Si nano-pillar is about 100 nm for the etching time of 3 For the etching time of 5 mins, the average diameter of Si nano-pillars is narrow down to 29 nm with the density of 2.84×10<sup>12</sup> cm<sup>-2</sup> and the average height of 150 nm. Moreover, an obvious PL between 350 nm and 600 nm can be observed. After decomposing with the multi-Gaussian function, two principle luminescent centers at 418 and 451 nm with spectra linewidths of 39 and 84 nm, respectively, are demonstrated. Since the PL intensity is saturated under the high pumping power, Gaussian peaks are attributed to defects, such as WOB and NOV defects, not the Si quantum confinement from Si nano-pillars. The future experiment tends to control the Si nano-pillar size below 10nm to get quantum effect.

## REFERENCES

- 1. V. Poborchii, T. Tada, and T. Kanayama, Opt. Commun. 210, 285, 2002.

- 2. K. Sunouchi, H. Tkato, N. Okabe, T. Yamada, T. Ozaki, S. Inoue, K. Hashimoto, K. Hieda, A. Nitayama, F. Horiguchi, and F. Masuoka, in IEDM Tech. Dig. 23, 1989.

- 3. A. V. Karabutov, V. D. Frolov, A. V. Smakin, and G. A. Shafeev, IEEE Proceedings of the 14<sup>th</sup> International Vacuum Microelectronics Conference (IVMC2001), pp.115-116. 2001.

- 4. M. Terauchi, N. Shigyo, A. Nitayama, and F. Horiguchi, IEEE Trans. Electron. Dev. 44, 2303, 1997.

- 5. F. D. Bauer, Solid-State Electron. 48, 705, 2004.

- 6. A. G. Nassiopoulos, S. Grigoropoulos, and D. Papadimitriou, Appl. Phys. Lett. 69, 2267, 1996.

- 7. D. Peyrade, Y. Chen, A. Talneau, M. Patrini, M. Galli, F. Marabelli, M. Agio, L. C. Andreani, E. Silberstein, and P. Lalanne, Microelectron. Eng. 529, 61, 2002.

- 8. M. Francois, J. Danlot, B. Grimbert, P. Mounaix, M. Muller, O. Vanbesien, and D. Lippens, Microelectron. Eng. 537, 61, 2002.

- 9. P. B. Fischer, K. Dai, E. Chen, and S. Y. Chou, J. Vac. Sci. Technol. B11, 2524, 1993.

- 10. H. I. Liu, D. K. Biegelsen, N. M. Johnson, F. A. Ponce, and R. F. W. Pease, J. Vac. Sci. Technol. B11, 2532, 1993.

- 11. J. S. Lee, S. K. Kim, G.Y. Yeom, J. B. Yoo, and C. Y. Park, Thin Solid Films 475, 41, 2005.

- 12. H. W. Huang, C. C. Kao, T. H. Hsueh, C. C. Yu, C. F. Lin, J. T. Chu, H. C. Kuo, and S. C. Wang, Mat. Science & Eng. B113, 125, 2004.

- 13. J. Narayan and S. Oktyabrysky, J. Appl. Phys. 92, 7122, 2002.

- 14. J. Narayan and B. C. Larson, J. Appl. Phys. 93, 278, 2003.

- 15. H. Zhou, D. Kumar, A. Kvit, A. Tiwari, and J. Narayan, J. Appl. Phys. 94, 4841, 2003.

- 16. D. Crouse, A. Y.-H. Lo, E. Millar, and M. Crouse, Appl. Phys. Lett. 76, 49, 2000.

- 17. Y. Homma, P. Finnie, T. Ogino, H. Noda, and T. Urisu, J. Appl. Phys. 86, 3083, 1999.

- 18. J. Zhao, J. Sullivan, J. Zayac, and T. D. Bennett, J. Appl. Phys. 95, 5475, 2004.

- 19. P. Muttia, G. Ghislotti, S. Bertoni, L. Bonoldi, G. F. Cerofolini, L. Meda, E. Grilli, and M. Guzzi, Appl. Phys. Lett. 66, 851, 1995.

- 20. R. Tohmon, Y. Shimogaichi, H. Mizuno, Y. Ohki, K. Nagasawa, and Y. Hama, Phys. Rev. Lett. 62, 1388, 1989.

- 21. H. Nishikawa, R. E. Stahlbush, and J. H. Stathis, Phys. Rev. B60, 15910, 1999.

- 22. L. Skuja, J. Non-Cryst. Solids 239, 16, 1998.