## (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2017/0032848 A1 CHUNG et al.

Feb. 2, 2017 (43) **Pub. Date:**

### (54) DIELECTRIC FUSE MEMORY CIRCUIT AND OPERATION METHOD THEREOF

(71) Applicant: NATIONAL CHIAO TUNG UNIVERSITY, Hsinchu City (TW)

Inventors: Steve S. CHUNG, Hsinchu City (TW); E-Ray HSIEH, Kaohsiung City (TW);

Zhi-Hong HUANG, Tainan City (TW)

(21) Appl. No.: 15/222,983

(22) Filed: Jul. 29, 2016

### Related U.S. Application Data

(60) Provisional application No. 62/198,666, filed on Jul. 29, 2015.

### **Publication Classification**

(51) Int. Cl. G11C 17/18 (2006.01)H01L 27/112 (2006.01)H01L 23/525 (2006.01) (52) U.S. Cl.

CPC ...... G11C 17/18 (2013.01); H01L 23/5256 (2013.01); **H01L 27/11206** (2013.01)

#### (57)ABSTRACT

This disclosure proposed one kind of one-time programming and repeatably random read integrated circuit memory. The storage device of this memory programs the information by using dielectric-fuse mechanism. The main characteristics of dielectric fuse mechanisms is that by applying an electric field on the dielectrics, the ions or atoms in the dielectrics are drifted-out, or the dielectrics are burned-out, that create damage of the dielectric structure in a form of porosity, and the conductivity (resistivity) of tunneling current through the dielectrics changes the state from high conductivity (resistivity) to low conductivity (resistivity). The dielectric fuse mechanism has been integrated in VLSI circuits, completed the validation, and implemented by the fabrication of CMOS process.

Fig. 1A

Fig. 1B

Fig. 1D

Fig. 1E

1000

1000A

1000B

1000I

1000E

Fig. 16

# DIELECTRIC FUSE MEMORY CIRCUIT AND OPERATION METHOD THEREOF

### RELATED APPLICATIONS

[0001] This application claims priority to U.S. Provisional Application Ser. No. 62/198,666, filed Jul. 29, 2015, which is herein incorporated by reference.

### **BACKGROUND**

[0002] Field of Invention

[0003] The present invention relates to a memory. In particular, the present invention relates to one-time programming and repeatedly random read integrated circuit memory. [0004] Description of Related Art

[0005] One time programming (OTP) memory and multi time programming (MTP) memory have three main kinds as shown below. The first kind memory is a traditional kind memory that metal atomic in the metal connection will be moved due to electromigration when there is a high current, thereby the metal connection is disconnected so as to form fuse-type wire memory. It can be implemented by Al/Cu/ Silicide liner, poly-Si liner, contact via, or metal gate liner. [0006] The second kind memory is that as the thickness of the gate dielectric layer is getting thinner, the breakdown electric field of the dielectric layer becomes lower; and therefore, such breakdown causes the changes of gate dielectric conductivity from low to high so as to form anti-fused type. Compared with metal electro-migration fused breakdown, anti-fused breakdown of the gate dielectric layer is steady in operation and needs lower area per unit cell. Hence, the anti-fused type memory becomes more popular in OTP application.

[0007] The third kind memory is using charge storage. For example, silicon-oxide-nitride-oxide-silicon (SONOS) structure or floating-gate on a MOSFET forms as a flash memory; or using spacers of the poly-Si CMOS stores electric charge for achieving information storage.

[0008] The first kind memory needs large area, high operation current, and its read margin is small. Therefore, the first kind memory is merely suitable for simple code programming. The second kind memory has better retention and does not need additional photomask. Furthermore, the second kind memory does not need special manufacturing process; and therefore its manufacturing cost is low. However, its drawback is charge loss and yields to poor retention.

[0009] In view of the foregoing, problems and disadvantages are associated with existing products that require further improvement. However, those skilled in the art have yet to find a solution.

### **SUMMARY**

[0010] The following presents a simplified summary of the disclosure in order to provide a basic understanding to the reader. This summary is not an extensive overview of the disclosure and it does not identify key/critical elements of the present disclosure or delineate the scope of the present disclosure.

[0011] One aspect of the present disclosure is related to an integrated circuit memory. The integrated circuit memory comprises plural memory cells. Each of the memory cells is connected to at least one decoding line or at least one ground line, and each of the memory cells comprises a first field-effect transistor and a second field-effect transistor. The first

field-effect transistor comprises a first region, a second region and a third region. The third region is connected to the first region and the second region. In addition, the first field-effect transistor further comprises at east one gate dielectric layer and at least one gate electrode layer. At least one gate dielectric layer is disposed on the third region. At least one gate electrode layer is configured to receive and apply an electric signal to the gate dielectric layer, such that the electric signal renders the conduction of the electric signal between the first region and the second region through the third region. The second field-effect transistor comprises a first region, a second region and a third region. The third region is connected to the first region and the second region. Besides, the second field-effect transistor further comprises at least one gate dielectric layer and at least one gate electrode layer. At least one gate dielectric layer is disposed on the third region. At least one gate electrode layer configured to receive and apply the electric signal to the gate dielectric layer, such that the electric signal renders the conduction of the electric signal between the first region and the second region through the third region. Applying the electric signal to the gate dielectric layer of the second field-effect transistor renders the conductivity of the gate dielectric layer from high state to low state and the conductivity of the gate dielectric layer remained unchanged by applying the electric signal to the gate dielectric layer of the second field-effect transistor. The high state and the low state of the gate dielectric layer respectively represent two different storing states of the memory cell.

[0012] According to one embodiment of the present disclosure, at least one gate electrode layer of the second field-effect transistor is connected to the first decoding line. The first region of the second field-effect transistor is connected to or shared with the second region of the first field-effect transistor. The second region of the second field-effect transistor is connected to the ground line. The gate electrode of the first field-effect transistor is connected to the second decoding line. The first region of the first field-effect transistor is connected to the third decoding line. Each of the first field-effect transistor and the second fieldeffect transistor further comprises a ground terminal, and the ground terminal is connected to the ground line of the memory cell. The first field-effect transistors of two adjacent memory cells of the memory cells are connected to the third decoding line. Applying the electric signal to the first decoding line, the second decoding line and the third decoding line renders the first field-effect transistor of one of the memory cells to conduct the electric signal, such that a voltage difference or a current is generated at two terminals of a gate oxide layer of the second field-effect transistor, so as to change the conductivity of the gate dielectric layer of the second field-effect transistor from high state to low state for storing information. Applying the electric signal to the first decoding line, the second decoding line and the third decoding line renders the first field-effect transistor of one of the memory cells to conduct the electric signal, and the intensity of the electric signal is sensed from the first decoding line or the third decoding line which is read as the state of the conductivity of the gate dielectric layer of the second field-effect transistor.

[0013] These and other features, aspects, and advantages of the present disclosure, as well as the technical means and embodiments employed by the present disclosure, will

become better understood with reference to the following description in connection with the accompanying drawings and appended claims.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0014] The disclosure can be more fully understood by reading the following detailed description of the embodiment, with reference made to the accompanying drawings as follows:

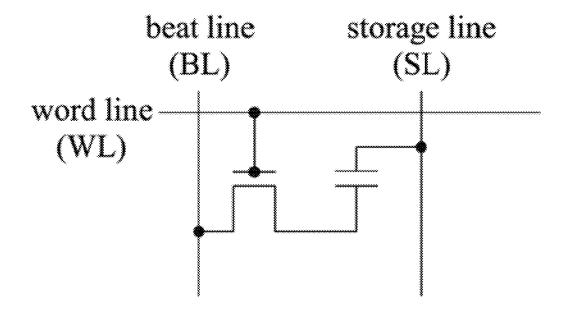

[0015] FIG. 1A is a schematic diagram of an anti-fused type dielectric memory cell according to prior art, wherein the memory cell is consisted of a control transistor (left side) and an anti-fused dielectric component (right side) connected with the control transistor in series.

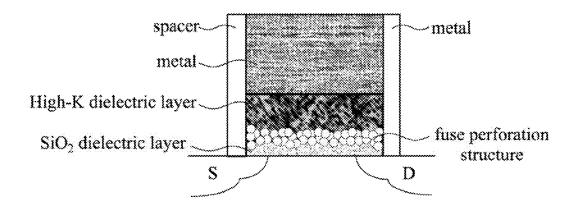

[0016] FIG. 1B is a schematic diagram of a fused type dielectric memory cell according to embodiments of the present disclosure, wherein the memory cell is consisted of a control transistor (left side) and a fused dielectric component (right side) connected with the control transistor in series.

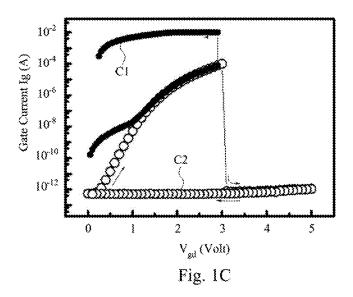

[0017] FIG. 1C is electrical characteristics of an anti-fused type dielectric and a fused type dielectric memory cell from the experiment.

[0018] FIG. 1D is a structure of a fused type dielectric memory cell after dielectric breakdown.

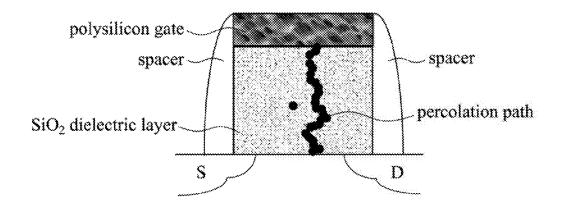

[0019] FIG. 1E is a structure of an anti-fused type dielectric memory cell after dielectric breakdown.

[0020] FIG. 2A is a schematic diagram of an integrated circuit memory according to embodiments of the present disclosure.

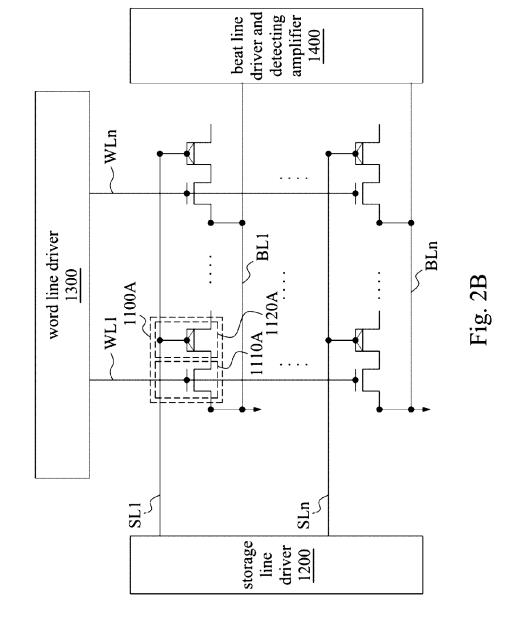

[0021] FIG. 2B is a schematic diagram of an integrated circuit memory according to embodiments of the present disclosure.

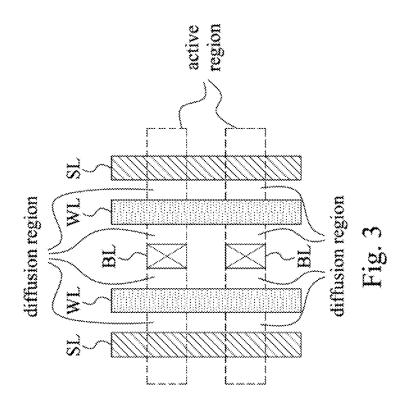

[0022] FIG. 3 is a layout of an integrated circuit memory as shown in FIG. 2A according to embodiments of the present disclosure.

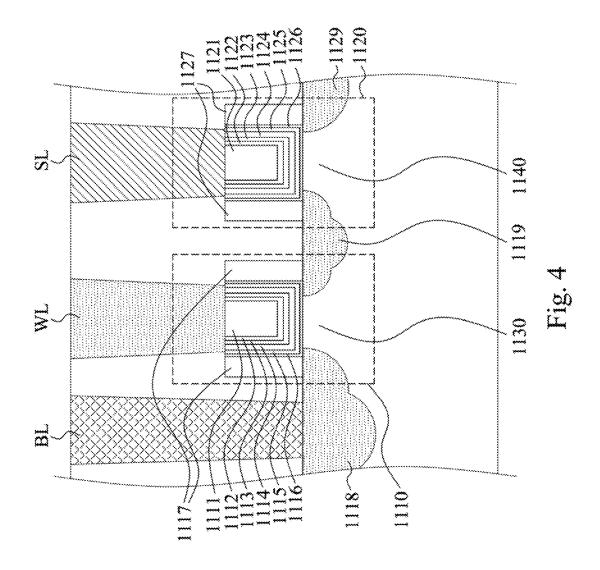

[0023] FIG. 4 is a structure diagram of an integrated circuit memory according to embodiments of the present disclosure.

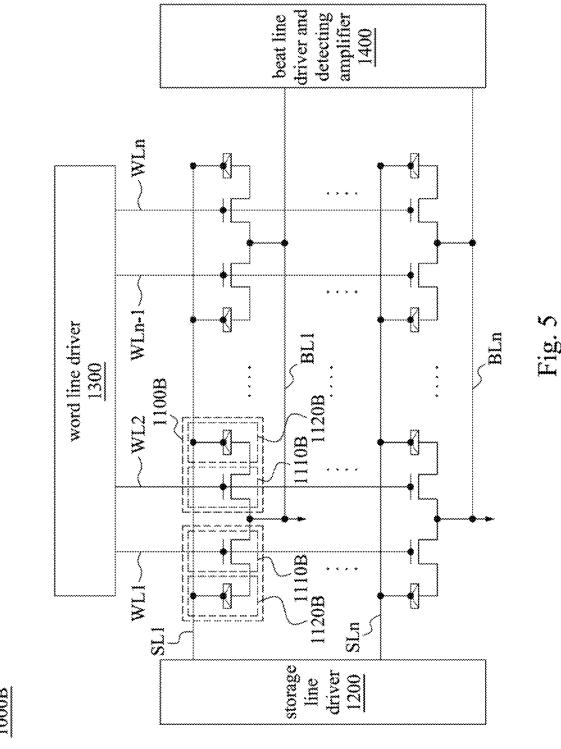

[0024] FIG. 5 is a schematic diagram of an integrated circuit memory according to embodiments of the present disclosure.

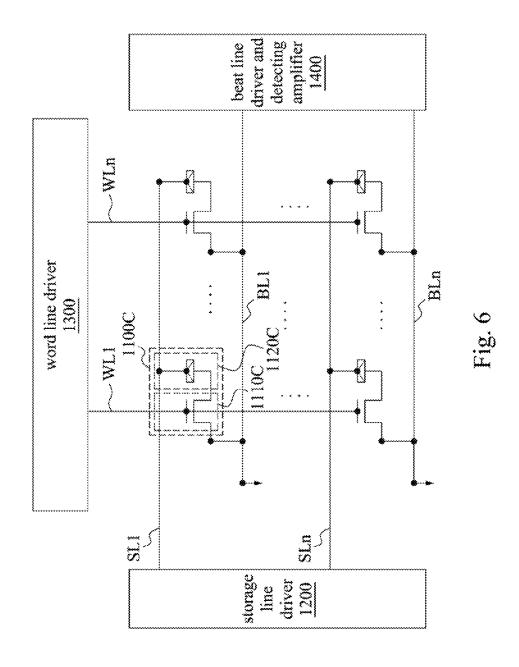

[0025] FIG. 6 is a schematic diagram of an integrated circuit memory according to embodiments of the present disclosure.

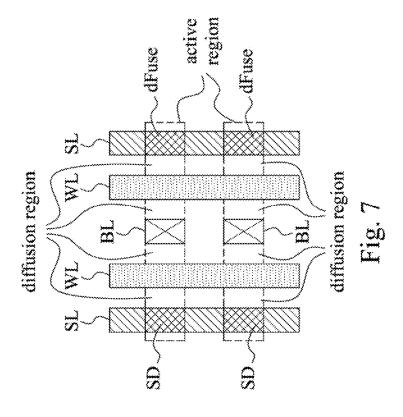

[0026] FIG. 7 is a layout of an integrated circuit memory as shown in FIG. 6 according to embodiments of the present disclosure.

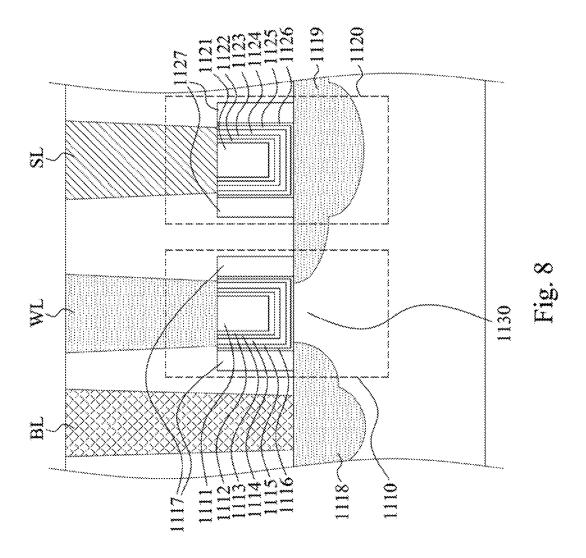

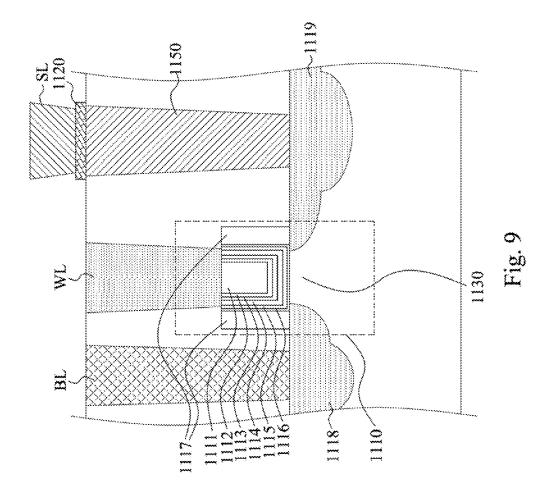

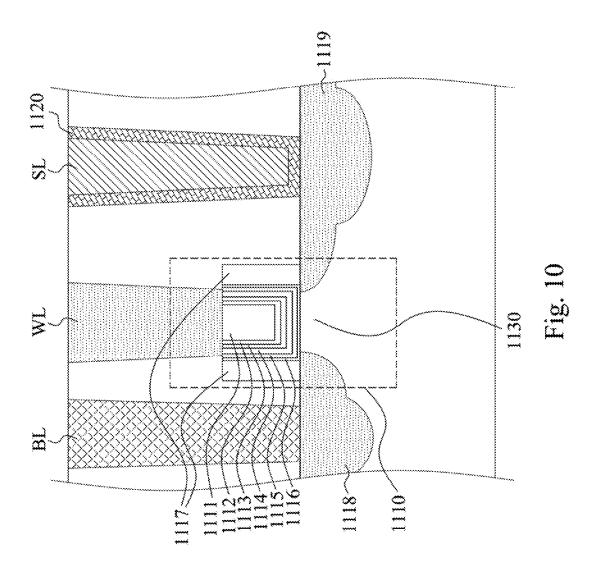

[0027] FIG. 8 is a structure diagram of an integrated circuit memory according to embodiments of the present disclosure

[0028] FIG. 9 is a structure diagram of an integrated circuit memory according to embodiments of the present disclosure.

[0029] FIG. 10 is a structure diagram of an integrated circuit memory according to embodiments of the present disclosure.

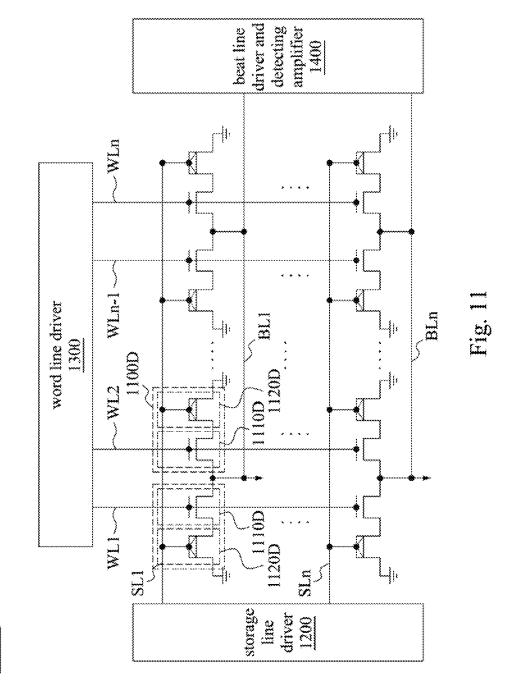

[0030] FIG. 11 is a schematic diagram of an integrated circuit memory according to embodiments of the present disclosure

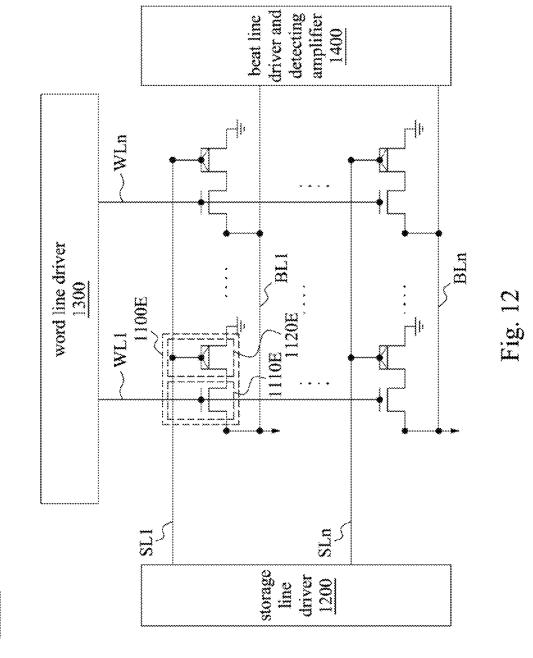

[0031] FIG. 12 is a schematic diagram of an integrated circuit memory according to embodiments of the present disclosure.

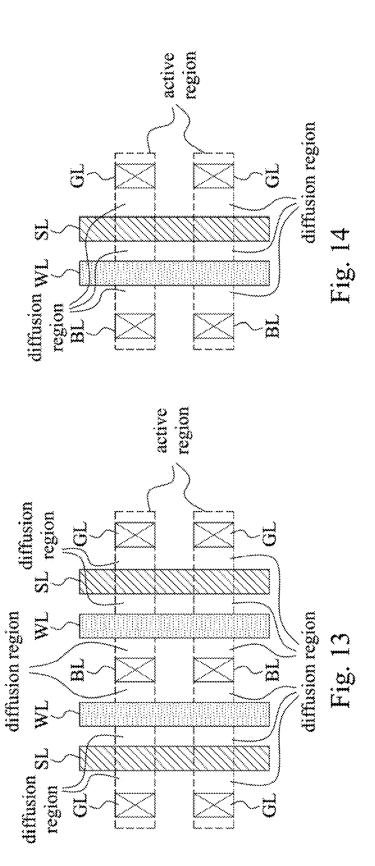

[0032] FIG. 13 is a layout of an integrated circuit memory as shown in FIG. 13 according to embodiments of the present disclosure.

[0033] FIG. 14 is a layout of an integrated circuit memory as shown in FIG. 14 according to embodiments of the present disclosure.

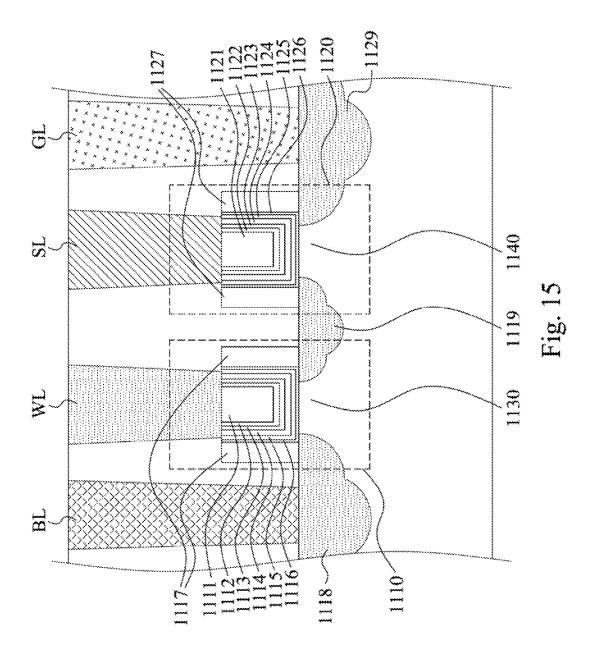

[0034] FIG. 15 is a structure diagram of an integrated circuit memory according to embodiments of the present disclosure.

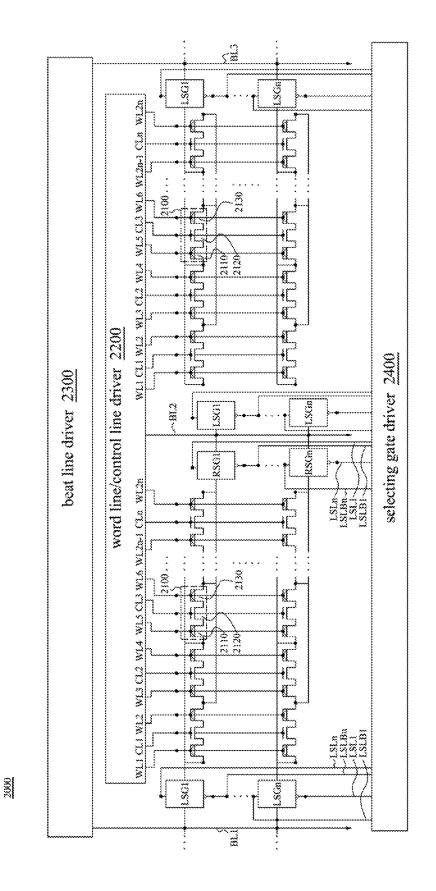

[0035] FIG. 16 is a schematic diagram of an integrated circuit memory according to embodiments of the present disclosure.

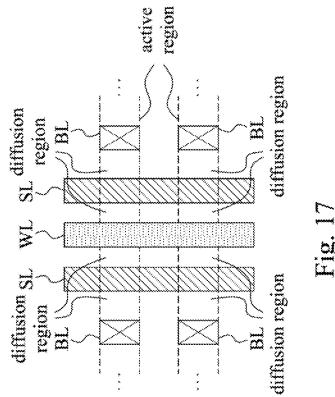

[0036] FIG. 17 is a layout of an integrated circuit memory as shown in FIG. 18 according to embodiments of the present disclosure.

[0037] FIG. 18 is a structure diagram of an integrated circuit memory according to embodiments of the present disclosure.

[0038] In accordance with common practice, the various described features/elements are not drawn to scale but instead are drawn to best illustrate specific features/elements relevant to the present disclosure. Also, wherever possible, similar or the same reference numerals are used in the drawings and the description to refer to the same or similar parts.

### DETAILED DESCRIPTION

[0039] The detailed description provided below in connection with the appended drawings is intended as a description of the present examples and is not intended to represent the only forms in which the present example may be constructed or utilized. The description sets forth the functions of the example and the sequence of steps for constructing and operating the example. However, the same or equivalent functions and sequences may be accomplished by different examples.

**[0040]** Unless otherwise defined herein, scientific and technical terminologies employed in the present disclosure shall have the meanings that are commonly understood and used by one of ordinary skill in the art. Unless otherwise required by context, it will be understood that singular terms shall include plural forms of the same and plural terms shall include singular forms of the same.

[0041] Different from conventional anti-fuse dielectric memory as shown in FIG. 1A, the memory of the present disclosure is basically consisted of two transistors, for example, the memory is composed of a control transistor and a dielectric fuse transistor which is connected in series with the control transistor as shown in FIG. 1B. The main characteristic of dielectric fuse mechanisms is by applying an electric field on the dielectrics, the ions or atoms in the dielectrics are drifted-out or the dielectrics are burned-out, that create damage of the dielectric structure in a form of porosity, and the conductivity (resistivity) of tunneling current through the dielectrics changes the state from high conductivity (low resistivity) to low conductivity (high resistivity), which is regard as a writing operation of a storing component. The foregoing mechanisms are validated by the manufacturing process of the high-k metal gate of the CMOS at the present stage. The characteristics of the fuse electrical property of the memory is shown in FIG. 1C. A pulse with a short time and a voltage higher than a hard breakdown voltage are applied to the gate of the transistor so as to obtain the Ig-Vgd property of the curve C2 with open

circles in FIG. 1C. The change of the current from the gate to drain is from high current to low current (i.e., clockwise). On the contrary, the experiment result of the traditional anti-fused type dielectric memory is as shown by the curve C1. The change of the current from the gate to drain is from low current to high current (i.e. counter clockwise). In addition, referring to FIG. 1C, after the dielectric is antifused, the conductance state of the dielectric is larger and irreversible; and after the dielectric is fused, the conductance state of the dielectric is smaller and irreversible. When the gate dielectric layer of the fuse dielectric transistor of the present disclosure is fused, materials in the dielectric are drifted-out, or the dielectrics are burned-out, thereby porousness is generated in the structure; and therefore, the conduction path from the gate to the transistor is blocked by the porousness, such that the transistor is regarded as an open circuit as shown in FIG. 1D; on the contrary, after the gate dielectric layer of the traditional anti-fused type dielectric transistor anti-fused, the dielectric layer is penetrated by current and forms a conduction path, such that the resistance from the gate to the drain is reduced (the conductance state is enhanced). The gate to the oxide layer of the traditional anti-fused type dielectric transistor forms a leakage path, for example, the circle symbols in FIG. 1E are connected in series to form a percolation path.

[0042] FIG. 2A is a schematic diagram of an integrated circuit memory 1000 according to embodiments of the present disclosure. The integrated circuit memory 1000 is a dielectric fuse one time programming (OTP) integrated circuit memory. The field effect transistor 1110 being regarded as a control component and the field effect transistor 1120 being capable of providing dielectric fuse are connected in series to form the memory cell 1100 of the integrated circuit memory 1000. The word line WL is connected to the gate of one of the field effect transistors 1110 of the memory cell 1100 of the integrated circuit memory 1000. The storage line SL is connected to the gate of one of the field effect transistors 1120 of the memory cell 1100 of the integrated circuit memory 1000. Bit line BL is connected with drains of the field effect transistors 1110 of two adjacent memory cells 1100. In addition, the storage line driver 1200 is connected to and provides electrical signals for the storage line SL, the word line driver 1300 is connected to and provides electrical signals for the word line WL, the Bit line driver and the sense amplifier 1400 is connected to and provides electrical signals for the Bit line

[0043] FIG. 2B is a schematic diagram of an integrated circuit memory 1000A according to embodiments of the present disclosure. The integrated circuit memory 1000A is a dielectric fuse one time programming (OTP) integrated circuit memory. The field effect transistor 1110A being regarded as a control component and the field effect transistor 1120A being capable of providing dielectric fuse is connected in series to form the memory cell 1100A of the integrated circuit memory 1000A. The word line WL is connected to the gate of one of the field effect transistors 1110A of the memory cell 1100A of the integrated circuit memory 1000A. The storage line SL is connected to the gate of one of the field effect transistors 1120A of the memory cell 1100A of the integrated circuit memory 1000A. The Bit line is connected to the drain of one of the field effect transistors 1110A of the memory cell 1100A of the integrated circuit memory 1000A.

[0044] FIG. 3 is a layout of an integrated circuit memory 1000 as shown in FIG. 2A according to embodiments of the present disclosure. As shown in the figure, the diffusion region is within the active region. The word line WL is disposed on the diffusion region perpendicularly. The control component (i.e., the field effect transistor 1110) can be disposed at the intersection of the word line WL and the diffusion region. The storage line SL is adjacent to the word line WL, and disposed on the diffusion region perpendicularly. The storage component (i.e., the field effect transistor 1120) can be disposed at the intersection of the storage line SL and the diffusion region. The Bit line is perpendicular to the diffusion region, the word line WL and the storage line SL, and the Bit line is connected to the diffusion region through the via and the metal plug extended to the middle of two adjacent word lines WL.

[0045] FIG. 4 is a structure diagram of an integrated circuit memory 1000 according to embodiments of the present disclosure. The field effect transistor 1110 being regarded as a control component and the field effect transistor 1120 being regarded as a storing component are connected to form the memory cell 1100 of the integrated circuit memory 1000. The field effect transistor 1110, 1120 can be implemented by High-K metal gate metal-oxidesemiconductor field-effect transistor (HKMG MOSFET). HKMG MOSFET is composed of drain/source 1118/1119/ 1129, tunnel 1130/1140, gate dielectric and gate metal. The drain/source 1118/1119/1129 can conduct electrical signals, the tunnel 1130/1140 is disposed between the drain and the source which can control electrical signal, the gate dielectric is disposed above the tunnel, and the gate metal is disposed above the gate dielectric. The gate dielectric of the HKMG MOSFET is composed of an interfacial layer 1116/1126 and a High-K dielectric layer. The gate metal is composed of three layers. The first layer is a barrier metal layer 1114/ 1124, the second layer is a work function metal layer 1113/1123, and the third layer is a block metal layer 1112/ 1122. The contact metal 1111/1121 is connected to and disposed above the gate metal. The contact metal 1111 of the field effect transistor 1110 is connected to or shared with the word line WL. The contact metal 1141 of the field effect transistor 1120 is connected to or shared with the storage line SL. The drain 1119 of the field effect transistor 1120 is connected to or shared with the source 1119 of the field effect transistor 1110. In addition, the drain 1118 of the field effect transistor 1110 is connected to the Bit line. Furthermore, spacers 1117, 1127 are disposed at bilateral sides of the interfacial layer 1116/1126.

[0046] In one embodiment, if the electric signal is applied to the gate dielectric layer of the field-effect transistor 1120, the conductivity of the gate dielectric layer is changed from high state to low state, and the conductivity of the gate dielectric layer is not changed by applying the electric signal to the gate dielectric layer of the field-effect transistor 1120 again. The high state and the low state of the gate dielectric layer are used for storing information. In another embodiment, the field-effect transistors 1110 of two adjacent memory cells 1100 of the memory cells 1100 of the integrated circuit memory 1000 are connected to the Bit line BL. [0047] In another embodiment, applying the electric signal

to the storage line SL, the word line WL and the Bit line BL renders the field-effect transistor 1110 of one of the memory cells 1100 to conduct the electric signal, such that a voltage difference or a current is generated at two terminals of a gate

oxide layer of the field-effect transistor 1120, so as to change the conductivity of the gate dielectric layer of the field-effect transistor 1120 from high state to low state for storing information. In one embodiment, applying the electric signal to the storage line SL, the word line WL and the Bit line BL render the field-effect transistor 1110 of one of the memory cells 1100 to conduct the electric signal and the intensity of the electric signal is sensed from the storage line SL or the Bit line BL which is read as the state of the conductivity (resistivity) of the gate dielectric layer of the field-effect transistor 1120. In one embodiment, the gate dielectric layer comprises silicon oxide, silicon nitride, silicon oxy-nitride aluminum oxide, aluminum oxy-nitride or high dielectric constant (high-k) material. High-k dielectrics comprise metal oxides, including oxides of Li, Be, Mg, Ca, Sr, Sc, Y, Zr, Hf, Al, La, Ce, Pr, Nd, Sm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb, Lu and mixtures thereof. In another embodiment, the gate dielectric layer of the field-effect transistor is composed of an interfacial layer 1116/1126 and a High-K dielectric layer 1115/1125. The relative dielectric constant of the High-K dielectric layer 1115/1125 is larger than 3.9, and the thickness of the interfacial layer 1116/1126 is less or equal to 7 nanometers. In another embodiment, the gate electrodes of the field-effect transistors 1110, 1120 comprise polycrystalline silicon or comprise metal selected from a group of W, Cu, Ti, Ag, Al, TiAl, TiAlN, TaC, TaCN, TaSiN, Mn, Zr, TiN, WN, TaN, and Ru or combinations thereof. In still another embodiment, the field-effect transistors 1110, 1120 can be n type MOSFET, p type MOSFET, n type junctionless MOSFET, p type junction-less MOSFET, n type Fin-FET, p type FinFET, n type trigate MOSFET, p type trigate MOSFET, n type nanowire MOSFET, or p type nanowire MOSFET.

[0048] FIG. 5 is a schematic diagram of an integrated circuit memory 1000B according to embodiments of the present disclosure. Compared with the field-effect transistor 1120 for providing dielectric fuse in FIG. 2A, the integrated circuit memory 1000B in FIG. 5 is implanted by a storing component 1120B for providing dielectric fuse. FIG. 6 is a schematic diagram of an integrated circuit memory 1000C according to embodiments of the present disclosure. Compared with the field-effect transistor 1120A for providing dielectric fuse in FIG. 2B, the integrated circuit memory 1000C in FIG. 6 is implanted by a storing component 1120C for providing dielectric fuse.

[0049] FIG. 7 is a layout of an integrated circuit memory 1000B as shown in FIG. 5 according to embodiments of the present disclosure. As shown in the figure, the diffusion region is within the active region. The word line WL is disposed on the diffusion region perpendicularly. The control component (i.e., the field effect transistor 1110B) can be disposed at the intersection of the word line WL and the diffusion region. The storage line SL is adjacent to the word line WL, and disposed on the diffusion region perpendicularly. The storing component (i.e., the storing component 1120B) can be disposed at the intersection of the storage line SL and the diffusion region. The Bit line BL is perpendicular to the diffusion region, the word line WL, and the storage line SL, and the Bit line BL is connected to the diffusion region through the via and the metal plug extended to the middle of two adjacent word lines WL.

[0050] FIGS. 8~10 are structure diagrams of integrated circuit memories according to embodiments of the present disclosure. Compared with the structure of the integrated circuit memory in FIG. 4, the disposition of the storage component 1120 of the integrated circuit memory in FIGS. 10-12 are different, which will be described as below. As shown in FIG. 8, the first terminal of the storage component 1120 is connected to the storage line SL, and the second terminal of the storage component 1120 is connected to the second region 1119 of the field-effect transistor 1110. As shown in FIG. 9, the first terminal of the storage component 1120 is connected to the storage line SL, and the second terminal of the storage component 1120 is connected to the second region 1119 of the field-effect transistor 1110 through the contact via 1150. As shown in FIG. 10, the first surface of the storage component 1120 is connected to the storage line SL, and the second surface which is opposite to the first surface of the storage component 1120 is connected to the second region 1119 of the field-effect transistor 1110.

[0051] In one embodiment, the dielectric layer of the storage component 1120 is composed of an interfacial layer 1116/1126 and a High-K dielectric layer 1115/1125. The relative dielectric constant of the High-k dielectric layer 115/1125 is larger than 3.9, and the thickness of the interfacial layer 1116/1126 is less or equal to 7 nanometers. In another embodiment, the dielectric layer comprises silicon oxide, silicon nitride, silicon oxy-nitride, aluminum oxide, aluminum oxy-nitride or high dielectric constant (high-k) material, High-k dielectrics comprise metal oxides, including oxides of Li, Be, Mg, Ca, Sr, Sc, Y, Zr, Hf, Al, La, Ce, Pr, Nd, Sm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb, Lu and mixtures thereof. Applying the electric signal to the dielectric of the storing component 1120 renders the conductivity of the dielectric from high state to low state for storing information thereby writing information into the storing component 1120, and the conductivity of the dielectric is not changed by applying the electric signal to the dielectric of the storing component 1120 again. In addition, the high state and the low state of the dielectric are used for storing information.

[0052] In another embodiment, the storing component 1120 further comprises a first layer portion and a second layer portion. The dielectric of the storing component 1120 is disposed on the first layer portion, and the second layer portion is disposed on the dielectric. The first layer portion can be but not limited to a first electrode or a first interconnect, and the second layer portion can be but not limited to a second electrode or a second interconnect.

[0053] In still another embodiment, the gate electrode layer of the field-effect transistor 1110 is connected to the word line WL, and the first region 1118 of the field-effect transistor 1110 is connected to the Bit line BL. In addition, the field-effect transistor 1110 further comprises a ground terminal (not shown in the figure), and the ground terminal is connected to the ground line (not shown in the figure) of the memory cell 1100.

[0054] Reference is now made to FIGS. 5, 6. In another embodiment, the field-effect transistors 1110B, 1110C of two adjacent memory cells of the memory cells 1100B, 1100C in the integrated circuit memory 1000B, 1000C are connected to the Bit line BL.

[0055] In still another embodiment, applying the electric signal to the storage line SL, the word line WL and the Bit line BL render the field-effect transistor 1110 of one of the memory cells 1100 to conduct the electric signal, such that a voltage difference or a current is generated at two terminals of the storing component 1120, so as to change the conductivity of the dielectric of the storing component 1120 from high state to low state, the conductivity of the storing component 1120 is therefore changed for storing information. In one embodiment, applying the electric signal to the storage line SL, the word line WL and the Bit line BL render the field-effect transistor 1110 of one of the memory cells 1100 to conduct the electric signal, and the intensity of the electric signal is sensed from the storage line SL or Bit line BL which is read as high state or low state of the conductivity of the storing component.

[0056] Referring to table 1 as shown below, it represents operations of the integrated circuit memory 1000, 1000B, 1000C of embodiments in FIGS. 5, 6 of the present disclosure. During programming,  $V_{\it WL}$  voltage is applied to the selected word line WL, 0V (volt) voltage is applied to the unselected word line WL.  $V_{BL}$  voltage is applied to the selected Bit line BL, 0V voltage is applied to the unselected Bit line BL.  $V_{SR}$  voltage is applied to the selected storage line SL, 0V voltage is applied to the unselected storage line SL. If there is a ground line, 0V voltage is applied to the ground line. During reading,  $V_{DD}$  voltage is applied to the selected word line WL, 0V voltage is applied to the unselected word line WL,  $0.1 V_{DD} \sim V_{DD}$  voltage is applied to the selected Bit line BL, 0V voltage is applied to the unselected Bit line L.  $V_{DD}$  voltage is provided to the selected storage line SL, 0V voltage is applied to the unselected storage line SL. If there is a ground line, 0V voltage is applied to the ground line.

[0057] Table 1, Operation Conditions

line WL, and disposed on the diffusion region perpendicularly. The storage component (i.e., the field effect transistor 1120D) can be disposed at the intersection of the storage line SL and the diffusion region. The Bit line BL is perpendicular to the diffusion region, the word line WL, and the storage line SL, and the Bit line BL is connected to the diffusion region through the via and the metal plug extended to the middle of two adjacent word lines WL. In addition, two ground lines GL are adjacent to two storage lines SL, disposed at outer side of the two storage lines SL, and disposed on the diffusion region perpendicularly.

[0060] FIG. 14 is a layout of an integrated circuit memory 1000E as shown in FIG. 12 according to embodiments of the present disclosure. The diffusion region is within the active region. The word line WL is disposed on the diffusion region perpendicularly. The control component (i.e., the field effect transistor 1110E) can be disposed at the intersection of the word line WL and the diffusion region. The storage line SL is adjacent to the word line WL, and disposed on the diffusion region perpendicularly. The storage component (i.e., the field effect transistor 1120E) can be disposed at the intersection of the storage line SL and the diffusion region. The Bit line BL is perpendicular to the diffusion region, the word line WL, and the storage line SL, and the Bit line BL is connected to the diffusion region through the via and the metal plug extended to the middle of two adjacent word lines WL. In addition, the ground line GL is adjacent to the storage line SL, and disposed on the diffusion region perpendicularly.

[0061] FIG. 15 is a structure diagram of an integrated circuit memory according to embodiments of the present disclosure. Compared with the structure of the integrated circuit memory in FIG. 4, the integrated circuit memory in FIG. 15 further has a ground line GL. The ground line GL

|                 |                                                             | conditions |                                                                                                                              |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |            |  |  |  |

|-----------------|-------------------------------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|--|--|--|

|                 | World line                                                  |            | Bit L                                                                                                                        | ine        | Stora                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ground     |            |  |  |  |

| operation       | Selected                                                    | Unselected | Selected                                                                                                                     | Unselected | Selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Unselected | (optional) |  |  |  |

| Program<br>Read | $\begin{array}{c} {\rm V}_{WL} \\ {\rm V}_{DD} \end{array}$ | 0 V<br>0 V | $\begin{array}{c} \mathbf{V}_{BL} \\ 0.1 \ \mathbf{V}_{DD} \hspace{-0.5mm} \sim \hspace{-0.5mm} \mathbf{V}_{DD} \end{array}$ | 0 V<br>0 V | $egin{array}{c} egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}$ | 0 V<br>0 V | 0 V<br>0 V |  |  |  |

[0058] FIG. 11 is a schematic diagram of an integrated circuit memory 1000D according to embodiments of the present disclosure. Compared with the disposition of the field-effect transistor 1120 in FIG. 2A, one terminal of the field-effect transistor 1120D as a storage component in FIG. 11 is grounded. FIG. 12 is a schematic diagram of an integrated circuit memory 1000E according to embodiments of the present disclosure. Compared with the disposition of the field-effect transistor 1120 in FIG. 2A, one terminal of the field-effect transistor 1120E as a storage component in FIG. 12 is grounded.

[0059] FIG. 13 is a layout diagram of an integrated circuit memory 1000D as shown in FIG. 11 according to embodiments of the present disclosure. As shown in the figure, the diffusion region is within the active region. The word line WL is disposed on the diffusion region perpendicularly. The control component (i.e., the field effect transistor 1110D) can be disposed at the intersection of the word line WL and the diffusion region. The storage line SL is adjacent to the word

is disposed above the diffusion region 1129, and connected to the field-effect transistor 1120 through the diffusion region 1129.

[0062] Referring to table 2 as shown below, it represents operations of the integrated circuit memory 1000D, 1000E of embodiments of the present disclosure. During programming,  $V_{WL}$  voltage is provided to the selected word line WL, 0V voltage is provided to the unselected word line WL.  $V_{BL}$ voltage is provided to the selected Bit line BL, 0V voltage is provided to the unselected Bit line BL.  $V_{SR}$  voltage is provided to the selected storage line SL, 0V voltage is provided to the unselected storage line SL. 0V voltage is provided to the ground line. During reading,  $V_{DD}$  voltage is applied to the selected word line WL, 0V voltage is provided to the unselected word line WL.  $0.1 V_{DD} \sim V_{DD}$  voltage is applied to the selected Bit line BL 0V voltage is applied to the unselected Bit line BL. 0V voltage is applied to the selected storage line SL, 0V voltage is also applied to the unselected storage line SL. 0V voltage is applied to the ground line.

[0063] Table 2, Operation Conditions

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | conditions |                                  |            |                        |            |            |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------|------------|------------------------|------------|------------|--|--|--|

|                 | World line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            | Bit L                            | ine        | Storage Line Groun     |            |            |  |  |  |

| operation       | Selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Unselected | Selected                         | Unselected | Selected               | Unselected | line       |  |  |  |

| Program<br>Read | $egin{array}{l} egin{array}{l} egin{array}$ | 0 V<br>0 V | $V_{BL}$ 0.1 $V_{DD}$ ~ $V_{DD}$ | 0 V<br>0 V | V <sub>SR</sub><br>0 V | 0 V<br>0 V | 0 V<br>0 V |  |  |  |

[0064] FIG. 16 is a schematic diagram of an integrated circuit memory 2000 according to embodiments of the present disclosure. The integrated circuit memory 2000 is a dielectric fuse one time programming (OTP) integrated circuit memory. The integrated circuit memory 2000 comprises plural memory pages, and each of the memory pages comprises plural memory cells 2100, a first select device LSG1 and a second select device RSG1. Each of the memory pages is connected to at least one decoding line (i.e., the word line WL, the control line CL or the Bit line BL) or at least one ground line GL (not shown in the figure), and the memory cells 2100 are connected to each other in series. Each of the memory cells 2100 comprises a first field-effect transistor 2110, a second field-effect transistor 2120 and a third field-effect transistor 2130. The field-effect transistors 2110~2130 all comprise a first region, a second region and a third region. The third region is connected to the first region and the second region. The field-effect transistors 2110~2130 further comprise a gate dielectric layer and a gate electrode layer. The gate dielectric layer is disposed on the third region and the gate electrode layer is configured to receive and apply an electric signal to the gate dielectric layer, such that the electric signal renders the conduction of the electric signal between the first region and the second region through the third region.

[0065] The second region of the first field-effect transistor 2110 is connected to or shared with the first region of the second field-effect transistor 2120, the first region of the first field-effect transistor 2110 is connected to the first select device LSG1, and the gate electrode layer of the first field-effect transistor 2110 is connected to one of the word lines WL~WL2n. The first region of the third field-effect transistor 2130 is connected to or shared with the second region of the second field-effect transistor 2120, the second region of the third field-effect transistor 2130 is connected to the second select device RSG1, and the gate electrode layer of the third field-effect transistor 2130 is connected to another one of the word line  $WL\sim WL2n$ . In addition, the word line/control line driver 2200 is connected to and applies the electric signal to the word lines  $WL\sim WL2n$  and the control lines CL~CLn. The Bit line driver 2300 is connected to and applies the electric signal to the Bit lines BL1~BL3, and the selecting gate driver 2400 is connected to and applies the electric signal to the selecting line LSL1 LSLn, LSLB1, LSLBn. The gate electrode layer of the second field-effect transistor 2120 is connected to the control lines CL1~CLn. Each of the first field-effect transistor 2110 the second field-effect transistor 2120 and the third fieldeffect transistor 2130 further comprises a ground terminal (not shown in the figure), and the ground terminal is connected to the ground line (not shown in the figure) of the memory cell 2100. In another embodiment, the first regions of the first field-effect transistors 2110 of two adjacent memory cells of the memory cells 2100 are connected to the first select device LSG1. In still another embodiment, the second regions of the third field-effect transistors 2130 of two adjacent memory cells of the memory cells 2100 are connected to the second select device RSG1. The first select device LSG1 and the second select device RSG1 all comprise a first terminal, a second terminal and a third terminal. The first terminal is connected to the first region of the first field-effect transistor 2110 of one of the memory cells 2100, the second terminal is connected to the Bit line BL, and the third terminal is connected to the selecting line LSL so as to render the transmission of the electric signal between the first terminal and the second terminal of the first select device LSG1 or the second select device RSG1. In another embodiment, each of the first select device LSG1 and the second select device RSG1 comprises a first terminal, a second terminal, a third terminal and a fourth terminal. The first terminal is connected to the first region of the first field-effect transistor 2110 of one of the memory cells 2100, the second terminal is connected to the Bit line BL and the third terminal and the fourth terminal are connected to the selecting line LSL so as to render the transmission of the electric signal between the first terminal and the second terminal of the first select device LSG1 or the second select device RSG1. The first select devices LSG1 or the second select devices RSG1 of two adjacent memory pages of the memory pages are connected to the Bit line BL.

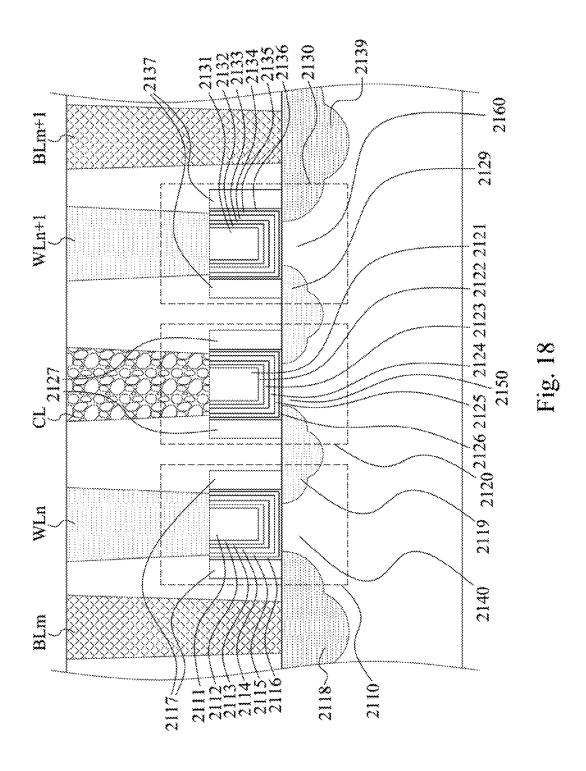

[0066] In one embodiment, each of the gate dielectric layers of field-effect transistors 2110, 2120, 2130 is composed of an interfacial layer 2116/2126/2136 and a High-K dielectric layer 2115/2125/2135. The relative dielectric constant of the High-K dielectric layer 2115/2125/2135 is larger 3.9, and the thickness of the interfacial layer 2116/2126/ 2136 is less than or equal to 7 nanometer. In another embodiment, the gate dielectric layers of the field-effect transistors 2110, 2120, 2130 comprise silicon oxide, silicon nitride, silicon oxy-nitride, aluminum oxide, aluminum oxynitride or high dielectric constant (high-k) material. High-k dielectrics comprise metal oxides, including oxides of Li, Be, Mg, Ca, Sr, Sc, Y, Zr, Hf, Al, La, Ce, Pr, Nd, Sm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb, Lu and mixtures thereof. In still another embodiment, the gate electrodes of the field-effect transistors 2110, 2120, 2130 comprise polycrystalline silicon or comprise metal selected from a group of W, Cu, Ti, Ag, Al, TiAl, TiAlN, TaC, TaCN, TaSiN, Mn, Zr, TiN, WN, TaN, and Ru or combinations thereof. In yet another embodiment, the field-effect transistors 2110, 2120 2130 can be n type MOSFET, p type MOSFET, n type junction-less MOSFET, p type Junction-less MOSFET, n type FinFET, p type FinFET, n type trigate MOSFET, p type trigate MOS-FET, n type nanowire MOSFET, or p type nanowire MOS-

[0067] In yet another embodiment, applying the electric signal to the word line WL, the Bit line BL and the selecting line renders the transmission of the electric signal between the first terminal and the second terminal of the first select device LSG1 and the second select device RSG1, such that a voltage difference or a current is generated at the gate dielectric layer of the first field-effect transistor 2110 or the third field-effect transistor 2130, so as to change the conductivity of the gate dielectric layer of the first field-effect transistor 2110 or the third field-effect transistor 2130 from high state to low state.

[0068] In still another embodiment, applying the electric signal to the control line CL renders the second field-effect transistor 2120 conduct, applying the electric signal to the word line WL (i.e., the word line WL6) renders the third field-effect transistor 2130 conduct, applying the electric signal around reference ground of the integrated circuit memory 2000 to the word line WL (i.e., the word line WL5), applying the electric signal to the Bit line BL1, and the intensity of the electric signal is sensed from the Bit line BL1 which is read as the state of the conductivity of the gate dielectric layer of the first field-effect transistor 2110.

[0069] In yet another embodiment applying the electric signal to the control line CL renders the second field-effect transistor 2120 conduct, applying the electric signal to the word line WL (i.e., the word line WL5) renders the first field-effect transistor 2110 conduct, applying the electric signal around reference ground of the integrated circuit memory 2000 to the WL (i.e., the word line WL6), applying the electric signal to the Bit line BL1, and the intensity of the electric signal is sensed from the Bit line BL1 which is read as the state of the conductivity of the gate dielectric layer of the third field-effect transistor 2130.

[0070] FIG. 17 is a layout diagram of an integrated circuit memory 2000 as shown in FIG. 16 according to embodiments of the present disclosure. As shown in the figure, the diffusion region is within the active region. The word line WL is disposed on the diffusion region perpendicularly. The storage line SL is adjacent to the word line WL, and is disposed on the diffusion region perpendicularly. The Bit line BL is perpendicular to the diffusion region, the word line WL, and the storage line SL, and the Bit line BL is

storing component, and further disposed a Bit line. For example, the integrated circuit memory in FIG. 20 further disposed a field-effect transistor 2110 as a storing component, the first region 2118 thereof is connected to the Bit line BLm, and the second region 2119 thereof is connected to or shared with the first region of the field-effect transistor 2120 which is used as a control component. In addition, the second region of the field-effect transistor 2120 which is used as a control component is connected to or shared with the first region of the field-effect transistor 2130 which is used as a storing component, and the second region of the transistor 130 is connected to the Bit line BLm+1.

[0072] Referring to table 3 as shown below, it represents an operation of the integrated circuit memory 2000 of embodiments of the present disclosure During programming,  $V_{WL}$  voltage is provided to the selected word line WL, and 0V voltage is provided to a word line WL which is adjacent to the selected word line WL. 0V voltage is provided to the unselected word line WL, or the unselected word line WL is floating. 0V voltage is provided to the selected control line CL, or the selected control line CL is floating. 0V voltage is provided to the unselected control line CL.  $V_{\it BL}$  voltage is provided to the selected beat line BL. 0V voltage is provided to a Bit line BL which is adjacent to the selected Bit line BL, or the foregoing Bit line BL is floating. 0V voltage is provided to the unselected Bit line  $BL.\ V_{\it SR}$  voltage is provided to the selected storage line SL,0V voltage is provided to the unselected storage line SL. If there is a ground line, 0V voltage is provided to the ground line. During reading, 0V voltage is provided to the selected word line WL, and  $V_{DD}$  voltage is provided to a word line WL which is adjacent to the selected word line WL. 0V voltage is provided to the unselected word line WL, or the unselected word line WL is floating.  $V_{DD}$  voltage is provided to the selected control line CL, and 0V voltage is provided to the unselected control line CL.  $0.1 V_{DD} \sim V_{DD}$  voltage is provided to the selected Bit line BL, and 0V voltage is provided to a Bit line BL which is adjacent to the selected Bit line BL. 0V voltage is provided to the unselected Bit line  $BL. V_{DD}$  voltage is provided to the selected storage line SL, 0V voltage is provided to the unselected storage line SL. If there is a ground line, 0V voltage is provided to the ground

[0073] Table 3, Operation Conditions

|           | conditions   |                                 |                    |                    |                 |                         |                                 |     |              |                 |                      |

|-----------|--------------|---------------------------------|--------------------|--------------------|-----------------|-------------------------|---------------------------------|-----|--------------|-----------------|----------------------|

|           | World line   |                                 |                    | Control line       |                 |                         | Bit Line                        |     | Storage Line |                 | •                    |

| operation | Selected,    | Neighborhood,<br>n + 1 or n - 1 | Unse-<br>lected    | Selected           | Unse-<br>lected |                         | Neighborhood,<br>n + 1 or n - 1 |     | Selected     | Unse-<br>lected | Ground<br>(optional) |

| Program   | $V_{\it WL}$ | 0 V                             | 0 V or<br>floating | 0 V or<br>floating | 0 V             | $V_{BL}$                | 0 V or<br>floating              | 0 V | $V_{SR}$     | 0 V             | 0 V                  |

| Read      | 0 V          | $V_{DD}$                        | 0 V or<br>floating | VDD                | 0 V             | 0.1 $V_{DD}$ ~ $V_{DD}$ |                                 | 0 V | $V_{D\!D}$   | 0 V             | 0 V                  |

connected to the diffusion region through the via and the metal plug extended to the middle of two adjacent word lines WL.

[0071] FIG. 18 is a structure diagram of an integrated circuit memory according to embodiments of the present disclosure. Compared with the structure of the integrated circuit memory in FIG. 4, the integrated circuit memory in FIG. 18 is further disposed a field-effect transistor as a

[0074] In view of the above embodiments of the present disclosure, it is apparent that the application of the present disclosure has the advantages as follows:

[0075] 1. Compared with the traditional fuse-type wire memory, the integrated circuit memory of the present disclosure merely needs extremely low operating current, lower area per unit memory, and read/write ability of the integrated circuit memory of the present disclosure is stable;

[0076] 2. Compared with dielectric anti-fuse type memory, the integrated circuit memory of the present disclosure has a stable operation margin, excellent data retention, lower area per unit memory, lower noise, lower electrical disturbance, and lower dynamic power consumption; [0077] 3. Compared with traditional charge storage memory, the manufacturing process of the integrated circuit memory of the present disclosure is simple, additional photomask does not need in such manufacturing process, data retention is better, and the manufacturing cost is low. [0078] Although the present disclosure has been described in considerable detail with reference to certain embodiments thereof, other embodiments are possible. Therefore, the spirit and scope of the appended claims should not be limited to the description of the embodiments contained herein.

[0079] It will be apparent to those skilled in the art that various modifications and variations can be made to the structure of the present disclosure without departing from the scope or spirit of the disclosure. In view of the foregoing, it is intended that the present disclosure cover modifications and variations of this disclosure provided they fall within the scope of the following claims.

What is claimed is:

- 1. An integrated circuit memory, comprising:

- plural memory cells, wherein each of the memory cells is connected to at least one decoding line or at least one ground line, and each of the memory cells comprises:

- a first field-effect transistor, comprising:

- a first region a second region and a third region, wherein the third region is connected to the first region and the second region;

- at least one gate dielectric layer being disposed on the third region; and

- at least one gate electrode layer being configured to receive and apply an electric signal to the gate dielectric layer, such that the electric signal renders the conduction of the electric signal between the first region and the second region through the third region; and

- a second field-effect transistor, comprising:

- a first region a second region and a third region, wherein the third region is connected to the first region and the second region;

- at least one gate dielectric layer being disposed on the third region; and

- at least one gate electrode layer being configured to receive and apply the electric signal to the gate dielectric layer, such that the electric signal renders the conduction of the electric signal between the first region and the second region through the third region;

- wherein applying the electric signal to the gate dielectric layer of the second field-effect transistor renders the conductivity of the gate dielectric layer from high state to low state, and the conductivity of the gate dielectric layer is not changed by applying the electric signal to the gate dielectric layer of the second field-effect transistor, wherein the high state and the low state of the gate dielectric layer respectively represent two different storing states of the memory cell.

- 2. The integrated circuit memory of claim 1, wherein at least one gate electrode layer of the second field-effect transistor is connected to a first decoding line, and the first

- region of the second field-effect transistor is connected to or shared with the second region of the first field-effect transistor.

- 3. The integrated circuit memory of claim 2, wherein the second region of the second field-effect transistor is connected to a fourth decoding line.

- 4. The integrated circuit memory of claim 2, wherein the gate electrode layer of the first field-effect transistor is connected to a second decoding line, and the first region of the first field-effect transistor is connected to a third decoding line, wherein each of the first field-effect transistor and the second field-effect transistor comprises a ground terminal, and the ground terminal is connected to the ground line of the memory cell.

- 5. The integrated circuit memory of claim 4, wherein the first field-effect transistors of two adjacent memory cells of the memory cells are connected to the third decoding line.

- 6. The integrated circuit memory of claim 1, wherein when the gate dielectric layer of the second field-effect transistor comprises one dielectric layer, the relative permittivity of the dielectric layer is less than or equal to 10; when the gate dielectric layer of the second field-effect transistor comprises plural dielectric layers, the relative permittivity of one of the dielectric layers is less than sir equal to 10 and the relative permittivities of the other the dielectric layers are larger than the relative permittivities of the one dielectric layer.

- 7. The integrated circuit memory of claim 5 wherein applying the electric signal to the first decoding line, the second decoding line and the third decoding line renders the first field-effect transistor of one of the memory cells to conduct the electric signal, such that a voltage difference or a current is generated at two terminals of a gate oxide layer of the second field-effect transistor, so as to change the conductivity of the gate dielectric layer of the second field-effect transistor from high state to low state for storing information.

- 8. The integrated circuit memory of claim 7, wherein applying the electric signal to the first decoding line, the second decoding line and the third decoding line renders the first field-effect transistor of one of the memory cells to conduct the electric signal, and the intensity of the electric signal is sensed from the first decoding line or the third decoding line which is read as the state of the conductivity of the gate dielectric layer of the second field-effect transistor.

- 9. The integrated circuit memory of claim 5, wherein applying the electric signal to the first decoding line and a fourth decoding line renders a voltage difference is generated at two terminals of the gate dielectric layer of the second field-effect transistor, so as to change the conductivity of the gate dielectric layer of the second field-effect transistor from high state to low state, the conductivity of the gate dielectric layer of the second field-effect transistor is therefore changed for storing information, wherein the electrical level of the electric signal of the fourth decoding line which is connected to the memory cell is about the electrical level of the first decoding line, is about the reference ground of the integrated circuit memory, or is floating.

- 10. The integrated circuit memory of claim 9, wherein applying the electric signal to the second decoding line and the third decoding line renders the first field-effect transistor of one of the memory cells to conduct the electric signal, applying the electric signal around reference ground to the

first decoding line and the fourth decoding line, and the intensity of the electric signal is sensed from the third decoding line or the fourth decoding line which is read as the state of the conductivity of the gate dielectric layer of the second field-effect transistor.

- 11. An integrated circuit memory, comprising:

- plural memory cells, wherein each of the memory cells is connected to at least one decoding line or at least one ground line, and each of the memory cells comprises:

- a field-effect transistor, comprising:

- a first region, a second region and a third region, wherein the third region is connected to the first region and the second region;

- at least one gate dielectric layer being disposed on the third region; and

- at least one gate electrode layer being configured to receive and apply an electric signal to the gate dielectric layer, such that the electric signal renders the conduction of the electric signal between the first region and the second region through the third region; and

- a storing component, comprising:

- at least one dielectric, applying the electric signal to at least one dielectric of the storing component renders the conductivity of the at least one dielectric from high state to low state for writing information into the storing component, wherein the conductivity of the at least one dielectric is not changed by applying the electric signal to the at least one dielectric of the storing component, wherein the high state and the low state of the dielectric respectively represent two different storing states of the memory cell.

- 12. The integrated circuit memory of claim 11, wherein the storing component further comprises:

- a first layer portion, wherein the at least one dielectric of the storing component is disposed on the first layer portion; and

- a second layer portion being disposed on the at least one dielectric;

- wherein the first layer portion is a first electrode or a first interconnect, and the second layer portion is a second electrode or a second interconnect.

- 13. The integrated circuit memory of claim 12, wherein the first electrode, the second electrode, the first interconnect and the second interconnect are selected from the group consisting of metal nitride metal silicide, metal polycrystal-line silicide and a combination thereof.

- 14. The integrated circuit memory of claim 11, wherein a first terminal of the storing component is connected to a first decoding line, and a second terminal of the storing component is connected to the second region of the field-effect transistor.

- 15. The integrated circuit memory of claim 14, wherein the gate electrode layer of the field-effect transistor is connected to a second decoding line, the first region of the field-effect transistor is connected to a third decoding line, the field-effect transistor further comprises a ground terminal, and the ground terminal is connected to the ground line of the memory cell.

- 16. The integrated circuit memory of claim 15, wherein the field-effect transistors of two adjacent memory cells of the memory cells are connected to the third decoding line.

- 17. The integrated circuit memory of claim 11, wherein when the storing component comprises one dielectric layer,

the relative permittivity of the dialelectric layer is less than or equal to 10 and the thickness of the dielectric layer is less than or equal to 3 nanometers; when the storing component comprises plural dielectric layers, the relative permittivity of one of the dielectric layers is less than or equal to 10, and each of the relative permittivities of the other dielectric layers is larger than the relative permittivities of the one dielectric layer.

- 18. The integrated circuit memory of claim 15, wherein applying the electric signal to the first decoding line, the second decoding line and the third decoding line renders the field-effect transistor of one of the memory cells to conduct the electric signal, such that a voltage difference or a current is generated at two terminals of the storing component, so as to hangs the conductivity of the at least one dielectric of the storing component from high state to low state the conductivity of the storing component is therefore changed for storing information.

- 19. The integrated circuit memory of claim 18 wherein applying the electric signal to the first decoding line, the second decoding line and the third decoding line renders the field-effect transistor of one of the memory cells to conduct the electric signal, and the intensity of the electric signal is sensed from the first decoding line or the third decoding line which is read as high state or low state of the conductivity of the storing component.

- 20. An integrated circuit memory, comprising:

- plural memory pages, wherein each of the memory pages comprises plural memory cells, a first select device and a second select device, wherein each of the memory pages is connected to at least one decoding line or at least one ground line, the memory cells is connected to each other in series, and each of the memory cells comprises:

- a first field-effect transistor, comprising:

- a first region, a second region and a third region, wherein the third region is connected to the first region and the second region;

- at least one gate dielectric layer being disposed on the third region; and

- at least one gate electrode layer being configured to receive and apply an electric signal to the gate dielectric layer, such that the electric signal renders the conduction of the electric signal between the first region and the second region through the third region;

- a second field-effect transistor, comprising:

- a first region, a second region and a third region, wherein the third region is connected to the first region and the second region;

- at least one gate dielectric layer being disposed on the third region; and