# High-Performance Poly-Si Thin-Film Transistors With L-Fin Channels

Yi-Hsien Lu, Po-Yi Kuo, Member, IEEE, Je-Wei Lin, Yi-Hong Wu, Yi-Hsuan Chen, and Tien-Sheng Chao

Abstract—For the first time, we construct poly-Si thin-film transistors (TFTs) with novel L-shaped poly-Si fin channels (poly-Si TFTs with L-fin channels, called LFin-TFTs). The L-fin channels of LFin-TFTs are similar to the multiple-gated fin channels of FinFETs. The LFin-TFTs exhibit a low supply gate voltage (3 V), a good subthreshold swing (SS)  $\sim$ 190 mV/dec, and a high on/off current ratio  $(I_{\rm ON}/I_{\rm OFF})>10^6~(V_D=1~{\rm V})$  without hydrogen-related plasma treatments. After Ni salicidation, the devices exhibit steep SS  $\sim$  148 mV/dec and  $I_{\rm ON}/I_{\rm OFF}\sim10^7$ . After NH $_3$  plasma treatment, the characteristics of the devices are further improved. The LFin-TFTs have steeper SS  $\sim$  132 mV/dec, higher  $I_{\rm ON}/I_{\rm OFF}>10^7$ , and threshold voltage  $(V_{\rm TH})\sim0.036~{\rm V}.$

Index Terms—FinFETs, L-fin, multiple gate,  $NH_3$  plasma, Ni salicidation, poly-Si thin-film transistors (TFTs).

# I. INTRODUCTION

ETTER gate electrostatic control of the channel potential **B** in nonplanar device structures has been a research goal for more than a decade [1]-[4]. To this end, multiple-gated metal-oxide-semiconductor field-effect transistor architectures such as FinFETs are expected to be used beyond the 22-nm technology node due to their excellent short-channel effect (SCE) immunity [5]. From a transistor variation and mismatch perspective, FinFETs are considered particularly suitable for further static random access memory (SRAM) scaling, owing to their improved SCE behavior and lower channel doping concentration [6]. Compared to conventional planar transistors, FinFETs with double gates are a promising architecture [7] for further scaling. Recently, high-performance low-temperature poly-Si thin-film transistors (TFTs) have been developed for the employment of active-matrix liquid crystal displays on a glass substrate and for driving integrated circuits (ICs) for the applications of system-on-panel (SOP) and the 3-D IC elements such as SRAM and dynamic random access memory [8]–[10].

Furthermore, high-speed display driving circuits require TFTs to operate at low voltages and high driving currents, with a low threshold voltage  $(V_{\rm TH})$ . In this letter, we demonstrate poly-Si TFTs with novel L-fin channels (LFin-TFTs) without the use of advanced lithographic tools. High-performance LFin-

Manuscript received July 6, 2011; accepted October 30, 2011. Date of publication December 6, 2011; date of current version January 27, 2012. This work was supported by the National Science Council, Taiwan, under Contract NSC-100-2221-E-009-012-MY3. The review of this letter was arranged by Editor W. S. Wong.

The authors are with the Department of Electrophysics, National Chiao Tung University, Hsinchu 30010, Taiwan (e-mail: yihsienlu@gmail.com; Kuopoyi. ee91g@gmail.com; hpmax1981.ep96g@nctu.edu.tw; honghong5023@gmail.com; Hoptrains@gmail.com; tschao@mail.nctu.edu.tw).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2011.2175357

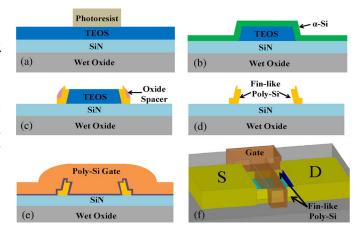

Fig. 1. (a)–(e) Key process flows of the LFin-TFTs and (f) 3-D schematic structure of the LFin-TFTs.

TFTs with low  $V_{\rm TH}$ , good subthreshold swing (SS), and high on/off current ratio  $(I_{\rm ON}/I_{\rm OFF})$  can be obtained. These hold great promise for the realization of SOP and 3-D IC.

### II. EXPERIMENT

The key process steps are shown in Fig. 1. The LFin-TFTs were built on Si wafers capped with a 500-nm thermal oxide layer. Si<sub>3</sub>N<sub>4</sub> (150 nm)/tetraethoxysilane (TEOS) (150 nm) dummy structures were then deposited by lowpressure chemical vapor deposition (LPCVD) [Fig. 1(a)]. The TEOS was patterned and overetched to the Si<sub>3</sub>N<sub>4</sub> in the dry etching step, and a 45-nm-thick amorphous Si (a-Si) layer was deposited by LPCVD at 500 °C [Fig. 1(b)]. Next, the a-Si layer was crystallized by solid-phase crystallization at 600 °C for 24 h in a N<sub>2</sub> ambient. After TEOS spacer was formed, the S/D region patterns were then defined by an I-line stepper. The S/D and the poly-Si L-fin channels were fabricated by anisotropic selective dry etching [Fig. 1(c)], and the TEOS dummy layer and spacer were removed using dilute HF solution [Fig. 1(d)]. The TEOS dummy layer and spacer protected the sidewalls of the L-fin channel during dry etching. A 10-nm-thick LPCVD TEOS oxide layer and an in situ doped  $n^+$  poly-Si gate with a thickness of 250 nm were then deposited [Fig. 1(e)]. After gate patterning by dry etching step, the  $n^+$  S/D regions were implanted with arsenic (As<sup>+</sup>; 25 keV at  $5 \times 10^{15}$  cm<sup>-2</sup>) and activated at 600 °C in a N2 ambient. Fig. 1(f) shows the 3-D schematic structure of the LFin-TFTs. For comparison, the LFin-TFTs with Ni salicidation (called LFin-Ni) were achieved by rapid thermal annealing at 450 °C for 30 s, and

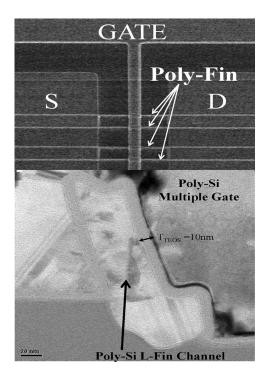

Fig. 2. SEM and cross-sectional TEM images of gate-stacked L-fin channels. the same devices with further NH<sub>3</sub> plasma treatments (called LFin-Ni-NH<sub>3</sub>) were also constructed.

## III. RESULT AND DISCUSSION

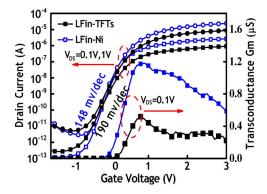

The scanning electron microscope (SEM) and cross-sectional transmission electron microscope (TEM) images of gatestacked L-fin channels are shown in Fig. 2. The L-fin channels are surrounded by TEOS gate oxide and poly-Si gate resulting in multiple-gated LFin-TFTs. The height and thickness of the L-fin channels are about 200 and 45 nm, respectively. In this work, we measured the electric characteristics of LFin-TFTs with a channel length of 0.35  $\mu$ m ( $N_{\rm Fin}=2$ ; effective channel width  $\sim 0.3 \times 2 = 0.6 \ \mu \text{m}$ ). We fabricated the TEOS spacer as small as possible to approach the ideal fin. When the height of L-fin is great enough, the spacer variation can be improved by a smaller spacer size. The 3-D L-fin channels were fabricated without use of advanced lithographic tools by simple and low-cost processes. Fig. 3 shows the transfer characteristics of LFin-TFTs and LFin-Ni. The LFin-TFTs without hydrogenrelated plasma treatments exhibit low  $V_{\rm TH} \sim 0.26$  V and good  $SS \sim 190 \text{ mV/dec}$  due to the multiple-gated structure. On the other hand, the ON-state currents and transconductance (Gm)of LFin-Ni are higher than those of LFin-TFTs due to the reduction in S/D parasitic resistance [11], while the SS of the LFin-Ni is steeper. Furthermore, the small drain-induced barrier lowering (DIBL) of LFin-Ni during device operation can be attributed to the multiple-gated L-fin channel structure, which offers good gate controllability.

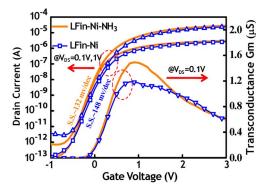

Fig. 4 shows the transfer characteristics of LFin-Ni-NH<sub>3</sub> and LFin-Ni. The characteristics of LFin-Ni-NH<sub>3</sub> are further improved by NH<sub>3</sub> plasma treatment, including SS,  $I_{\rm ON}/I_{\rm OFF}$  ( $I_{\rm OFF}<10^{-12}$  at  $V_D=1$  V), and DIBL. Those improvements can be attributed to the hydrogen passivation of the defect

Fig. 3. Transfer characteristics of LFin-TFTs and LFin-Ni. The well-behaved transfer characteristics of the LFin-Ni are due to the reduction in S/D parasitic resistance.

Fig. 4. Transfer characteristics of LFin-Ni-NH $_3$  and LFin-Ni. The well-behaved transfer characteristics for the LFin-Ni-NH $_3$  are illustrated.

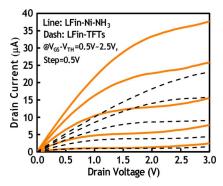

Fig. 5. Output characteristics of LFin-Ni-NH $_3$  and LFin-TFTs. The LFin-Ni-NH $_3$  devices exhibit higher driving currents.

states, the nitrogen pileup at SiO<sub>2</sub>/poly-Si interface, and the strong Si–N bond formation that terminates the dangling bonds in the grains and at the grain boundaries in the poly-Si channels [12]. The LFin-TFTs have a multiple-gated L-fin channel structure similar to single-crystal FinFETs, but additional hydrogen-related plasma treatments are required to improve the characteristics of the 45-nm-thick poly-Si L-fin channel. Nevertheless, the hydrogen-related plasma treatments are unnecessary in our previous work with sub-10-nm Si nanowire (NW) channel [13]. The characteristics of nanoscaled NW devices with different plasma treatment times are identical. We argue that the thickness and size of the poly-Si channels are the key points for future nanoscaled poly-Si TFTs.

TABLE I

COMPARISON OF IMPORTANT PARAMETERS OF THE L-FIN DEVICES IN

THIS RESEARCH WITH HIGH-PERFORMANCE TFTS INVESTIGATED

IN OTHER RESEARCH STUDIES

|                                                         |                          | LFin                       |                                      | LFin-Ni                   |                            | LFin-Ni-NH <sub>3</sub>  |                          |  |

|---------------------------------------------------------|--------------------------|----------------------------|--------------------------------------|---------------------------|----------------------------|--------------------------|--------------------------|--|

| V <sub>TH</sub> (V)                                     |                          | ~0.26                      |                                      | 0.16                      |                            | 0.036                    |                          |  |

| S.S. (mV/dec)                                           |                          | 190                        | 190                                  |                           | 148                        |                          | 132                      |  |

| I <sub>ON</sub> /I <sub>OFF</sub> (V <sub>DD</sub> =1V) |                          | >10 <sup>6</sup>           | >10 <sup>6</sup> 8.6x10 <sup>6</sup> |                           | >10 <sup>7</sup>           |                          | >10 <sup>7</sup>         |  |

| DIBL (mV/V)                                             |                          | 99                         | 47                                   |                           |                            | 20                       |                          |  |

|                                                         | This Work                | [14]                       |                                      | [15]                      | [16]                       |                          | [17]                     |  |

| Structure                                               | Fin-like                 | High-k<br>MG               |                                      | Nanowire                  | Nanowire                   |                          | DSSB                     |  |

| Channel                                                 | SPC                      | SPC                        | SPC                                  |                           | SPC                        |                          | SPC                      |  |

| Gate Stack                                              | Poly-Si / Si             | D <sub>2</sub> TaN / HfSiG | o <sub>x</sub>                       | Poly-Si/ SiO <sub>2</sub> | Poly-Si / SiO <sub>2</sub> |                          | Poly-Si / HfO₂           |  |

| W/L<br>(µm/µm)                                          | 0.6/0.35                 | 150/0.3                    | 3 0.13/1                             |                           | 0.035/0.03                 |                          | 0.02/0.09                |  |

| V <sub>TH</sub><br>(V)                                  | 0.036                    | 0.75                       |                                      | 0.6~0.76                  | 0.97                       |                          | 1.162                    |  |

| EOT<br>(nm)                                             | 10                       | 2.8                        |                                      | 25                        | 25                         |                          | T <sub>Hf02</sub> =20    |  |

| S.S.<br>(mV/dec)                                        | 132                      | 193                        |                                      | 209                       | 224                        |                          | 113                      |  |

| DIBL<br>(mV/V)                                          | 20                       | 80                         |                                      | 20                        | 895                        |                          | 254                      |  |

| I <sub>ON</sub> /I <sub>OFF</sub><br>(V <sub>DD</sub> ) | >10 <sup>7</sup><br>(1V) |                            |                                      |                           |                            | >10 <sup>7</sup><br>(1V) | >10 <sup>7</sup><br>(1V) |  |

The output characteristics of LFin-Ni-NH<sub>3</sub> and LFin-TFTs are compared in Fig. 5. After Ni salicidation and NH<sub>3</sub> plasma treatment, the improvement of saturation currents ( $\sim 37.7 \,\mu\text{A}$ ) over the LFin-TFTs ( $\sim 23~\mu A$ ) is about 63% at  $V_G - V_{TH} =$ 2.5 V and  $V_D = 3$  V. The LFin-Ni-NH<sub>3</sub> devices exhibit higher driving currents than the LFin-TFTs due to their extra Nisalicidation and NH<sub>3</sub> plasma treatment processes. In addition, we show the extracted parameters of the LFin-TFTs, LFin-Ni, and LFin-Ni-NH<sub>3</sub> at the top part of Table I. We also present a comparison of several important parameters of the LFin-Ni-NH<sub>3</sub> with high-performance TFTs investigated in other research studies [14]–[17] at the bottom part of Table I. Compared to planar TFTs with high- $\kappa$  gate dielectric, as shown in Table I [14], [17], the LFin-Ni-NH3 devices show a lower  $V_{\mathrm{TH}}$ , a lower SS, and improved DIBL with thicker equivalent oxide thickness. The highly improved performances of the LFin-Ni-NH<sub>3</sub> can be attributed to the employment of a double-gate structure which provides higher gate controllability. Compared to the TFTs with a NW structure [15], [16], the LFin-Ni-NH<sub>3</sub>devices have good SS and comparable DIBL, using a simpler process.

### IV. CONCLUSION

High-performance poly-Si TFTs with novel L-fin channel structure have been constructed and investigated in this research. Compared with FinFETs, the LFin-TFT processes are simpler and have lower cost. The S/D parasitic resistance can be reduced by the Ni salicidation. Additional NH $_3$  plasma treatment was adopted to effectively passivate the defects and interface states in LFin-TFTs. The well-behaved electric characteristics (low off-leakage currents, good SS, improved DIBL, and high  $I_{\rm ON}/I_{\rm OFF}$ ) simultaneously achieved in the

LFin-TFTs are the result of the multiple-gated L-fin channel structure. These high-performance LFin-TFTs appear to be promising for future applications in SOP and 3-D IC.

## ACKNOWLEDGMENT

The authors would like to thank the National Nano Device Laboratories and the Nano Facility Center of the National Chiao Tung University, Hsinchu, Taiwan, for the process support.

### REFERENCES

- [1] B. Doyle, B. Boyanov, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, R. Rios, and R. Chau, "Tri-gate fully-depleted CMOS transistors: Fabrication, design and layout," in *VLSI Symp. Tech. Dig.*, 2003, pp. 133–134.

- [2] J. Chen, T. Saraya, and T. Hiramoto, "Mobility enhancement over universal mobility in (100) silicon nanowire gate-all-around MOSFETs with width and height of less than 10 nm range," in VLSI Symp. Tech. Dig., 2010, pp. 175–176.

- [3] J. T. Park and J. P. Colinge, "Multiple-gate SOI MOSFETs: Device design guidelines," *IEEE Trans. Electron Devices*, vol. 49, no. 12, pp. 2222–2229, Dec. 2002.

- [4] H. Lee, L. E. Yu, S. W. Ryu, J. W. Han, K. Jeon, D. Y. Jang, K. H. Kim, J. Lee, J. H. Kim, S. C. Jeon, G. S. Lee, J. S. Oh, Y. C. Park, W. H. Bae, H. M. Lee, J. M. Yang, J. J. Yoo, and Y. K. Choi, "Sub-5 nm all around gate FinFET for ultimate scaling," in VLSI Symp. Tech. Dig., 2006, pp. 58–59.

- [5] J. Kavalieros, B. Doyle, S. Datta, G. Dewey, M. Doczy, B. Jin, D. Lionberger, M. Metz, W. Rachmady, M. Radosavljevic, U. Shah, N. Zelick, and R. Chau, "Tri-gate transistor architecture with high-k gate dielectrics, metal gates and strain engineering," in VLSI Symp. Tech. Dig., 2006, pp. 50–51.

- [6] C. H. Lin, W. Haensch, P. Oldiges, H. Wang, R. Williams, J. Chang, M. Guillorn, A. Bryant, T. Yamashita, T. Standaert, H. Bu, E. Leobandung, and M. Khare, "Modeling of width-quantization-induced variations in logic FinFETs for 22 nm and beyond," in VLSI Symp. Tech. Dig., 2006, pp. 58–59.

- [7] H. S. P. Wong, D. J. Frank, P. M. Solomon, C. H. J. Wann, and J. J. Welser, "Nanoscale CMOS," *Proc. IEEE*, vol. 87, no. 4, pp. 537–570, Apr. 1999.

- [8] Y. Oana, "Current and future technology of low-temperature poly-Si TFT-LCDs," J. Soc. Inf. Disp., vol. 9, no. 3, pp. 169–172, 2001.

- [9] F. Hayashi, H. Ohkubo, T. Takahashi, S. Horiba, K. Noda, T. Uchida, T. Shimizu, N. Sugawara, and S. Kumashiro, "A highly stable SRAM memory cell with top-gated P-N drain poly-Si TFTs for 1.5 V operation," in *IEDM Tech. Dig.*, 1996, pp. 283–286.

- [10] H. J. Cho, F. Nemati, P. B. Griffin, and J. D. Plummer, "A novel pillar DRAM cell for 4 Gbit and beyond," in VLSI Symp. Tech. Dig., 1998, pp. 38–39.

- [11] P. Y. Kuo, Y. S. Huang, Y. H. Lue, T. S. Chao, and T. F. Lei, "The characteristics of n- and p-channel poly-Si thin-film transistors with fully Ni-salicided S/D and gate structure," *J. Electrochem. Soc.*, vol. 157, no. 1, pp. H113–H119, 2010.

- [12] H. C. Cheng, F. S. Wang, and C. Y. Huang, "Effects of NH<sub>3</sub> plasma passivation on n-channel polycrystalline silicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 44, no. 1, pp. 64–68, Jan. 1997.

- [13] Y. H. Lu, P. Y. Kuo, Y. H. Wu, Y. H. Chen, and T. S. Chao, "Novel GAA raised source/drain sub-10-nm poly-Si NW channel TFTs with selfaligned corked gate structure for 3-D IC applications," in VLSI Symp. Tech. Dig., 2011, pp. 142–143.

- [14] M. H. Lee, K. J. Chen, S. C. Weng, W. H. Liu, M. J. Yang, C. T. Shih, L. S. Lee, and M. J. Kao, "High performance high-k metal-gate poly-Si TFTs with subthreshold swing <200 mV/dec. for monolithic 3D integrated circuits applications," in *Proc. SSDM*, 2010, pp. 1036–1037.

- [15] T. K. Kang, T. C. Liao, C. M. Lin, H. W. Liu, and H. C. Cheng, "High-performance single-crystal-like nanowire poly-Si TFTs with spacer patterning technique," *IEEE Electron Device Lett.*, vol. 32, no. 3, pp. 330–332, Mar. 2011.

- [16] C.-M. Lee and B.-Y. Tsui, "A high-performance 30-nm gate-all-around poly-Si nanowire thin-film transistor with NH<sub>3</sub> plasma treatment," *IEEE Electron Device Lett.*, vol. 31, no. 7, pp. 683–685, Jul. 2010.

- [17] C.-M. Lee and B.-Y. Tsui, "High-performance poly-Si nanowire thin-film transistors using the HfO<sub>2</sub> gate dielectric," *IEEE Electron Device Lett.*, vol. 32, no. 3, pp. 327–329, Mar. 2011.