# Impacts of the Underlying Insulating Layers on the MILC Growth Length and Electrical Characteristics

Chia-Chun Liao, Min-Chen Lin, Shao-Xuan Liu, and Tien-Sheng Chao

Abstract—This letter investigates the impacts of proximity layers on metal-induced lateral crystallization (MILC). The underlying insulating layers not only affect the MILC growth length but also influence the electrical characteristics. Based on the comparison among the underlying insulating layers, SiN is unsuitable to be an underlying insulating layer because of concerns regarding the crystallization condition. This letter proposes three reasonable mechanisms, including the gettering of Ni, intrinsic stress, and the involvement of hydrogen to enhance the understanding of the impacts of proximity layers.

*Index Terms*—Metal-induced lateral crystallization (MILC), strain, thin-film transistors (TFTs).

#### I. INTRODUCTION

ETAL-INDUCED lateral crystallization (MILC) has been studied as a lower temperature alternative to solid-phase crystallization (SPC) of amorphous silicon or amorphous SiGe because of its high-quality poly-Si layer with higher carrier mobility, larger grain size, and lower defect density [1].

Although MILC has been a subject of numerous studies, its detailed mechanism still provokes many questions, including metal sources, temperature, and dopant species [1], [2]. Wong *et al.* reported that the underlying insulating materials influence the MILC growth length [3], [4]. Although this study proposed a reasonable mechanism (Ni gettering occurs at the interface between a-Si and the buffered layer), Wong *et al.* found that this mechanism does not suffice to bridge the MILC growth length with the dopant species involved, implying the involvement of another mechanism [4].

In contrast, FinFETs, nanowires, and double-gated TFTs have drawn considerable attention for a number of applications [5]–[7]. With the advantage of these structures, MILC poly-Si can achieve enhanced performance. Basically, the fabrication flow of these novel structures requires SiN, thermally grown oxide, or TEOS oxide to serve as the proximity layer, such as the hard mask, the underlying insulating layer, or the spacer before MILC [5]–[8]. Thus, clarifying the influences of these

Manuscript received October 12, 2011; revised October 23, 2011; accepted October 29, 2011. Date of publication December 12, 2011; date of current version January 27, 2012. This work was supported by the National Science Council, Taiwan, under Contract NSC 100-2221-E-009-012-MY3. The review of this letter was arranged by Editor X. Zhou.

The authors are with the Department of Electrophysics, National Chiao Tung University, Hsinchu 30050, Taiwan (e-mail: forgethard@hotmail.com; yihsin0914@hotmail.com; keepmypower@gmail.com; tschao@mail.nctu.edu.tw).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2011.2174609

proximity layers on crystallization in addition to the advantages of the structures of poly-Si TFTs becomes critical.

This letter presents three commonly used layers for clarifying the effects of proximity layers on MILC length and electrical characteristics of p-channel TFTs. To avoid other mechanisms involved in carrier transportation (e.g., different mechanisms of scattering and charge trapping based on different gate oxides or spacers) that are not the scope of this letter, only different underlying insulating layers are studied for clarifying the influence of the proximity layer.

## II. EXPERIMENTAL PROCEDURE

Fabrication of the underlying insulating layers (proximity layers) was started by capping a 500-nm-thick thermal oxide layer or the TEOS oxide layer on 6-in silicon wafers. A number of wafers with thermal oxides, namely, inserted SiN, were deposited as 150-nm SiN by low-pressure chemical vapor deposition (LPCVD) as a stacked double layer for investigating the impact of the SiN proximity layer. Then, a 50-nm-thick a-Si thin film was deposited by LPCVD on all wafers. A 5-nm-thick Ni thin film was selectively deposited using an electron gun evaporator on an a-Si film using the lift-off process. The wafers were heat treated at 550 °C in a  $N_2$  ambient for 24 h to laterally crystallize the channel region where the nickel thin film was not deposited. All unreacted Ni was subsequently removed in a H<sub>2</sub>SO<sub>4</sub> solution. A 500-nm-thick plasma-enhanced chemical vapor deposition (PECVD) oxide was deposited at 300 °C for device isolation. The oxide was then patterned and etched to define the active region of the device. The source and drain regions were implanted with BF<sub>2</sub> (15 keV at  $5 \times 10^{15}$  cm<sup>-2</sup>) and activated at 600  $^{\circ}\mathrm{C}$  for 24-h annealing in a  $N_2$  ambient. A 30-nm-thick oxide was deposited at 300 °C by PECVD as the gate oxide. After patterning of contact holes, aluminum was deposited by PVD and patterned as the probe pads to complete the TFT devices.

The devices were annealed at 350 °C for 1 h. Other than postannealing, no other hydrogenation process was performed for investigating the intrinsic behavior of the devices.

### III. RESULTS AND DISCUSSION

Ni-induced MIC of a-Si occurs through a three-step process: silicide formation, breakup of the silicide layer into small nodules, and transport of the silicide nodules through the a-Si film. At the edge of a Ni-covered region, a certain number of the breakaway NiSi<sub>2</sub> nodules move laterally into the a-Si region not originally covered by Ni. As the nodules move laterally,

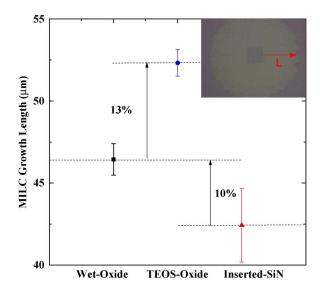

Fig. 1. Dependence of MILC growth length on proximity layers.

any a-Si along the path of the moving nodules is crystallized during the MILC process [9]. According to this theory, the growth model of MILC does not reveal the dependence of MILC growth length on the proximity layer.

Fig. 1 shows the relation between MILC growth length and different underlying insulating layers. The region crystallized by MILC was identified with optical microscopy, as shown in the inset. Using TEOS oxide achieves the fastest growth length ( $\sim$ 52.5  $\mu$ m), and using inserted SiN exhibits the slowest growth length ( $\sim$ 42  $\mu$ m). Three possible mechanisms could be responsible for the dependence of MILC growth length on the underlying insulating layers. The first mechanism proposed by Wong et al. is that Ni gettering occurs at the interface between a-Si and the buffered layer, meaning that the different interface between a-Si and the buffered layer would generate different gettering sites of Ni [4]. The second mechanism is the effect of stress on lateral growth behavior during MILC. Tensile stress enhances the breakage of Si-Si bonding and increases the number of absorbing Si atoms at the front of the NiSi<sub>2</sub>/a-Si interface. This tensile stress also generates more vacancies in the NiSi<sub>2</sub> precipitates, and these vacancies raise the diffusion rate of Ni atoms through NiSi<sub>2</sub>. Consequently, the tensile stress enhances MILC growth length, whereas the compressive stress retards it [10]. Thus, the stress of the underlying insulating layer is reasonable to affect MILC growth length. This stress may originate from the different coefficients of thermal expansion between a-Si and the proximity layer, the different lattice constants of various films, and intrinsic stress caused by film shrinkage, although the realistic stress interaction is difficult to gauge [11]. We believe that the higher compressive stress (-312 MPa) of the wet oxide could explain the lower MILC growth length compared to the growth length of the TEOS oxide (-52 MPa). The third possible cause is the outdiffusion of the released hydrogen from the underlying insulating layer, such as SiN, because the MILC growth length of the H<sub>2</sub>doped sample was retarded [2]. The higher H content signifies a film with less dangling bonds in amorphous Si, leading to a lower MILC growth length. We believe that the released

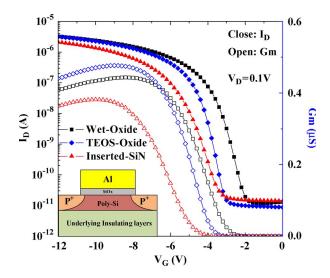

Fig. 2 Transfer characteristics  $I_D - V_G$  of p-channel TFTs with different underlying insulating layers.

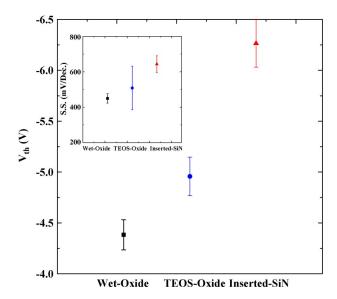

Fig. 3. Variation of threshold voltage as a function of channel width for  $W/L=10~\mu \mathrm{m}/10~\mu \mathrm{m}$ . The inset shows the variation of subthreshold swing as a function of channel width for  $W/L=10~\mu \mathrm{m}/10~\mu \mathrm{m}$ .

hydrogen from SiN would counteract the effects of tensile stress (1.2 GPa), resulting in the slowest growth length.

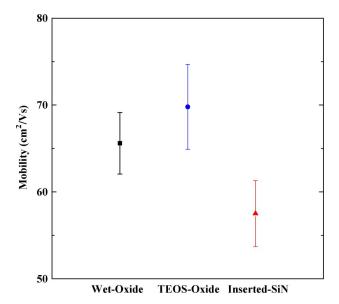

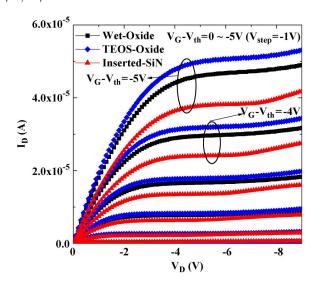

Fig. 2 shows the  $I_D$ – $V_G$  curves of a p-channel TFT and shows that using different underlying insulating materials results in a substantial impact on the electrical characteristics because of the different crystallization conditions and channel/bottom oxide interface. Fig. 3 shows the threshold voltage and subthreshold swing. The threshold voltage  $(V_{\rm th})$  is defined as the gate voltage required to achieve a normalized drain current of  $I_D = (W/L) \times 100$  nA at  $V_{\rm DS} = 0.1$  V. Figs. 4 and 5 show the field-effect mobility and output characteristics (the  $I_D$ – $V_D$  curve). The deep states that originate from the dangling bonds in grain boundaries influence the threshold voltage and subthreshold swing, whereas the tail states that originate from intragrain defects affect field-effect mobility [12]. Kim *et al.* proposed that a higher MILC growth rate may generate lower trap density in the poly-Si channel [2]. However, they did not

Fig. 4 Variation of mobility as a function of channel width for  $W/L = 10 \; \mu \mathrm{m}/10 \; \mu \mathrm{m}.$

Fig. 5 Output characteristics (the  $I_D$ – $V_D$  curve) of n-channel TFTs with  $W/L=10~\mu{\rm m}/10~\mu{\rm m}$  for all samples.

catalogue the types of defects or verify this theory with any electrical characteristics of transistors. The inserted SiN sample exhibits the lowest mobility, the worst output characteristics, and the highest threshold voltage, correlating well with the slowest MILC growth length. In contrast, the TEOS oxide sample exhibits superior mobility, although with a slightly higher threshold voltage and subthreshold swing, compared to the wet oxide sample. Therefore, the underlying insulating layers affect not only the MILC growth length but also the electrical characteristics.

# IV. CONCLUSION

This letter has clarified the effects of underlying insulating layers on MILC growth length and electrical characteristics.

Three possible mechanisms can be used to explain the dependence of MILC growth length on the proximity layer. In addition, other than the difference in MILC growth length, the underlying insulating layers affect threshold voltage and mobility. Based on the comparison among underlying insulating layers, using SiN not only retards MILC growth length the most but also exhibits the worst threshold voltage and mobility. Therefore, we believe that the three probable mechanisms, which can be affected by the dopant, annealing, and different fabrication processes, can provide guidance for further examinations on the effects of the proximity layer.

#### ACKNOWLEDGMENT

The authors would like to thank the National Nano Device Laboratories for the procedural support, and the Nano Facility Center of National Chiao Tung University.

#### REFERENCES

- [1] Z. Jin, K. Moulding, H. S. Kwok, and M. Wong, "The effects of extended heat treatment on Ni induced lateral crystallization of amorphous silicon thin films," *IEEE Trans. Electron Devices*, vol. 46, no. 1, pp. 78–82, Jan 1999

- [2] G. B. Kim, Y. G. Yoon, M. S. Kim, H. Jung, S. W. Lee, and S. K. Joo, "Electrical characteristics of MILC poly-Si TFTs with long Nioffset structure," *IEEE Trans. Electron Devices*, vol. 50, no. 12, pp. 2344– 2347. Dec. 2003.

- [3] M. Wong, Z. Jin, G. A. Bhat, P. C. Wong, and H. S. Kwok, "Characterization of the MIC/MILC interface and its effects on the performance of MILC thin-film transistors," *IEEE Trans. Electron Devices*, vol. 47, no. 5, pp. 1061–1067, May 2000.

- [4] T. Ma and M. Wong, "Dopant and thickness dependence of metal-induced lateral crystallization of amorphous silicon films," *J. Appl. Phys.*, vol. 91, no. 3, pp. 1236–1241, Feb. 2002.

- [5] W. C. Chen, H. C. Lin, Y. C. Chang, C. D. Lin, and T.-Y. Huang, "In situ doped source/drain for performance enhancement of double-gated poly-Si nanowire transistor," *IEEE Trans. Electron Devices*, vol. 57, no. 7, pp. 1608–1615, Jul. 2010.

- [6] C. W. Chang, S. F. Chen, C. L. Chang, C. K. Deng, J. J. Huang, and T. F. Lei, "High-performance nanowire TFTs with metal-induced lateral crystallized poly-Si channels," *IEEE Electron Device Lett.*, vol. 29, no. 5, pp. 474–476, May 2008.

- [7] H. C. Lin and C. J. Su, "High-performance poly-Si nanowire NMOS transistors," *IEEE Trans. Nanotechnol.*, vol. 6, no. 2, pp. 206–212, Mar. 2007.

- [8] X. Z. Bo, N. Yao, S. R. Shieh, T. S. Duffy, and J. C. Sturm, "Large-grain polycrystalline silicon films with low-temperature solid-phase crystallization without underlying oxide," *J. Appl. Phys.*, vol. 91, pp. 2910–2915, 2002

- [9] Z. Jin, G. A. Bhat, M. Yeung, H. S. Kwok, and M. Wong, "Nickel induced crystallization of amorphous silicon thin films," *J. Appl. Phys.*, vol. 84, pp. 193–200, 1998.

- [10] N. K. Song, M. S. Kim, S. H. Han, Y. S. Kim, and S. K. Joo, "Effects of mechanical stress on the growth behaviors of metal-induced lateral crystallization," *J. Electrochem. Soc.*, vol. 154, pp. H370–H373, 2007.

- [11] P. R. Chidambaram, C. Bowen, S. Chakravarthi, C. Machala, and R. Wise, "Fundamentals of silicon material properties for successful exploitation of strain engineering in modern CMOS manufacturing," *IEEE Trans. Electron Devices*, vol. 53, no. 5, pp. 944–964, May 2006.

- [12] I. W. Wu, T. Y. Huang, W. B. Jackson, A. G. Lewis, and A. Chiang, "Passivation kinetics of two types of defects in polysilicon TFT by plasma hydrogenation," *IEEE Electron Device Lett.*, vol. 12, no. 4, pp. 181–183, Apr. 1991.