# Oxide Thinning and Structure Scaling Down Effect of Low-Temperature Poly-Si Thin-Film Transistors

William Cheng-Yu Ma, Tsung-Yu Chiang, Je-Wei Lin, and Tien-Sheng Chao, Senior Member, IEEE

Abstract-In this paper, the gate oxide thickness, and the channel length and width of low-temperature poly-Si thin-film transistors (LTPS-TFTs) have been comprehensively studied. The scaling down of gate oxide thickness from 50 to 20 nm significantly improves the subthreshold swing (S.S.) of LTPS-TFTs from 1.797 V/decade to 0.780 V/decade and the threshold voltage  $V_{

m TH}$  from 10.87 V to 5.00 V. Moreover, the threshold voltage  $V_{

m TH}$  roll-off is also improved with the scaling down of gate oxide thickness due to gate capacitance density enhancement. The channel length scaling down also shows significant subthreshold swing S.S. improvement due to a decreasing of the channel grain boundary trap density  $N_t$ . However, the scaling down of channel length also increases the series resistance effect, resulting in the degradation of the field-effect mobility  $\mu_{\rm FE}$ . Therefore, the channel length dependence of field-effect mobility  $\mu_{\rm FE}$  is slightly different with different channel width due to the competition of channel grain boundary trap density effect and series resistance effect.

*Index Terms*—Gate oxide thickness, low-temperature poly-Si thin-film transistors (LTPS-TFTs), scaling down.

#### I. INTRODUCTION

OW-TEMPERATURE polycrystalline silicon (LTPS) thin-film transistors (TFTs) have been used for active-matrix liquid crystal displays (AMLCDs) on glass substrates as pixel and driving integrated circuits instead of amorphous silicon [1]–[8]. This is because the field-effect mobility  $\mu_{\rm EF}$ in polycrystalline silicon is significantly higher (by two orders of magnitude) than that in amorphous silicon [6], so that CMOS devices with reasonably high drive currents can be achieved in polycrystalline silicon. Recently, the topic of system-on-panel (SOP) is attracting much attention. Therefore, high-performance TFTs with high driving current, low gate leakage current, low threshold voltage  $V_{\rm TH}$  and subthreshold swing S.S. are required urgently for high-speed display driving circuits [9], [10]. Increasing the gate capacitance density is a direct and simple method of improving the performance and specifically the driving current of LTPS-TFTs. Therefore, a comprehensive study of the effect of reducing gate oxide thickness in LTPS-TFTs is important for further development. Here, we investigate the gate oxide thickness scaling impacts of LTPS-TFTs with different channel length  $L_g$  and width W

Manuscript received April 26, 2011; revised July 09, 2011; accepted July 18, 2011. This work was supported by the National Science Council of the Republic of China under Contract NSC 100-2221-E-009-012-MY3. Date of publication September 29, 2011; date of current version January 04, 2012.

The authors are with the Institute and Department of Electrophysics, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: williammaa@gmail.com; tychiang0528@gmail.com; hpmax1981.ep96g@nctu.edu.tw; tschao@mail.nctu.edu.tw)

Color versions of one or more of the figures are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JDT.2011.2162938

on the electrical behavior of threshold voltage  $V_{\rm TH}$ , field-effect mobility  $\mu_{\rm FE}$ , and subthreshold swing S.S.

### II. EXPERIMENTAL PROCEDURE

The fabrication of devices was started by depositing an undoped amorphous Si ( $\alpha$ -Si) layer 55-nm at 550 °C in a low-pressure chemical vapor deposition (LPCVD) system on Si wafers capped with a 500-nm thick thermal oxide layer. Then, the  $\alpha$ -Si layer was recrystallized by a solid-phase-crystallization (SPC) process in furnace at 600 °C for 24 h in a N<sub>2</sub> ambient. After the crystallization of the channel film, the active region was patterned by dry etching. Then, three thicknesses of gate oxide 20, 32, and 50 nm were deposited by plasma-enhanced chemical vapor deposition (PECVD) system at 300 °C. 250-nm in situ N<sup>+</sup> doped  $\alpha$ -Si is deposited by LPCVD at 550 °C as the gate electrode. After gate stack patterning, the gate and source/drain regions are implanted with phosphorus (15 keV at  $5\times10^{15}$  cm<sup>-2</sup>) and activated at 600 °C for 24 h annealing in a N2 ambient. A 500-nm PECVD oxide is deposited for the passivation layer. After the patterning of contact holes, aluminum was deposited by thermal evaporation system and patterned as the probe pads to complete the TFT devices. The grain size of the polycrystalline Si channel is about 250-300 nm [9]. Generally, LTPS-TFT with SPC process has many grain boundaries within the poly-Si channel, resulting in many electrical traps exist. These traps would capture carriers to create potential barriers, resulting in poor subthreshold swing S.S., higher threshold voltage  $V_{\rm TH}$ , lower field-effect mobility  $\mu_{\rm FE}$  and poor performance. Therefore, hydrogenation process is usually used to passivate these traps to improve the electrical behavior of LTPS-TFTs [11]. In order to study the intrinsic electrical property of LTPS-TFTs, there is no any defect passivation process in our fabrication of LTPS-TFTs.

The threshold voltage  $V_{\rm TH}$  is defined as  $V_G$  at which  $I_D$  reaches 100 nA  $\times$   $(W/L_g)$  and  $V_D=1$  V. The field-effect mobility  $\mu_{\rm FE}$  is extracted from the maximum transconductance  $G_m$ .

### III. RESULTS AND DISCUSSION

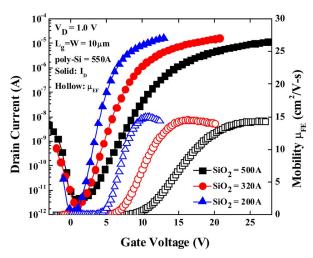

Fig. 1 shows the transfer curves  $(I_D - V_G)$  and field-effect mobility  $\mu_{\rm FE}$  of LTPS-TFTs with different gate oxide thickness. The subthreshold swing S.S. is significantly improved from 1.797 V/decade to 0.780 V/decade when the gate oxide thickness is scaled from 50 to 20 nm. The subthreshold swing S.S. should be strongly related to the gate capacitance density  $C_{\rm ox}$  and interface states  $D_{\rm it}$  according to the Dimitriadis model [12]

S.S. =

$$\left[\frac{qN_{\rm it}}{C_{\rm ox}} + 1\right] \frac{KT}{q} \ln 10.$$

(1)

Fig. 1. Transfer curve  $(I_D-V_G)$  and field-effect mobility  $\mu_{\rm FE}$  of LTPS-TFTs with three gate oxide thickness 50, 32, and 20 nm.

TABLE I IMPORTANT DEVICE PARAMETERS OF LTPS-TFTS WITH DIFFERENT OXIDE THICKNESS  $t_{\rm ox},$  55-NM Channel Film Thickness,  $W/L_g=10~\mu{\rm m}/10~\mu{\rm m}$

| tox                               | $V_{TH}$                                                                                                                            | s.s.                  | $\mu_{	ext{FE}}$       | D <sub>it</sub>       |     |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|-----------------------|-----|

| (nm)                              | (V)                                                                                                                                 | (V/dec.)              | (cm <sup>2</sup> /V-s) | (cm <sup>-2</sup> )   |     |

| 20                                | 5.00                                                                                                                                | 0.780                 | 14.91                  | 1.30x10 <sup>13</sup> |     |

| 32                                | 7.35                                                                                                                                | 1.180                 | 14.54                  | 1.27x10 <sup>13</sup> |     |

| 50                                | 10.87                                                                                                                               | 1.797                 | 14.33                  | 1.26x10 <sup>13</sup> |     |

| 10 <sup>-5</sup> SiO <sub>2</sub> | $^{=}1.0 \mathrm{~V}, \mathrm{~W}$ $^{=}500\mathrm{A}, \mathrm{~J}$ $^{=}L_{\mathrm{g}}$ $^{=}10\mu\mathrm{m}$ $^{=}L_{\mathrm{g}}$ | poly-Si = <b>55</b> 0 | ······                 | - 20                  |     |

| 10-7                              | $L_{ m g}$ =2 $\mu$ m, $L_{ m g}$ =1 $\mu$ m                                                                                        |                       | . (VII)                | 15                    | 5 , |

| 10-9                              | <b>1</b>                                                                                                                            |                       |                        | - 10                  | 0   |

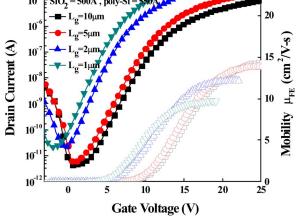

Fig. 2. Transfer curve  $(I_D-V_G)$  and field-effect mobility  $\mu_{\rm FE}$  of LTPS-TFTs with 50-nm gate oxide thickness, channel width  $W=10~\mu{\rm m}$  and four channel length  $L_g=10,~2,~{\rm and}~1~\mu{\rm m}.$

The extracted interface states  $D_{\rm it}$  and other important parameters are listed in the Table I. It shows that the interface states  $D_{\rm it}$  of LTPS-TFTs with different gate oxide thickness are the same, indicating the subthreshold swing S.S. improvement is completely attributed to the increase in the gate capacitance density  $C_{\rm ox}$ . It also indicates the oxide/Si interface quality of LTPS-TFTs with different gate oxide thickness is the same. In addition, the field-effect mobility  $\mu_{\rm FE}$  of LTPS-TFTs with different gate oxide thickness are comparable, indicating the

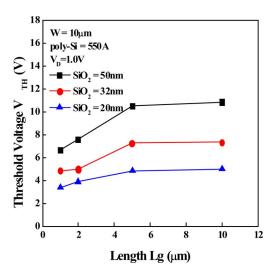

Fig. 3. Threshold voltage  $V_{\rm TH}$  versus channel length  $L_g$  of LTPS-TFTs with three gate oxide thickness 50, 32, and 20 nm.

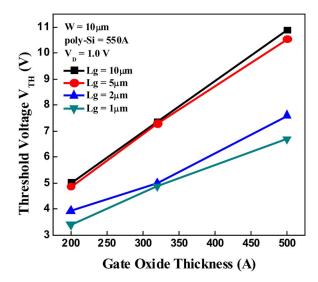

Fig. 4. Threshold voltage  $V_{\rm TH}$  versus gate oxide thickness of LTPS-TFTs with four channel length  $L_g=10,~5,~2,~{\rm and}~1~\mu{\rm m}.$

field-effect mobility  $\mu_{\rm FE}$  is less dependent on gate capacitance density  $C_{\rm ox}$  if the oxide–Si interface and channel film quality is the same.

Fig. 2 shows the transfer curves of LTPS-TFTs with different channel length  $L_g$ . Significant threshold voltage  $V_{\rm TH}$  roll-off is observed, as shown in Fig. 3, and reducing the gate oxide thickness from 50 to 20 nm enhances the control afforded by the gate, thereby improving the threshold voltage  $V_{\rm TH}$  roll-off. Fig. 4 shows the gate oxide thickness dependence of threshold voltage  $V_{\rm TH}$ , indicating that the threshold voltage  $V_{\rm TH}$  is almost linearly proportional to oxide thickness whether the channel length is long or short.

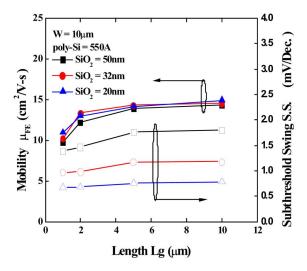

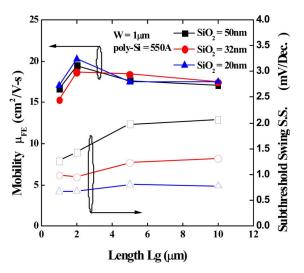

In addition to threshold voltage  $V_{\rm TH}$  behavior, the channel length  $L_g$  dependence of field-effect mobility  $\mu_{\rm FE}$  and subthreshold swing S.S. are also shown in Fig. 5. The reduction in subthreshold swing S.S. with decrease of the channel length  $L_g$  is due to the decreasing of channel grain boundary trap density  $N_t$  when the channel length  $L_g$  is decreasing, resulting in fewer surface interface states  $D_{\rm it}$ . The channel grain boundary trap

Fig. 5. Channel length  $L_g$  dependence of field-effect mobility  $\mu_{\rm FE}$  and subthreshold swing S.S of LTPS-TFTs with channel width  $W=10~\mu{\rm m}$  and three gate oxide thickness 50, 32, and 20 nm.

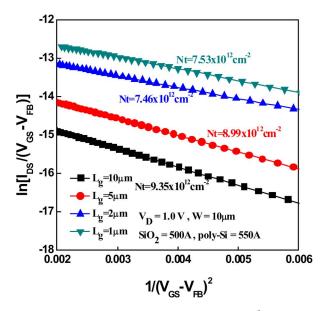

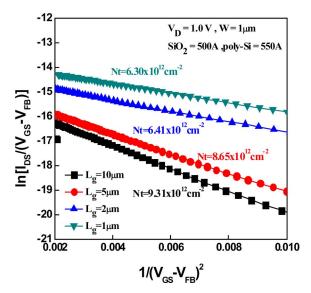

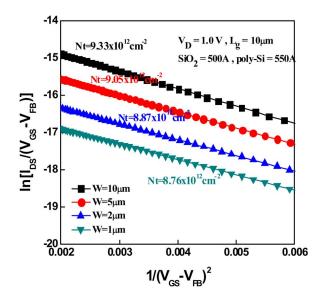

Fig. 6. Plot of  $\ln[I_{\rm DS}/(V_{\rm GS}-V_{\rm FB})]$  versus  $1/(V_{\rm GS}-V_{\rm FB})^2$  curves of LTPS-TFTs at  $V_{\rm DS}=1.0$  V and high  $V_{\rm GS}$  with channel width  $W=10~\mu{\rm m}$  and four channel length  $L_g=10,~5,~2,~{\rm and}~1~\mu{\rm m}$ .

density  $N_t$  of LTPS-TFTs with different channel length  $L_g$ are extracted from the plot of  $\ln \left[ I_{\rm DS}/(V_{\rm GS}-V_{\rm FB}) \right]$  versus  $1/(V_{\rm GS}-V_{\rm FB})^2$  curves at  $V_{\rm DS}=1~{

m V}$  and high  $V_{\rm GS}$  [13], [14], as shown in Fig. 6. When the channel length  $L_q$  or width Wis much larger than the grain size, the average grain boundary density is fairly constant, resulting in less device dimension dependence of electrical behavior of LTPS-TFTs. As the device dimension is reduced the number of grain boundaries in the channel becomes small, and therefore the varying number of grain boundaries between devices becomes significant, resulting in greater variation in device characteristics. Fig. 5 also shows that the field-effect mobility  $\mu_{\mathrm{FE}}$  is reduced when the channel length  $L_q$  is decreased. With the reduction of channel length  $L_q$ , the grain boundary trap density  $N_t$  would decrease, and the series resistance  $R_s$  effect would be more serious [15], [16]. A reduced grain boundary density could

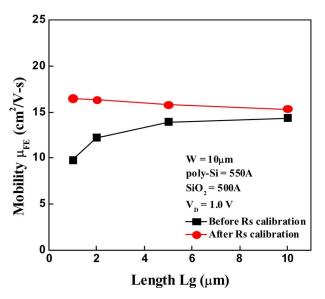

Fig. 7. Channel length  $L_g$  dependence of field-effect mobility  $\mu_{\rm FE}$  of LTPS-TFTs with channel width  $W=10~\mu{\rm m}$  before and after series resistance  $R_s$  calibration.

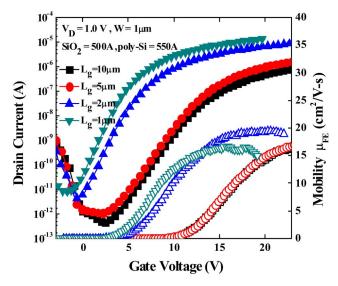

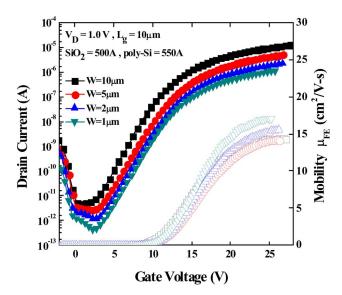

Fig. 8. Transfer curve  $(I_D-V_G)$  and field-effect mobility  $\mu_{\rm FE}$  of LTPS-TFTs with 50 nm gate oxide thickness, channel width  $W=1~\mu{\rm m}$  and four channel length  $L_g=10,~5,~2,~{\rm and}~1~\mu{\rm m}.$

improve the field-effect mobility  $\mu_{\rm FE}$  and subthreshold swing S.S. due to a reduced trap density and less carrier scattering in the conduction channel. However, the series resistance  $R_s$  effect would lead to less drain voltage drop in the conduction channel, resulting in less drain current and lower field-effect mobility  $\mu_{\rm FE}$ . Therefore, the effect of the grain boundary trap density  $N_t$  decreasing and the series resistance effect are in competition when the channel length  $L_q$  is reduced. In the subthreshold region, a small drain current would not lead to a significant reduction in actual voltage across the channel due to the series resistance, and the grain boundary trap density  $N_t$ decrease effect could improve the subthreshold swing S.S. as the channel length  $L_q$  is reduced. However, for a high driving current, the series resistance  $R_s$  effect would significantly degrade the field-effect mobility  $\mu_{\mathrm{FE}}$  as the scaling down of channel length  $L_g$  even the grain boundary trap density  $N_t$

Fig. 9. Plot of  $\ln[I_{\rm DS}/(V_{\rm GS}-V_{\rm FB})]$  versus  $1/(V_{\rm GS}-V_{\rm FB})^2$  curves of LTPS-TFTs at  $V_{\rm DS}=1.0$  V and high  $V_{\rm GS}$  with channel width  $W=1~\mu{\rm m}$  and four channel length  $L_q = 10, 5, 2, \text{ and } 1 \,\mu\text{m}.$

Fig. 10. Channel length  $L_g$  dependence of field-effect mobility  $\mu_{\mathrm{FE}}$  and subthreshold swing S.S of LTPS-TFTs with channel width  $W=1~\mu{\rm m}$  and three gate oxide thickness 50, 32, and 20 nm.

decreased. In order to estimate the series resistance effect of LTPS-TFTs, the modified field-effect mobility  $\mu'_{\rm FE}$  is defined as follows [17]:

$$I_D = \frac{W}{L} C_{\text{ox}} \mu_{\text{eff}} (V_g - V_{TH}) V_D \tag{2}$$

$$I_D = \frac{W}{L} C_{\text{ox}} \mu'_{\text{eff}} (V_g - V_{TH}) V'_D \tag{3}$$

$$V'_D = \stackrel{L}{V_D} - I_D \times R_s \tag{4}$$

$$I_{D} = \frac{W}{L} C_{\text{ox}} \mu'_{\text{eff}} (V_{g} - V_{TH}) V'_{D}$$

$$V'_{D} = V_{D} - I_{D} \times R_{s}$$

$$\mu'_{\text{eff}} = \mu_{\text{eff}} \times \frac{V_{D}}{V_{D} - I_{D} \times R_{s}}$$

$$(5)$$

where  $V_D$  is the total applied voltage. The voltage drop should occur in the series resistance and conductive channel of TFTs.  $V'_D$  is thus the real applied voltage across the channel of TFTs. About 6.1 k $\Omega$  series resistance of device is extracted from drain current relation of gate voltage  $V_g$  and channel length  $L_g$  [17]. The modified field-effect mobility  $\mu'_{FE}$  with and without series resistance  $R_s$  calibration is shown in Fig. 7. It shows that

Fig. 11. Transfer curve  $(I_D\text{-}V_G)$  and field-effect mobility  $\mu_{\mathrm{FE}}$  of LTPS-TFTs with 50-nm gate oxide thickness, channel length  $L_g=10~\mu\mathrm{m}$  and four channel width  $L_g = 10, 5, 2, \text{ and } 1 \,\mu\text{m}$ .

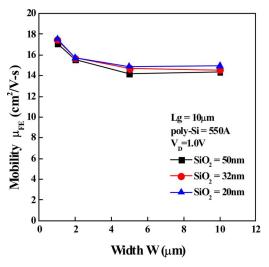

Fig. 12. Field-effect mobility  $\mu_{\rm FE}$  versus channel width W of LTPS-TFTs with three gate oxide thickness 50, 32, and 20 nm.

the modified field-effect mobility  $\mu'_{\rm FE}$  is increased with the reduction in channel length  $L_q$ , and the field-effect mobility  $\mu_{\rm FE}$ without  $R_s$  calibration shows the 6.1 k $\Omega$  series resistance would result in series  $\mu_{\rm FE}$  degradation. As for the narrower channel width  $W=1~\mu\mathrm{m}$ , the transfer curves of LTPS-TFTs with different channel  $L_g$  are shown in Fig. 8. Comparing to wide channel width  $W = 10 \mu m$ , the grain boundary trap density  $N_t$ decreasing effect is more significant as shown in Fig. 9, resulting in that the field-effect mobility  $\mu_{\rm FE}$  exhibiting a slight increase first before it decreases with the reduction of channel length  $L_q$ , as shown in Fig. 10. Moreover, the subthreshold swing improvement  $\Delta S.S.$  from channel length  $L_q = 10 \ \mu m$  to  $1 \ \mu m$  is also enhanced from  $\Delta S.S. = 0.4 \text{ V/decade}$  to 0.8 V/decade with the reduction of channel width from  $W=10~\mu\mathrm{m}$  to  $1~\mu\mathrm{m}$ . Fig. 11 shows the transfer curves of LTPS-TFTs with different channel width. The channel width dependence of field-effect mobility  $\mu_{\rm FE}$  is shown in Fig. 12. It shows that the field-effect mobility  $\mu_{\rm FE}$  is independent of gate oxide thickness and increases with the reduction in the channel width. As mentioned above, the

Fig. 13. Plot of  $\ln[I_{\rm DS}/(V_{\rm GS}-V_{\rm FB})]$  versus  $1/(V_{\rm GS}-V_{\rm FB})^2$  curves of LTPS-TFTs at  $V_{\rm DS}=1.0$  V and high  $V_{\rm GS}$  with channel length  $L_g=10~\mu{\rm m}$  and four channel width  $L_g=10,\,5,\,2,\,$  and  $1~\mu{\rm m}.$

channel width reduction can decrease the grain boundary trap density  $N_t$  in the channel film, as shown in Fig. 13, resulting in higher field-effect mobility  $\mu_{\rm FE}$ . Finally, the impacts of reducing gate oxide thickness, channel length  $L_g$  and width on LTPS-TFTs are all extracted simultaneously.

# IV. CONCLUSION

A comprehensive study of scaling down effects of LTPS-TFTs with various gate oxide thicknesses, channel length  $L_g$  and width W are studied simultaneously. Gate oxide thickness strongly affects the electrical performance of LTPS-TFTs, including threshold voltage  $V_{\rm TH}$ , subthreshold swing S.S., channel length  $L_g$  dependence of field-effect mobility  $\mu_{\rm FE}$  and subthreshold swing S.S. The thin gate oxide thickness of LTPS-TFTs results in the most stable and superior electrical behavior. In addition, the competition of channel grain boundary trap density effect and series resistance effect is also observed; the different channel width of LTPS-TFTs exhibit slightly different channel length dependence of field-effect mobility  $\mu_{\rm FE}$ .

# ACKNOWLEDGMENT

The authors would like to thank the processes support from National Nano Device Labs and the Nano Facility Center of the National Chiao Tung University, Hsinchu, Taiwan.

#### REFERENCES

- G. K. Guist and T. W. Sigmon, "High-performance thin-film transistors fabricated using excimer laser processing and grain engineering," *IEEE Trans. Electron Devices*, vol. 45, no. 4, pp. 925–932, Apr. 1998.

- [2] Y. W. Choi, J. N. Lee, T. W. Jang, and B. T. Ahn, "Thin-film transistors fabricated with poly-silicon films crystallized at low temperature by microwave annealing," *IEEE Electron Device Lett.*, vol. 20, no. 1, pp. 2–4, Jan. 1999.

- [3] C. W. Lin, M. Z. Yang, C. C. Yeh, L. J. Cheng, T. Y. Huan, H. C. Cheng, H. C. Lin, T. S. Chao, and C. Y. Chang, "Effects of plasma treatments, substrate types, and crystallization methods on performance and reliability of low temperature polysilicon TFTs," in *IEDM Tech. Dig.*, 1999, pp. 305–308.

- [4] K. M. Chang, W. C. Yang, and C. P. Tsai, "Electrical characteristics of low temperature polysilicon TFT with a novel TEOS/oxynitride stack gate dielectric," *IEEE Electron Device Lett.*, vol. 24, no. 8, pp. 512–514, Aug. 2003.

- [5] J.-H. Jeon, M.-C. Lee, K.-C. Park, S.-H. Jung, and M.-K. Han, "A new poly-Si TFT with selectively doped channel fabricated by novel excimer laser annealing," in *IEDM Tech. Dig.*, 2000, pp. 213–216.

- [6] W. G. Hawkins, "Polycrystalline-silicon device technology for largearea electronics," *IEEE Trans. Electron Devices*, vol. 33, no. 4, pp. 477–481, Apr. 1986.

- [7] T.-Y. Chiang, M.-W. Ma, Y.-H. Wu, P.-Y. Kuo, K.-T. Wang, C.-C. Liao, C.-R. Yeh, and T.-S. Chao, "MILC-TFT with high-k dielectrics for one-time-programmable memory application," *IEEE Electron Device Lett.*, vol. 30, no. 9, pp. 954–956, Sep. 2009.

- [8] T. T.-J. Wang, W. C.-Y. Ma, S.-W. Hung, and C.-T. Kuo, "Low temperature Ni-nanocrystals-assisted hybrid polycrystalline silicon thin film transistor for non-volatile memory applications," *Thin Solid Films*, vol. 518, no. 24, pp. 7429–7432, 2010.

- [9] M.-W. Ma, T.-Y. Chiang, C.-R. Yeh, T.-S. Chao, and T.-F. Lei, "Electrical characteristics of high performance SPC and MILC p-channel LTPS-TFT with high- gate dielectric," *Electrochem. and Solid State Lett.*, vol. 12, no. 10, pp. H361–H364, 2009.

- [10] M.-W. Ma, T.-Y. Chiang, W.-C. Wu, T.-S. Chao, and T.-F. Lei, "Characteristics of HfO<sub>2</sub>/poly-Si interfacial layer on CMOS LTPS-TFTs with HfO<sub>2</sub> gate dielectric and O<sub>2</sub> plasma surface treatment," *IEEE Trans. Electron Devices*, vol. 55, no. 12, pp. 3489–3493, Dec. 2008.

- [11] I.-W. Wu, T.-Y. Huang, W. B. Jackson, A. G. Lewis, and A. C. Chiang, "Passivation kinetics of two types of defects in polysilicon TFI by plasma hydrogenation," *IEEE Electron Device Lett.*, vol. 12, no. 4, pp. 181–183, Apr. 1991.

- [12] C. A. Dimitriadis, P. A. Coxon, L. Dozsa, L. Papadimitrious, and N. Economou, "Performance of thin-film transistors on polysilicon films grown by low-pressure chemical vapor deposition at various pressures," *IEEE Trans. Electron Devices*, vol. 39, no. 3, pp. 598–606, Mar. 1992.

- [13] J. Levinson, F. R. Shepherd, P. J. Scanlon, W. D. Westwood, G. Este, and M. Rider, "Conductivity behavior in polycrystalline semiconductor thin film transistors," *J. Appl. Phys.*, vol. 53, no. 2, pp. 1193–1202, Feb. 1092

- [14] R. E. Proano, R. S. Misage, and D. G. Ast, "Development and electrical properties of undoped polycrystalline silicon thin-film transistor," *IEEE Trans. Electron Devices*, vol. 36, no. 9, pp. 1915–1922, Sep. 1989.

- [15] A. Valletta, L. Mariucci, and G. Fortunato, "Surface-scattering effects in polycrystalline silicon thin-film transistors," *Appl. Phys. Lett.*, vol. 82, no. 18, pp. 3119–3121, May 2003.

- [16] P. Gaucci, A. Valletta, L. Mariucci, G. Fortunato, and S. D. Brotherton, "Numerical simulation of parasitic resistance effects in polycrystalline silicon TFTs," *IEEE Trans. Electron Devices*, vol. 53, no. 3, pp. 573–577, Mar. 2006.

- [17] C.-Y. Ma, T.-Y. Chiang, C.-R. Yeh, T.-S. Chao, and T.-F. Lei, "Channel film thickness effect of low-temperature polycrystalline-silicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 58, no. 4, pp. 1268–1272, Apr. 2011.

William Cheng-Yu Ma was born in Taipei, Taiwan, in 1980. He received the B.S. degree in Electrophysics from National Chiao-Tung University, Hsinchu, Taiwan, in 2002, and the M.S. and Ph.D. degrees in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 2004, and 2008, respectively.

In 2009, he had changed his name from Ming-Wen Ma to William Cheng-Yu Ma in 2009. He is currently working on the research and design of 28-nm node CMOS technology. His research interests are the

fabrication and characterization of low-temperature polycrystalline thin-film transistor (LTPS-TFT), silicon-on-insulator (SOI) device, metal-gate/high-K (MG/HK) technology, and RF metal-insulator-metal capacitor (MIM).

Tsung-Yu Chiang was born in Yunlin, Taiwan, in 1984. He received the B.S. degree in physics from National Chung Cheng University, Chiayi, Taiwan, in 2006, and is currently working toward the Ph.D. degree in the Department of Electrophysics, National Chiao Tung University, Hsinchu, Taiwan.

His research interest includes the studies of semiconductor device physics, including low-temperature polycrystalline-silicon thin-film transistor (LTPS-TFT), metal-gate/high-k technology, strain technique, and nonvolatile Flash memories.

**Tien-Sheng Chao** (SM'01) was born in Penghu, Taiwan, in 1963. He received the Ph.D. degrees in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan in 1992.

He joined the National Nano Device Laboratories (NDL) as an associate researcher in July, 1992, and became as a researcher in 1996. He was engaged in developing the thin dielectrics preparations, cleaning processes, and CMOS devices fabrication. Since 2001, he has been with the Department of Electrophysics, National Chiao Tung University,

Hsinchu, Taiwan. He has published over than 140 papers in this field.

**Je-Wei Lin** was born in Yilan, Taiwan, in 1981. He received the B.S. and M.S. degrees from the Department of Electrical Engineering, Chung Hua University, HsinChu, Taiwan, in 2004 and 2007, respectively, and is currently working toward the Ph.D. degree from same university.

His research interest includes the studies of electrooptical semiconductor device physics, including high-efficiency monocrystalline silicon solar cells and metal insulator semiconductor solar cells.