## MIXED SIGNAL LETTER

# An active device based wide tuning range CMOS transconductor

Tien-Yu Lo · Chung-Chih Hung

Received: 5 March 2011/Revised: 10 August 2011/Accepted: 10 August 2011/Published online: 30 August 2011 © Springer Science+Business Media, LLC 2011

**Abstract** A CMOS transconductor for wide tuning range filter application is presented. The linear transconductor is designed based on the flipped-voltage follower (FVF) circuit and can work in the weak, moderate, and strong inversion regions to maximize the transconductance tuning range. The transconductance tuning can be achieved by changing the bias current of the active resistor, and a ratio of 28 is obtained. The transconductor was evaluated by using TSMC 0.18  $\mu$ m CMOS process, and the total harmonic distortion (THD) of -56 dB can be obtained by giving a 12 MHz 0.4 Vpp input swing signal. In the design, the maximum power consumption is 2 mW with the transconductance of 1.1 mS under a 1.8 V supply voltage.

**Keywords** Transconductor · THD · FVF · CMOS

#### 1 Introduction

The trend of the portable solutions tends to include multiple applications in a long-standby system. Cost efficiency has been greatly increased with the emergence of CMOS technology in high performance VLSI implementations. Moreover, to save the silicon area in a standalone system-on-a-chip solution, re-usable circuits for different system

T.-Y. Lo · C.-C. Hung (⊠)

Analog Integrated Circuit Laboratory, Department of Electrical Engineering, National Chiao Tung University,

Hsinchu 300, Taiwan

e-mail: cchung@mail.nctu.edu.tw

T.-Y. Lo

e-mail: tienyu.cm90g@nctu.edu.tw

applications can be even cost-effective. This study presents a CMOS implementation of a transconductor with a very wide transconductance tuning range for multi-mode applications. The transconductor, which performs the voltage-to-current conversion, is a basic building block in the continuous-time filters [1]. There are numerous works to improve the transconductor linearity [2–5], but the reported technology is not suitable for wide tuning range applications. In the letter, a high performance linear circuit with the use of an active equivalent resistor is designed based on the flipped-voltage follower (FVF) [6] structure. The equivalent resistor circuit could operate in the weak, moderate, and strong inversion regions to achieve a wide transconductance tuning range, and the tuning ability can be achieved by adjusting the bias current.

## 2 Proposed transconductor circuit and performance

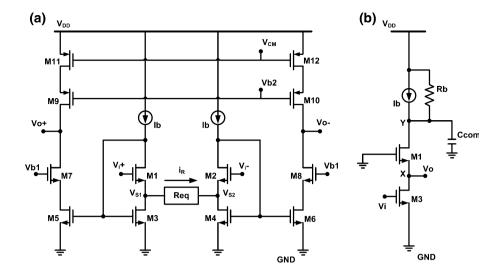

Figure 1(a) shows the implementation of the transconductor, and the circuit is designed based on the FVF structure. The FVF structure composed by transistors M1 (M2), M3 (M4), and bias current Ib is a very efficient low-voltage implementation. Because the follower is biased at the drain terminal rather the source terminal, the circuit behaves as the conventional source follower with even lower output impedance. Due to the shunt feedback through transistor M3 (M4), the equivalent impedance at the source of transistor M1 (M2) is given by

$$Ro_{eq} = \frac{1}{gm_1gm_3ro_1} \tag{1}$$

where parameters gmi and roi are the transconductance and the output resistance of transistor Mi, respectively. The output resistance is a relatively low impedance value

**Fig. 1** a The proposed transconductor circuit. b Open loop model of the FVF circuit

compared with the conventional structure, and some of the design constrain can be relaxed under the FVF structure as well. In the proposed circuit, an equivalent resistor Req is used to perform the voltage-to-current conversion. The input voltage  $V_{\rm in} = V_{\rm i} + -V_{\rm i}$  is applied to the resistor through the very low output impedance buffers. Thus, the negative feedback loop would force  $V_{\rm i} + -V_{\rm i} - = V_{\rm S1} - V_{\rm S2}$  to perform the voltage-to-current conversion. We can find that the current  $i_R = (V_i + -V_i -)/Req$ , and thus the transconductance would be affected by the value of the equivalent resistance. The current flowing through transistor M3 (M4) is mirrored to transistor M5 (M6) while the drain current  $I_{\rm D1}$  ( $I_{\rm D2}$ ) would be biased to the current source Ib. In addition, the cascode output stage is used to maintain the required gain of the transconductor. The stability of the transconductor is determined by the stability of the FVF buffers, and thus the stability of shunt feedback should be taken into consideration. For the FVF circuit, if we open the loop at the gate of M3 and provide a test voltage source, as illustrated in Fig. 1(b), the open loop gain of  $AOL = -gm_1ROLY$  would be obtained, where ROLY is the equivalent impedance at node Y. The circuit has a dominant pole at node Y which equals to 1/ROLYCY and a non-dominant pole at node X which equals to 1/ROL-XCX, where ROLX is the equivalent impedance at node X. For stability issues, the non-dominate pole should be larger then twice the gain bandwidth of the circuit, and thus the constrain  $CX/CY < gm_1/4gm_3$  should be maintained. The condition is easily achieved by proper sizing of transistors M1 (M2) and M3 (M4). Moreover, to further improve circuit stability, a compensating capacitor Ccom could be also added at the drain node of transistor M1 (M2).

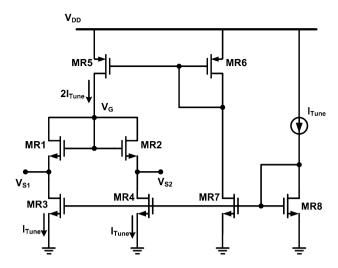

In order to add the tuning ability for the transconductor, active devices, instead of a passive resistor, are used

to implement an equivalent resistor with the drawback of the degraded linearity performance. Figure 2 shows the equivalent resistor circuit. If the transistors MR1 and MR2 are working in the saturation region, we could find

$$i_{\rm R1} = I_{\rm Tune} - i_{\rm R} = \frac{1}{2}K(V_{\rm G} - V_{\rm S1} - V_{\rm th})^2$$

(2)

$$i_{R2} = I_{Tune} + i_{R} = \frac{1}{2}K(V_{G} - V_{S2} - V_{th})^{2}$$

(3)

where K is the MOS strong inversion parameter and  $V_{\rm th}$  is the MOS threshold voltage. By subtracting Eq. 2 from Eq. 3, the current  $i_{\rm R}$  which flows through the equivalent resistor would be given by

$$i_{\rm R} = \frac{1}{4}K(V_{\rm S1} - V_{\rm S2})[2(V_{\rm G} - V_{\rm th}) - (V_{\rm S1} + V_{\rm S2})]$$

(4)

When we combine the equivalent resistor circuit into the transconductor, as shown in Fig. 1(a), the DC voltage at nodes  $V_{\rm S1}$  and  $V_{\rm S2}$  could be defined as

$$V_{\rm S1} = V_{\rm cm} + \frac{V_{\rm d}}{2} - V_{\rm SF} \tag{5}$$

$$V_{\rm S2} = V_{\rm cm} - \frac{V_{\rm d}}{2} - V_{\rm SF} \tag{6}$$

where  $V_{\rm cm}$  is the input common-mode voltage,  $V_{\rm d}$  is the input differential-mode voltage, and  $V_{\rm SF}$  is the voltage shift from the FVF circuit. By substituting 5 and 6 into 4, we can obtain

$$i_{\rm R} = \frac{1}{2} K V_{\rm d} (V_{\rm G} - V_{\rm th} - V_{\rm cm} + V_{\rm SF})$$

(7)

From Eq. 7, we can find that the output current has a linear relationship with the input voltage, and the transconductance can be tuned by adjusting the gate voltage of

Fig. 2 The equivalent resistor circuit

transistors MR1 and MR2. In our final resistor circuit implementation, the bias current  $I_{\text{Tune}}$  could be changed to choose the gate voltage and thus the transconductance can also be tuned, as shown in Fig. 2. The above design carried out was analyzed based on the assumption that transistors operate in the strong inversion region. However, if the provided current  $I_{\text{Tune}}$  is small enough, the equivalent resistor would operate in the moderate or weak inversion region to provide smaller transconductance. Similar analysis can be also performed by giving

$$i_{R1} = I_{Tune} - i_{R} = I_{D1} \exp\left(\frac{V_{G} - V_{S1}}{nU_{T}}\right)$$

(8)

$$i_{R2} = I_{Tune} + i_{R} = I_{D1} \exp\left(\frac{V_{G} - V_{S2}}{nU_{T}}\right)$$

(9)

where  $I_{\rm D1}$  is the reverse saturation current, n is the subthreshold slope factor, and  $U_{\rm T}$  is the thermal voltage. By subtracting Eq. 8 from Eq. 9 and substituting Eqs. 5 and 6 into it, the output current which could be approximated through a Taylor series expansion is given by

$$i_{\rm R} = V_{\rm d} \left( \frac{I_{\rm D1}}{nU_{\rm T}} \right) \left( 1 + \frac{V_{\rm G} - V_{\rm cm} + V_{\rm SF}}{nU_{\rm T}} \right)$$

(10)

Again, the linear relationship confirms the circuit operation and thus the proposed transconductor can operate to achieve a wider tuning range for multi-mode wireless applications.

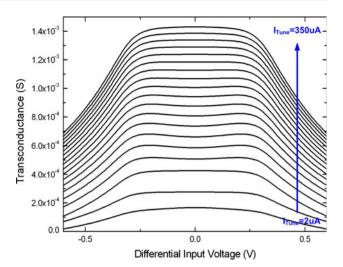

The transconductor was designed in the TSMC 0.18 µm Deep N-WELL CMOS process, and thus body effects can be simply eliminated by connecting the source and the bulk terminals together in the design. Figure 3 shows the large signal simulation with respect to the function of differential input voltage. The magnitude of Ib is 200 uA in this design. When the current Ib is large, the gate voltage of

Fig. 3 The Gm range of the proposed transconductor

transistors M3 and M4 becomes large and the source voltage of transistors M1 and M2 becomes small. Therefore, transistors M3 and M4 will enter the triode region under large input swing, and the linearity performance is degraded. On the opposite, when the current Ib is small, transistors M3 and M4 will enter the weak inversion region, and thus the limited transconductance is shown. In this design, the required transconductance and linearity should be maintained, and the optimal value of current Ib is swept by simulation. The tuning range of the transconductance is from 50 uS to 1.4 mS. Compared with the traditional tuning range ratio of less than 5 [7], the ratio of the proposed circuit is 28, and a wide tuning range is achieved. In 7 and 10, the value of voltage  $V_G$  is defined by the tuning current  $I_{\text{Tune}}$ , and the calculated value of equivalent resistance is 5 K. When we adjust the bias current, the value changes from 1 to 30 K and the result is consistent with simulation. We should note that a small aspect ratio of transistors MR1 and MR2 is required, so the equivalent resistance circuit is biased from weak inversion region to saturation region. For the linearity performance, the simulated THD of -56 dB is obtained by giving a 12 MHz 0.4Vpp input swing signal under a power consumption of 2 mW.

### 3 Conclusions

A CMOS implementation of a wide tuning range transconductor is presented. The transconductor is designed based on the FVF structure and an equivalent resistor circuit. Instead of a passive resistor, the active resistor could work in the weak, moderate, and strong inversion regions to extend the transconductance tuning range. Through the use of the transconductor as a building block, we can

design the multi-mode circuit for the wireless and mobile applications. The theoretical analysis of the high performance operation and the simulation results are provided to demonstrate the validity of the transconductor.

**Acknowledgments** The authors would like to thank the National Chip Implementation Center of Taiwan for providing the TSMC 180-nm CMOS process.

#### References

- 1. Lo, T. Y., & Hung, C. C. (2008). A 40 MHz double differential-pair CMOS OTA with -60 dB IM3. *IEEE Transactions on Circuits and Systems I*, 55(2), 258–265.

- Lo, T.Y., & Hung, C.C. (2006). High speed and high linearity OTA in 1-V power supply voltage. In *Proceedings IEEE* international symposium on circuits and systems, 1864–1867.

- 3. Fischer, T. W., Karsilayan, A. I., & Sanchez-Sinencio, E. (2005). A rail-to-rail amplifier input stage with ± 0.35% gm fluctuation. *IEEE Transactions on Circuits and Systems I*, 52(2), 271–282.

- Masoom, A., & Hadidi, Kh. (2006). A 1.5-V, constant-gm, rail-torail input stage operational amplifier. In *Proceedings of interna*tional conference on electronics circuits and systems, (pp. 632–635). Phoenix.

- Hori, S., et al. (2003). A widely tunable CMOS Gm-C filter with a negative source degeneration resistor transconductor. In *Proceedings of IEEE solid-state circuits conference* (pp. 449–452). Lisbon.

- Carvajal, R. G., et al. (2005). The flipped voltage follower: A useful cell for low-voltage low-power circuit design. *IEEE Transactions on Circuits and Systems I*, 52(7), 1276–1291.

- Yodprasit, U., & Enz, C. C. (2003). A 1.5-V 75-dB dynamic range third-order Gm-C filter integrated in a 0.18-um standard digital cmos process. *IEEE Journal of Solid-State Circuits*, 38(7), 1189–1197.

Tien-Yu Lo received the B.S., M.S., and Ph.D. degrees in communication engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2001, 2003, and 2007, respectively. Since 2008, he has been with MediaTek Inc., as an analog IC designer. His research interests include low-voltage analog and mixed-signal integrated circuits.

Chung-Chih Hung was born in Tainan, Taiwan. He received the B.S. degree in electrical engineering from National Taiwan University, Taipei, Taiwan, in 1989, and the M.S. and Ph.D. degrees in electrical engineering from The Ohio State University, Columbus, Ohio, in 1993 and 1997, respectively. From 1989 to 1991, he served in the Taiwan Marine Corps as a communication officer. From 1997 to 2003, he worked for several IC design companies in San Jose, CA, and

San Diego, CA, where he held analog circuit design manager and director positions. Since 2003, he has been with National Chiao Tung University, Hsinchu, Taiwan, where he is currently an Associate Professor in the Department of Electrical Engineering. His research interests include the design of analog and mixed-signal integrated circuits for communication and high-speed applications.