ELSEVIER

Contents lists available at SciVerse ScienceDirect

# Materials Chemistry and Physics

journal homepage: www.elsevier.com/locate/matchemphys

# Enhanced performance and reliability of NILC-TFTs using FSG buffer layer

# Chien-Chih Chen, YewChung Sermon Wu\*, Chih-Pang Chang

Department of Material Science and Engineering, National Chiao Tung University, 1001 University Road, Hsinchu 300, Taiwan, ROC

### ARTICLE INFO

Article history: Received 16 December 2010 Received in revised form 30 September 2011 Accepted 30 November 2011

Keywords: Fluorinated-silicate-glass (FSG) Polycrystalline silicon thin-film transistors (poly-Si TFTs) Ni-metal-induced lateral crystallization (NILC)

#### ABSTRACT

A new manufacturing method for Ni-metal-induced lateral crystallization thin film transistors (NILC-TFTs) using fluorine-silicate-glass (FSG) was proposed. In FSG-TFTs, fluorine ion was implanted into the buffer oxide layer to form FSG before NILC processes. It was found FSG-TFTs exhibit high field-effect mobility, low threshold voltage, low subthreshold slope, high ON/OFF current ratio, low trap state density, low interface trap state density, and good reliability compared with typical NILC-TFTs.

© 2011 Elsevier B.V. All rights reserved.

## 1. Introduction

Polycrystalline silicon thin-film transistors (poly-Si TFTs) had been widely used in active-matrix organic light emitting diode (AMOLED) because they exhibit good electrical properties and can be integrated in peripheral circuits on inexpensive glass substrates [1]. Since poly-Si TFTs require glass substrates, intensive studies have been carried out to lower the crystallization temperature of amorphous silicon (a-Si) films. Ni-metal-induced lateral crystallization (NILC) was one of the effective methods that could crystallize at a temperature below 600 °C [2,3]. Unfortunately, poly-Si/oxide interfaces and grain boundaries trap Ni and NiSi<sub>2</sub>, which increases trap state density, shifts threshold voltage, and lowers field-effect mobility [4,5]. Recently, fluorine ion implantation was employed to improve the electrical performance of TFTs [6,7]. It was found that fluorine atoms effectively minimize the trap state density and improve NILC-TFTs' electrical properties and reliabilities [8].

In early research, fluorine ion was also used to improve TFT performance [9–11]. To avoid implantation damage, fluorine ion was implanted through a pad oxide before into active layer [9,10]. If fluorine ion was implanted directly into active layer (without a pad oxide), the implantation may damage the channel (poly-Si surfaces) and lower fluorine passivation effects [11].

In this paper, fluorinated-silicate-glass (FSG) process was developed to reduce this implantation damage and improve the

performance of NILC-TFTs. The TFT devices with FSG buffer layer not only can prevent the implant damage also save a pad oxide fabrication.

# 2. Experiment

The NILC-TFTs with FSG layer (FSG-TFTs) fabrication process began with capping Si wafers with 500-nm-thick wet thermal oxide. To fabricate FSG-TFTs, the fluorine ion was implanted into the thermal oxide layer to form fluorine-silicate-glass (FSG). The projection range of fluorine ion was set at under the top surface of the FSG layer and the accelerating energy was 30 keV.

To investigate the effect of fluorine content in FSG layer on the performances of TFTs, two types of FSG-TFTs were fabricated. They were denoted as F2E12-TFT ( $2\times10^{12}$  cm $^{-2}$  dosages) and F2E15-TFT ( $2\times10^{15}$  cm $^{-2}$  dosages). Next, a 100-nm-thick undoped amorphous silicon (a-Si) layer was deposited by low pressure chemical vapor deposition (LPCVD) at 550 °C. The 5-nm-thick line-patterned Ni was deposited on the a-Si, subsequently annealed at 530 °C for 48 h to form the NILC poly-Si film. After the crystallization of the a-Si, the active regions were defined by reactive ion etching (RIE). The 100-nm-thick TEOS oxide was deposited by plasma-enhanced CVD (PECVD) for gate oxide and 100-nm-thick poly-Si film was deposited by LPCVD for gate electrodes. P\*-ion was implanted at a dose of  $5\times15$  cm $^2$  to form the source/drain and gate after defining the gate pattern. The activation of the source/drain regions was realized by the thermal furnace under N<sub>2</sub> ambient at 600 °C for 24 h.

For the purpose of comparison, the NILC-TFTs were also subjected to the same processes but without fluorine ion implantation.

<sup>\*</sup> Corresponding author. Tel.: +886 3 5131555; fax: +886 3 5724727. E-mail address: sermonwu@stanfordalumni.org (Y.S. Wu).

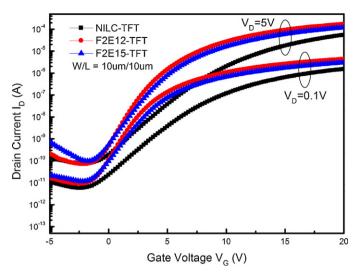

**Fig. 1.**  $I_D$ – $V_G$  transfer characteristics of TFTs.

#### 3. Results and discussion

Fig. 1 illustrates the  $I_{\rm D}$ – $V_{\rm G}$  transfer characteristics of TFTs (W/L = 10/10  $\mu$ m) with and without FSG. The measured and extracted key device parameters were summarized in Table 1. It was found FSG-TFTs (F2E12-TFT and F2E15-TFT) exhibit high field-effect mobility ( $\mu_{\rm FE}$ ), low threshold voltage ( $V_{\rm TH}$ ), low subthreshold slope (S.S.) and high ON/OFF current ratio ( $I_{\rm ON}/I_{\rm OFF}$ ) compared with NILC-TFTs. This indicates the trap state density ( $N_{\rm T}$ ) was effectively reduced using FSG.

The trap state density of the TFTs was extracted using Levinson and Proano's method, which can estimate the  $N_{\rm T}$  from the slope of the linear segment of  $\ln[I_{\rm DS}/(V_{\rm GS}-V_{\rm FB})]$  vs.  $1/(V_{\rm GS}-V_{\rm FB})^2$  at low  $V_{\rm DS}$  and high  $V_{\rm GS}$ , where  $V_{\rm FB}$  is defined as the gate voltage that yields the minimum drain current at  $V_{\rm DS}=0.1$  [12,13]. As shown in Table 1, the trap state densities of F2E12-TFT and F2E15-TFT were less than those of NILC-TFTs.

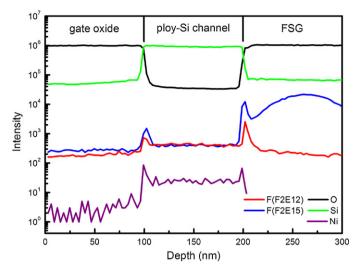

In NILC poly-Si, there are two kinds of defects related to trap state density  $(N_T)$ : (1) grain boundary defects and (2) Ni-related defects. These defects would degrade electric performance because they introduced dangling bonds and strain bonds [4,5]. Secondaryion mass spectroscopy (SIMS) was used to study the distribution of Ni and F. Fig. 2 shows the depth profile of the F2E12 and F2E15 gate-oxide/poly-Si/buffer-oxide structure. High Ni and high F contents are both present at the poly-Si/buffer-oxide interface. This observation suggested that fluorine atoms have diffused to the interface/boundaries to terminate Ni-related trap states and boundary defects. As a result, the trap state density  $(N_T)$  was reduced, and electrical characteristics were improved [6–8]. This F diffusion behavior might be because most of the Ni-related defects (residues) were located at the interface between poly-Si and oxide. As a result, F atoms diffused to interface to passivate these defects, which including dangling bonds and strain bonds by forming strong Si-F bonds [8]. Besides, since the NILC poly-Si film is only 100 nm, F atoms have enough time to reach the interface during the subsequently procedures (including 600 °C, 24 h).

**Fig. 2.** SIMS depth profile of fluorine, oxygen, silicon and nickel the atoms of F2E12-TFT and F2E15-TFT.

However, the performance of F2E15-TFT was poorer than that of F2E12-TFT, as shown in Fig. 1. This is because F content in the active layer was higher than F solubility ( $[F]_{RT}$ ) in the Si at room temperature. As mentioned earlier, F ions were implanted into the thermal oxide layer. With the subsequently activation process (600 °C, 24h), F atoms have enough time to diffuse to interface to passivate defects. At the same time, F content in the active layer reached F solubility  $[F]_{600 \, ^{\circ}\text{C}}$ , which is much higher than  $[F]_{RT}$ . As a result, when devices were cooled down to the room temperature, F content in the active layer was higher than the F solubility ( $[F]_{RT}$ ).

This is consistent with our SIMS measurements. As shown in Fig. 2, the F content inside two FSG-TFTs films were almost the same except at interface areas. This is because in both case, F contents reached  $[F]_{600\,^{\circ}C}$ . Extra F atoms were trapped at interfaces, where most of Ni-related defects (residues) were. As a result, the excess F atoms in F2E15-TFT segregated and formed fluorine clusters at interfaces. These fluorine clusters would not passivate the trap states but increase the defects and then degrade the electrical performances [8,14]. As shown in Table 1, the  $N_{\rm T}$  of F2E15-TFT was higher than that of F2E12-TFT.

As mentioned earlier, most Ni residues (Ni-related defects) were located at the Si/oxide interface (Fig. 2) and formed trap states. The interface trap state density ( $N_{\rm it}$ ) near the poly-Si/gate oxide interface could be calculated as:

$$N_{\rm it} = \left[ \left( \frac{\rm S.S.}{\ln 10} \right) \left( \frac{q}{kT} \right) - 1 \right] \left( \frac{C_{\rm ox}}{q} \right)$$

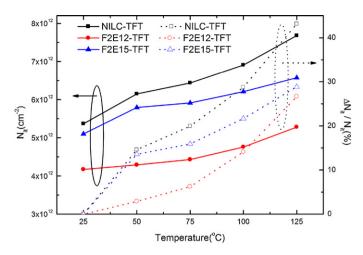

where  $C_{\rm ox}$  was gate oxide capacitance [15]. As shown in Fig. 3,  $N_{\rm it}$  of FSG-TFTs was less than those of NILC-TFTs. Besides,  $N_{\rm it}$  of TFTs increased with temperature. This increase implies that leakage current increases with the devices working temperature due to the thermal excited trapped carriers [16]. Compared with those of NILC-TFTs, the  $N_{\rm it}$  degradation (thermal stability) of FSG-TFTs was improved by FSG processes. This was because of the passivation of dangling bonds and strain bonds at the poly-Si/oxide interface by fluorine atoms.

**Table 1** Device characteristics of NILC-TFT, F2E12-TFT and F2E15-TFT.

|           | $\mu_{	ext{FE}}(	ext{cm}^2/	ext{Vs})$ | V <sub>TH</sub> (V) | S.S. (V/dec) | $I_{\rm ON}/I_{\rm OFF}$ (10 <sup>6</sup> ) | $N_{\rm T}  (10^{12}  {\rm cm}^{-2})$ |

|-----------|---------------------------------------|---------------------|--------------|---------------------------------------------|---------------------------------------|

| NILC-TFT  | 55.1                                  | 6.12                | 2.13         | 0.56                                        | 4.61                                  |

| F2E12-TFT | 97.5                                  | 2.48                | 1.14         | 2.36                                        | 2.25                                  |

| F2E15-TFT | 79.4                                  | 3.00                | 1.41         | 1.22                                        | 3.23                                  |

**Fig. 3.** The interface trap state density and their variation versus temperature for NILC-TFT, F2E12-TFT and F2E15-TFT.

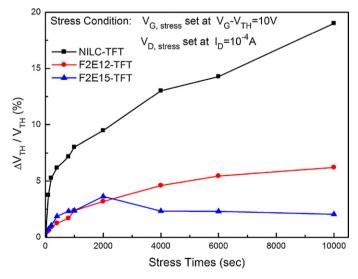

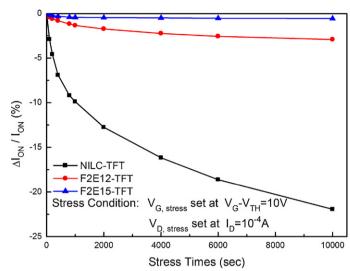

The other important issue of poly-Si TFTs is their reliability, which was examined under hot-carrier stress. The DC stress condition was set gate voltage  $V_{\rm C,stress}$  at  $V_{\rm G}-V_{\rm TH}=10\,\rm V$  and drain voltage  $V_{\rm D,stress}$  at  $I_{\rm D}=10^{-4}\,\rm A$ . The stress time was  $10,000\,\rm s$ . As shown in Figs. 4 and 5, the  $V_{\rm TH}$  and the  $I_{\rm ON}$  of TFTs were degraded. This was because when TFTs were under the DC stress operation, hot-carrier would impact into drain side and create broken bonds due to the weak Si-Si bonds and Si—H bonds. Those broken bonds or dangling bonds would increase the trap state density, leading to the degradation of electrical characteristics [17,18]. Compared with those of NILC-TFTs, the  $V_{\rm TH}$  variation and  $I_{\rm ON}$  degradations of FSG-TFTs were greatly improved. This was because the weaker Si—Si bonds and Si—H bonds in FSG-TFTs were replaced by the stronger Si—F bonds which appeared excellent electrical endurance against hot-carrier impact.

Although the electrical reliabilities were enhanced by fluorine-ion incorporating in poly-Si, it was also found the electrical degradation of F2E12-TFT was worse than that of F2E15-TFT, as shown in Figs. 4 and 5. On account of the F2E12-TFT has the highest  $\mu_{\rm FE}$ , the hot-carrier impact effects would be more serious. When TFT devices were under working, the electron will be accelerated by the applied drain electric field. The higher  $\mu_{\rm FE}$  implies that the less electron scattering while electron transferring from source to

**Fig. 4.** Threshold voltage variation versus stress time for NILC-TFT, F2E12-TFT and F2E15-TFT.

**Fig. 5.** ON-current degradation versus stress time for NILC-TFT, F2E12-TFT and F2E15-TFT.

drain, so the degradation of electrical performances was greater due to the electron with higher energy [19].

### 4. Conclusion

An investigation of the effects of FSG buffer layer on the electrical characteristics and reliability of NILC-TFTs has led to the development of a simple, effective process for improving the NILC-TFTs electrical properties. This was because F atoms could passivate dangling bonds and strain bonds. It was also found that FSG process could greatly alleviate the threshold voltage and the ON-current degradations under hot-carrier stress. This was due to the weaker Si—H and Si—Si bonds were replaced by stronger Si—F bonds, thus leading to improved electrical reliability. However, the excess fluorine atoms would not passivate the trap states but increase the defects and then degrade the electrical performances.

### Acknowledgments

This project was funded by Sino American Silicon Products Incorporation and the NSC of the ROC under Grant No. 98-2221-E-009-041-MY3. Technical supports from the National Nano Device Laboratory, Center for Nano Science and Technology and the Nano Facility Center of the National Chiao Tung University are also acknowledged.

### Appendix A. Supplementary data

Supplementary data associated with this article can be found, in the online version, at doi:10.1016/j.matchemphys.2011.11.080.

## References

- M. Stewart, R.S. Howell, L. Pires, M.K. Hatalis, IEEE Trans. Electron Devices 48 (2001) 845.

- [2] S.W. Lee, S.K. Joo, IEEE Electron Device Lett. 17 (1996) 160.

- [3] Z. Meng, M. Wang, M. Wong, IEEE Trans. Electron Devices 47 (2000) 404.

- [4] P.J. van der Zaag, M.A. Verheijen, S.Y. Yoon, N.D. Young, Appl. Phys. Lett. 81 (2002) 3404.

- [5] G.A. Bhat, Z. Jin, H.S. Kwok, M. Wong, IEEE Electron Device Lett. 20 (1999) 97.

- [6] C.H. Tu, T.C. Chang, P.T. Liu, C.Y. Yang, H.C. Liu, W.R. Chen, Y.C. Wu, C.Y. Chang, IEEE Electron Device Lett. 27 (2006) 262.

- [7] C.H. Tu, T.C. Chang, P.T. Liu, H.W. Zan, Y.H. Tai, C.Y. Yang, Y.C. Wu, H.C. Liu, W.R. Chen, C.Y. Chang, Electrochem. Solid-State Lett. 8 (2005) G246.

- [8] C.P. Chang, Y.S. Wu, IEEE Electron Device Lett. 28 (2007) 467.

- [9] H.N. Chern, C.L. Lee, T.F. Lei, IEEE Trans. Electron Devices 41 (1994) 698.

- [10] C.L. Fan, M.C. Chen, Electrochem. Solid-State Lett. 5 (2002) G75.

- [11] J.W. Park, B.T. Ahn, K. Lee, Jpn. J. Appl. Phys. Part 1 34 (1995) 1436.

- [12] J. Levinson, G. Este, M. Rider, P.J. Scanlon, F.R. Shepherd, W.D. Westwood, J. Appl. Phys. 53 (1982) 1193.

- [13] R.E. Proano, R.S. Misage, D.G. Ast, IEEE Trans. Electron Devices 36 (1989) 1915.

- [14] C.H. Tu, T.C. Chanf, P.T. Liu, C.H. Chen, C.Y. Yang, Y.C. Wu, H.C. Liu, L.T. Chang, C.C. Tsai, S.M. Sze, C.Y. Chang, J. Electrochem. Soc. 153 (2006) G815.

- [15] C.A. Dimitriadis, P.A. Coxon, L. Dozsa, L. Papadimitriou, N. Economou, IEEE Trans. Electron Devices 39 (1992) 598.

- [16] T.K. Kim, G.B. Kim, B.I. Lee, S.K. Joo, IEEE Electron Device Lett. 16 (2000) 347.

- [17] S. Banerjee, R. Sundraesan, H. Shichijo, S. Malhi, IEEE Trans. Electron Devices 35 (1988) 152.

- [18] M. Hack, A.G. Lewis, I.W. Wu, IEEE Trans. Electron Devices 40 (1993) 890.

- [19] C.H. Tu, T.C. Chang, P.T. Liu, C.Y. Yang, L.W. Feng, C.C. Tsai, L.T. Chang, Y.C. Wu, S.M. Sze, C.Y. Chang, J. Disp. Technol 3 (2007) 45.