# $V_t$ Retention Distribution Tail in a Multitime-Program MLC SONOS Memory Due to a Random-Program-Charge-Induced Current-Path Percolation Effect

Yueh-Ting Chung, Tzu-I Huang, Chi-Wei Li, You-Liang Chou, Jung-Piao Chiu, Tahui Wang, *Senior Member, IEEE*, M. Y. Lee, Kuang-Chao Chen, and Chih-Yuan Lu, *Fellow, IEEE*

Abstract—A  $V_t$  retention distribution tail in a multitimeprogram (MTP) silicon-oxide-nitride-oxide-silicon (SONOS) memory is investigated. We characterize a single-program-chargeloss-induced  $\Delta V_t$  in NOR-type SONOS multilevel cells (MLCs). Our measurement shows the following: 1) A single-charge-lossinduced  $\Delta V_t$  exhibits an exponential distribution in magnitudes, which is attributed to a random-program-charge-induced currentpath percolation effect, and 2) the standard deviation of the exponential distribution depends on the program-charge density and increases with a program  $V_t$  level in an MLC SONOS. In addition, we measure a  $V_t$  retention distribution in a 512-Mb MTP SONOS memory and observe a significant  $V_t$  retention tail. A numerical  $V_t$  retention distribution model including the percolation effect and a Poisson-distribution-based multiple-charge-loss model is developed. Our model agrees with the measured  $V_t$  retention distribution in a 512-Mb SONOS well. The observed  $V_t$  tail is realized mainly due to the percolation effect.

Index Terms—Model, percolation, silicon–oxide–nitride–oxide–silicon (SONOS),  $V_t$  retention distribution.

# I. INTRODUCTION

S ILICON-OXIDE-nitride-oxide-silicon (SONOS) Flash memory has received much interest because it offers better performance with small cell size, fast program/erase, and memory retention improvement than a floating-gate (FG) Flash memory [1] cells with a vertical gate [2], [3] have been considered as a promising candidate for a 3-D nonvolatile memory

Manuscript received November 28, 2011; revised January 19, 2012; accepted February 13, 2012. Date of publication April 3, 2012; date of current version April 25, 2012. The work of Y.-T. Chung, T.-I. Huang, C.-W. Li, Y.-L. Chou, J.-P. Chiu, and T. Wang was supported in part by the National Science Council, Taiwan, under Contract NSC-99-2221-E009-171-MY3 and in part by the Ministry of Education, Taiwan, under the ATU Program. The review of this paper was arranged by Editor R. Huang.

Y.-T. Chung, T.-I. Huang, C.-W. Li, Y.-L. Chou, J.-P. Chiu, and T. Wang are with the Department of Electronics Engineering and the Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: twang@cc.nctu.edu.tw).

M. Y. Lee and K.-C. Chen are with Macronix International Company, Ltd., Hsinchu 300. Taiwan.

C.-Y. Lu is with Macronix International Company, Ltd., Hsinchu 300, Taiwan, and also with Ardentec Corporation, Hsinchu 303, Taiwan.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2012.2188531

in terabit storage applications. However, as the scaling of the SONOS technology advances aggressively, significant variations of  $V_t$  retention loss in SONOS cells are observed because of a reduced number of stored charges [4]. For a technology node beyond 45 nm, only tens of electrons are stored in each program level of a multilevel cell (MLC) SONOS. A singlecharge loss would induce a large variation in read current and sometimes result in a read failure. Two kinds of single-charge phenomena in a Flash cell have been reported. One is the switching of a read current between two current levels, referred to as random telegraph noise (RTN), due to single-charge emission and capture at an interface oxide trap. The other is discrete program-charge retention loss, which is manifested by a stepwise increase of read current versus retention time [4]. The RTN amplitudes in FG Flash and SONOS cells have been studied extensively [5]. The RTN amplitudes are found to follow an exponential distribution approximately in both FG and SONOS cells due to a current-path percolation effect [6], [7]. As for a single-program-charge-loss-induced  $\Delta V_t$ , SONOS and FG Flash cells, however, exhibit different characteristics. In an FG cell, program charges are stored in a conducting and equipotential FG. Thus, each program-charge loss has the same weight and contributes the same  $\Delta V_t$  [8]. Unlike those in an FG cell, program charges in a SONOS are stored randomly and discretely in an insulating silicon nitride layer. The current percolation paths in a channel are therefore affected by random placement of nitride program charges [4], [5], [9]. A programcharge loss at different positions of a nitride may result in a large difference in  $\Delta V_t$  due to a percolation effect. In this paper, we characterize a single-program-charge-loss-induced  $\Delta V_t$  in different program levels in a NOR-type MLC SONOS. An RTNinduced  $\Delta V_t$  distribution is also characterized for comparison.

In addition, we measure a  $V_t$  distribution in a 512-Mb SONOS before and after 1000-h retention. A significant postretention  $V_t$  tail is observed. To examine the cause of the  $V_t$  tail bits, we develop a numerical  $V_t$  distribution model based on the current-path percolation effect and a Poisson-distribution-based multiple-charge-loss model [10]. An analytical description of the  $V_t$  tail bit distribution is derived. We evaluate the tail bit distributions from the percolation effect and multiple-charge loss, respectively. By using the model, we simulate a  $V_t$  tail in different program levels of an MLC SONOS.

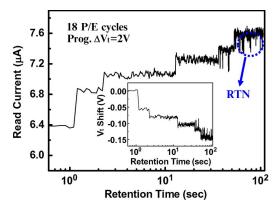

Fig. 1. Read current versus cumulative retention time in a P/E cycle SONOS. The measurement consists of two alternating phases, namely, retention phase and read phase. To accelerate program-charge loss, a negative gate voltage of  $-5~\rm V$  was applied in the retention phase. The inset shows a corresponding  $V_t$  retention trace.

# II. SINGLE-PROGRAM-CHARGE-LOSS-INDUCED $\Delta V_t$

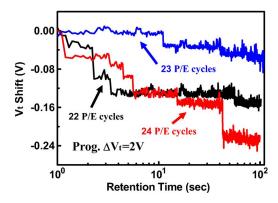

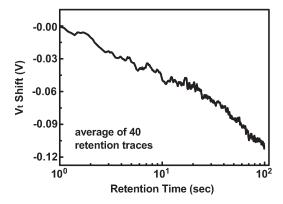

NOR-type SONOS cells in this work are fabricated with a 0.1- $\mu m$  technology. The gate width (W) and length (L) are  $W/L = 0.1 \, \mu \text{m}/0.14 \, \mu \text{m}$ . The thicknesses of top oxide, silicon nitride, and bottom oxide are 7, 6, and 5.5 nm, respectively. Channel hot electron program and band-to-band hot hole erase are employed with a reverse read scheme [11]. The program and erase bias conditions are  $V_g/V_s = 8.5 \text{ V}/4.2 \text{ V}$  and  $V_g/V_s =$ -7 V/4 V, respectively. To characterize a single-programcharge-loss-induced  $\Delta V_t$ , our measurement consists of two alternating phases, namely, retention loss phase and read phase. The  $V_d$  in read phase is 1.5 V. To accelerate program-charge loss, a negative gate bias of -5 V was applied in the retention phase. Fig. 1 shows the evolution of a read current with cumulative retention time in an 18-P/E-cycle SONOS cell. Discrete nitride-program-charge loss is clearly observed, which is manifested by sudden jumps in a read current. Each current jump is realized due to a single-program-charge loss [4]. Two-level RTN is also noticed in the figure. A corresponding  $V_t$  retention trace is plotted in the inset of the figure, which is obtained from the measured current divided by a transconductance at the read current. The reason why we measure a read current rather than a threshold voltage directly is that the current measurement has a better resolution. It should be mentioned that the magnitude of a single-charge-induced  $\Delta V_t$  varies from program charge to program charge. This feature is different from an FG Flash cell, where each program-charge loss should induce the same  $V_t$  shift. Moreover, we measure  $V_t$  retention traces at three different P/E cycles. The result is shown in Fig. 2. Because the placement of program charges changes at a different P/E cycle, the  $V_t$  retention trace varies from cycle to cycle, suggesting that current percolation paths in program state are determined by the injected program charges. An average of  $V_t$  retention traces in 40 devices is shown in Fig. 3. The  $\log(t)$  dependence of  $V_t$  retention loss in Fig. 3 is consistent with a Frenkel-Poole charge emission model [12].

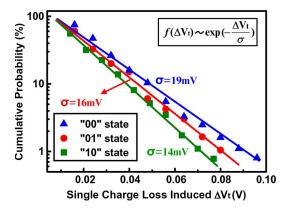

We collect all the  $V_t$  jumps from more than 80 retention traces in different P/E cycles in a total of 40 devices. The cumulative probability distribution of the  $\Delta V_t$  magnitude is shown in Fig. 4 in three program levels ("10," "01," and "00,"

Fig. 2. Program  $V_t$  retention traces as a function of cumulative retention time at three consecutive P/E cycles (22, 23, and 24 cycles).

Fig. 3. Average of  $V_t$  retention traces in 40 SONOS cells. A  $\log(t)$  retention time dependence is observed. A negative gate voltage of -5 V was applied in retention for accelerating charge loss.

Fig. 4. Cumulative probability distribution of a single-program-charge-loss-induced  $\Delta V_t$  in an MLC SONOS. The program  $V_t$  levels are  $\Delta V_t=1$  V for "10,"  $\Delta V_t=2$  V for "01," and  $\Delta V_t=3$  V for "00." The distribution at each program level is measured at  $V_d=1.5$  V and  $I_d=6~\mu\mathrm{A}$ . The gate overdrive is about 0.6 V.

which are defined as program  $V_t$  windows of 1, 2, and 3 V, respectively.). Data points with  $\Delta V_t$  less than 5 mV are not drawn here because of the resolution of the measurement. In Fig. 4, we find the following: 1) The  $\Delta V_t$  magnitude distribution in each program level can be approximated by an exponential function  $f(\Delta V_t) = \exp(-\Delta V_t/\sigma)/\sigma$ , and 2) the  $\sigma$  increases with a program  $V_t$  level. To explain the reason for an increasing  $\sigma$  with a program  $V_t$  level in a SONOS cell, we perform a 2-D numerical device simulation by ISE-TCAD for the three program  $V_t$  levels. The read  $V_d$  is 1.5 V, and the  $V_g$  is

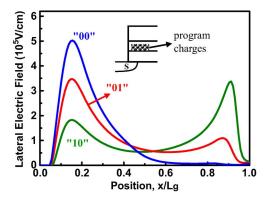

Fig. 5. Calculated channel lateral field distributions in "10," "01," and "00" states. The read  $V_d$  is 1.5 V, and the read  $V_g$  is chosen to keep the read current at 6  $\mu$ A. The CHE program charge has a uniform distribution in a 15-nm region above the source junction, as shown in the figure.

Fig. 6. Measured  $V_t$  distributions in a 512-Mb NOR-type MTP SONOS memory immediately after program and after 1000-h retention. No gate stress voltage was applied in retention. A postretention  $V_t$  distribution tail is highlighted.

adjusted to keep the read current level at 6  $\mu$ A. The simulated lateral electric field profiles are shown in Fig. 5. The highest  $V_t$  level has the largest lateral electric field E beneath a program-charge region (i.e., near the source junction in Fig. 5). From a first-order approximation, a single-charge-loss-induced  $\Delta I_d$  is proportional to  $q\mu E$ . Thus, a program-charge loss at a higher program  $V_t$  level results in larger  $\Delta V_t$  and  $\sigma$  because of a larger E under a program-charge region.

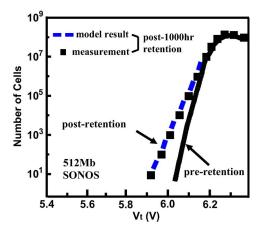

In addition to single device data, we measure a  $V_t$  retention distribution in a 512-Mb SONOS memory. The program  $V_t$  distributions immediately after program and after 1000-h retention are shown in Fig. 6. The program window is 2 V, and the P/E cycle number is about ten [multitime program (MTP)]. In Fig. 6, we find that the main part of the  $V_t$  distributions before the retention and that after the retention match very well, suggesting that the majority of the cells do not have program-charge loss. Aside from the main distribution, we clearly observe a tail in the postretention  $V_t$  distribution, which is highlighted in Fig. 6. The spread of the  $V_t$  tail is about 0.16 V.

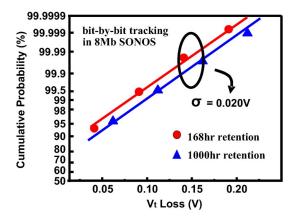

We further measure a postretention  $V_t$  shift by bit-by-bit tracking in an 8-Mb MTP SONOS array. The cumulative probability distributions of the  $V_t$  shift are plotted in Fig. 7 at two retention times: 168 and 1000 h. Two points should be noted. First, the tail of the  $V_t$  shift can be well fitted by an exponential

Fig. 7. Cumulative probability distributions of  $V_t$  retention loss at two retention times (168 and 1000 h) in an 8-Mb MTP SONOS are measured by bit-by-bit tracking. The solid lines represent an exponential distribution with a  $\sigma$  value of 0.020 V.

distribution (solid lines in Fig. 7), and the extracted  $\sigma$  value is about 0.02 V. Second, the  $V_t$  loss tail increases with retention time, which provides evidence that the measured  $\Delta V_t$  loss tail is caused by program-charge loss rather than RTN. Furthermore, we would like to make a note about the comparison of RTN amplitudes and a program-charge-loss-induced  $\Delta V_t$ . We measure RTN amplitudes in 30 SONOS cells. The  $\sigma$  value of RTN is about  $\Delta V_t = 12$  mV, which is significantly smaller than the  $\sigma$  value of a program-charge-loss-induced  $\Delta V_t$ . The reason is that RTN traps in MTP SONOS cells are randomly distributed in the channel and only a small part of the RTN traps are in the program-charge region of about 15 nm [13]. As pointed out earlier, a charge loss in a high-lateral-field region (programcharge region), whether an RTN charge or a program charge, yields a larger  $\Delta V_t$ . Thus, most of the RTN-induced  $\Delta V_t$  values are small. This can explain why program-charge loss rather than RTN dominates the  $V_t$  retention tail in a 512-Mb SONOS memory.

# III. Modeling of $V_t$ Retention Distribution

In this section, a numerical model to simulate a  $V_t$  retention distribution is developed. Our model includes a program-charge-induced percolation effect and a Poisson-distribution-based multiple-charge-loss model. The distribution function of a single-program-charge-loss-induced  $\Delta V_t$  is expressed as

$$f(\Delta V_t) = \frac{1}{\sigma} \exp\left(-\frac{\Delta V_t}{\sigma}\right) \tag{1}$$

where  $\sigma$  is an average value of  $\Delta V_t$  and also the standard deviation of the distribution. Assume that  $g(V_t)$  is a program  $V_t$  distribution immediately after program, which can be obtained from measurement. The  $V_t$  distribution after a single-charge loss is calculated from a convolution integral of  $f(\Delta V_t)$  and  $g(V_t)$ , i.e.,

$$f(\Delta V_t) * g(V_t) \equiv \int f(\Delta V_t) g(V_t + \Delta V_t) d\Delta V_t$$

(2)

where the symbol \* presents a convolution integral. Therefore, the postretention  $V_t$  distribution  $h(V_t)$  can be derived from (2)

Fig. 8. Modeled and measured  $V_t$  distributions after 1000-h retention. The  $\sigma$  value used in the model is 0.020 V. The  $\lambda$  value is equal to 0.1. The integration interval of the convolution integral is 0.625 mV. The preretention distribution is also plotted as a reference.

and weighted by the probability of a Poisson distributed number of program-charge loss  $P_{\lambda}(n)$ , as described in the following:

$$P_{\lambda}(n) = \frac{e^{-\lambda} \lambda^n}{n!}.$$

(3)

$P_{\lambda}(n)$  denotes the probability of n-program-charge loss in a cell, and  $\lambda$  is an average number of charge losses in a cell. The postretention  $V_t$  distribution finally can be expressed as

$$h(V_t) = P_{\lambda}(0)g(V_t) + P_{\lambda}(1)f(\Delta V_{t1}) * g(V_t) + P_{\lambda}(2)f(\Delta V_{t2}) * (f(\Delta V_{t1}) * g(V_t)) + \cdots$$

(4)

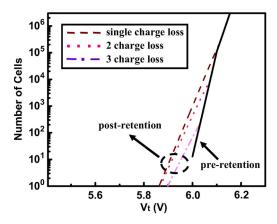

where the first term  $P_{\lambda}(0)g(V_t)$  represents the cells without charge loss and the second term  $P_{\lambda}(1)f(\Delta V_{t1})*g(V_t)$  and the third term  $P_{\lambda}(2) f(\Delta V_{t2}) * (f(\Delta V_{t1}) * g(V_t))$  represent a single-charge loss and a two-charge loss, respectively. Other terms for loss of more than two charges can be expressed in a similar way. The model is used to simulate a  $V_t$  retention distribution in a 512-Mb MTP SONOS. In the simulation,  $\sigma$  is obtained from measurement (20 mV in Fig. 7), and  $\lambda$  is treated as a fitting parameter. The measurement and model results are shown in Fig. 8. Our model fits the measured distribution well with  $\lambda = 0.1$ . This small value of  $\lambda$  is reasonable in an MTP operation. In order to compare the contributions from multiplecharge loss and from the percolation effect to the  $V_t$  tail, we calculate the single-, two-, and three-charge-loss-induced  $V_t$  retention tails according to (4). The result is shown in Fig. 9. The single-charge loss dominates a postretention  $V_t$  tail because a single-charge-loss probability is much larger than the probability of multiple-charge loss. This result reveals that the  $V_t$  retention loss tail in a SONOS memory is mainly attributed to a random-program-charge-induced percolation effect.

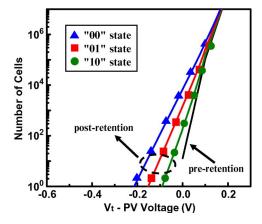

In addition, we simulate the percolation-effect-induced  $V_t$  retention tail in different program levels of an MLC SONOS memory. The parameter  $\lambda$  is assumed to be proportional to a program  $V_t$  window as a first-order approximation. The reason is that an average number of charge losses  $(\lambda)$  should be dependent on the number of stored charges in a cell and the latter is proportional to a program window. For simplicity, we assume that each program level has the same initial program

Fig. 9. Calculation of single-, two-, and three-charge-loss-induced  $V_t$  retention tails. The  $V_t$  retention distribution tail is mainly contributed by the percolation effect.

Fig. 10. Calculated  $V_t$  retention distribution tail in different program levels of an MLC SONOS. The  $V_t$  retention tail is plotted with reference to a PV voltage.

$V_t$  distribution  $g(V_t)$ . The simulation result is plotted in Fig. 10 with reference to a program verify (PV) voltage. The highest program level ("00") apparently has the largest  $V_t$  retention tail due to a larger percolation effect, i.e., a larger  $\sigma$ . The large  $V_t$  tail may cause a read error in an MLC and requires the use of an error code correction technique [14].

## IV. CONCLUSION

We observe and characterize discrete program-charge loss in a SONOS cell. A single-program-charge-loss-induced  $\Delta V_t$  exhibits approximately an exponential distribution due to a random-program-charge-induced percolation effect. The program-charge-loss-induced  $\Delta V_t$  is larger than an RTN-induced  $\Delta V_t$  in a NOR-type SONOS. A  $V_t$  retention distribution model including the percolation effect and Poissondistribution-based multiple-charge-loss model has been developed. Our model can simulate a postretention  $V_t$  distribution in an MTP SONOS memory. Our simulation confirms that the observed postretention  $V_t$  distribution tail is attributed to the percolation effect, a unique characteristic in a SONOS memory. Our study further shows that the  $V_t$  distribution tail increases with a program  $V_t$  level in a NOR-type MLC SONOS. The percolation effect and the  $V_t$  loss tail are expected to be more pronounced in further scaling of the SONOS technology.

### REFERENCES

- [1] M. H. White, D. Adams, and J. Bu, "On the go with SONOS," *IEEE Circuits Devices Mag.*, vol. 16, no. 4, pp. 22–31, Jul. 2000.

- [2] W. Kim, S. Choi, J. Sung, T. Lee, C. Park, H. Ko, J. Jung, I. Yoo, and Y. Park, "Multi-layered vertical gate NAND Flash overcoming stacking limit for terabit density storage," in *Proc. VLSI Symp.*, 2009, pp. 188–189.

- [3] H. T. Lue, T. H. Hsu, Y. H. Hsiao, S. P. Hong, M. T. Wu, F. H. Hsu, N. Z. Lien, S. Y. Wang, J. Y. Hsieh, L. W. Yang, T. Yang, K. C. Chen, K. Y. Hsieh, and C. Y. Lu, "A highly scalable 8-layer 3D vertical-gate (VG) TFT NAND Flash using junction-free buried channel BE-SONOS device," in *Proc. VLSI Technol. Symp.*, 2010, pp. 131–132.

- [4] Y. L. Chou, Y. T. Chung, T. Wang, S. H Gu, N. K. Zou, V. Chen, W. P. Lu, K. C. Chen, and C.-Y. Lu, "Variations of V<sub>t</sub> retention loss in a SONOS Flash memory due to a current-path percolation effect," *IEEE Electron Device Lett.*, vol. 32, no. 4, pp. 458–460, Apr. 2011.

- [5] J. P. Chiu, Y. L. Chou, H. C. Ma, T. Wang, S. H. Ku, N. K. Zou, V. Chen, W. P. Chen, and C.-Y. Lu, "Program charge effect on random telegraph noise amplitude and its device structural dependence in SONOS Flash memory," in *IEDM Tech. Dig.*, 2009, pp. 1–4.

- [6] A. Asenov, R. Balasubramaniam, A. R. Brown, and J. H. Davies, "RTS amplitudes in decananometer MOSFETs: 3-D simulation study," *IEEE Trans. Electron Devices*, vol. 50, no. 3, pp. 839–845, Mar. 2003.

- [7] A. Ghetti, C. M. Compagnoni, A. S. Spinelli, and A. Visconti, "Comprehensive analysis of random telegraph noise instability and its scaling in deca-nanometer Flash memories," *IEEE Trans. Electron Devices*, vol. 56, no. 8, pp. 1746–1752, Aug. 2009.

- [8] L. Guo, E. Leobandung, and S. Y. Chou, "A room-temperature silicon single-electron metal-oxide-semiconductor memory with nanoscale floating-gate and ultranarrow channel," *Appl. Phys. Lett.*, vol. 70, no. 7, pp. 850–852, Feb. 1997.

- [9] A. Mauri, C. M. Compagnoni, S. M. Amoroso, A. Maconi, A. Ghetti, A. S. Spinelli, and A. L. Lacaita, "Comprehensive investigation of statistical effects in nitride memories—Part I: Physics-based modeling," *IEEE Trans. Electron Devices*, vol. 57, no. 9, pp. 2116–2123, Sep. 2010.

- [10] R. E. Walpole, R. H. Myers, S. L. Myers, and K. Ye, Probability and Statistics for Engineers and Scientists, 9th ed. Upper Saddle River, NJ: Pearson Educ., 2010, p. 161.

- [11] B. Eitan, P. Pavan, I. Bloom, E. Aloni, A. Frommer, and D. Finzi, "NROM: A novel localized trapping, 2-bit nonvolatile memory cell," *IEEE Electron Device Lett.*, vol. 21, no. 11, pp. 543–545, Nov. 2000.

- [12] W. J. Tsai, N. K. Zous, C. J. Liu, C. C. Liu, C. H. Chen, W. Tahui, S. Pan, C.-Y. Lu, and S. H. Gu, "Data retention behavior of a SONOS type two-bit storage Flash memory cell," in *IEDM Tech. Dig.*, Dec. 2001, pp. 32.6.1–32.6.4.

- [13] H. C. Ma, Y. L. Chou, J. P. Chiu, Y. T. Chung, T. Y. Lin, T. Wang, Y. P. Chao, K. C. Chen, and C.-Y. Lu, "A novel random telegraph signal method to study program/erase charge lateral spread and retention loss in a SONOS Flash memory," *IEEE Trans. Electron Devices*, vol. 58, no. 3, pp. 623–630, Mar. 2011.

- [14] Z. Wang, J. Zhang, and Y. Ge, "Design and simulate of ECC circuit for multilevel Flash memory," in *Proc. Int. Conf. ISDEA*, 2010, vol. 1, pp. 536–538.

Yueh-Ting Chung was born in Kaohsiung, Taiwan, in 1986. He received the B.S. and M.S. degrees in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2009 and 2010, respectively, where he is currently working toward the Ph.D. degree in the Department of Electronics Engineering and the Institute of Electronics.

His research interests include reliability analysis in nonvolatile memory devices with random telegraph noise and retention loss.

**Tzu-I Huang** was born in Hsinchu, Taiwan, in 1989. She received the B.S. degree in electronics engineering from National Chiao Tung University, Hsinchu, in 2011, where she is currently working toward the M.S. degree in electronics engineering in the Department of Electronics Engineering and the Institute of Electronics.

Her research interests include random telegraph noise in Flash memory devices.

Chi-Wei Li was born in Chiayi, Taiwan, in 1989. He received the B.S. degree in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2011, where he is currently working toward the M.S. degree in the Department of Electronics Engineering and the Institute of Electronics.

His research interests are reliability analysis in high-k devices and random telegraph noise.

You-Liang Chou received the B.S. degree in electrical engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2006, where he is currently working toward the Ph.D. degree in the Department of Electronics Engineering and the Institute of Electronics.

His research interests include the study of microscopic mechanisms in Flash memory devices, reliability analysis in semiconductor memory, and high-voltage devices.

Jung-Piao Chiu was born in Kaohsiung, Taiwan, in 1985. He received the B.S. degree in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2007, where he is currently working toward the Ph.D. degree in electronics engineering in the Department of Electronics Engineering and the Institute of Electronics.

His research interests are reliability analysis in high-k devices and Monte Carlo simulation.

**Tahui Wang** (S'85–M'86–SM'94) received the B.S. degree in electrical engineering from National Taiwan University, Taipei, Taiwan, and the Ph.D. degree in electrical engineering from the University of Illinois, Urbana.

From 1985 to 1987, he was with Hewlett-Packard Laboratories, Palo Alto, CA. Since 1987, he has been with the Department of Electronics Engineering and the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, where he is currently a Professor. Since 2000, he has been a Consultant

with Macronix International Company, Ltd., Hsinchu, working on nonvolatile memory technology. He is currently an Associate Editor of the *Journal of Computational Electronics*. He has published more than 200 journal and conference papers. He is the holder of 18 patents. His current research interests include Flash memory devices, CMOS reliability and modeling, high-voltage/high-power devices, and charge transport simulation in nanostructures.

Dr. Wang served on the technical program committees of the International Electron Devices Meeting (IEDM); IEEE International Reliability Physics Symposium; International Symposium on VLSI Technology, Systems and Applications; and Asia Symposium on Quality Electronic Design. He also served as the Tutorial Chair of the 2004 International Symposium on the Physical and Failure Analysis of Integrated Circuits and an Electron Device Society Newsletter Editor for region 10 (Taiwan, Hong Kong, and China). He was an Invited Speaker on the topic of SONOS Flash memory reliability of the 2003 IEDM. He is currently an Editor for the IEEE ELECTRON DEVICE LETTERS. He was the recipient of the Best Teaching Award from the Ministry of Education, Taiwan, and the Best Paper Award of the 2004 IPFA and a corecipient of the Best Student Paper Award of the 2005 VLSI Symposium on Technology.

M. Y. Lee, photograph and biography not available at the time of publication.

**Kuang-Chao Chen** received the M.S. degree in chemistry from National Chong-Shan University, Kaohsiung, Taiwan, in 1987.

From 1989 to 1995, he was with the Electronic Research and Service Organization, Hsinchu, Taiwan, where he was involved in the development of backend-of-line planarization process technology. From 1995 to 1998, he was with Mosel-Vitelic International Company, Ltd., Hsinchu. He performed yield improvement in the manufacturing line. In 1998, he was with Vanguard International Semiconductor

Company, Ltd., Hsinchu, as a Department Manager. He was responsible for thin-film module development. Since 2000, he has been with Macronix International Company, Ltd., Hsinchu, where he worked on advanced module development and is currently the Executive Director of the Technology Development Center.

**Chih-Yuan Lu** (M'77–SM'84–F'94) received the B.S. degree from National Taiwan University, Taipei, Taiwan, in 1972 and the Ph.D. degree in physics from Columbia University, New York, NY, in 1977.

From 1984 to 1989, he was a Professor with National Chiao Tung University, Hsinchu, Taiwan, and AT&T Bell Laboratories, Murray Hill, NJ. In 1989, he was with the Electronic Research and Service Organization/Industrial Technology Research Institute (ITRI) as the Deputy General Director responsible for the MOEA grand Submicron Project. This

project successfully developed Taiwan's first 8-in manufacturing technology with high-density dynamic random-access memory (RAM)/static RAM. In 1994, he cofounded Vanguard International Semiconductor Corporation, which is a spinoff memory integrated circuit company from ITRI's Submicron Project, in which he was the Vice President of Operation, Vice President of R&D, and, later, President from 1994 to 1999. He is currently the Chairman and CEO of Ardentec Corporation, Hsinchu, which is a very large scale integration testing service company. He was also a Senior Vice President/Chief Technology Officer of Macronix International Company, Ltd., Hsinchu, where he is currently the President. He led Macronix's Technology Development Team to successfully achieve the state-of-the-art nonvolatile memory technology and is currently responsible for Macronix's overall operation. He has authored more than 200 published papers. He is the holder of 135 worldwide patents.

Dr. Lu is a Fellow of the American Physical Society. He was the recipient of the IEEE Millennium Medal and the Most Prestigious Semiconductor R&D Award in Taiwan from Pan Wen Yuan Foundation and the highest honor prize, i.e., the National Science and Technology Achievement Award, from the Prime Minister of Taiwan for his leadership and achievement in the Submicron Project.