## Charge trapping induced drain-induced-barrier-lowering in HfO2/TiN p-channel metaloxide-semiconductor-field-effect-transistors under hot carrier stress

Wen-Hung Lo, Ting-Chang Chang, Jyun-Yu Tsai, Chih-Hao Dai, Ching-En Chen, Szu-Han Ho, Hua-Mao Chen, Osbert Cheng, and Cheng-Tung Huang

Citation: Applied Physics Letters 100, 152102 (2012); doi: 10.1063/1.3697644

View online: http://dx.doi.org/10.1063/1.3697644

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/100/15?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Investigation of abnormal negative threshold voltage shift under positive bias stress in input/output n-channel metal-oxide-semiconductor field-effect transistors with TiN/HfO2 structure using fast I-V measurement Appl. Phys. Lett. **104**, 113503 (2014); 10.1063/1.4868532

Physical understanding of different drain-induced-barrier-lowering variations in high-k/metal gate n-channel metal-oxide-semiconductor-field-effect-transistors induced by charge trapping under normal and reverse channel hot carrier stresses

Appl. Phys. Lett. 103, 183502 (2013); 10.1063/1.4826918

Abnormal threshold voltage shift under hot carrier stress in Ti1xNx/HfO2 p-channel metal-oxide-semiconductor field-effect transistors

J. Appl. Phys. 114, 124505 (2013); 10.1063/1.4822158

Abnormal sub-threshold swing degradation under dynamic hot carrier stress in HfO2/TiN n-channel metal-oxide-semiconductor field-effect-transistors

Appl. Phys. Lett. 103, 022106 (2013); 10.1063/1.4811784

Hot-carrier charge trapping and trap generation in HfO 2 and Al 2 O 3 field-effect transistors

J. Appl. Phys. **94**, 1728 (2003); 10.1063/1.1586985

## Charge trapping induced drain-induced-barrier-lowering in HfO<sub>2</sub>/TiN p-channel metal-oxide-semiconductor-field-effect-transistors under hot carrier stress

Wen-Hung Lo, <sup>1</sup> Ting-Chang Chang, <sup>1,2,a)</sup> Jyun-Yu Tsai, <sup>1</sup> Chih-Hao Dai, <sup>3</sup> Ching-En Chen, <sup>4</sup> Szu-Han Ho, <sup>4</sup> Hua-Mao Chen, <sup>5</sup> Osbert Cheng, <sup>6</sup> and Cheng-Tung Huang <sup>6</sup> <sup>1</sup>Department of Physics, National Sun Yat-Sen University, Kaohsiung, Taiwan

(Received 12 February 2012; accepted 1 March 2012; published online 9 April 2012)

This letter studies the channel hot carrier stress (CHCS) behaviors on high dielectric constant insulator and metal gate HfO<sub>2</sub>/TiN p-channel metal-oxide-semiconductor field effect transistors. It can be found that the degradation is associated with electron trapping, resulting in G<sub>m</sub> decrease and positive V<sub>th</sub> shift. However, V<sub>th</sub> under saturation region shows an insignificant degradation during stress. To compare that, the CHC-induced electron trapping induced DIBL is proposed to demonstrate the different behavior of V<sub>th</sub> between linear and saturation region. The devices with different channel length are used to evidence the trapping-induced DIBL behavior. © 2012 American Institute of Physics. [http://dx.doi.org/10.1063/1.3697644]

The physical limitation of the silicon dioxide (SiO<sub>2</sub>) as gate insulator has achieved the point where its thickness is approaching to a few atomic layers thick. 1,2 Below the physical thickness 12 Å, the significant gate leakage current results in a volume active power consumption, leading a worse reliability of metal-oxide semiconductor field effect transistors (MOSFETs). To avoid this serious issue, high-k dielectrics have been introduced as hafnium (Hf)-base, zirconium, aluminum oxides<sup>3-6</sup> and heavily investigated as a replacement for conventional SiO<sub>2</sub> gate insulator. However, high-k/metal gate stack has to face many critical issues such as defects in high-k material which can lead to undesired transport through the dielectrics and trapping-induced instabilities. 7-10 As MOSFETs scaling down, not only the BTI reliability at gate terminal but also hot carrier effect (HCE) which is associated with lateral electric field is important issue in MOS-FETs. Therefore, hot carrier effect in high-k/metal gate n-MOSFETs was still one of major device reliability concern. As is well known, under hot carrier injection, a high lateral electric field in pinch-off region accelerates the electrons sufficiently to gain enough energy to damage the drain side, resulting in the degradation of I-V characteristics. However, most of the studies were concentrated on n-MOSFETs. 11-14 The degradation due to hot carrier effect in p-MOSFETs with high-k/metal gate stacks has not received as much attention. Therefore, the aim of this letter is to investigate the effects of channel hot carrier stress (CHCS) on HfO<sub>2</sub>/TiN p-MOSFETs. It was found that the CHCinduced electron trapping dominates the degradation during stress, instead of interface states (Nit) creation, including Vth shift and G<sub>m</sub> decrease. As the drain voltage (V<sub>D</sub>) was applied at saturation region, there is no significant V<sub>th</sub> shift during stress. This behavior was doubted to result from trappinginduced drain-induced-barrier-lowering (DIBL). To explain this phenomenon, the device with different channel length (L) was introduced to support our model in this work.

The HfO<sub>2</sub>/TiN p-MOSFETs were studied in this paper based on the high-performance 28-nm CMOS technology. Both devices were fabricated using a conventional selfaligned transistor flow through the gate first process. For the gate first process devices, 10 Å and 30 Å of high quality thermal oxide were, respectively, grown on a (100) Si substrate as buffer oxide layers. After standard cleaning procedures, 30 Å of HfO<sub>2</sub> films were sequentially deposited by atomic layer deposition. Next, 10 nm of TiN films were deposited by radio frequency physical vapor deposition, followed by poly-Si deposition as a low resistance gate electrode. The source/drain and poly-Si gate activation were performed at 1025 °C. In this study, the dimensions of the selected devices were  $10 \,\mu m$  and 1  $\mu$ m in width and length, respectively. The device with buffer thickness of 10 A was subjected to the maximum substrate current of CHCS conditions with  $-3.6\,\mathrm{V}$  drain voltage ( $\mathrm{V_D}$ ). The stress was briefly interrupted to measure the drain current-gate voltage (ID-VG) and substrate current-gate voltage (I<sub>B</sub>-V<sub>G</sub>) transfer characteristics. The gate induced drain leakage (GIDL) current was defined under the  $V_G = 0.5 \text{ V}$  and  $V_D = -2.4 \, \text{V}$ . All experimental curves were measured using an Agilient B1500 semiconductor parameter analyzer.

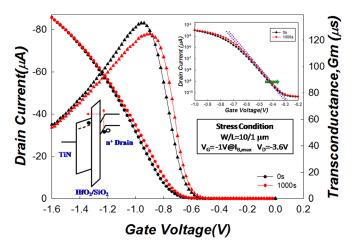

Figure 1 shows the drain current  $(I_D)$  curve versus gate voltage (V<sub>G</sub>) and corresponding transconductance (G<sub>m</sub>) of HfO<sub>2</sub>/TiN p-MOSFETs under CHCS. The stress condition  $V_G$  was selected at the maximum substrate current ( $I_{Bmax}$ ) of CHCS conditions while  $V_D = -3.6 \text{ V}$ . As the result, the degradations on device during CHCS show decrease and positive shift in transconductance (Gm) and threshold voltage

$<sup>^2</sup>$ Advanced Optoelectronics Technology Center, National Cheng Kung University, Taiwan

<sup>&</sup>lt;sup>3</sup>Department of Photonics, National Sun Yat-Sen University, Kaohsiung, Taiwan

<sup>&</sup>lt;sup>4</sup>Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan

Department of Photonics & Institute of Electro-Optical Engineering, National Chiao Tung University, Hsinchu, Taiwan

Device Department, United Microelectronics Corporation, Tainan Science Park, Taiwan

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: tcchang@mail.phys.nsysu.edu.tw.

- 0s

1.5

FIG. 1. I<sub>D</sub>-V<sub>G</sub> and corresponding G<sub>m</sub>-V<sub>G</sub> transfer characteristic curves of HfO<sub>2</sub>/TiN p-MOSFETs before and after stress. The inset shows the comparison of subthreshold slope in log ID-VG under CHCS and the energy diagram of CHC-induced trapping.

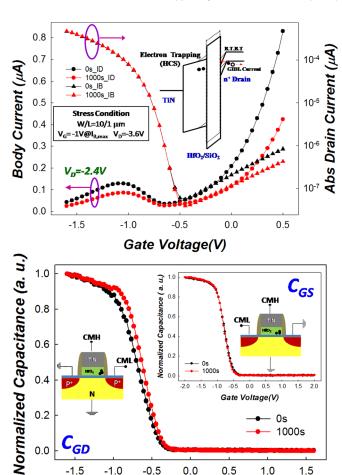

(V<sub>th</sub>), respectively. And I<sub>D</sub> seems to be invariant at  $V_G = -1.6 \text{ V}$ . Generally, the behavior of CHC effect on n-MOSFETs has a cruel degradation at drain side due to impact ionization, decreasing in I<sub>D</sub> and G<sub>m</sub>, but V<sub>th</sub> shift is insignificant unless N<sub>it</sub> generation due to higher lateral electric field during CHCS, respectively. 15 However, the V<sub>th</sub> shift toward positive direction is obtained under CHCS for high-k/Metal gate p-MOSFETs as shown in Fig. 1. We suggest that V<sub>th</sub> shift and decrease in G<sub>m</sub> could result from electron trapping in high-k layer during stress. When electronhole pairs are produced by impact ionization, the stressing potential difference between gate and drain (V<sub>GD</sub>) makes electron tend to inject to gate side, resulting in V<sub>th</sub> shift. Simultaneously, the field-effect mobility (G<sub>m</sub>) is also influenced by charge trapping, enhancing the channel scattering.  $^{16-18}$  However,  $V_{th}$  shift due to electron trapping should make I<sub>D</sub> increasing, but the scattering reduces the channel-mobility and decreases I<sub>D</sub>. Because those two causes are antagonistic in I<sub>D</sub> then resulting an invariant in I<sub>D</sub>. Additionally, the inset of Fig. 1 shows the I<sub>D</sub>-V<sub>G</sub> curve under semi-logarithmic scale before and after CHCS. It can be found that the degradation of subthreshold slope (SS) is insignificant, illustrating the N<sub>it</sub> is less. Therefore, this result supports our assumption that the degradation of V<sub>th</sub> is induced by electron trapping in high-k layer located at drain side, instead of CHC-induced Nit. In order to solid the claim, the effect of CHCS on the characteristics of I<sub>B</sub>-V<sub>G</sub> and  $I_D$ - $V_G$  measured at  $V_D = -2.4 \text{ V}$  are shown in Figure 2(a). It can be seen that the GIDL current and/or IB current at VG > 0.5 V gradually increased during CHCS. This result implies that electrons are trapped in HfO<sub>2</sub> layer within drain side to bend the band upward, therefore elongating the path of band to band tunneling during CHCS. Consequently, it can decrease the GIDL current and/or IB current at  $V_G > 0.5 \text{ V}$  as I-V measurement. The corresponding energy diagram is shown in the inset of Fig. 2(a). Additionally, the C-V curve shows the occurrence of electron trapping near drain side as shown in Figure 2(b). It can be seen that the capacitance of gate terminal to drain terminal versus gate voltage (C<sub>GD</sub>-V<sub>G</sub>) curve shifts in positive direction after CHCS, which is consistent with the linear I<sub>D</sub>-V<sub>G</sub> result in Fig. 1.

FIG. 2. (a) I<sub>D</sub>-V<sub>G</sub> and corresponding I<sub>B</sub>-V<sub>G</sub> transfer characteristic curves under  $V_D = -2.4 \, V$  as a function of stress time during CHCS for devices. The inset shows the energy diagram of GIDL behavior under CHCS. (b) Normalized C<sub>GD</sub>-V<sub>G</sub> curve before and after CHCS and its measurement method. The inset shows Normalized CGS-VG curve before and after CHCS and its measurement method.

Gate Voltage(V)

-0.5

0.2

0.0

-1.5

-1.0

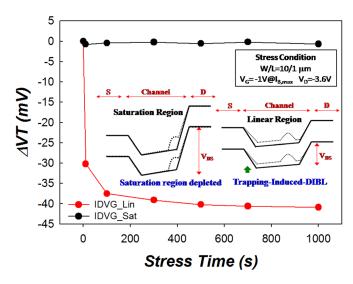

However, the capacitance of gate terminal to source terminal versus gate voltage  $(C_{GS}-V_G)$  curve has on significant change before and after stress, demonstrating the degradation is located at drain side. As well as, those experimental data are consistent with the suggestion of degradation which is dominated by CHC-induced electron trapping within drain side we declared. However, the occurrence of electron trapping at drain side still has insufficient justification to vary V<sub>th</sub> with insignificant N<sub>it</sub> generation. In order to comprehend how comes the V<sub>th</sub> shift under CHCS, we extract the degraded tendency of V<sub>th</sub> versus stress time in linear and saturation region, which are defined Lin-V<sub>th</sub> and Sat-V<sub>th</sub>, respectively. Figure 3 shows the CHCS degradation of Lin-V<sub>th</sub> and Sat-V<sub>th</sub> versus stress time. The Lin-V<sub>th</sub> was extracted from  $G_{\text{mmax}}$  and corresponding gate voltage at  $I_D = 10^{-5}$  A is selected for Sat-V<sub>th</sub>. It can be observed that an obvious shift on Lin-V<sub>th</sub>, but Sat-V<sub>th</sub> seem almost to be invariant under CHCS. As the result, the mechanism is deduced by trappinginduced DIBL. As electron-hole pairs are created by CHC impact ionization, CHC-induced electrons could be trapped into HfO<sub>2</sub> layer within drain side, which has been evidenced previously. As electron trapping occurs, it could bend channel potential upward to help the linear V<sub>D</sub> (Lin-V<sub>D</sub>) to

FIG. 3. The CHCS-induced Lin-V<sub>th</sub> and Sat-Vth shift for HfO<sub>2</sub>/TiN p-MOSFETs with  $L=1\,\mu m$ . The inset shows the trapping-induced DIBL mechanism due to CHC-induced electron-trapping under linear and saturation region.

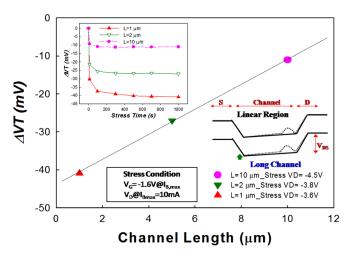

deplete channel, therefore lowering the source barrier as the illustration shown in the inset of Fig. 3. Nevertheless, under saturation region, higher V<sub>D</sub> could deplete the trappinginduced potential variation to dominate the lateral electric field in channel, expressing an invariant in Sat-V<sub>th</sub> as shown in the inset of Fig. 3. This is because the original  $I_D$ - $V_G$  characteristic before stress has a conventional DIBL, resulting in a shift between Lin-V<sub>th</sub> and Sat-V<sub>th</sub> about 30 mV (not shown on here). If the Sat-V<sub>th</sub> will be changed, the more significant trapping behavior which is greater than the influence of Sat-V<sub>D</sub> should be required. According to our argument, the devices with long channel length were selected to prove the mechanism. Figure 4 shows the Lin-V<sub>th</sub> shift versus stress time on HfO<sub>2</sub>/TiN p-MOSFETs under CHCS with different L, including 1  $\mu$ m and 10  $\mu$ m. In order to keep the equivalent probability of trapping, the close impact ionization rate is considered by choosing similar I<sub>Bmax</sub> to control the same amount of electron-hole pairs. Due to the  $10\ mA\ I_{Bmax}$ , the long channel devices L = 10 and  $2 \mu m$  have a corresponding  $V_D$  are -4.5 V and -3.8 V, respectively. Figure 4 shows the Lin-V<sub>th</sub> shift under CHCS for HfO<sub>2</sub>/TiN p-MOSFETs with different channel length L. It can be found that the Lin-V<sub>th</sub> has a positive shift on all the devices, regardless of different channel length. However, the Lin-V<sub>th</sub> shift has a negative related to channel length L. The device with the longest channel corresponds to the most insignificant shift under CHCS, since the behavior of trapping-induced DIBL is suppressed by long channel device. This is because the potential variation due to electron trapping is growingly hard to extend to source side as channel length increases under Lin-V<sub>D</sub>. Therefore, the Lin-V<sub>th</sub> on long channel device has an insignificant degradation which is consistent with the model we supported. Consequently, the Lin-V<sub>th</sub> shift on HfO<sub>2</sub>/TiN pchannel MOSFETs under CHCS results from electron trapping has been generalized in this work.

This letter studies the CHCS behaviors on  $HfO_2/TiN$  p-channel MOSFETs. We found that the degradations result from electron trapping, leading  $G_{\rm m}$  decrease and positive

FIG. 4. The relation of Lin-V $_{th}$  shift versus channel length for HfO $_2$ /TiN p-MOSFETs under CHCS. The inset shows the Lin-V $_{th}$  shift versus stress time for HfO $_2$ /TiN p-MOSFETs with L=1  $\mu$ m, 2  $\mu$ m and 10  $\mu$ m under CHCS and the illustration of trapping-induced DIBL behavior for long channel devices.

Lin- $V_{th}$  shift, but Sat- $V_{th}$  shows an insignificant degradation during stress. This dissimilar behavior of  $V_{th}$  is attributed to CHC-induced electron trapping induced DIBL. The devices with different channel length are introduced into evidence of trapping-induced DIBL behavior. As the result, the slightest Lin-Vth shift is corresponding to the  $HfO_2/TiN$  p-channe MOSFET with the longest channel length.

Part of this work was performed at United Microelectronics. The work was supported by the National Science Council under Contract Corporation NSC100-2120-M110-003.

<sup>1</sup>D. A. Buchanan, IBM J. Res. Dev. **43**, 245 (1999).

<sup>2</sup>G. Ribes, J. Mitard, M. Denais, S. Bruyere, F. Monsieur, C. Parthasarathy, E. Vincent, and G. Ghibaudo, IEEE Trans. Device Mater. Reliab. 5, 5 (2005).

<sup>3</sup>Y. Kim, G. Gebara, M. Freiler, J. Barnett, D. Riley, J. Chen, K. Torres, J. E. Lim, B. Foran, F. Shaapur, A. Agarwal, P. Lysaght, G. A. Brown, C. Young, S. Borthakur, H. J. Li, B. Nguyen, P. Zeitzoff, G. Bersuker, D. Derro, R. Bergmann, R. W. Murto, A. Hou, H. R. Huff, E. Shero, C. Pomarede, M. Givens, M. Mazanec, and C. Werkhoven, Tech. Dig.–Int. Electron Devices Meet. **2001**, 455.

<sup>4</sup>C. Hobbs, H. Tseng, K. Reid, B. Taylor, L. Dip, L. Hebert, R. Garcia, R. Hegde, J. Grant, D. Gilmer, A. Franke, V. Dhandapani, M. Azrak, L. Prabhu, R. Rai, S. Bagchi, J. Conner, S. Backer, F. Dumbuya, B. Nguyen, and P. Tobin, Tech. Dig.—Int. Electron Devices Meet. 2001, 651.

<sup>5</sup>M. Casse, L. Thevenod, B. Guillaumot, L. Tosti, F. Martin, J. Mitard, O. Weber, F. Andrieu, T. Ernst, G. Reimbold, T. Billon, M. Mouis, and F. Boulanger, IEEE Trans. Electron Devices 53, 759 (2006).

<sup>6</sup>E. P. Gusev, in The Physics and Chemistry of SiO<sub>2</sub> and the Si-SiO<sub>2</sub> Interface - 4 (Electrochemical Society, 2000), p. 477.

<sup>7</sup>M. Casse, L. Thevenod, B. Guillaumot, L. Tosti, F. Martin, J. Mitard, O. Weber, F. Andrieu, T. Ernst, G. Reimbold, T. Billon, M. Mouis, and F. Boulanger, IEEE Trans. Electron Devices **53**, 759 (2006).

<sup>8</sup>G. Ribes, J. Mitard, M. Denais, S. Bruyere, F. Monsieur, C. Parthasarathy, E. Vincent, and G. Ghibaudo, IEEE Trans. Device Mater. Reliab. 5, 5 (2005).

<sup>9</sup>S. Zafar, A. Callegari, E. Gusev, and M. V. Fischetti, J. Appl. Phys. 93, 9298 (2003).

<sup>10</sup>C. H. Dai, T. C. Chang, A. K. Chu, Y. J. Kuo, W. H. Lo, S. H. Ho, C. E. Chen, J. M. Shih, H. M. Chen, B. S. Dai, G. Xia, O. Cheng, and C. T. Huang, Appl. Phys. Lett. 98, 092112 (2011).

<sup>11</sup>C. H. Dai, T. C. Chang, A. K. Chu, Y. J. Kuo, S. H. Ho, T. Y. Hsieh, W. H. Lo, C. E. Chen, J. M. Shih, W. L. Chung, B. S. Dai, H. M. Chen, G. Xia, O. Cheng, and C. T. Huang, Appl. Phys. Lett. 99, 012106 (2011).

- <sup>12</sup>I. Crupi, Microelectron. Eng. **86**, 1 (2009).

- <sup>13</sup>K. T. Lee, C. Y. Kang, O. S. Yoo, R. Choi, B. H. Lee, J. C. Lee, H. D. Lee, and Y. H. Jeong, IEEE Electron Device Lett. **29**, 389 (2008).

- <sup>14</sup>H. Park, R. Choi, B. H. Lee, S. C. Song, M. Chang, C. D. Young, G. Bersuker, J. C. Lee, and H. Hwang, IEEE Electron Device Lett. 27, 662 (2006).

- <sup>15</sup>H. Gesch, J. P. Leburton, and G. E. Dorda, IEEE Trans. Electron Devices **29**, 913. (1982).

- <sup>16</sup>C. H. Dai, T. C. Chang, A. K. Chu, Y. J. Kuo, Y. C. Hung, W. H. Lo, S. H. Ho, C. E. Chen, J. M. Shih, W. L. Chung, H. M. Chen, B. S. Dai, T. M. Tsai, G. Xia, O. Cheng, and C. T. Huang, Thin Solid Films 520, 1511 (2011).

- <sup>17</sup>G. Bersuker, P. Zeitzoff, J. H. Sim, B. H. Lee, R. Choi, G. Brown, and C. D. Young, Appl. Phys. Lett. 87, 042905 (2005).

- <sup>18</sup>J. H. Sim, S. C. Song, P. D. Kirsch, C. D. Young, R. Choi, D. L. Kwong, B. H. Lee, and G. Bersuker, Microelectron. Eng. 80, 218 (2005).