## Reliability improvement of InGaZnO thin film transistors encapsulated under nitrogen ambient

Chun-Yu Wu, Huang-Chung Cheng, Chao-Lung Wang, Ta-Chuan Liao, Po-Chun Chiu, Chih-Hung Tsai, Chun-Hsiang Fang, and Chung-Chun Lee

Citation: Applied Physics Letters 100, 152108 (2012); doi: 10.1063/1.3702794

View online: http://dx.doi.org/10.1063/1.3702794

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/100/15?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Electrical stability enhancement of the amorphous In-Ga-Zn-O thin film transistor by formation of Au nanoparticles on the back-channel surface

Appl. Phys. Lett. 102, 102108 (2013); 10.1063/1.4795536

Highly stable amorphous In-Ga-Zn-O thin-film transistors produced by eliminating deep subgap defects Appl. Phys. Lett. **99**, 053505 (2011); 10.1063/1.3622121

Investigating the degradation behavior caused by charge trapping effect under DC and AC gate-bias stress for InGaZnO thin film transistor

Appl. Phys. Lett. 99, 022104 (2011); 10.1063/1.3609873

Effect of channel thickness on density of states in amorphous InGaZnO thin film transistor Appl. Phys. Lett. **98**, 122105 (2011); 10.1063/1.3570641

Transition of dominant instability mechanism depending on negative gate bias under illumination in amorphous In-Ga-Zn-O thin film transistor

Appl. Phys. Lett. 98, 033504 (2011); 10.1063/1.3540500

## Reliability improvement of InGaZnO thin film transistors encapsulated under nitrogen ambient

Chun-Yu Wu,¹ Huang-Chung Cheng,¹ Chao-Lung Wang,¹ Ta-Chuan Liao,¹ Po-Chun Chiu,¹ Chih-Hung Tsai,² Chun-Hsiang Fang,² and Chung-Chun Lee²

<sup>1</sup>Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, 1001 University Road, Hsinchu 300, Taiwan

(Received 16 February 2012; accepted 27 March 2012; published online 11 April 2012)

The nitrogen ambient encapsulation (NAE) technique is introduced to improve the reliability issue for the amorphous InGaZnO (a-IGZO) thin-film transistors under positive gate bias stress (PGBS). For the NAE devices, the threshold voltage ( $V_{th}$ ) shift is significantly decreased from 1.88 to 0.09 V and the reduction of saturation drain current is improved from 15.75 to 5.61  $\mu$ A as compared to the bare a-IGZO counterparts after PGBS. These improvements are attributed to the suppression of negatively charged oxygen adsorption on the a-IGZO backsurface and thereby well maintain the channel potential of NAE devices, which in turn sustain the  $V_{th}$  during PGBS. © 2012 American Institute of Physics. [http://dx.doi.org/10.1063/1.3702794]

Thin film transistors (TFTs) are widely used as pixel switch in the active-matrix liquid crystal display (AMLCD). The carrier mobility and device uniformity of TFTs are well known to strongly affect the properties of AMLCD. Due to the low carrier mobility of hydrogenated amorphous silicon (a-Si:H) TFTs, a larger dimensional device is required to obtain the higher drive current and makes the a-Si:H TFTs actualize high brightness and high aperture ratio in TFT array difficultly. To overcome this problem, various crystallization methods such as excimer laser annealing have been proposed to enhance the carrier mobility, i.e., polycrystalline silicon TFTs (poly-Si TFTs). However, the uniformity of electrical characteristics in poly-Si TFTs is still a critical issue, which seriously restricted its applications. Recently, the amorphous InGaZnO TFTs (a-IGZO TFTs) have been considered as a good alternative for the AMLCD and activematrix organic light-emitting diode (AMOLED) applications due to their higher carrier mobility than the traditional a-Si:H TFTs and superior device uniformity than the poly-Si TFTs.<sup>2–4</sup> Although the high-performance a-IGZO TFTs have been proposed,<sup>2-4</sup> the poor device reliability is one of the main limitations for the commercial product exploitation.

It is already known that the ambient effects such as oxygen molecules and light illumination play important roles in the electrical degradation of metal oxide transistors.<sup>5–9</sup> The study by Kang et al. reported that the threshold voltage (V<sub>th</sub>) shift of a-IGZO TFTs was about 47 V as the oxygen pressure increased from  $8.5 \times 10^{-6}$  to 760 Torr. <sup>10</sup> Therefore, for practical application, it is necessary to fabricate the robust a-IGZO TFTs which can immunize against the unfavorable environment effects. In this work, we propose a simple method to construct a highly stable a-IGZO TFTs. In order to isolate the interference of environment atmosphere, the fabricated a-IGZO TFTs were finally encapsulated under nitrogen ambient. As compared with the bare TFT devices, the nitrogen ambient encapsulation (NAE) ones exhibit negligible V<sub>th</sub> shift and minor saturation drain current (I<sub>Dsat</sub>) reduction after DC positive gate bias stress (PGBS). The possible mechanism of the instability phenomenon is also investigated.

Bottom-gate inverted-staggered a-IGZO TFTs were fabricated on the glass substrate in this work. First, the Ti/Al/Ti (50/180/150 nm) trilayer metal film was deposited through dc-sputter system and the gate pattern was transferred by lithography process. Next, a 300-nm-thick SiN<sub>x</sub> film was deposited by plasma-enhanced chemical vapor deposition (PECVD) at 200 °C as the gate insulator. A 30-nm-thick a-IGZO active layer was then deposited by the dc-sputtering system at 300 W of plasma discharge power and 5 mTorr of process pressure in a gas mixture ratio of  $O_2/Ar = 20\%$ . Then, the thermal annealing process was carried out at 220 °C for 2 h in clean dry air ambient. After defining the active region, the 200-nm-thick SiO<sub>x</sub> as etch stop layer was deposited by PECVD at 170 °C and patterned by dry etching to open the source/drain (S/D) contact hole, followed by the Ti/Al/Ti (50/180/150 nm) metal S/D formation. Some of these samples attached with driers, named as NAE TFTs, were then simultaneously encapsulated under the nitrogen ambient by using a covered glass. A thin adhesive layer of UV glue was applied to fix the covered glass for the protection of the devices from the outer ambience. Eventually, the adhesive layer was solidified by means of UV light exposure for 10 min in N2 ambient. The photographic image of the NAE TFTs devices was shown in Fig. 1. For comparison, the conventional bare TFTs without encapsulation were also fabricated with the same process run.

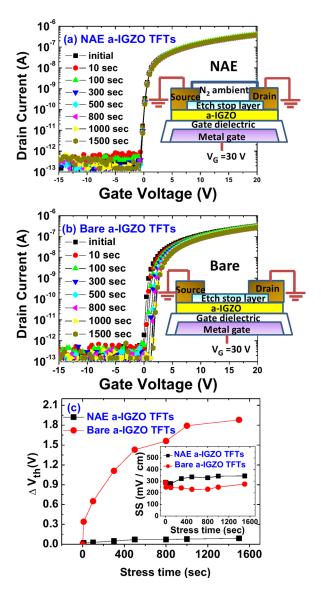

The a-IGZO TFTs with  $L=4\,\mu m$  and  $W=30\,\mu m$  are employed in this work. The  $V_{th}$  is determined at normalized drain current ( $I_{DS}\times L/W$ ) = 1 nA for  $V_{DS}=0.1$  V. The subthreshold swing (SS) is extracted from the inverse maximum slope of the semi-logarithmic  $I_{DS}$  versus  $V_{GS}$  curve at  $V_{DS}=0.1$  V. The initial  $V_{th}$ , SS, and field-effect mobility ( $\mu_{FE}$ ) are 0.44 V, 291 mV/decade, and 12.8 cm²/Vs for the NAE a-IGZO TFTs, respectively, while those values are 0.81 V, 290 mV/decade, and 12.1 cm²/Vs for the bare devices, as shown in Figs. 2(a) and 2(b). The corresponding

<sup>&</sup>lt;sup>2</sup>Advanced Display Technology Research Center, AU Optronics, No. 1, Li-Hsin Rd. 2, Hsinchu Science Park, Hsin-Chu 30078, Taiwan

FIG. 1. The photograph of the NAE a-IGZO TFTs. The dotted lines indicate the covered glass substrate that was used to isolate the interference of environment atmosphere.

cross-sectional diagrams of the NAE and bare TFTs are also plotted in Figs. 2(a) and 2(b), accordingly. Although both devices appear the similar SS and  $\mu_{FE}$ , however, the bare devices exhibit larger initial  $V_{th}$ . The oxygen adsorption on the a-IGZO surface is relatively easy for the bare TFTs, thus its initial  $V_{th}$  is significantly increased. On the contrary, the lower  $V_{th}$  of NAE devices is attributed to the reduced negatively charged oxygen adsorption on the a-IGZO backsurface.

Prior to the PGBS experiment, all the samples were cured on a hot plate at 100 °C for 2 h to decrease the influence of ambient moisture. The electrical instabilities of NAE and bare devices are performed with the DC PGBS of  $V_G = 30 \text{ V}$  and  $V_{DS} = 0 \text{ V}$  for 1500 s at room temperature as shown in Figs. 2(a) and 2(b), respectively. The V<sub>th</sub> shift as a function of bias stress duration is plotted in Fig. 2(c) and the inset shows the SS variation with the stress time. During PGBS, the parallel transfer characteristics shift to the positive direction with no significant degradation of SS for both devices are observed, which indicates that the interface state creations are negligible in a-IGZO TFTs after PGBS. However, a much greater V<sub>th</sub> shift of 1.88 V is observed for the bare devices as compared to 0.09 V for the NAE ones under the same stress time. Previous investigations have reported that a combination of the charge trapping at the dielectric/ channel layer and the oxygen adsorption at the a-IGZO backsurface is responsible for the electrical-stress degradation of a-IGZO TFTs. 11-13 Considering that both devices have an identical vertical electric field during PGBS test, the charge trapping at their dielectric/channel layers will be similar. Therefore, the remarkable V<sub>th</sub> shift of the bare TFTs is mainly ascribed to the influence of the ambient environment. Although the SiO<sub>x</sub> etch stop layer coated on the back channel region can be used as a passivation layer, the outer ambience such as oxygen molecules can still penetrate through the SiO<sub>x</sub> layer due to the less dense thin film deposited by PECVD at relatively low temperature. 14,15 As mentioned in previous oxide-semiconductor device literatures, 11,16-18 adsorption oxygen molecules on their surface would cause a charge transfer phenomenon and the reaction could be expressed in the form of  $O_2 + e^- \rightarrow O_2^-$ . As the applied gate bias is raised beyond the V<sub>th</sub> of a-IGZO TFTs, the conduction electrons [e<sup>-</sup>] in the a-IGZO thin film will be consid-

FIG. 2. The transfer characteristics of (a) NAE a-IGZO TFTs and (b) bare ones during PGBS of  $V_{\rm G}=30\,{\rm V}$  and  $V_{\rm DS}=0\,{\rm V}$  for 1500 s. The inset showed the corresponding cross-sectional diagrams. (c) Stress time dependence of  $V_{\rm th}$  shift for the NAE TFTs and bare ones. The inset showed the SS variation with the stress time for both devices.

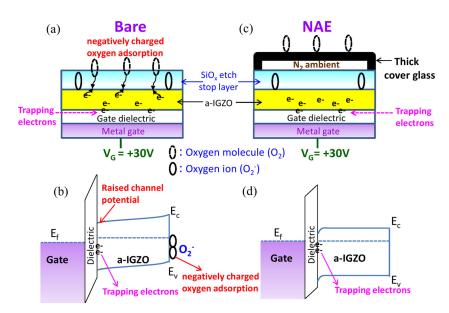

erably increased and then extracted by the surrounded oxygen molecules, resulting in a significant increase in negatively charged oxygen [O2<sup>-</sup>] adsorption on the device backsurface. For the bare TFTs, the depletion layer formed underneath the a-IGZO backsurface will therefore be enlarged and simultaneously raise the channel potential, leading to the increase of V<sub>th</sub> as the oxygen molecules are absorbed. The schematic plot and band diagram for the bare TFTs after PGBS are shown in Figs. 3(a) and 3(b) to explain the observed experimental results, respectively. In contrast, for the NAE devices, the undesirable oxygen molecules are obstructed outside the covered glass and effectively eliminate the oxygen penetration through the SiO<sub>x</sub> etch stop layer, as shown in Fig. 3(c). The corresponding band diagram of NAE devices after PGBS is also shown in Fig. 3(d). Due to the suppression of the oxygen adsorption on the a-IGZO backsurface for the NAE devices, the channel potential will not be elevated, thereby sustaining the  $V_{th}$  during PGBS.

FIG. 3. (a) The schematic plot of bare a-IGZO TFTs during PGBS of  $V_G\!=\!30\,V$  and  $V_{DS}\!=\!0\,V$ . (b) The band diagram of bare a-IGZO TFTs after PGBS. (c) The schematic plot of NAE a-IGZO TFTs during PGBS of  $V_G\!=\!30\,V$  and  $V_{DS}\!=\!0\,V$ . (d) The band diagram of NAE a-IGZO TFTs after PGBS.

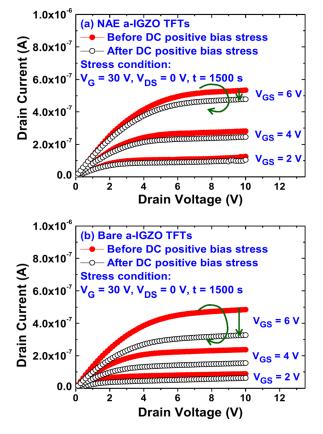

Figures 4(a) and 4(b) show the output characteristics of the NAE and bare devices after PGBS of  $V_G = 30\,\mathrm{V}$  and  $V_{DS} = 0\,\mathrm{V}$  for 1500 s, respectively. The  $I_{Dsat}$  reduction of the bare devices ( $\Delta I_{Dsat} = 15.75\,\mu\mathrm{A}$ ) after PGBS is more severe than the NAE ones ( $\Delta I_{Dsat} = 5.61\,\mu\mathrm{A}$ ) at  $V_{DS} = 10\,\mathrm{V}$  and  $V_{GS} = 6\,\mathrm{V}$ . Owing to the large amount of oxygen adsorption during PGBS for the bare devices, the  $V_{th}$  will be significantly increased to degrade the drain current. Nevertheless, the slight  $I_{Dsat}$  reduction is still observed in the NAE devices, which can be ascribed to the minor electron trapping at or near the dielectric/channel interface.

FIG. 4. The output characteristics of (a) NAE a-IGZO TFTs and (b) bare ones after PGBS of  $V_G\!=\!30\,V$  and  $V_{DS}\!=\!0\,V$  for  $1500\,s.$

In summary, the effect of nitrogen encapsulation on the electrical instabilities of a-IGZO TFTs under the DC PGBS is investigated. The NAE devices exhibit superior  $V_{th}$  stability ( $\Delta V_{th} = 0.09 \, V$ ) than the bare ones ( $\Delta V_{th} = 1.88 \, V$ ) after PGBS at  $V_G = 30 \, V$  for 1500 s. Furthermore, a small  $I_{Dsat}$  reduction of 5.61  $\mu A$  after PGBS test is also observed for the NAE TFTs as compared to 15.75  $\mu A$  for the bare ones at  $V_{DS} = 10 \, V$  and  $V_{GS} = 6 \, V$ . The improvement can be attributed to the elimination of the negatively charged oxygen adsorption on the backsurface for the NAE devices. Practically, such simple method to construct a highly stable a-IGZO TFTs is promising for the applications in AMLCD and AMOLED.

This work was supported by the National Science Council of the Republic of China under the Grant Number NSC 99-2221-E-009-168-MY3, and in part by the AU Optronics, Advanced Display Technology Research Center, for process equipment support. Also, the authors would like to thank the Nano Facility Center (NFC) of National Chiao Tung University and the National Nano Device Laboratory (NDL) for facility utilization.

<sup>&</sup>lt;sup>1</sup>J. S. Im, R. S. Sposili, and M. A. Crowder, Appl. Phys. Lett. **70**, 3434 (1997).

<sup>&</sup>lt;sup>2</sup>K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, Nature (London) **432**, 488 (2004).

<sup>&</sup>lt;sup>3</sup>J. B. Kim, C. Fuentes-Hernandez, and B. Kippelen, Appl. Phys. Lett. **93**, 242111 (2008).

<sup>&</sup>lt;sup>4</sup>J. H. Na, M. Kitamura, and Y. Arakawa, Appl. Phys. Lett. **93**, 063501 (2008).

<sup>5</sup>Q. H. Li, Q. Wan, Y. X. Liang, and T. H. Wang, Appl. Phys. Lett. **84**, 4556 (2004).

<sup>&</sup>lt;sup>6</sup>D. Zhang, C. Li, S. Han, X. Liu, T. Tang, W. Jin, and C. Zhou, Appl. Phys. Lett. 82, 112 (2006).

<sup>&</sup>lt;sup>7</sup>T.-C. Chen, T.-C. Chang, T.-Y. Hsieh, C.-T. Tsai, S.-C. Chen, C.-S. Lin, M.-C. Hung, C.-H. Tu, J.-J. Chang, and P.-L. Chen, Appl. Phys. Lett. **97**, 192103 (2010).

<sup>&</sup>lt;sup>8</sup>T.-C. Chen, T.-C. Chang, C.-T. Tsai, T.-Y. Hsieh, S.-C. Chen, C.-S. Lin, M.-C. Hung, C.-H. Tu, J.-J. Chang, and P.-L. Chen, Appl. Phys. Lett. 97, 112104 (2010).

<sup>&</sup>lt;sup>9</sup>J.-Y. Kwon, J. S. Jung, K. S. Son, K.-H. Lee, J. S. Park, T. S. Kim, J.-S. Park, R. Choi, J. K. Jeong, B. Koo, and S. Y. Lee, Appl. Phys. Lett. **97**, 183503 (2010).

<sup>&</sup>lt;sup>10</sup>D. Kang, H. Lim, C. Kim, I. Song, J. Park, Y. Park, and J. G. Chung, Appl. Phys. Lett. **90**, 192101 (2007).

<sup>&</sup>lt;sup>11</sup>J. K. Jeong, H. W. Yang, J. H. Jeong, Y.-G. Mo, and H. D. Kim, Appl. Phys. Lett. **93**, 123508 (2008).

- <sup>12</sup>Y.-C. Chen, T.-C. Chang, H.-W. Li, S.-C. Chen, J. Lu, W.-F. Chung, Y.-H. Tai, and T.-Y. Tseng, Appl. Phys. Lett. 96, 262104 (2010).

- <sup>13</sup>J.-M. Lee, I.-T. Cho, J.-H. Lee, W.-S. Cheong, C.-S. Hwang, and H.-I. Kwon, Appl. Phys. Lett. **94**, 222112 (2009).

- <sup>14</sup>A. G. Erlat, R. J. Spontak, R. P. Clarke, T. C. Robinson, P. D. Haaland, Y. Tropsha, N. G. Harvey, and E. A. Vogler, J. Phys. Chem. B, 103, 6047 (1999).

- <sup>15</sup>K. H. Ji, J.-I. Kim, H. Y. Jung, S. Y. Park, R. Choi. U. K. Kim, C. S. Hwang, D. Lee, H. Hwang, and J. K. Jeong, Appl. Phys. Lett. 98, 103509 (2011).

- <sup>16</sup>S. A. Hoenig and J. R. Lane, Surf. Sci. **11**, 163 (1968).

- <sup>17</sup>S. Strassler and A. Reis, Sens. Actuators **4**, 465 (1983).

- <sup>18</sup>J. M. Wu, Nanotechnology **21**, 235501 (2010).