# Temperature-Oriented Mobility Measurement and Simulation to Assess Surface Roughness in Ultrathin-Gate-Oxide (~1 nm) nMOSFETs and Its TEM Evidence

Ming-Jer Chen, Senior Member, IEEE, Li-Ming Chang, Shin-Jiun Kuang, Chih-Wei Lee, Shang-Hsun Hsieh, Chi-An Wang, Sou-Chi Chang, and Chien-Chih Lee, Student Member, IEEE

Abstract—On a 1.27-nm gate-oxide nMOSFET, we make a comprehensive study of SiO<sub>2</sub>/Si interface roughness by combining temperature-dependent electron mobility measurement, sophisticated mobility simulation, and high-resolution transmission electron microscopy (TEM) measurement. Mobility measurement and simulation adequately extract the correlation length  $\lambda$  and roughness rms height  $\Delta$  of the sample, taking into account the Coulombdrag-limited mobilities in the literature. The TEM measurement yields the apparent correlation length  $\lambda_m$  and roughness rms height  $\Delta_m$ . It is found that the following hold: 1)  $\lambda \approx \lambda_m$ for both the Gaussian and exponential models, validating the temperature-oriented extraction process; 2) the extracted  $\Delta$ ( $\sim$ 1.3 Å for the Gaussian model and 1.0 Å for the exponential one) is close to that  $(\sim 1.2 \text{ Å})$  of  $\Delta_m$ , all far less than the conventional values ( $\sim$ 3 Å) in thick-gate-oxide case; and 3) the TEM 2-D projection correction coefficient  $\Delta_m/\Delta$  is approximately 1.0, which cannot be elucidated with the current thick-gate-oxide-based knowledge.

Index Terms—Coulomb drag, gate oxide, interface plasmons, mobility, metal-oxide-semiconductor field-effect transistors (MOSFETs), scattering, surface roughness, transmission electron microscopy (TEM), universal mobility.

# I. INTRODUCTION

**R** ANDOM roughness at the  $SiO_2/Si$  interface can critically affect the carrier transport in the inversion layers of MOSFETs. Thus, attempts to characterize the surface roughness parameters are essential. To facilitate the description of the surface roughness picture, two fundamentally distinct models were proposed [1]: Gaussian and exponential. Both models contain two elements, i.e., correlation length  $\lambda$  and roughness rms height  $\Delta$ . To assess the underlying  $\lambda$  and  $\Delta$ , numerical

Manuscript received October 24, 2011; accepted December 29, 2011. Date of publication February 3, 2012; date of current version March 23, 2012. This work was supported by the National Science Council of Taiwan under Contract NSC 98-2221-E-009-164-MY3. The review of this paper was arranged by Editor M. Ieong.

- M.-J. Chen, L.-M. Chang, C.-W. Lee, S.-H. Hsieh, C.-A. Wang, and C.-C. Lee are with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan (e-mail: chenmj@faculty.nctu.edu.tw).

- S.-J. Kuang is with the Taiwan Semiconductor Manufacturing Company, Hsinchu 300, Taiwan.

- S.-C. Chang is with the Department of Electrical and Computer Engineering, Georgia Institute of Technology (Georgia Tech), Atlanta, GA 30332-0250 USA.

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2012.2182771

simulations were applied with the inversion-layer mobility data as inputs [1]–[4]. However, for MOSFETs having ultrathin gate oxides, such a scheme encountered difficulties due to the increasing importance of remote scatterers [5], [6]. Indeed, how to correctly distinguish between the surface roughness and remote scatterers has been a challenging issue [7]. To overcome the issue, we recently proposed a temperature-dependent extraction method [8]. As has been demonstrated [8] on 1.65-nmgate-oxide nMOSFETs through the use of the Gaussian model, the merits of the method are summarized: 1) it can effectively distinguish the surface-roughness-limited mobility from the remote-scatterer-limited mobility; 2) it can accurately determine the surface roughness parameters; and 3) it can easily be conducted in a certain range around room temperature.

Alternatively, TEM measurements can be performed to provide the apparent correlation length  $\lambda_m$  and the apparent rms height  $\Delta_m$ . To address the 2-D projection effect in the TEM measurement, a link to the aforementioned  $\Delta$  was established in terms of correction coefficient  $\Delta_m/\Delta$  [1]. Furthermore, a mathematical transformation from digitized TEM surface roughness data, without directly accounting for  $\lambda$  and  $\Delta$ , to mobility values was developed, thus producing a quantity associated with the projection correction [9]. However, these works [1], [9] were devoted to the thick-gate-oxide samples only.

To make a comprehensive surface roughness study and to advance the studies [1]–[9], in this paper, we integrate the aforementioned means, i.e., temperature-dependent mobility measurement, sophisticated mobility simulation accounting for both the Gaussian and exponential models, and TEM measurement. In addition, a thinner gate-oxide sample (1.27 nm), which enables fair citation of the simulated Coulomb-drag-limited mobilities (on 1-nm gate oxide) [5], is presented. The results are novel and might substantially improve current understanding of the surface roughness, particularly for the case of ultrathin gate oxides.

### II. SAMPLE AND ELECTRICAL CHARACTERIZATION

The device under study was fabricated in a conventional manufacturing process. In this process, SiO<sub>2</sub> film was thermally grown on the (001) surface, followed by NO annealing. Corresponding process parameters can essentially be obtained by

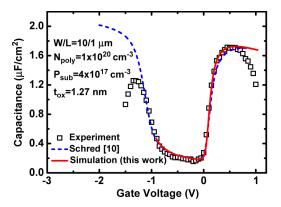

Fig. 1. Comparison of the measured (symbol) and simulated (lines) gate capacitance versus gate voltage. The lines came from the self-consistent Schrödinger and Poisson's equations solvers [10], [11].

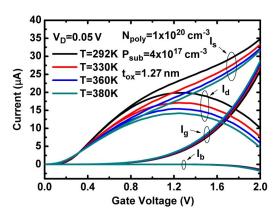

Fig. 2. Measured terminal currents at a drain voltage of  $0.05~\rm V$  versus gate voltage for four different temperatures.

fitting the measured gate capacitance versus the gate voltage  $(C_g - V_g)$ , as shown in Fig. 1. This was realized with the use of a self-consistent Schrödinger and Poisson's equations solver. Two such solvers were cited: one named Schred [10] and the other in the previous work [11]. Obviously, the two sources [10] and [11] are consistent of each other in the data fitting. Although Cg-Cg data at high gate voltages were seriously distorted due to the prepared ultrathin gate oxide, where the direct tunneling current is profoundly large, the fitting was successfully done in the remaining regions, leading to n<sup>+</sup> polysilicon doping concentration =  $1 \times 10^{20}$  cm<sup>-3</sup>, gate oxide (SiO<sub>2</sub>) physical thickness = 1.27 nm, and p-type substrate doping concentration =  $4 \times 10^{17}$  cm<sup>-3</sup>. As will be explained in detail later, the NO annealing used may have an impact on the SiO<sub>2</sub>/Si interface formation but not the SiO<sub>2</sub> bulk one.

The ratio of channel width W to length L of the device is  $1/1~\mu m$ . The channel length direction is along the  $\langle 110 \rangle$  direction. We conducted I-V measurements at four temperatures (292, 330, 360, and 380 K). Measured I-V curves across different positions on wafer were found to be comparable with each other. This ensures the integrity of the presented sample. Fig. 2 shows the measured drain current  $I_d$ , source current  $I_s$ , gate current  $I_g$ , and bulk current  $I_b$  at drain voltage  $V_D = 50~{\rm mV}$ , plotted versus gate voltage with the temperature as a parameter. The effect of the huge gate tunneling current on the source and drain currents is evidently clear. Similar behaviors

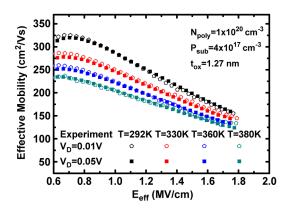

Fig. 3. Measured electron effective mobility at two drain voltages of 0.01 and  $0.05~\rm V$  versus vertical effective field for four temperatures.

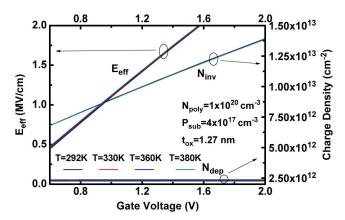

Fig. 4. Simulated vertical effective field, inversion-layer charge density, and substrate depletion charge density versus gate voltage with the temperature as a parameter.

were also observed elsewhere [12]. In this situation, the correct mobility assessment should be formulated as [12]

$$\mu(V_g) = \frac{L}{W} \frac{(I_s(V_g) + I_d(V_g))}{2V_d} \frac{1}{qN_{\text{inv}}(V_q)}.$$

(1)

Resulting temperature-dependent mobilities are given in Fig. 3 and plotted versus vertical effective field  $E_{\rm eff}$ . Here,  $E_{\rm eff}$  followed the well-known expression

$$E_{\text{eff}} = \frac{q(0.5N_{\text{inv}} + N_{\text{dep}})}{\varepsilon_{\text{si}}}$$

(2)

where  $N_{\rm inv}$  is the inversion-layer charge density,  $N_{\rm dep}$  is the substrate depletion charge density, and  $\varepsilon_{\rm si}$  is the silicon permittivity. With the aforementioned process parameters as inputs, the self-consistent Schrödinger and Poisson's equations solver [11] was executed to furnish  $N_{\rm inv}$  and  $N_{\rm dep}$ . Corresponding  $N_{\rm inv}$ ,  $N_{\rm dep}$ , and  $E_{\rm eff}$  are plotted in Fig. 4 versus gate voltage, with the temperature as a parameter. Moreover, we repeated the case of  $V_D=10$  mV and found that the change is little, as shown in Fig. 3. This ensures the quality of the presented mobility data, particularly for their temperature dependencies.

# III. SIMULATION AND EXTRACTION

In the mobility simulation, we employed the self-consistent Schrödinger and Poisson's equations solver [11] to deliver subbands and wavefunctions while computing the total mobility  $\mu_{\rm total}.$  Here,  $\mu_{\rm total}$  was limited to the high- $E_{\rm eff}$  region, where the microscopic scattering by acoustic and optical phonons in the channel region and by the SiO $_2$ /Si surface roughness dominates. Two literature sources were quoted concerning the scattering rate formalisms: one for the phonon scattering rate [2] and the other for both the Gaussian and exponential surface roughness ones [13]. The material parameters used in the phonon scattering rate calculation were the same as in previous work [8]. These two surface roughness scattering rate formalisms are given as follows [13]:

$$\frac{1}{\tau_{\rm SR}^i(E)} = \frac{m_{\rm dos}^i e^2 E_{\rm eff}^2 \Delta^2 \lambda^2}{2\hbar^3} \int_0^{2\pi} \exp\left(-\frac{q^2 \lambda^2}{4}\right) (1 - \cos\theta) d\theta \tag{3}$$

for the Gaussian model and

$$\frac{1}{\tau_{\rm SR}^{i}(E)} = \frac{m_{\rm dos}^{i} e^{2} E_{\rm eff}^{2} \Delta^{2} \lambda^{2}}{2\hbar^{3}} \int_{0}^{2\pi} \frac{1}{[1 + (\lambda^{2} q^{2}/2)]} (1 - \cos \theta) d\theta$$

(4)

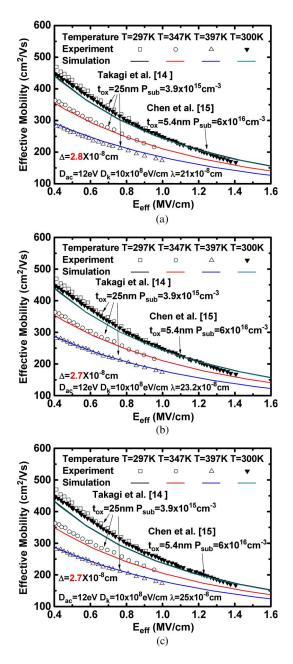

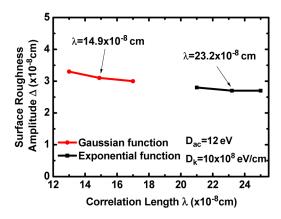

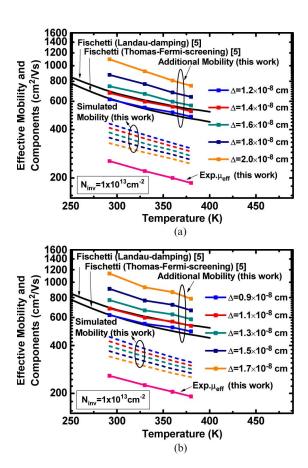

for the exponential model. In (3) and (4),  $\tau_{\rm SR}^i$  is the scattering rate of subband i,  $m_{\rm dos}^i$  is the density-of-states effective mass of subband i,  $\theta$  is the scattering angle, and  $q^2 = 2k^2(1 - \cos \theta)$ , with  $k^2=2m_{\rm dos}^i(E-E_i)/2\hbar^2$ . Simulated total mobility with different  $\Delta$ 's and different  $\lambda$ 's were used to reproduce universal mobility data [14], [15] in a temperature range comparable with the measurement one in this work, as shown in Figs. 5 and 6 for the Gaussian and exponential models, respectively. The best fitting produces the solutions of  $\Delta$  and  $\lambda$ , as shown in Fig. 7 for both models. Other values of  $\Delta$  and  $\lambda$  only led to a poor fitting of the temperature dependencies and had been ruled out. It can be seen from Fig. 7 that  $\Delta$  is considerably constant and is higher for the Gaussian model,  $\lambda$  has a broad range and is smaller in magnitude for the exponential model, and there is no overlap between the two models. Thus, in the subsequently analysis,  $\lambda$ will be fixed at the middle value, i.e., 14.9 and 23.2 Å for the Gaussian and exponential models, respectively. Accordingly, the values of  $\Delta$  are 3.1 and 2.7 Å, respectively, which are close to the published values in the thick-gate-oxide case [1]-[4]. This dictates the applicability of the proposed temperaturedependent extraction process.

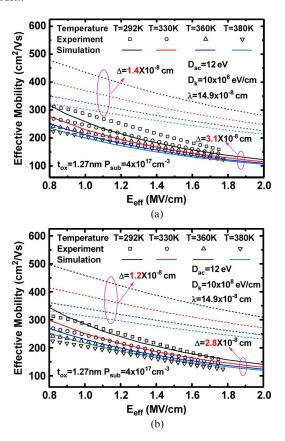

However, we found that, with the aforementioned  $\Delta$  and  $\lambda$  values, simulated results cannot match all observed temperature dependencies of mobilities in a 1.27-nm sample. As shown in Figs. 8 and 9 for both models, simulated mobilities at 292, 330, and 360 K fall below data points, despite the apparent coincidence for the remaining temperature (380 K). Since this is physically unreasonable, the value of  $\Delta$  must be reduced. The case of reducing  $\Delta$  to lower values is depicted in these two figures.

The required reduction in  $\Delta$  indicates the existence of the remote scatterers. In this sense, the additional mobility  $\mu_{\rm add}$  due to the remote scatterers, ionized substrate impurity atoms,

Fig. 5. Comparison of the experimental electron universal mobility curves for (open symbols) three temperatures [14] and (filled symbols) one temperature [15] with the (lines) simulated ones in this work for the Gaussian model. (a)  $\Delta=3.3$  Å, and  $\lambda=13$  Å. (b)  $\Delta=3.1$  Å, and  $\lambda=14.9$  Å. (c)  $\Delta=3.0$  Å, and  $\lambda=17$  Å.  $D_{\rm ac}$  is the acoustic deformation potential.  $D_k$  is the deformation potential of the kth intervalley phonon.

and interface traps can be defined according to Matthiessen's rule, i.e.,

$$\frac{1}{\mu_{\text{eff}}} = \frac{1}{\mu_{\text{total}}} + \frac{1}{\mu_{\text{add}}} \tag{5}$$

where  $\mu_{\rm eff}$  is the measured mobility [i.e., (1)], and  $\mu_{\rm total}$  is the simulated total mobility that does not include the contributions by remote scatterers, substrate impurity atoms, or interface traps. Note that Matthiessen's rule can empirically apply as long as the undertaken  $E_{\rm eff}$  or  $N_{\rm inv}$  is high enough [16]. The effect of substrate impurity atoms or interface traps

Fig. 6. Comparison of the experimental electron universal mobility curves for (open symbols) three temperatures [14] and (filled symbols) one temperature [15] with the (lines) simulated ones for the exponential model. (a)  $\Delta=2.8$  Å, and  $\lambda=21$  Å. (b)  $\Delta=2.7$  Å, and  $\lambda=23.2$  Å. (c)  $\Delta=2.7$  Å, and  $\lambda=25$  Å.

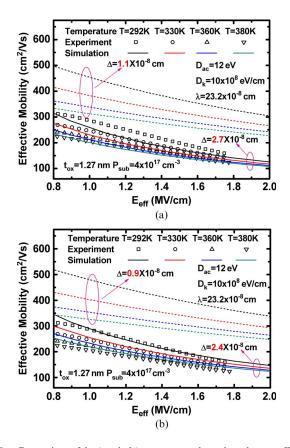

can also be suppressed in the high- $E_{\rm eff}$  region. In Fig. 10, we show the extracted  $\mu_{\rm add}$  at  $N_{\rm inv}$  of  $1\times 10^{13}$  cm $^{-2}$ , with  $\Delta$  as a parameter, along with the two separate curves for the simulated Coulomb-drag-limited mobilities [5]. These two Coulomb-drag-limited mobility curves represent two limiting conditions of the Landau-damping wave vector: one for "zero-temperature Landau damping wave vector" and the other for "damping at Thomas Fermi screening wave vector" [5]. According to Fischetti [5], the realistic Coulomb-drag-limited mobility is likely to be situated between the two limits. In this sense, the actual  $\Delta$  of the presented sample should be approximately 1.3 and 1.0 Å for the Gaussian and exponential models, respectively.

Fig. 7. Best-fitting results of  $\Delta$  versus  $\lambda$  for both the Gaussian and exponential models.

Fig. 8. Comparison of the (symbols) temperature-dependent electron effective mobility data with the simulated mobility curves using the Gaussian model for (a)  $\Delta$  of (dashed line) 1.4 Å and (solid line) 3.1 Å, and (b)  $\Delta$  of (dashed line) 1.2 Å and (solid line) 2.8 Å.  $\lambda$  = 14.9 Å.

# IV. TEM MEASUREMENT AND ANALYSIS

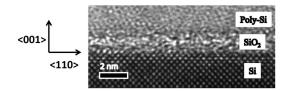

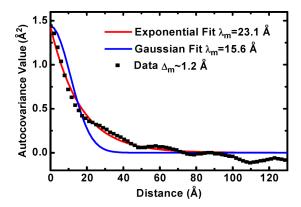

In performing TEM measurements, the sample was 1000 nm long, and its cross-section thickness had a range of 20–60 nm. A TEM image was created, as shown in Fig. 11. In this picture, the labeled  $\langle 110 \rangle$  direction is parallel to the SiO<sub>2</sub>/Si interface, whereas the  $\langle 001 \rangle$  direction is normal to the interface. Underlying  $\lambda_m$  and  $\Delta_m$  were determined by following the work of Goodnick *et al.* [1]. First, digitalization of surface roughness was done by directly counting lattice points on the TEM photographs. The same sampling interval (1.92 Å) [1] was used. This led to the autocovariance function

Fig. 9. Comparison of the (symbols) temperature-dependent electron effective mobility data with the simulated mobility curves using the exponential model for (a)  $\Delta$  of (dashed line) 1.1 Å and (solid line) 2.7 Å and (b)  $\Delta$  of (dashed line) 0.9 Å and (solid line) 2.4 Å.  $\lambda=23.2$  Å.

in Fig. 12 as a function of the distance. In the figure, the squared root of the autocovariance at zero distance yields  $\Delta_m$  of around 1.2 Å. Data fitting was carried out, producing  $\lambda_m=15.6$  and 23.1 Å for the Gaussian and exponential models, respectively.

Straightforwardly, several key arguments can be drawn. First, the sample length effect [1] may be neglected due to a long sample used. Thus, the ratio of  $\lambda_m/\lambda \approx 1.0$  is reached accordingly [1]. Strikingly, this is the fact because the extracted values of  $\lambda_m = 15.6$  and 23.1 Å in this work separately are close to those (14.9 and 23.2 Å) of  $\lambda$ . One of the arguments can thereby be inferred: the sample length effect as cited in [1] can act to be corroborating evidence for the temperature-dependent extraction method. Second, the TEM 2-D projection correction coefficient  $\Delta_m/\Delta$  is approximately 1.0, valid for both the Gaussian and exponential models. However, the current thickgate-oxide-based knowledge [1] cannot reasonably explain this because, for the TEM sample cross-section thickness range of 20-60 nm as in our work, the theoretical calculation pointed out [1] that the upper limit of  $\Delta_m/\Delta$  decreases sharply from 0.7 (see [1]). Even the  $\Delta_m/\Delta$  in this work is much higher than the published experimental  $\Delta_m/\Delta$  values of 0.50–0.71 [8]. We attribute such significant deviations to the sole use of the ultrathin gate oxide (1.27 nm) in this work. It is therefore suggested that further theoretical investigation of the TEM sample cross-section thickness effect is needed, particularly for the ultrathin-gate-oxide situation.

Fig. 10. Temperature dependence of the measured effective mobility, simulated mobility, and extracted additional mobility, all made at a fixed inversion-layer density of  $1\times 10^{13}~\text{cm}^{-2}$  to make a fair comparison with simulated interface-plasmons-limited mobility [5]. Simulated mobility and additional mobility are presented as a function of  $\Delta.$  (a) Gaussian model. (b) exponential model.

Fig. 11. TEM image of the sample.

Finally, we want to stress that the physical gate oxide thickness can be estimated from the TEM picture in Fig. 11, and it appears to be in proximity of 1.27 nm, which is the value of Cg-Vg fitting. The same gate oxide thickness had earlier been applied to p-type counterparts on the same wafer [17]. This strongly suggests that the presented SiO<sub>2</sub> bulk film was less nitrided during the NO annealing. Moreover, according to the literature [4], the use of the oxide nitridation process will produce a smoother Si/SiO<sub>2</sub> interface in terms of a reduced  $\Delta$ . Extra traps may be created during the pure nitridation or mixed one (i.e., NO annealing process); however, their effect might be limited to the low- $E_{\rm eff}$  region, rather than the high- $E_{\rm eff}$  region where this work was focused on. Therefore, it is argued that the mixed NO annealing used may have an impact on the SiO<sub>2</sub>/Si interface formation but not the SiO<sub>2</sub> bulk one.

Fig. 12. Autocovariance function extracted from the TEM photograph as a function of distance. Both the Gaussian and exponential fits are shown.

## V. Conclusion

Electron mobility of a 1.27-nm gate-oxide nMOSFET sample has been measured at various temperatures. Temperature-dependent numerical simulation has for the first time transformed existing universal mobility data into the solutions of surface roughness parameters and has been applied to the presented sample, taking into account the available Coulomb-drag-limited mobilities. The extracted surface roughness parameters have been correlated with the values from TEM measurements. As a consequence, novel results have been created and might substantially improve the current understanding of interface roughness, particularly for the case of ultrathin gate oxides.

### REFERENCES

- [1] S. M. Goodnick, D. K. Ferry, C. W. Wilmsen, Z. Liliental, D. Fathy, and O. L. Krivanek, "Surface roughness at the Si(100) — SiO<sub>2</sub> interface," *Phys. Rev. B, Condens. Matter Mater. Phys.*, vol. 32, no. 12, pp. 8171– 8186, Dec. 1985.

- [2] S. Takagi, J. L. Hoyt, J. J. Welser, and J. F. Gibbons, "Comparative study of phonon-limited mobility of two-dimensional electrons in strained and unstrained Si metal-oxide-semiconductor field-effect transistors," *J. Appl. Phys.*, vol. 80, no. 3, pp. 1567–1577, Aug. 1996.

- [3] G. Mazzoni, A. L. Lacaita, L. M. Perron, and A. Pirovano, "On surface roughness-limited mobility in highly doped n-MOSFETs," *IEEE Trans. Electron Devices*, vol. 46, no. 7, pp. 1423–1428, Jul. 1999.

- [4] A. Pirovano, A. L. Lacaita, G. Ghidini, and G. Tallarida, "On the correlation between surface roughness and inversion layer mobility in Si-MOSFETs," *IEEE Electron Device Lett.*, vol. 21, no. 1, pp. 34–36, Jan. 2000.

- [5] M. V. Fischetti, "Long-range Coulomb interactions in small Si devices. Part II: Effective electron mobility in thin-oxide structures," J. Appl. Phys., vol. 89, no. 2, pp. 1232–1250, Jan. 2001.

- [6] F. Gámiz and M. V. Fischetti, "Remote Coulomb scattering in metal-oxide-semiconductor field effect transistors: Screening by electrons in the gate," *Appl. Phys. Lett.*, vol. 83, no. 23, pp. 4848–4850, Dec. 2003.

- [7] M. V. Fischetti, T. P. ORegan, S. Narayanan, C. Sachs, S. Jin, J. Kim, and Y. Zhang, "Theoretical study of some physical aspects of electronic transport in nMOSFETs at the 10-nm gate-length," *IEEE Trans. Electron Devices*, vol. 54, no. 9, pp. 2116–2136, Sep. 2007.

- [8] M. J. Chen, S. C. Chang, S. J. Kuang, C. C. Lee, W. H. Lee, K. H. Cheng, and Y. H. Zhan, "Temperature-dependent remote-Coulomb-limited electron mobility in n+-polysilicon ultrathin gate oxide nMOSFETs," *IEEE Trans. Electron Devices*, vol. 58, no. 4, pp. 1038–1044, Apr. 2011.

- [9] Y. Zhao, H. Matsumoto, T. Sato, S. Koyama, M. Takenaka, and S. Takagi, "Comprehensive understanding of surface roughness limited mobility in unstrained- and strained-Si MOSFETs by novel characterization scheme of Si/SiO<sub>2</sub> interface roughness," in VLSI Symp. Tech. Dig., 2009, pp. 18–19.

- [10] Schred. [Online]. Available: http://nanohub.org/resources/schred

- [11] M. J. Chen, C. C. Lee, and K. H. Cheng, "Hole effective masses as a booster of self-consistent six-band  $k \cdot p$  simulation in inversion layers of pMOSFETs," *IEEE Trans. Electron Devices*, vol. 58, no. 4, pp. 931–937, Apr. 2011.

- [12] S. Takagi and M. Takayanagi, "Experimental evidence of inversion-layer mobility lowering in ultrathin gate oxide metal-oxide-semiconductor field-effect-transistors with direct tunneling current," *Jpn. J. Appl. Phys.*, vol. 41, no. 4B, pp. 2348–2352, Apr. 2002, pt. 1.

- [13] S. Yamakawa, H. Ueno, K. Taniguchi, C. Hamaguchi, K. Miyatsuji, K. Masaki, and U. Ravaioli, "Study of interface roughness dependence of electron mobility in Si inversion layers using the Monte Carlo method," *J. Appl. Phys.*, vol. 79, no. 2, pp. 911–916, Jan. 1996.

- [14] S. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the universality of inversion layer mobility in Si MOSFETs: Part I—Effects of substrate impurity concentration," *IEEE Trans. Electron Devices*, vol. 41, no. 12, pp. 2357–2362, Dec. 1994.

- [15] K. Chen, C. Hu, P. Fang, M. R. Lin, and D. L. Wollensen, "Predicting CMOS speed with gate oxide and voltage scaling and interconnect loading effects," *IEEE Trans. Electron Devices*, vol. 44, no. 11, pp. 1951–1957, Nov. 1997

- [16] F. Stern, "Calculated temperature dependence of mobility in Si inversion layers," *Phys. Rev. Lett.*, vol. 44, no. 22, pp. 1469–1472, Jun. 1980.

- [17] C. Y. Hsu, C. C. Lee, Y. T. Lin, C. Y. Hsieh, and M. J. Chen, "Enhanced hole gate direct tunneling current in process-induced uniaxial compressive stress p-MOSFETs," *IEEE Trans. Electron Devices*, vol. 56, no. 8, pp. 1667–1673, Aug. 2009.

Ming-Jer Chen (S'78–M'79–SM'98) received the B.S. degree in electrical engineering (with highest honors) from National Cheng Kung University, Tainan, Taiwan, in 1977 and the M.S. and Ph.D. degrees in electronics engineering from National Chiao Tung University (NCTU), Hsinchu, Taiwan, in 1979 and 1985, respectively.

In 1985, he was with the Department of Electronics Engineering, NCTU and, in 1993, became a Full Professor. From 1987 to 1992, he was a Consultant with Taiwan Semiconductor Manufacturing

Company (TSMC), where he led a team from NCTU and the Electronics Research and Service Organization/Industrial Technology Research Institute to build up a series of process windows and design rules. From 2000 to 2001, he was a Visiting Professor with the Department of Electrical Engineering and the Center for Integrated Systems, Stanford University, Stanford, CA. He is the holder of eight U.S. patents and six Taiwanese patents in the field of the high-precision analog capacitors, 1-T memory cell, dynamic threshold MOS, electrostatic discharge protection, and Flash memory. He has graduated 17 Ph.D. students and more than 100 M.S. students. His current research interests include device physics, trap physics, and reliability physics, all in the area of nanoelectronics.

Dr. Chen is a member of the Phi Tau Phi.

Li-Ming Chang was born in Taipei, Taiwan, in 1981. He received the B.S. degree in electronics engineering, in 2003, from National Chiao Tung University, Hsinchu, Taiwan, where he is currently working toward the Ph.D. degree in the Department of Electronics Engineering and Institute of Electronics.

His current research interests include carrier transport phenomena and characterization of nanoscale devices.

Shin-Jiun Kuang received the B.S. degree in electrical engineering from National Chung Hsing University, Taichung, Taiwan, in 2009 and the M.S. degree in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2011.

She is currently with Taiwan Semiconductor Manufacturing Company, Hsinchu. Her research interests include characterization and modeling of nanoscale devices.

Chi-An Wang received the B.S. degree in electronic engineering from National Kaohsiung Normal University, Kaohsiung, Taiwan, in 2011. He is currently working toward the M.S. degree in electronics engineering in the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan.

Chih-Wei Lee was born in Taipei, Taiwan, in 1988. He received the B.S. degree in engineering and system science from National Tsing Hua University, Hsinchu, Taiwan, in 2010. He is currently working toward the M.S. degree in electronics engineering in the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan.

His research interests include characterization and modeling of nanoscale devices.

Sou-Chi Chang received the B.S. degree in electrical engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2008 and the M.S. degree in electrical engineering and computer science from the University of Michigan, Ann Arbor, in 2011. He is currently working toward the Ph.D. degree in electrical and computer engineering in the Department of Electrical and Computer Engineering, Georgia Institute of Technology (Georgia Tech), Atlanta.

Shang-Hsun Hsieh received the B.S. degree in physics from National Changhua University of Education, Changhua, Taiwan, in 2010. He is currently working toward the M.S. degree in electronics engineering in the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan.

nanoscale devices.

Chien-Chih Lee (S'07) was born in Taipei, Taiwan, in 1981. He received the B.S. degree in physics from National Chung Hsing University, Taichung, Taiwan, in 2004. He is currently working toward the Ph.D. degree in electronics engineering in the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan.

His research interests include characterization and modeling of strained devices, development of quantum simulators, and study of trap physics in