Home Search Collections Journals About Contact us My IOPscience

Investigation of Hot-Carrier Stress Effect on High-Frequency Performance of Laterally Diffused Metal–Oxide–Semiconductor Transistors

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2012 Jpn. J. Appl. Phys. 51 02BC12

(http://iopscience.iop.org/1347-4065/51/2S/02BC12)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 28/04/2014 at 21:48

Please note that terms and conditions apply.

# Investigation of Hot-Carrier Stress Effect on High-Frequency Performance of Laterally Diffused Metal-Oxide-Semiconductor Transistors

Kun-Ming Chen<sup>1\*</sup>, Zong-Wen Mou<sup>2</sup>, Hao-Chung Kuo<sup>2</sup>, Chia-Sung Chiu<sup>1</sup>, Bo-Yuan Chen<sup>1</sup>, Wen-De Liu<sup>1</sup>, Ming-Yi Chen<sup>3</sup>, Yu-Chi Yang<sup>3</sup>, Kai-Li Wang<sup>3</sup>, and Guo-Wei Huang<sup>1,4</sup>

Received September 16, 2011; accepted November 1, 2011; published online February 20, 2012

The hot-carrier stress effects on the high-frequency performance characteristics of laterally diffused metal–oxide–semiconductor (LDMOS) transistors were investigated. A constant bias channel hot-carrier stress was applied at room temperature. After applying 3 h of hot-carrier stress, the on-resistance and saturation drain current degradations are 18 and 9%, respectively. However, the degradations of the cutoff frequency and maximum oscillation frequency were less than 2% when the devices were biased before the onset of quasi-saturation. In addition, we found that the degradations of high-frequency parameters are not related to the change in transconductance but to the changes in gate capacitances. Finally, S-parameter variations under hot-carrier stress were also examined in this study. The observations of S-parameter variations are important for RF power amplifier design. © 2012 The Japan Society of Applied Physics

#### 1. Introduction

The rapid growth of wireless communication product markets has created a huge demand for low-cost, highefficiency, and good-linearity RF power amplifiers. Among power devices, laterally diffused metal-oxide-semiconductor (LDMOS) transistors are the most attractive in cost and potential for improvements in performance and integration. LDMOS transistors have been widely used in RF power amplifier modules for a high frequency range up to 3.8 GHz. 1-3) Because the LDMOS used in power amplifiers is operated at a high drain voltage while carrying a high current, it could be vulnerable to hot carrier injection and trapping. Therefore, hot-carrier instability is one of the major reliability issues in an LDMOS and has widely attracted attention in recent years.<sup>4–7)</sup> Owing to the existence of a drift region, the mechanisms of hot-carrier-induced degradation in LDMOS transistors differ substantially from that in standard complementary metal-oxide-semiconductor (CMOS) transistors. The degradation mechanism depends on the device structure and stress condition. Generally, the hot-carrier degradation is associated with the effects of hot hole/electron injection in the channel region and/or the drift region of LDMOS transistors.

For RF power circuit design, it is important to evaluate the hot-carrier stress effects on the high-frequency characteristics of power transistors to predict stress-induced circuit performance drifts. Although the hot-carrier reliability of LDMOS transistors has been investigated in many studies, there are only a few reports that address the hot-carrier stress effects on RF behaviors, 8-10) particularly on the degradation of S-parameters and the RF figures of merit, such as cutoff frequency  $(f_T)$  and maximum oscillation frequency  $(f_{max})$ . Previously, hot-carrier-induced  $f_T$  or S-parameter degradations were shown only to verify the reliability improvement of a new device structure<sup>8,9)</sup> or compare the measurement results of different aging test methods. 10) However, the mechanisms of high-frequency parameter degradations were not discussed in detail. In this paper, we present the experimental results of the high-frequency characteristics of

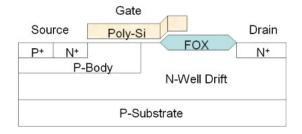

Fig. 1. (Color online) Schematic cross section of an LDMOS transistor.

LDMOS transistors under hot-carrier stress. It was observed that  $f_{\rm T}$  decreases and  $f_{\rm max}$  remains almost unchanged after applying stress under the bias conditions of RF-power-amplifying applications. The degradation mechanisms of the high-frequency parameters are discussed in detail by analyzing the changes in gate capacitances. Finally, S-parameter variations under hot-carrier stress are also shown in this paper.

## 2. Experiments

The n-channel LDMOS transistors used in this study were fabricated by a  $0.5\,\mu m$  CMOS-DMOS process with a gate oxide thickness of  $135\,\text{Å}.^{11)}$  The off-state breakdown voltage is about 41 V. As illustrated in Fig. 1, the devices have a lightly doped N-well drift region under the field oxide (FOX). The effective channel length and drift length are 1.1 and  $2\,\mu m$ , respectively. The source and p-body contacts are tied together to eliminate extra surface bond wires to reduce the source inductance and improve the RF performance in a power amplifier configuration. To monitor the body current, devices with separate source and p-body contacts were also fabricated. The devices under test have a multifinger gate configuration featuring eight fingers with a total width of  $80\,\mu m$ .

A constant bias hot-carrier stress was applied with a gate voltage of 2.5 V and a drain voltage of 28 V at room temperature. The applied gate voltage corresponds to the maximum body current. The stress tests were interrupted periodically to measure the degradation of device electrical parameters. The S-parameters were measured on chip using

<sup>&</sup>lt;sup>1</sup>National Nano Device Laboratories, Hsinchu 300, Taiwan

<sup>&</sup>lt;sup>2</sup>Department of Photonics, National Chiao Tung University, Hsinchu 300, Taiwan

<sup>&</sup>lt;sup>3</sup>United Microelectronics Corporation, Hsinchiu 300, Taiwan

<sup>&</sup>lt;sup>4</sup>Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan

<sup>\*</sup>E-mail address: kmchen@ndl.narl.org.tw

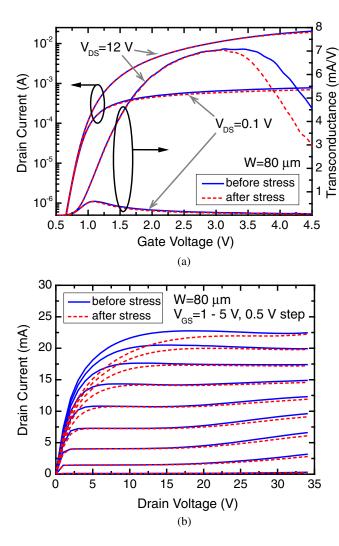

**Fig. 2.** (Color online) (a)  $I_{\rm D}-V_{\rm GS}$  and (b)  $I_{\rm D}-V_{\rm DS}$  characteristics of an LDMOS measured before and after applying 3 h of hot-carrier stress.

an Agilent 8510 network analyzer from 100 MHz to 15 GHz. After de-embedding the parasitic pad effects, the ac current gain  $(H_{21})$  and unilateral power gain (U) were calculated to extract  $f_{\rm T}$  and  $f_{\rm max}$ , respectively.

#### 3. Results and Discussion

#### 3.1 DC characteristics

Figure 2 shows the effects of hot-carrier stress on the dc characteristics of an LDMOS. In Fig. 2(a), the threshold voltage is found to exhibit no degradation after applying stress (<0.5 mV), which means that there is no damage on the source side of the channel. When the device operates in the linear region (drain voltage  $V_{\rm DS}=0.1\,\rm V$ ), the maximum value of linear transconductance  $(g_{m,lin})$  shows an approximately 3% degradation, probably owing to the interface trap generation near the drain side of the channel. When the device operates in the saturation region ( $V_{DS} = 12 \text{ V}$ ), the drain current  $(I_D)$  and transconductance  $(g_m)$  degradations are not observed (<0.2%) before the quasi-saturation effect occurs ( $V_{\rm GS}$  < 3 V). In this bias range, the drain current is dominated by the channel current. In addition, the pinch-off region on the drain side of the channel is created; thus, the generated interface traps in the channel would only slightly affect the carrier mobility. At high gate voltages, the device operation enters the quasi-saturation region, and  $I_D$  and  $g_m$

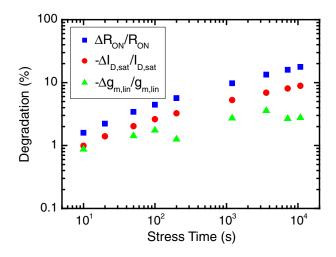

**Fig. 3.** (Color online) Degradations of  $R_{\rm ON}$ ,  $I_{\rm D,sat}$ , and  $g_{\rm m,lin}$  with hot-carrier stress time.  $R_{\rm ON}$  and  $I_{\rm D,sat}$  are extracted at  $V_{\rm DS}=0.5$  and 12 V, respectively, under  $V_{\rm GS}=5$  V.  $g_{\rm m,lin}$  is the maximum transconductance at  $V_{\rm DS}=0.1$  V.

decrease significantly after applying stress. In this operation region, N-well drift resistivity has a large impact on the device characteristics. During hot-carrier stress, the generated interface traps in the drift region may capture the electrons and thus increase the surface scattering, leading to the reduction in carrier mobility.<sup>4-6)</sup>

The severe hot-carrier-induced current degradation in the quasi-saturation region can also be observed in the device output characteristics, as depicted in Fig. 2(b). At high drain voltages,  $I_D$  degradation decreases as the current is pushed deeper in the silicon; hence, the trap-induced surface scattering also decreases. From Fig. 2(b), we extracted the on resistance  $(R_{ON})$  and saturation drain current  $(I_{D,sat})$  at  $V_{\rm DS} = 0.5$  and 12 V, respectively, under the gate voltage condition  $V_{\rm GS}=5$  V. We found that  $R_{\rm ON}$  increases and  $I_{\rm D,sat}$ decreases upon applying hot-carrier stress. As shown in Fig. 3, the degradations of  $R_{ON}$  and  $I_{D,sat}$  are about 18 and 9%, respectively, after applying 3 h of stress; they are higher than the degradation of  $g_{m,lin}$ , suggesting that the stressinduced damage in the drift region is more serious than that in the channel region. In addition, the slopes of the  $R_{\rm ON}$  and  $I_{D,\text{sat}}$  curves in Fig. 3 are in the 0.3–0.4 range, which is close to that reported in ref. 4. Moens et al. pointed out that the hot-carrier-induced interface traps in the drift region are produced at the source-side bird's beak of the FOX when the stress condition corresponds to the maximum body current.<sup>4)</sup> Since the hot carriers affect the dc characteristics of an LDMOS transistor, they may also result in the degradation of high-frequency performance.

## 3.2 $f_T$ and $f_{max}$

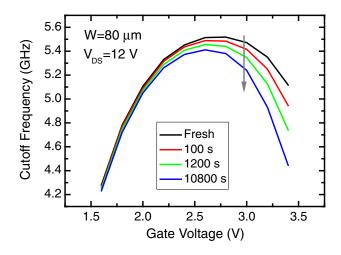

The gate voltage dependence of  $f_{\rm T}$  under hot-carrier stress is shown in Fig. 4. The degradation of the maximum value of  $f_{\rm T}$  is  $\sim 1.9\%$  after applying 3 h of stress. This degradation is much lower than those of  $R_{\rm ON}$  and  $I_{\rm D,sat}$ , owing to the different measurement biases. This result indicates that hot-carrier instability would be less serious when the LDMOS is used in RF power amplifiers than when the LDMOS is used in power switching circuits. In addition, we found that although  $g_{\rm m}$  is unchanged by the stress at the peak  $f_{\rm T}$  [see

**Fig. 4.** (Color online) Measured cutoff frequency as a function of gate voltage for LDMOS under hot-carrier stress.

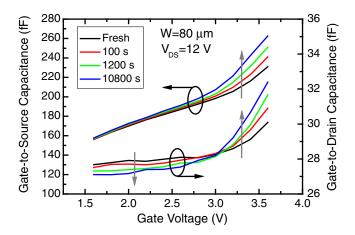

**Fig. 5.** (Color online) Extracted gate capacitances as a function of gate voltage for LDMOS under hot-carrier stress.

Fig. 2(a)],  $f_T$  still exhibits a small degradation. This observation is different from that in metal–oxide–semiconductor field-effect transistors (MOSFETs), where  $g_m$  plays an important role in  $f_T$  degradation. The cutoff frequency can be expressed as a function of  $g_m$  and gate capacitances, that is,

$$f_{\rm T} = \frac{g_{\rm m}}{2\pi (C_{\rm gs} + C_{\rm gd})},$$

(1)

where  $C_{\rm gs}$  is the gate-to-source capacitance and  $C_{\rm gd}$  is the gate-to-drain capacitance. Because  $g_{\rm m}$  is unchanged by the stress, the degradation of  $f_{\rm T}$  may be attributed to the changes in gate capacitances.

The changes in  $C_{\rm gs}$  and  $C_{\rm gd}$  under hot-carrier stress are shown in Fig. 5. The values of the gate capacitances are extracted from the Y-parameters at low frequencies. Before quasi-saturation ( $V_{\rm GS} < 3$  V),  $C_{\rm gs}$  increases with increasing stress time, whereas  $C_{\rm gd}$  decreases. The increase in  $C_{\rm gs}$  under hot-carrier stress was also observed in MOSFET devices, <sup>14)</sup> and this phenomenon can be explained by the change in channel surface potential owing to the negative trap charges appearing near the drain side of the channel. However, in MOSFETs,  $C_{\rm gd}$  was nearly unchanged under hot-carrier stress as the device was operated in the saturation

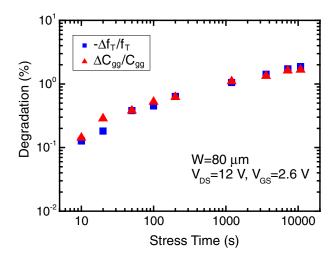

**Fig. 6.** (Color online) Degradations of cutoff frequency and total gate capacitance under hot-carrier stress.

region. <sup>13,14</sup>) The different results between MOSFETs and our device are due to the existence of a drift region. In LDMOS transistors, a large part of  $C_{\rm gd}$  comes from the drift region. The stress-induced negative interface charges in the drift region lead to positive mirror charges in the silicon, thus reducing the effective top N-well concentration. As such, the depletion layer width in the drift region increases and thus  $C_{\rm gd}$  decreases. By plotting the degradations of cutoff frequency and total gate capacitance ( $C_{\rm gg} = C_{\rm gs} + C_{\rm gd}$ ) as functions of stress time (see Fig. 6), we found that the changes in  $f_{\rm T}$  and  $C_{\rm gg}$  are similar. This result confirms that the  $f_{\rm T}$  degradation is dominated by the change in gate capacitance.

When the gate voltage increases and reaches the quasisaturation region, both the transconductance and gate capacitance markedly change [see Figs. 2(a) and 5] owing to the increased drain resistance after stress. As a result,  $f_{\rm T}$  exhibits a large stress-induced degradation at high gate voltages. It was also noted that both  $C_{\rm gs}$  and  $C_{\rm gd}$  increase with stress time in this bias range. In LDMOS transistors, because the inversion charges may be injected from the intrinsic MOSFET to the depleted area of the drift region,  $C_{\rm gs}$  and  $C_{\rm gd}$  increase with increasing gate voltage, and  $C_{\rm gs}$  even increases over the limit of inversion. The increase in gate capacitance with gate voltage may become more apparent as the drain resistance increases. Therefore, the increases in  $C_{\rm gs}$  and  $C_{\rm gd}$  under stress might be mainly attributed to the increased drain resistance.

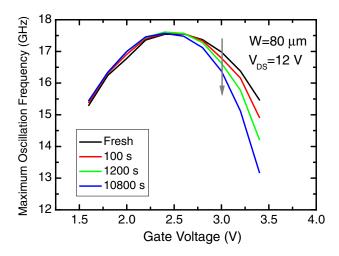

Figure 7 shows the degradation of maximum oscillation frequency under hot-carrier stress. The maximum value of  $f_{\rm max}$  is nearly unchanged with stress time (<0.5%).  $f_{\rm max}$  can be expressed as  $^{16}$ )

$$f_{\rm max} \cong \sqrt{\frac{f_{\rm T}}{8\pi R_{\rm g} C_{\rm gd}}},$$

(2)

where  $R_{\rm g}$  is the gate resistance. Because the gate resistance is not affected by the hot carriers, we only consider the effects of  $f_{\rm T}$  and  $C_{\rm gd}$  on  $f_{\rm max}$ , and the  $f_{\rm max}$  degradation  $(\Delta f_{\rm max}/f_{\rm max})$  is now written as

$$\frac{\Delta f_{\text{max}}}{f_{\text{max}}} \cong \frac{1}{2} \left( \frac{\Delta f_{\text{T}}}{f_{\text{T}}} \right) - \frac{1}{2} \left( \frac{\Delta C_{\text{gd}}}{C_{\text{gd}}} \right). \tag{3}$$

**Fig. 7.** (Color online) Measured maximum oscillation frequency as a function of gate voltage for LDMOS under hot-carrier stress.

After 3 h of stress, the degradations of  $f_{\rm T}$  and  $C_{\rm gd}$  are 1.9 and 2.0%, respectively, at  $V_{\rm GS}=2.6\,{\rm V}$  and  $V_{\rm DS}=12\,{\rm V}$ . Owing to the similar degradations of  $f_{\rm T}$  and  $C_{\rm gd}$ ,  $f_{\rm max}$  would not be changed by the hot carriers. At high gate voltages, large  $f_{\rm max}$  degradations are observed owing to the obvious  $f_{\rm T}$  reduction and  $C_{\rm gd}$  enhancement.

#### 3.3 S-parameters

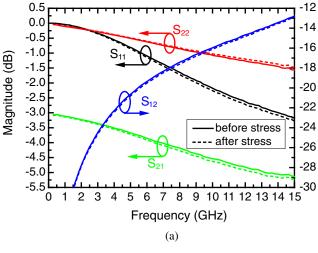

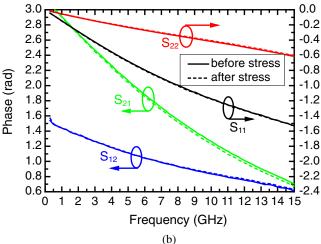

Figure 8 shows the S-parameters measured before and after hot-carrier stress versus frequency. The transistor was measured at  $V_{\rm GS} = 2.6 \, \rm V$  and  $V_{\rm DS} = 12 \, \rm V$  for the maximum value of  $f_T$ . Although all S-parameters are affected by the hot carriers, their degradations (1.1-1.3% at 15 GHz) are not as significant as those of  $R_{\rm ON}$  and  $I_{\rm D,sat}$ . As shown in Fig. 8, the stress-induced deviations of the four S-parameters are similar and increase with increasing frequency. These findings differ from the results for MOSFET devices. 17,18) In the case of MOSFETs,  $S_{21}$  and  $S_{22}$  change more than  $S_{11}$ and  $S_{12}$  after applying stress. Moreover, the stress-induced deviations of  $S_{21}$  and  $S_{22}$  decrease with increasing frequency. This is because the changes in S-parameters are mainly attributed to the changes in the tranconductance and channel conductance of MOSFETs. In our devices, the degradations of S-parameters are due to the changes in  $C_{\rm gs}$ and  $C_{\rm gd}$ .

The observations in hot-carrier-induced S-parameter degradations are very important for power amplifier design. In Fig. 8(a), the reduction in  $S_{12}$  implies that the isolation of transistors is improved. Therefore, the degradation of  $f_{\text{max}}$  is less than that discussed previously. It is worthwhile to pay attention to the measured results of  $S_{21}$  and  $S_{22}$ . At low frequencies,  $S_{21}$  and  $S_{22}$  are almost unchanged. This suggests that the tranconductance and channel conductance are not affected by the stress, which is consistent with the measured dc characteristics. As the frequency increases,  $S_{21}$  and thus the voltage gain decrease gradually. Moreover, the increase in  $S_{22}$  is observed at high frequencies; this is due to not only the reduction in  $C_{gd}$  but also the increase in drain resistance. Since  $S_{11}$  and  $S_{22}$  change after applying stress, we know that the hot carriers also affect the input and output reflection coefficients of the transistors.

**Fig. 8.** (Color online) (a) Magnitudes and (b) phases of *S*-parameters before and after applying 3 h of hot-carrier stress. The measurement conditions were  $V_{\rm GS}=2.6\,{\rm V}$  and  $V_{\rm DS}=12\,{\rm V}$ .

## 4. Conclusions

In this work, we investigated the hot-carrier stress effects on the high-frequency performance characteristics of LDMOS transistors. After applying stress, the cutoff frequency decreases, while the maximum oscillation frequency remains almost the same when the device operates before the quasisaturation effect occurs. This observation can be explained by the changes in  $C_{\rm gs}$  and  $C_{\rm gd}$  owing to the generated trap charges in the channel and drift regions, respectively. In addition, we also examined S-parameter variations under hot-carrier stress. Our experimental results showed that the hot carriers affect the voltage gain as well as the input and output reflection coefficients of the LDMOS transistors. However, these degradations are less than those of onresistance and saturation drain current, indicating that the hot-carrier effect is less serious when the devices are used in RF power amplifying applications.

#### **Acknowledgements**

The authors would like to thank the staff members of United Microelectronics Corporation for their helpful comments. This work was supported in part by the National Science Council of R.O.C. through contracts NSC99-2221-E-492-027-MY2.

- 1) A. Wood, C. Dragon, and W. Burger: IEDM Tech. Dig., 1996, p. 87.

- G. Ma, Q. Chen, O. Tornblad, T. Wei, C. Ahrens, and R. Gerlach: IEDM Tech. Dig., 2005, p. 361.

- 3) F. van Rijs: IEEE Radio and Wireless Symp., 2008, p. 69.

- P. Moens, G. V. D. Bosch, C. D. Keukeleire, R. Degraeve, M. Tack, and G. Groeseneken: IEEE Trans. Electron Devices 51 (2004) 1704.

- N. Hefyene, C. Anghel, R. Gillon, and A. M. Ionescu: Proc. Int. Reliability Physics Symp. (IRPS), 2005, p. 551.

- P. Moens, J. Mertens, F. Bauwens, P. Joris, W. De Ceuninck, and M. Tack: Proc. Int. Reliability Physics Symp. (IRPS), 2007, p. 492.

- 7) J. S. Yuan and L. Jiang: IEEE Trans. Electron Devices 55 (2008) 1519.

- N. R. Mohapatra, K. E. Ehwald, R. Barth, H. Rucker, D. Bolze, P. Schley, D. Schmidt, and H. E. Wulf: Proc. European Solid-State Device Research Conf. (ESSDERC), 2005, p. 481.

- A. Mai, H. Rucker, and R. Sorge: Proc. Int. Symp. Power Semiconductor Devices and ICs, 2009, p. 100.

- 10) M. A. Belaid and K. Ketata: Proc. Int. Workshop Thermal Investigations of

- ICs and Systems (THERMINIC), 2008, p. 123.

- H. H. Hu, K. M. Chen, G. W. Huang, C. Y. Chang, Y. C. Lu, Y. C. Yang, and E. Chen: Jpn. J. Appl. Phys. 46 (2007) 2032.

- 12) F. M. Rotella, G. Ma, Z. Yu, and R. W. Dutton: IEEE Trans. Microwave Theory Tech. 48 (2000) 991.

- S. Y. Huang, K. M. Chen, G. W. Huang, D. Y. Yang, and C. Y. Chang: Top. Meet. Silicon Monolithic Integrated Circuits in RF Systems, 2006, p. 81.

- 14) Y. T. Yew, C. H. Ling, and L. K. Ah: IEEE Electron Device Lett. 12 (1991) 366.

- C. Anghel, Y. S. Chauhan, N. Hefyene, and A. Ionescu: Proc. IEEE Int. Symp. Industrial Electronics (ISIE), 2005, p. 473.

- 16) T. C. Lim and G. A. Armstronga: Solid-State Electron. 50 (2006) 774.

- 17) H. L. Kao, A. Chin, C. C. Liao, C. C. Chen, S. P. McAlister, and C. C. Chi: IEEE Trans. Electron Devices 53 (2006) 636.

- D. Gloria, A. Perrotin, P. Gonella, and G. Morin: IEEE MTT-S Int. Microwave Symp. Dig., 1999, p. 831.