# Random Work-Function-Induced Threshold Voltage Fluctuation in Metal-Gate MOS Devices by Monte Carlo Simulation

Yiming Li, Member, IEEE, and Hui-Wen Cheng, Student Member, IEEE

Abstract-In this paper, we estimate the effect of random work function (WK) on the threshold voltage fluctuation ( $\sigma V_{th}$ ) of 16-nm-gate metal-oxide-semiconductor field-effect transistors (MOSFETs) with metal-gate materials. To examine the random WK induced  $\sigma V_{\text{th}}$ , nanosized metal grains with different gate materials are considered in a large-scale statistical simulation. An analytical expression of the  $\overline{W}K$  induced  $\sigma V_{th}$  is proposed based on the Monte Carlo simulation results which can outlook different extents of fluctuation resulting from various metal gates and benefit the device fabrication. Devices with a two-layer metalgate are further studied for fluctuation suppression; the finding of this paper indicates the first layer of the gate structure plays the most significant role in the suppression of the WK induced  $\sigma V_{th}$ , compared with the second layer. This paper provides an insight into random work-function-induced threshold voltage fluctuation, which can, in turn, be used to assess metal gate characteristics of MOSFETs.

Index Terms—Averaged work function, metal gate, Monte Carlo, MOS devices, threshold voltage fluctuation simulation, work function (WK).

### I. INTRODUCTION

HARACTERISTIC fluctuation is a crucial issue for nanometer-scale (nanoscale) metal-oxide-semiconductor field-effect transistors (MOSFETs) [1]. For state-of-the-art nanoscale devices, the intrinsic parameter fluctuations resulting from line edge roughness, random dopants, and other causes have substantially affected device's characteristics [2]. Diverse approaches have recently been presented to investigate intrinsic parameter fluctuations in semiconductor devices [2]–[10]. Among these approaches, the high- $\kappa$ /metal gate is one of the key technologies for suppressing intrinsic parameter fluctuations; it has been recognized as a key to sub-45-nm transistor technology due to the small gate leakage current with an increased gate capacitance. The sheet resistance is also reduced with the use of metal as gate material. Comparing

Manuscript received October 18, 2011; accepted December 10, 2011. Date of publication December 26, 2011; date of current version May 4, 2012. This work was supported in part by the Taiwan National Science Council (NSC), under Contracts NSC-100-2221-E-009-018 and NSC-99-2221-E-009-175, and by Taiwan Semiconductor Manufacturing Company, Hsinchu, Taiwan, under a 2011 grant.

The authors are with the Parallel and Scientific Computing Laboratory, Department of Electrical Engineering, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: ymli@faculty.nctu.edu.tw; hwcheng@mail.ymlab.org).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TSM.2011.2181964

with the poly-gate technology, the metal gate material will not react with high-k dielectric; therefore, there exists a less pinning effect of threshold voltage ( $V_{th}$ ). Moreover, the phonon scattering effect is significantly reduced due to the less quantum resonance effect [11], [12].

However, the grain orientation of metal is uncontrollable during growth period. Metal grains will be grown up to a few nanometers in size under temperatures that normally used in semiconductor device fabrication [2], [11]. The gate area of 16-nm devices will contain only a small number of grains. The use of metal as gate material will result in the work function fluctuation (WKF) due to the dependence of work function on nanosized metal grain orientations [13]. A simulation study of WKF is, thus, necessary for us to understand the threshold voltage fluctuation ( $\sigma V_{\text{th}}$ ) in 16-nm devices. In this paper, we present a Monte Carlo simulation to evaluate the effect of WKF on 16-nm MOSFET devices. Both the metal grain size and the metal gate material are considered in the statistical simulation to examine the effect of WKF on device's  $V_{\text{th}}$ . Among four examined gate materials, titanium nitride (TiN) possesses the smallest  $\sigma V_{\text{th}}$ . A device with a multilayer metal gate material is further simulated; it is found that the first layer plays the most important role in suppressing  $\sigma V_{\text{th}}$ .

This paper is organized as follows. In Section II, we introduce the simulation procedure for studying the WKF induced  $\sigma V_{\text{th}}$ . In Section III, we study and model the fluctuations with respect to different device gate area, size of metal grains, and gate materials. We further advance the method to explore the WKF induced  $\sigma V_{\text{th}}$  for devices with multilayer metal gatestacks. Finally, we draw conclusions and suggest the future work.

## II. STATISTICAL SIMULATION TECHNIQUE

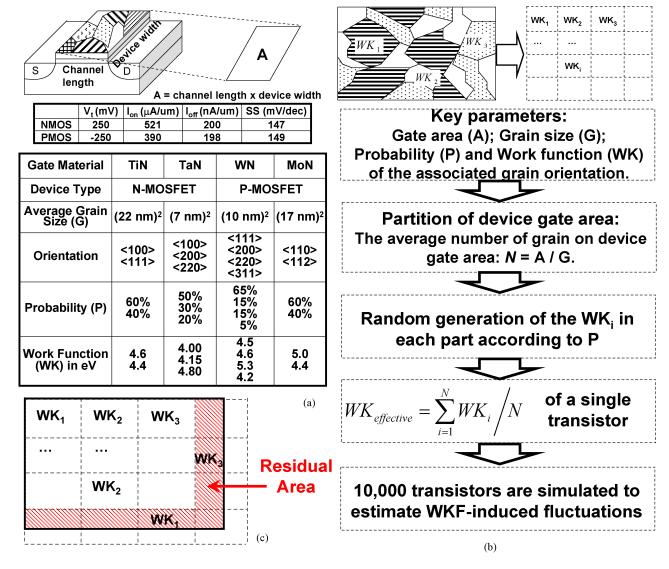

We explore the planar MOSFET device with amorphous-based HfSiON gate-stacks and different metal materials; TiN and tantalum nitride (TaN) are considered in the n-type MOSFET (N-MOSFET), and tungsten nitride (WN) and molybdenum nitride (MoN) are used for the p-type MOSFET (P-MOSFET) [2], [12]. The nominal device characteristics of the examined TiN-gate N-MOSFET and the MoN-gate P-MOSFET devices are mainly according to the projection of ITRS roadmap for low operating power applications. Fig. 1(a) indicates the gate area (A) containing many metal grains

Fig. 1. (a) Device gate area is A which composes many nanosized metal grains; the average grain size (G), the probability (P), and the work function (WK) of each grain orientation for different metal materials used in this paper are listed. The performances shown here are the N-MOSFET with a TiN gate and the P-MOSFET with a MoN gate, where  $V_{th}$  is the threshold voltage,  $I_{on}$  and  $I_{off}$  are the on-state and off-state currents, and SS is the subthreshold swing. (b) Proposed simulation flow to study the WKF induced  $\sigma V_{th}$ , the grain shape is assumed to be square without loss of generality. (c) In the simulation procedure, residual areas are also considered to provide the best accuracy of statistical simulation.

for a given material, the average grain size (G) which is adopted from experimental observations in [11], for example, the probability (P), and the work function (WK) of grain orientation for different metal materials used in the Monte Carlo simulation [12]. Since each random grain orientation has different WK which should be treated as a probabilistic distribution rather than a deterministic value, the Monte Carlo simulation is advanced to account for such a probabilistic distribution. Fig. 1(b) shows the simulation procedure. First, the gate area of a 16-nm transistor is partitioned into several square subareas according to the average grain size. The WK of each partitioned subarea is randomly generated according to its probability; and the effective WK of the metal gate is equal to an averaged value of all WKs. We calculate the effective work function of 10000 randomly generated gates to estimate the WKF induced  $\sigma V_{\text{th}}$ . Notably, the approach appearing in [12] does not consider the residual of gate area.

Without including residual of gate area may underestimate  $\sigma V_{\text{th}}$ . In order to consider the residual of gate area, as shown in Fig. 1(c), we also randomly generate WK for each residual grain in the Monte Carlo simulation and take account of the corresponding weight of these residual areas when calculating the total effective WK.

#### III. RESULTS AND DISCUSSION

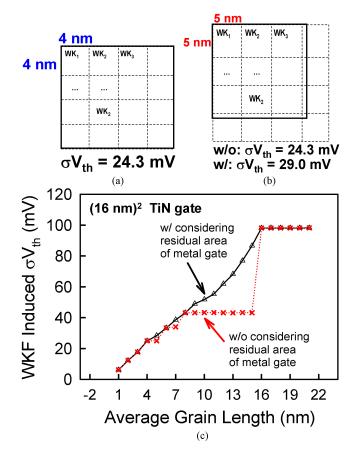

First, we compare the difference of  $\sigma V_{th}$  in the proposed method with and without considering residual areas because the device's gate area will not always contain integer grains. As shown in Fig. 2(a), for N-MOSFETs with  $(16 \text{ nm})^2$  TiN gate, for a 4-nm length of metal grain, the threshold voltage fluctuation is the same ( $\sigma V_{th} = 24.3 \text{ mV}$ ) for the method with and without considering residual area because the device area of  $(16 \text{ nm})^2$  divided by the grain size of  $(4 \text{ nm})^2$  is

Fig. 2. Plot of device with a  $(16 \, \text{nm})^2$  TiN gate, where each grain size is (a)  $(4 \, \text{nm})^2$  and (b)  $(5 \, \text{nm})^2$ . (c) Plot of the WKF induced  $\sigma V_{\text{th}}$  as a function of the average grain size for the method with (w/) and without (w/o) considering the residual areas of metal gate.

an integer. For a 5-nm length of metal grain, as shown in Fig. 2(b), the fluctuation of threshold voltages calculated with considering residual area ( $\sigma V_{\text{th}} = 29.0 \,\text{mV}$ ) is greater than that of without considering residual area ( $\sigma V_{\text{th}} = 24.3 \,\text{mV}$ ). The device area of (16 nm)<sup>2</sup> divided by the grain size of (5 nm)<sup>2</sup> is not an integer and it has a fractional part, and such a residual area is not considered into the calculation without considering residual area; consequently, the fluctuation of threshold voltages calculated with considering is greater than that of without considering residual area. As shown in Fig. 2(c), the WKF induced  $\sigma V_{\text{th}}$  increases continuously as the average grain length (i.e., the square root of averaged grain size) increases when the Monte Carlo calculation with considering the residual areas. If we do not consider the residual area properly the change of  $\sigma V_{\text{th}}$  behaves as a step-like function when the average grain length increases. Estimation of  $\sigma V_{\text{th}}$  will be underestimated and compared with the result of Monte Carlo simulation with considering residual area of metal gate because sizeable residual areas will be ignored in this scenario. For example, for the device area of  $(16 \text{ nm})^2$ , the device maintains  $\sigma V_{\text{th}}$  the same and is less than the fluctuation of threshold voltages calculated with considering residual areas because the residual areas are not counted into the calculation without including residual areas for the grain sizes varying from  $(8 \text{ nm})^2$  to  $(15 \text{ nm})^2$ .

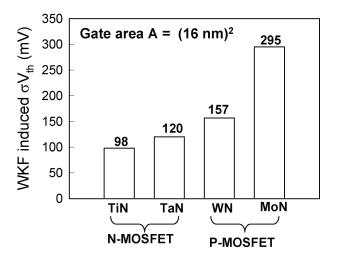

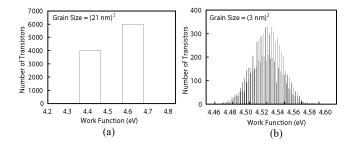

Fig. 3. WKF induced  $\sigma V_{\text{th}}$  with respect to different material whose properties are listed in Fig. 1(a). The gate area of devices is  $(16 \text{ nm})^2$ .

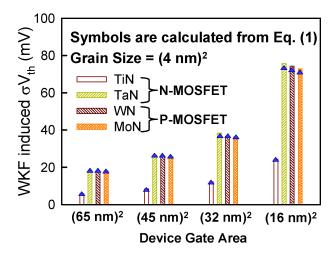

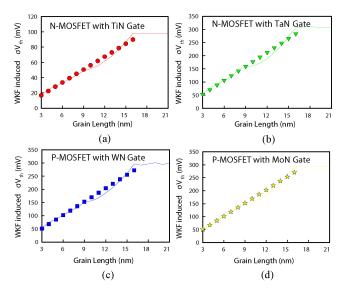

Fig. 3 shows the WKF induced  $\sigma V_{\text{th}}$  for the property of metal, as shown in Fig. 1(a). We find that the gate with TiN material exhibits the smallest  $\sigma V_{\text{th}}$  among four different gate materials and the device with MoN gate shows the largest  $\sigma V_{\text{th}}$ . To find the key factor of WKF, we further compare the  $\sigma V_{th}$  with respect to different materials and gate areas  $(A = \text{channel length} \times \text{device width}), \text{ where the grain size}$ (4 nm)<sup>2</sup> is fixed, as shown in Fig. 4. The device with TiN gate induces the smallest  $\sigma V_{\text{th}}$  due to few grain orientations and small WKF of each orientation. As shown in Fig. 5, among TiN, TaN, WN, and MoN gate materials, we compare the WKF induced  $\sigma V_{\text{th}}$  versus the size of metal grains, where the gate area of  $(16 \,\mathrm{nm})^2$  is fixed. The results indicate that the value of  $\sigma V_{\rm th}$  increases as the grain size increases. It is because when the grain size is large, the gate area may contain only one grain, and thus the effective WK of a single transistor could be either 4.4 or 4.6 eV; consequently, it induces two quite different threshold voltages, as shown in Fig. 6(a). As a result, it will result in a relatively large standard deviation of the threshold voltage in the simulated 10000 devices. On the other hand, when the metal gate's grain size is small (e.g., amorphous-like material), the gate area contains many nanosized metal grains and the averaged WK approaches a Gaussian distribution, as shown in Fig. 6(b). From a device fabrication point of view, metal deposition at a low temperature or adding composite materials could be considered to obtain small size of metal grains. Additionally, when the grain size is larger than the device's gate area, the  $\sigma V_{\rm th}$  will saturate at a specific value due to the unchanged number of grains in the device's gate area (i.e., it contains only one grain which totally covers the gate area). We observe that the WKF induced  $\sigma V_{\text{th}}$  is strongly affected by the gate area, the size of metal grains, and the adopted gate material, according to the results of aforementioned Monte Carlo simulation. Therefore, an analytical expression is empirically proposed to model the WKF induced  $\sigma V_{th}$

$$\sigma V_{\rm th} = \alpha \sigma_{\Phi m} \sqrt{\frac{G}{A}} \tag{1}$$

Fig. 4. Comparison of the WKF induced  $\sigma V_{\text{th}}$  among four different gate materials with respect to different device gate areas (the area A = channel length  $\times$  device width). A minimal grain size of  $(4 \text{ nm})^2$  is assumed for all metal grains. Each symbol is analytically calculated by using (1).

Fig. 5. WKF induced  $\sigma V_{\text{th}}$  as a function of grain length for the N-MOSFET with the (a) TiN and (b) TaN gates, and the P-MOSFET with the (c) WN and (d) MoN gates, respectively, where the gate area is  $(16\,\text{nm})^2$  and the grain length is the square root of grain size. The line is the Monte Carlo simulation result and the symbol is analytically calculated by using (1).

where G and A are the grain size and the device gate area, respectively, and  $\sigma_{\Phi m}$  is the work function deviation calculated from the probability P and the work function of metal grain's orientation. The  $\alpha$  is a fitting coefficient, which is independent of the probability P and gate area A, and could be validated from silicon data experimentally. According to metal's property, as shown in Fig. 1(a), the extracted values of  $\sigma_{\Phi m}$  for TiN, TaN, WN, and MoN are 0.098, 0.305, 0.296, and 0.294, respectively. The symbols, as shown in Figs. 4 and 5, are the calculated  $\sigma V_{\rm th}$  using (1) with the coefficient a=920; as shown in Fig. 4, the calculated  $\sigma V_{\rm th}$  using (1) versus the device gate area show acceptable approximations to the Monte Carlo simulation. Notably, for the results before the saturation, the calculations by using (1) with respect to four

Fig. 6. Work-function distribution for the grain size of (a)  $(21 \text{ nm})^2$  and (b)  $(3 \text{ nm})^2$ .

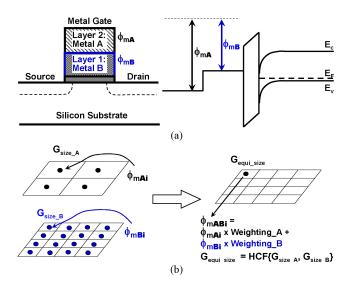

Fig. 7. (a) Schematic plot of the simulated two-layer metal-gate structure and its band diagram,  $\phi_{\rm mB}$  and  $\phi_{\rm mA}$  are WKs of metal with respect to different grain orientation at the first and second layers, respectively. (b) Illustration of the method used to determine the equivalent grain size ( $G_{\rm equi\_size}$ ) and the associated WK ( $\phi_{\rm mAB}$ ) for the Monte Carlo simulation of the WKF induced  $\sigma V_{\rm th}$  of the device with two-layer metal-gate structure. Notably, the adopted weightings of all WKs in partitioned grain areas are determined from device simulation.  $\phi_{\rm mBi}$  and  $\phi_{\rm mAi}$  are WKs at each point i within the local gate area of the metal B (layer 1) and the metal A (layer 2), respectively.

TABLE I

COMPARISON OF THE THRESHOLD VOLTAGE FLUCTUATION OF THE

16-NM N-MOSFET WITH DIFFERENT TWO-LAYER METAL-GATE

STRUCTURES

|   | Material     | Minimal Grain Size   | Device Gate Area     | $\sigma V_{\text{th}} \text{ (mV)}$ |

|---|--------------|----------------------|----------------------|-------------------------------------|

|   | TiN (layer1) | $(4 \text{ nm})^2$   | $(16 \mathrm{nm})^2$ | 22.9                                |

| Γ | MoN (layer2) | $(4 \text{ nm})^2$   |                      |                                     |

| Γ | MoN (layer1) | (4 nm ) <sup>2</sup> | $(16 \mathrm{nm})^2$ | 65.9                                |

|   | TiN (layer2) | (4 nm) <sup>2</sup>  |                      |                                     |

Compared with the results of devices with single-layer metal gate, the device with TiN as the first layer of the two-layer metal-gate configuration TiN + MoN has a minimal  $\sigma V_{\rm th}$  of 22.9 mV.

different materials are in good agreement with the Monte Carlo simulations. Equation (1) is validated for those grain sizes which are smaller than the device's gate area; for the grain size larger than the gate area, the WKF induced  $\sigma V_{th}$  is saturated, as mentioned above. Equation (1) works for both N-MOSFET and P-MOSFET devices which could be used as first-order estimation for the effect of WKF on metal-gate devices.

Device with a multilayer metal gate structure is one of the process techniques to reduce the WK induced  $\sigma V_{\text{th}}$ . The Monte Carlo simulation technique discussed in this paper can also predict the tendency of  $\sigma V_{\text{th}}$  owing to a multilayer metal gate. Fig. 7(a) illustrates a two-layer metal-gate structure and its band diagram; as shown in Fig. 7(b), we introduce a mapping method to estimate the WKF resulting from the structure of multilayer metal gate. We first independently and randomly generate the WK of each grain for different metal layers by following the procedure, as shown in Fig. 1(b). Thus, each layer has its own distribution of WK. To calculate the averaged WK for the device with the two-layer metal-gate structure, we first find the highest common factor, also known as the greatest common divisor, of each grain size between two layers; and then, the WK at each point within the local gate area is a combination of the  $\phi_{\rm mB}$  and  $\phi_{\rm mA}$  with a given weight, as shown in Fig. 7(b), and the  $\phi_{mABi}$  is the effective WK in the given partitioned area. The weight of each layer could be determined by the device simulation; for example, by alternating the metal layers as the first layer on the gate, we can get different threshold voltages. Then the weight of each layer can be determined by the percentage of the total sum of those threshold voltages, where the device characteristic is estimated by using a 3-D device simulation [2], [8], [9].

Based upon this mapping method, we examine the device with a two-layer metal-gate structure, where devices with two layers TiN and MoN denoted as TiN + MoN, and MoN and TiN denoted as MoN + TiN are studied. The adopted weight of the first layer is 90% and that of the second layer is 10%. Table I lists the  $\sigma V_{th}$  comparison for the device using two different materials as the first layer of the two-layer metalgate structures. Considering the device area of  $(16 \text{ nm})^2$ , for example, for the given materials TiN and MoN with the grain size of  $(4 \text{ nm})^2$ , as the first layer of the two-layer metal-gate structure, the results of this paper suggest that the first layer dominates the  $\sigma V_{\text{th}}$ . It is because physically the first layer of metal gate plays the most significant controllability to the surface of device channel. Compared with the results of 16-nm device with TiN and MoN gate materials as shown in Fig. 4, we find that the  $\sigma V_{\text{th}}$  is reduced from 24.3 mV to 22.9 mV for the device with TiN as the first layer of the two-layer metalgate structure. For the device with MoN as the first layer of the two-layer metal gate materials, the reduction is from 72.9 mV to 65.9 mV, as summarized in Table I.

#### IV. CONCLUSION

In this paper, a simple Monte Carlo simulation was performed to estimate the effect of WKF on the threshold voltage of 16-nm devices. The results of this paper have shown that the large size of metal grains and small device's gate area will induce sizeable  $\sigma V_{\rm th}$ . However, the fluctuation will be saturated if the grain size is larger than the device's gate area. Devices with TiN gate have shown interesting behavior against WKF due to few grain orientations and small WK deviation of each orientation. For the device with a multilayer metal gate structure, the first layer plays the most important role in suppressing the WK fluctuation. The Monte Carlo simulation

method has also been implemented for random WK induced  $\sigma V_{\rm th}$  in 16-nm FinFETs. The results predicted with this model could be in good agreement with the experimental data [14], thus proving the reliability of this method. Instead of the statistically averaged WK method presented here, studying WKF with a realistic 3-D device simulation will bring more rich physical insights. In addition, the grain size may obey a probability distribution; instead of an average value assumed in this paper, a probability distribution to generate sizes of different grains covering the gate should be used in the future work. Notably, we do not consider the random-dopant fluctuation with the WKF simultaneously and this should be subject to further investigation for more accurate estimation and engineering findings.

#### REFERENCES

- K. J. Kuhn, M. D. Giles, D. Becher, P. Kolar, A. Kornfeld, R. Kotlyar, S. T. Ma, A. Maheshwari, and S. Mudanai, "Process technology variation," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2197–2208, Aug. 2011.

- [2] Y. Li, C.-H. Hwang, T.-Y. Li, and M.-H. Han, "Process variation effect, metal-gate workfunction and random dopant fluctuations in emerging CMOS technologies," *IEEE Trans. Electron Devices*, vol. 57, no. 2, pp. 437–447, Feb. 2010.

- [3] Y. Li, H.-W. Cheng, and M.-H. Han, "Statistical simulation of static noise margin variability in static random access memory," *IEEE Trans. Semicond. Manuf.*, vol. 23, no. 4, pp. 509–516, Nov. 2010.

- [4] Y. Li, H.-W. Cheng, C.-Y. Yiu, and H.-W. Su, "Nanosized metal grains induced electrical characteristic fluctuation in 16-nm-gate high-k/metal gate bulk FinFET devices," *Microelectron. Eng.*, vol. 88, pp. 1240–1242, Jul. 2011.

- [5] Y. Li and H.-W. Cheng, "Nanosized-metal-grain-induced characteristic fluctuation in 16-nm-gate complementary metal-oxide-semiconductor devices and digital circuits," *Japan. J. Appl. Phys.*, vol. 50, no. 4, p. 04DC22, Apr. 2011.

- [6] A. T. Putra, T. Tsunomura, A. Nishida, S. Kamohara, K. Takeuchi, and T. Hiramoto, "Impact of oxide thickness fluctuation and local gate depletion on threshold voltage variation in metal-oxide-semiconductor field-effect transistors," *Japan. J. Appl. Phys.*, vol. 48, no. 6, p. 064504, 2009.

- [7] K.-F. Lee, Y. Li, and C.-H. Hwang, "Asymmetric gate capacitance and dynamic characteristic fluctuations in 16 nm bulk MOSFETs due to random distribution of discrete dopants," *Semicond. Sci. Technol.*, vol. 25, no. 4, p. 045006, Apr. 2010.

- [8] Y. Li and C.-H. Hwang, "Discrete-dopant-induced characteristic fluctuations in 16 nm multiple-gate silicon-on-insulator devices," *J. Appl. Phys.*, vol. 102, no. 8, p. 084509, Oct. 2007.

- [9] Y. Li, C.-H. Hwang, and M.-H. Han, "Simulation of characteristic variation in 16-nm-gate FinFET devices due to intrinsic parameter fluctuations," *Nanotechnology*, vol. 21, no. 5, p. 095203, Mar. 2010

- [10] Y. Li, S.-M. Yu, J.-R. Hwang, and F.-L. Yang, "Discrete dopant fluctuations in 20-nm/15 nm-gate planar CMOS," *IEEE Trans. Electron Devices*, vol. 55, no. 6, pp. 1449–1455, Jun. 2008.

- [11] K. Ohmori, T. Matsuki, D. Ishikawa, T. Morooka, T. Aminaka, Y. Sugita, T. Chikyow, K. Shiraishi, Y. Nara, and K. Yamada, "Impact of additional factors in threshold voltage variability of metal/high-k gate-stacks and its reduction by controlling crystalline structure and grain size in the metal gates," in *Proc. IEDM Tech. Dig.*, Dec. 2008, pp. 409–412.

- [12] H. Dadgour, K. Endo, V. De, and K. Banerjee, "Modeling and analysis of grain-orientation effects in emerging metal-gate devices and implications for SRAM reliability," in *Proc. IEDM Tech. Dig.*, Dec. 2008, pp. 705–708.

- [13] T. Matsukawa, S. O'uchi, K. Endo, Y. Ishikawa, H. Yamauhci, Y. X. Liu, J. Tsukada, K. Sakamoto, and M. Masahara, "Comprehensive analysis of variability sources of FinFET characteristics," in *Proc. Symp. VLSI Tech. Dig.*, Jun. 2009, pp. 118–119.

- [14] H.-W. Cheng and Y. Li, "Random work function variation induced threshold voltage fluctuation in 16-nm bulk FinFET devices with highk-metal-gate material," in *Proc. 14th IEEE IWCE*, Oct. 2010, pp. 1–4.

Yiming Li (M'02) received the B.S. degree in applied mathematics and electronics engineering, the M.S. degree in applied mathematics, and the Ph.D. degree in electronics from National Chiao Tung University (NCTU), Hsinchu, Taiwan, in 1996, 1998, and 2001, respectively.

In 2001, he joined the National Nano Device Laboratories (NDL), Hsinchu, as an Associate Researcher and the Microelectronics and Information Systems Research Center (MISRC), NCTU, as a Research Assistant Professor, where he has been

engaged in the field of computational science and engineering, particularly in modeling, simulation, and optimization of nanoelectronics and very large scale integration circuits. In 2002, he was a Visiting Assistant Professor with the Department of Electrical and Computer Engineering, University of Massachusetts, Amherst. From 2003 to 2004, he was a Research Consultant with the System-on-a-Chip Technology Center, Industrial Technology Research Institute, Hsinchu. From 2003 to 2005, he was the Head of the Departments of Nanodevice and Computational Nanoelectronics, NDL, and since 2004, he has been a Research Associate Professor with MISRC. He has also been the Deputy Director General with NDL from 2009 to 2011. From 2005 to 2008, he was an Associate Professor with the Department of Communication Engineering, NCTU, where he is currently a Full Professor with the Department of Electrical Engineering, is the Deputy Director of the Modeling and Simulation Center, and conducts the Parallel and Scientific Computing Laboratory. He is a Visiting Scholar with the Department of Electrical Engineering, Stanford University, Stanford, CA, in 2011. He has authored or co-authored over 150 research papers appearing in international book chapters, journals, and conferences. He has delivered more than 50 invited talks and lectures in international conferences, summer schools, and academic and industrial organizations worldwide. He has been a Professional Lecturer and conducted over 35 in-house research projects in both semiconductor and photonics industries. His current research interests include computational electronics and electromagnetics, physics of semiconductor nanostructures, transport simulation and model parameter extraction for semiconductor and photonics devices, computer-aided-design theory and technology, biomedical and energy harvesting devices simulation, parallel and scientific computing, and optimization methodology.

Dr. Li is a member of Phi Tau Phi and is included in *Who's Who in the World*. He has served as a Reviewer, Guest Associate Editor, Guest Editor, Associate Editor, and Editor for more than 30 international journals. He was the recipient of the 2002 Research Fellowship Award presented by the Pan Wen-Yuan Foundation, Taiwan, the 2006 Outstanding Young Electrical Engineer Award from the Chinese Institute of Electrical Engineering, Taiwan, the Best Paper Award of the 2008–2011 International Electron Devices and Materials Symposia, and the Best Paper Award of the 2009 and 2011 IEEE Asia Symposium on Quality Electronic Design, Kuala Lumpur, Malaysia. He has served on technical committees and as the Chairman for many international professional conferences. He has served as an Active Reviewer for seven IEEE journals. He has organized and served on several international conferences and was an Editor for proceedings of international conferences, including IEEE IEDM, SISPAD, ISQED, IWCE, INEC, and AQSED.

**Hui-Wen Cheng** (S'08) received the B.S. degree in atmospheric sciences from National Taiwan University, Taipei, Taiwan, in 2003. Currently, she is pursuing the Ph.D. degree with the Parallel and Scientific Computing Laboratory, Department of Electrical Engineering, National Chiao Tung University, Hsinchu, Taiwan.

Her current research interests include numerical modeling and computer simulation of semiconductor nano-CMOS devices.

Ms. Cheng was the recipient of the Best Paper Award presented by the 2011 International Electron Devices and Materials Symposia, Taiwan, for her studying characteristic fluctuation in emerging 16-nm-gate CMOS and FinFET devices with high-k/metal gate technologies, and the Best Paper Award of the 2011 IEEE Asia Symposium on Quality Electronic Design, Kuala Lumpur, Malaysia.