Home Search Collections Journals About Contact us My IOPscience

### Flexible One Diode-One Resistor Crossbar Resistive-Switching Memory

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2012 Jpn. J. Appl. Phys. 51 04DD09

(http://iopscience.iop.org/1347-4065/51/4S/04DD09)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 28/04/2014 at 21:23

Please note that terms and conditions apply.

DOI: 10.1143/JJAP.51.04DD09

#### Flexible One Diode-One Resistor Crossbar Resistive-Switching Memory

Jiun-Jia Huang, Tuo-Hung Hou\*, Chung-Wei Hsu, Yi-Ming Tseng, Wen-Hsiung Chang<sup>1</sup>, Wen-Yueh Jang<sup>1</sup>, and Chen-Hsi Lin<sup>1</sup>

Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan <sup>1</sup> Winbond Electronics Corporation, Taichung 428, Taiwan

Received September 26, 2011; revised December 2, 2011; accepted December 24, 2011; published online April 20, 2012

We report the first demonstration of a flexible one diode—one resistor (1D1R) resistive-switching (RS) memory cell capable of high-density crossbar array implementation at an extremely low cost. A Ti/TiO<sub>2</sub>/Pt diode with a large rectifying ratio and a stable Ni/HfO<sub>2</sub>/Pt unipolar RS memory element have been fabricated on a polyimide substrate using only room-temperature processes. No significant degradation of the rectifying ratio of the TiO<sub>2</sub> diode and the cycling variations, retention, and read disturb immunity of the HfO<sub>2</sub> memory was observed in the bending state. The series 1D1R cell shows highly reproducible unipolar RS because of the low reset current of the HfO<sub>2</sub> memory, which greatly mitigates the adverse effect of diode series resistance. Furthermore, the 1D1R cell can effectively suppress read interference and realize a crossbar array as large as 512 kbit. © 2012 The Japan Society of Applied Physics

#### 1. Introduction

Flexible electronics have received increasing attention because of their advantages of low cost, light weight, flexibility, and capability of large-area process. However, traditional Si technology requiring high-temperature processes is incompatible with the low glass transition temperature of flexible substrates. In contrast, oxide-based materials deposited at a low temperature have shown promising characteristics for flexible electronics applications, such as indium-gallium-zinc oxide for thin-film transistors in the flexible active matrix backplane. 1) To realize another fundamental building block of flexible electronics, namely, nonvolatile memory, considerable efforts are being made to develop resistive-switching random access memory (RRAM) on flexible substrates, exploiting the nonvolatile variable resistance in transition metal oxides.<sup>2-4)</sup> In addition to its superior memory characteristics, RRAM is highly attractive for flexible nonvolatile memory because of its simple crossbar architecture and low-temperature fabrication.<sup>5)</sup> However, a passive crossbar array is known to suffer from the so-called sneak current problem, and thus it is difficult to scale up beyond 64 bits because of severe read interference.<sup>6,7)</sup> The development of low-temperature selection devices in series with resistive-switching (RS) memory elements on flexible substrates is critical, but significantly less emphasized. Recently, we have successfully demonstrated the fabrication of both RS memories and rectifying oxide diodes on Si substrates at room temperature.<sup>8,9)</sup> The TiO<sub>2</sub>-based metal– insulator-metal (MIM) devices with a Pt bottom electrode exhibited excellent rectifying, bipolar RS, and unipolar RS characteristics, which were realized by choosing appropriate top-electrode materials. The rectifying oxide diode is applicable to the compact one diode-one resistor (1D1R) crossbar architecture, which suppresses read interference in high-density memory arrays. 10-12) In comparison with the conventional one transistor—one resistor (1T1R) architecture, 1D1R with a 4F<sup>2</sup> unit cell size not only significantly increases bit density, but also enables a simple implementation of the low-temperature and low-cost flexible memory.

In this study, we fabricated 1D1R memory cells, consisting of a Ti/TiO<sub>2</sub>/Pt diode element and two different

types of RS memory elements, namely, Pt/TiO2/Pt and Ni/HfO<sub>2</sub>/Pt. The TiO<sub>2</sub>-based diode and RS element are interesting because of their potential for a monolithic TiO<sub>2</sub> 1D1R cell, but a high reset current ( $I_{RESET}$ ) of the TiO<sub>2</sub> RS element (over 10 mA) led to unstable unipolar RS in the 1D1R cell. On the other hand, when the TiO<sub>2</sub>-based diode was integrated with the  $HfO_2$  RS element with a low  $I_{RESET}$ (less than 1 mA), stable unipolar RS characteristics can be realized. Additionally, the excellent rectifying characteristics with a high resistance ratio at reverse and forward biases enabled the realization of a compact 512 kilobit (kb) crossbar memory array with an at least 10% readout margin. Because the entire device fabrication was completed at room temperature, the proposed 1D1R cell was successfully fabricated on a polyimide (PI) substrate and was found to be promising for flexible and high-density memory applications using roll-to-roll processing at an extremely low cost in the future.

#### 2. Experimental Procedure

Prior to the device fabrication, 75-µm-thick Kapton® polyimide (PI) substrates were cut and ultrasonically cleaned in acetone for 10 min to remove particles and contamination, followed by baking at 100 °C for 30 min. The cleaned PI substrates were then electrostatically attached to silicon wafers. Because the PI substrate is susceptible to water absorption, a buffer layer of SiO<sub>2</sub> with a thickness of 300 nm was deposited by plasma-enhanced chemical vapor deposition (PECVD). Platinum bottom electrodes of 80 nm with a thin Ti adhesion layer were deposited onto substrates by electron beam evaporation. To fabricate the TiO2 oxide diode and RS memory element, the TiO2 active layers with a thickness of 50 nm were deposited by electron beam evaporation at room temperature, and then 100-nm-thick Ti and Pt top electrodes with an area of 10<sup>4</sup> μm<sup>2</sup> were patterned using a shadow-mask technique for the Ti/TiO<sub>2</sub>/ Pt diode and the Pt/TiO<sub>2</sub>/Pt RS element, respectively. To fabricate the HfO<sub>2</sub> RS memory element, HfO<sub>2</sub> active layers with a thickness of 80 nm were prepared by dc magnetron reactive sputtering using a Hf target (99.5%) in a mixture of Ar and O<sub>2</sub> at room temperature, and then 100-nm-thick Ni top electrodes with an area of  $10^4 \, \mu m^2$  were patterned using a shadow-mask technique for the Ni/HfO<sub>2</sub>/ Pt RS element. All devices reported in this study were fabricated completely at room temperature without any

<sup>\*</sup>E-mail address: thhou@mail.nctu.edu.tw

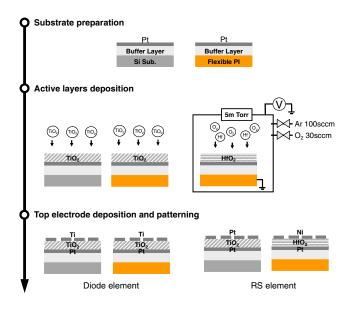

Fig. 1. (Color online) Fabrication of  ${\rm Ti/TiO_2/Pt}$ ,  ${\rm Pt/TiO_2/Pt}$ , and  ${\rm Ni/HfO_2/Pt}$  devices on PI and silicon substrates.

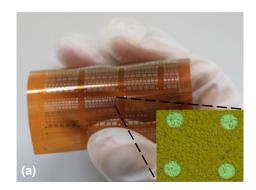

**Fig. 2.** (Color online) (a) Photograph of a fabricated flexible device under bending condition. The insert shows the microscope image of the device on the PI substrate. (b) Measurement setup using a concave stage with a radius of 30 mm to characterize devices in the bending state.

additional thermal treatment. In addition to the flexible devices, conventional devices on silicon substrates were also prepared using the same process. The detailed process flow is shown in Fig. 1. Figure 2(a) shows a photograph of a fabricated flexible device that was highly robust under mechanical strain. Figure 2(b) shows the measurement setup using a concave stage with a radius of 30 mm to characterize

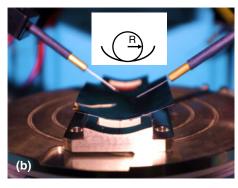

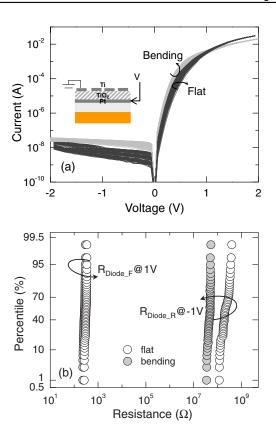

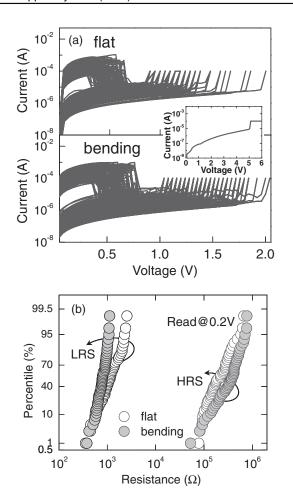

**Fig. 3.** (Color online) (a) 100 successive  $\pm 2 \, \text{V}$  dc sweeps, and (b) cumulative plot of forward/reverse resistances at  $1 \, \text{V}/-1 \, \text{V}$  of the flexible Ti/TiO<sub>2</sub>/Pt diodes in both flat and bending states.

devices in the bending state. All electrical measurements were performed using a HP-4156B semiconductor analyzer. The 1D1R cells were externally connected and voltage was applied to the Ni or Pt top electrode of the RS memory element while the Ti top electrode of the  $TiO_2$  diode element was grounded.

#### 3. Results and Discussion

#### 3.1 Ti/TiO<sub>2</sub>/Pt diode

Figure 3 shows the rectifying characteristics of the Ti/TiO<sub>2</sub>/ Pt diode under both flat and bending conditions. Even though fabricated on the flexible substrate, Ti/TiO2/Pt diodes exhibit a large rectifying ratio of  $10^6$  at  $\pm 1$  V, an ideality factor of 1.2, and a robust endurance up to hundreds of successive DC sweeps without dielectric breakdown. The results are comparable with those of the diodes fabricated on Si, 9) showing a minimal substrate effect. A rectifying ratio of more than  $10^5$  at  $\pm 1 \,\mathrm{V}$  can be maintained in the bended devices, indicating negligible degradation of the diode characteristics under bending condition. The asymmetry of current-voltage (I-V) curves was explained by the different Schottky barrier heights at the Ti/TiO<sub>2</sub> and the TiO<sub>2</sub>/Pt interfaces. 9 When applying a negative voltage to the Pt electrode, electrons were injected from Pt to TiO2, but encountered a substantial Schottky barrier. When applying a positive voltage to Pt, electrons were injected from Ti to TiO<sub>2</sub>. Current increased exponentially with bias voltage and was eventually limited by the smaller barrier at the Ti/TiO2 interface and parasitic series resistance.

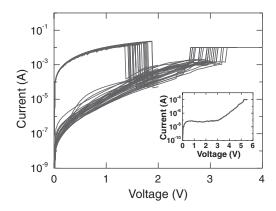

**Fig. 4.** Typical unipolar RS characteristics of the Pt/TiO<sub>2</sub>/Pt memory element with  $I_{RESET}$  over 10 mA. Inset shows the typical forming I-V curve with a forming voltage of approximately 5 V.

#### 3.2 Pt/TiO<sub>2</sub>/Pt RS memory element and monolithic TiO<sub>2</sub> 1D1R cell

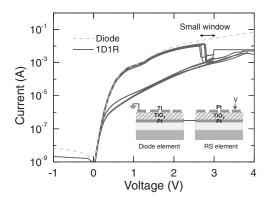

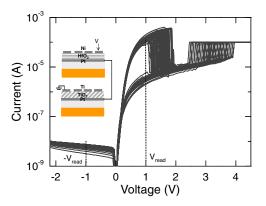

In contrast to the Ti/TiO<sub>2</sub>/Pt bipolar RS memory element, 9) the Pt/TiO<sub>2</sub>/Pt RS memory was nonpolar after the initial forming process and applicable to the 1D1R crossbar array utilizing unipolar RS. The oxygen-deficient filament was believed to be responsible for the observed RS.<sup>8)</sup> Figure 4 shows the typical unipolar RS curves of the Pt/TiO<sub>2</sub>/Pt RS memory for positive SET  $(V_{SET})$  and RESET  $(V_{RESET})$ voltages. Although the unipolar RS was stable, the  $I_{RESET}$ was over 10 mA, comparable to the maximum current a  $TiO_2$  diode can provide. The high  $I_{RESET}$  not only resulted in excessive switching power undesirable for low-power operation, but also deteriorated the stability of RS in a 1D1R cell. Because of the comparable currents in the diode and RS element, the diode series resistance was not negligible in the 1D1R cell when the RS element was in the low resistance state (LRS). Hence,  $V_{\text{RESET}}$  significantly increased. In contrast,  $V_{\text{SET}}$  was less sensitive to diode series resistance because of the considerably larger resistance of the RS element in the high resistance state (HRS). As a result, the programming margin between unipolar  $V_{\rm SET}$  and  $V_{\text{RESET}}$  diminished and unipolar RS became less stable, as shown in Fig. 5, that the TiO<sub>2</sub> 1D1R cell exhibits only a few stable switching cycles without programming error. Figure 6 further shows the predicted programming margin as a function of  $I_{RESET}$  at a fixed diode on-current of 10 mA. For a RS memory element with  $V_{RESET}$  of 0.5 V and  $V_{SET}$ between 2 to 4V considering cycling variations,  $I_{RESET}$ below 1 mA would be required for a stable unipolar RS in the 1D1R cells.

## 3.3 Ni/HfO<sub>2</sub>/Pt RS memory element and heterogeneous HfO<sub>2</sub>-TiO<sub>2</sub> 1D1R cell

The RS in the Ni/HfO<sub>2</sub>/Pt memory fabricated on the flexible PI substrate was also nonpolar after the initial forming process. The RS may be attributed to the formation of Ni filaments through HfO<sub>2</sub> by Ni ion migration from the top electrode after electrical forming, and rupture and connection of Ni filaments by Joule heating and ion migration. Other studies suggested a different mechanism by Joule-heat-induced redox of NiO<sub>x</sub> at the interface of Ni and HfO<sub>2</sub>. Is, I6 Further studies in the future are required

**Fig. 5.** Unstable unipolar RS in the monolithic TiO<sub>2</sub> 1D1R cell because of the small programming margin.

**Fig. 6.** (Color online) (a) Programming margin of a 1D1R cell as a function of  $I_{\rm RESET}$ . The diode on-current was fixed at 10 mA. A  $R_{\rm HRS}/R_{\rm LRS}$  ratio of 100,  $V_{\rm RESET}$  of 0.5 V, and  $V_{\rm SET}$  between 2 to 4 V considering cycling variations were assumed for the RS element. (b) Simulated 1D1R unipolar switching curves for RS elements with  $I_{\rm RESET}$  of 0.1 and 10 mA, respectively.

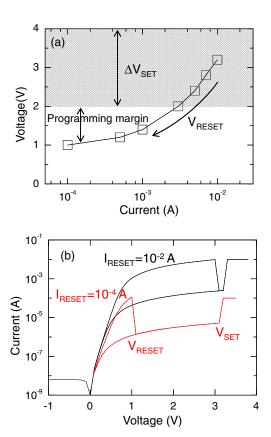

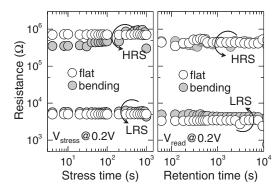

to clarify the origin of the RS in more detail. The unipolar RS with positive  $V_{\rm SET}$  and  $V_{\rm RESET}$  was highly reproducible, as shown in Fig. 7(a), with a resistance ratio of HRS to LRS  $(R_{\rm HRS}/R_{\rm LRS})$  of approximately  $10^2$  and  $I_{\rm RESET}$  less than 1 mA even under bending condition. Figure 7(b) shows the cumulative plot of HRS and LRS resistance in both the flat and bending states with markedly tight distributions. Figure 8 shows superior immunity to read disturb and retention characteristics of the HfO<sub>2</sub> RS element regardless of whether the substrate was flat or bended. The reproducible and reliable unipolar RS in the bending state demonstrates

**Fig. 7.** (a) 100 successive unipolar RS cycles with  $I_{\rm RESET}$  less than 1 mA, and (b) cumulative plot of HRS and LRS resistance at 0.2 V of the flexible Ni/HfO<sub>2</sub>/Pt memory element in both flat and bending states. Inset in (a) shows the typical forming I-V curve with a forming voltage of approximately 5 V.

Fig. 8. Read disturb and retention characteristics of the flexible  $\rm Ni/HfO_2/Pt$  memory element in both flat and bending states.

the feasibility of RS memory for flexible electronics applications. In Fig. 9, by connecting the  $HfO_2$  RS memory with low  $I_{RESET}$  and the  $TiO_2$  diode in series, a highly reproducible unipolar RS with a substantial  $R_{HRS}/R_{LRS}$  ratio was realized at a positive bias, whereas the current at a negative bias remained extremely low owing to the reverse-biased diode even when the RS memory was in LRS. The high rectifying ratio shown here is among the best ever

**Fig. 9.** (Color online) More than 200 successive unipolar RS cycles with a high rectifying ratio at  $\pm 1 \, \text{V}$  in the heterogonous  $\text{TiO}_2\text{-HfO}_2 \, 1\text{D1R}$  cell.

**Fig. 10.** (Color online) Schematic of an  $N \times N$  crossbar memory array and its equivalent circuit in the worse-case read scenario where all unselected cells are in LRS. The sneak current through  $R_1$ ,  $R_2$ , and  $R_3$  results in severe read interference.

reported for 1D1R cells, including those fabricated on Si substrates. 10-12)

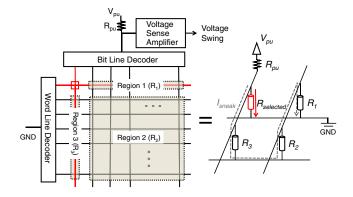

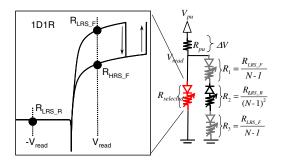

# 3.4 Prediction of read margin in 1D1R crossbar array In this section, the prediction on the read margin of 1D1R

crossbar array is explained using the device parameters extracted from the standalone 1D1R cell in Fig. 9. Figure 10 depicts the equivalent circuit of an  $N \times N$  crossbar memory array in the worse-case scenario of read interference where all unselected cells are in LRS.6,17) Considering a one bitline pull-up read scheme, 6) the sneak current can flow through the unselected cells, represented by the parallel resistor networks of R<sub>1</sub>, R<sub>2</sub>, and R<sub>3</sub> in Fig. 10, which leads to read error when the selected cell is in HRS  $(R_{\text{selected}} = R_{\text{HRS}})$ . In the 1D1R crossbar array as shown in Fig. 11, R<sub>2</sub> contributed by all unselected cells at unselected word/bit lines in parallel is considerably larger than the sum of R<sub>1</sub> and R<sub>3</sub> because of the reverse biased diodes. Therefore, the resistance in the sneak current path can be approximated by  $R_{LRS\_R}/(N-1)^2$ , where  $R_{LRS\_R}$  is the resistance of the standalone 1D1R cell in LRS dominated by the reverse biased diode at the negative read voltage  $-V_{\text{read}}$ , as shown in Fig. 11. R<sub>LRS\_F</sub> and R<sub>HRS\_F</sub> are also defined as the resistances of the standalone 1D1R cell in LRS and HRS, respectively, when read at  $V_{\text{read}}$ . When  $R_{\text{LRS\_R}}/(N-1)^2$ decreases as N increases and eventually becomes comparable to  $R_{LRS\_F}$  of the selected bit, the sneak current begins to

**Fig. 11.** (Color online) Equivalent circuit of a 1D1R crossbar array at read. The total resistance of the sneak current path is dominated by  $R_2$  because of the reverse-biased diodes.

interfere with the read process in the large 1D1R array. Thus, the ratio of  $R_{LRS\_R}$  to  $R_{LRS\_F}$  is a good measure of the maximum crossbar array size with a tolerable read margin.

The readout voltage on the pull-up resistor  $R_{\rm pu}$  can be calculated when  $R_{\rm selected}=R_{\rm LRS\_F}$  and  $R_{\rm selected}=R_{\rm HRS\_F}$ , using an equivalent circuit method similar to that applied for a complementary resistive switch (CRS) crossbar array<sup>18)</sup> and a one selector–one resistor (1S1R) crossbar array.<sup>19)</sup> When  $R_1$  and  $R_3$  are omitted in Fig. 11, the readout voltage swing  $\Delta V$  normalized to the pull-up voltage  $V_{\rm pu}$  can be quantitatively estimated using the resistor voltage divider equation as follows:

$$\frac{\Delta V}{V_{\text{pu}}} = \frac{R_{\text{pu}}}{\left[R_{\text{LRS\_F}} \parallel \frac{R_{\text{LRS\_R}}}{(N-1)^2}\right] + R_{\text{pu}}} - \frac{R_{\text{pu}}}{\left[R_{\text{HRS\_F}} \parallel \frac{R_{\text{LRS\_R}}}{(N-1)^2}\right] + R_{\text{pu}}}, \tag{1}$$

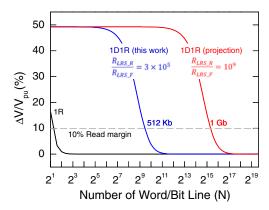

where  $R_{\rm pu}$  is set to  $R_{\rm LRS\_F}$  for the maximum read margin. For a 10% readout margin, Fig. 12 shows that the maximum allowed word lines in a square crossbar array increased dramatically from 2 in a passive array to 750, which is equivalent to approximately 512 kb, in a 1D1R array utilizing the parameters extracted from Fig. 9. The 1D1R array can be further scaled up to 1 Gb with an improved  $R_{\rm LRS\_R}/R_{\rm LRS\_F}$  ratio of  $10^9$ .

#### 4. Conclusions

A rectifying Ti/TiO<sub>2</sub>/Pt oxide diode and a unipolar RS Ni/ HfO<sub>2</sub>/Pt memory element have been fabricated on a flexible PI substrate with excellent characteristics using only roomtemperature processes. No significant device degradation was found in the bending state. Additionally, the impact of  $I_{RESET}$  on the programming margin of unipolar RS has been examined. The heterogeneous TiO2-HfO2 1D1R cell not only demonstrates a more stable unipolar RS than a monolithic TiO<sub>2</sub> 1D1R cell because of the lower  $I_{RESET}$  in the HfO<sub>2</sub> memory element, but also effectively suppresses the sneak current. The maximum allowed array size with an at least 10% read margin is predicted to exceed 512 kb using a simple equivalent circuit model. Therefore, the proposed 1D1R cell is extremely attractive for implementing highdensity nonvolatile memory in future low-cost flexible electronics.

**Fig. 12.** (Color online) Normalized readout margin  $\Delta V/V_{pu}$  as a function of the number of word/bit lines in an  $N \times N$  crossbar array. The maximum allowed array size with an at least 10% readout margin can be markedly increased in 1D1R arrays compared with 1R passive arrays.

#### **Acknowledgments**

This work was supported by the National Science Council of Taiwan, Republic of China, under grant NSC 97-2218-E009-039-MY3, 99RB08, and 100RB13. The authors would like to thank the Nano Facility Center at National Chiao Tung University and National Nano Device Laboratories, where the experiments in this study were performed.

- K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono: Nature 432 (2004) 488.

- 2) C. H. Cheng, F. S. Yeh, and A. Chin: Adv. Mater. 23 (2011) 902.

- N. G. Hackett, B. Hamadni, B. Dunlap, J. Suehle, C. Richter, C. Hacker, and D. Gundlach: IEEE Electron Device Lett. 30 (2009) 706.

- C. W. Hsu, J. J. Huang, Y. M. Tseng, T. H. Hou, W. H. Chang, W. Y. Jang, and C. H. Lin: Ext. Abstr. Solid State Devices and Materials, 2011, p. 1015.

- R. Waser, R. Dittmann, G. Staikov, and K. Szot: Adv. Mater. 21 (2009) 2632.

- A. Flocke and T. G. Noll: Proc. 33rd European Solid-State Circuits Conf., 2007, p. 328.

- 7) J. Liang and H. S. P. Wong: IEEE Trans. Electron Devices 57 (2010) 2531.

- 8) C. W. Kuo, J. J. Huang, W. C. Chang, and T. H. Hou: Ext. Abstr. Solid State Devices and Materials. 2010. p. 311.

- J. J. Huang, C. W. Kuo, W. C. Chang, and T. H. Hou: Appl. Phys. Lett. 96 (2010) 262901.

- 10) I. G. Baek, D. C. Kim, M. J. Lee, H.-J. Kim, E. K. Yim, M. S. Lee, J. E. Lee, S. E. Ahn, S. Seo, J. H. Lee, J. C. Park, Y. K. Cha, S. O. Park, H. S. Kim, I. K. Yoo, U.-I. Chung, J. T. Moon, and B. I. Ryu: IEDM Tech. Dig., 2005, p. 750.

- 11) M. J. Lee, Y. Park, B. S. Kang, S. E. Ahn, C. B. Lee, K. Kim, W. Xianyu, G. Stefanovich, J. H. Lee, S. J. Chung, Y. H. Jim, C. S. Lee, and J. B. Park: IEDM Tech. Dig., 2007, p. 771.

- G. Tallarida, N. Huby, B. Kutrzeba-Kotowska, S. Spiga, M. Arcari, G. Csaba, and P. Lugli: Int. Memory Workshop, 2009, p. 1.

- K. L. Lin, T. H. Hou, J. Shieh, J. H. Lin, C. T. Chou, and Y. J. Lee: J. Appl. Phys. 109 (2011) 084104.

- 14) N. Raghavan, W. Liu, X. Li, X. Wu, M. Bosman, and K. L. Pey: IEEE Electron Device Lett. 32 (2011) 455.

- 15) X. A. Tran, B. Gao, J. F. Kang, L. Wu, Z. R. Wang, Z. Fang, K. L. Pey, Y. C. Yeo, A. Y. Du, B. Y. Nguyen, M. F. Li, and H. Y. Yu: Symp. VLSI Technology, 2011, p. 44.

- 16) W. S. Chen, Y. S. Chen, Y. Y. Hsu, S. Y. Yang, W. H. Liu, H. Y. Lee, P. Y. Gu, C. H. Tsai, S. M. Wang, P. S. Chen, Y. H. Wang, F. T. Chen, and M.-J. Tsai: Symp. VLSI Technology, Systems and Applications, 2011, p. 102.

- 17) G. H. Kim, K. M. Kim, J. Y. Seok, H. J. Lee, D. Y. Cho, J. H. Han, and C. S. Hwang: Nanotechnology 21 (2010) 385202.

- 18) E. Linn, R. Rosezin, C. Kügeler, and R. Waser: Nat. Mater. 9 (2010) 403.

- J. J. Huang, Y. M. Tseng, C. W. Hsu, and T. H. Hou: IEEE Electron Device Lett. 32 (2011) 1427.