# Power-Tracking Embedded Buck–Boost Converter With Fast Dynamic Voltage Scaling for the SoC System

Yu-Huei Lee, Student Member, IEEE, Shao-Chang Huang, Shih-Wei Wang, Wei-Chan Wu, Student Member, IEEE, Ping-Ching Huang, Student Member, IEEE, Hsin-Hsin Ho, Yuan-Tai Lai, and Ke-Horng Chen, Senior Member, IEEE

Abstract—A power-tracking embedded buck—boost converter with a fast dynamic voltage scaling (F-DVS) function is proposed to power the system-on-a-chip (SoC) system. To meet the power request of the SoC for different operation functions, fast up/down-tracking is implemented to achieve the F-DVS function. Recycling energy is also derived to minimize power dissipation during the down-tracking period. In addition, the peak current control and valley current control methods are utilized in the buck and boost operations, respectively, to minimize the effect of switching noise in high switching operation for compact solution. Moreover, the self-tuning pulse skipping mechanism extends the effective duty cycle to achieve voltage regulation and improves efficiency when the input voltage is close to that of the output. Through F-DVS, the tracking speed from 3 to 2 V and vice versa are 15 and 20  $\mu s$ , respectively, with a high switching frequency of 5 MHz.

Index Terms—Buck-boost (BB) converter, dc-dc converter, dynamic voltage scaling (DVS), peak current control (PCC), power tracking, pulse skipping, system-on-a-chip (SoC), valley current control (VCC).

# I. INTRODUCTION

YSTEM-ON-A-CHIP (SoC) system is a design trend in today's consumer portable devices. Power management module is demanded to have high efficiency, low output voltage ripple, and fast transient response at the same time. To effectively power the battery-operated portable system, dc-dc converter is utilized to provide a constant output voltage over a wide input voltage range from the Li-ion battery [1]-[3]. The buck-boost (BB) converter [4]-[20] can operate in either the buck or boost operation to convert a regulated output voltage according to the input voltage condition. However, the transition between these

Manuscript received September 1, 2010; revised November 29, 2010; accepted December 13, 2010. Date of current version February 7, 2012. This work was supported by the National Science Council, Taiwan, under Grants NSC 97-2221-E-009-172 and NSC 97-2220-E-009-027. Recommended for publication by Associate Editor Y. C. Liang.

Y.-H. Lee, S.-W. Wang, H.-H. Ho, and K.-H. Chen are with the Institute of Electrical Control Engineering, National Chiao Tung University, Hsinchu, 300 Taiwan (e-mail: khchen@cn.nctu.edu.tw).

S.-C. Huang is with eMemory Technology, Hsinchu 30265, Taiwan.

W.-C. Wu and P.-C. Huang are with Richtek Technology Corporation, Hsinchu 30288, Taiwan.

Y.-T. Lai is with Material Science Center, National Tsing Hua University, Hsinchu 30013, Taiwan.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2010.2101085

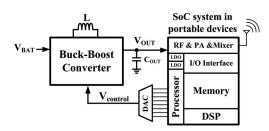

Fig. 1. System application of the PTE-BB converter for the SoC system in portable devices.

two different operations may result in large output voltage ripple due to their different operated characteristics. Thus, it is important to ensure smooth transition between the two operations in BB converter. As reported in [8], a three-mode dual-frequency two-edge modulation scheme is implemented to handle the transition when the input voltage level is close to that of output. In addition, the feedforward control scheme is utilized to improve the mode transition and the line transient response in voltage-mode BB converters [10]–[12]. The transient response should be taken into consideration owing to the diffident power requests from the distinct operation modes in the SoC system. Although a digital control scheme is proposed to enhance the transient response [13], a digital signal processing unit is needed to provide the control signals.

Fig. 1 shows the system application of the proposed powertracking embedded BB (PTE-BB) converter. To power the function blocks in the SoC system, the PTE-BB converter can automatically switch the operation modes to generate a regulated output voltage  $V_{\rm OUT}$  with different input voltage  $V_{\rm BAT}$ . For example, high-efficiency RF power amplifier is a critical part of the SoC system. The required power depends on the different operation mode, such as the demands for a large power supply to achieve data transmission [15]–[19]. In the conventional dynamic voltage scaling (DVS) design [21]-[24], the settling time for achieving output voltage position is determined by the system loop response. However, the slow voltage tracking speed deteriorates the performance of the RF circuit, since the supply power is insufficient at the beginning of the data transmission period. As a result, the proposed PTE-BB converter presents a fast DVS (F-DVS) function that can achieve fast voltage-tracking response and precise voltage position through the signal  $V_{\rm control}$ sent from the SoC system. The optimum value of  $V_{\rm control}$  is generated from the processor and converted by the digital-to-analog

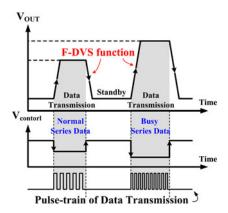

Fig. 2. Operations of the F-DVS function in the data transmission periods of the RF circuit in the SoC system.

converter (DAC) to indicate the different energy request of the SoC system to power management. Thus, high performance and high efficiency can be simultaneously achieved.

The operation of the proposed F-DVS function is shown in Fig. 2. When the data transmission period is activated, the signal  $V_{\rm control}$  starts up-tracking response in the PTE-BB converter to raise the output voltage for improving the driving capability. In addition, a larger power request is obtained by the busy series data transmission.  $V_{\rm OUT}$  is returned to its nominal value when the data transmission period is over in order to minimize the power consumption for extending the battery life. Similarly, the signal  $V_{\rm control}$  also enables the down-tracking response to meet the power demand in the standby period. Therefore, the F-DVS function of the PTE-BB converter achieves both fast voltagetracking and adjustable output voltage. Moreover, to avoid the effect of system instability resulting from the switching noise in high switching operation, the PTE-BB converter utilizes the dual-mode operation, which includes the peak current control (PCC) [25] in the buck operation and the valley current control (VCC) in the boost operation, respectively. The self-tuning pulse skipping (SPS) mechanism is also implemented to achieve the smooth mode transition in the BB converter when the value of  $V_{\rm BAT}$  is closed to that of  $V_{\rm OUT}$ .

In this paper, the structure of the proposed PTE-BB converter is described in Section II. The system operation is illustrated in Section III. Detailed circuit implantation is presented in Section IV. Experimental results are shown in Section V. Finally, the conclusion is made in Section VI.

# II. PROPOSED BB CONVERTER STRUCTURE

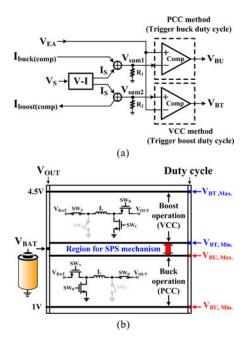

The structure of the PTE-BB converter is shown in Fig. 3. The current-mode control is utilized to achieve fast transient response, better line rejection capability, and on-chip system compensation scheme at the same time. In addition, the output voltage ripple is minimized especially for some noise-sensitive blocks, such as the RF circuits in the SoC system. Using the high switching frequency in dc-dc converter can decrease the output voltage ripple and reduces the value of off-chip inductor to further reduce the printed circuit board area.

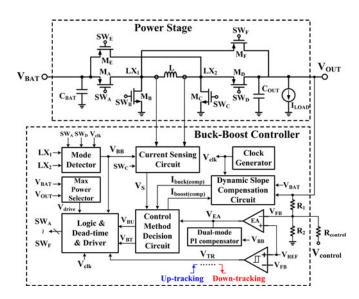

Fig. 3. Proposed structure of the PTE-BB converter with the F-DVS function.

The power stage in the PTE-BB converter contains six power switches,  $M_A$ – $M_F$ , to achieve the energy transition and the F-DVS function. The signal  $V_{\rm TR}$  generated by the hysteresis comparator enables the F-DVS function through the rising and falling edge triggers to achieve the up-tracking and downtracking of the output voltage, respectively. The resistors  $R_1$  and  $R_2$  form the voltage feedback to regulate the output voltage. The error signal  $V_{\rm EA}$  generated by a high-gain error amplifier makes a comparison with the summing signal, which is the summation of the current-sensing signal  $V_S$  and the slope compensation signal, in order to generate the control duties,  $V_{\rm BU}$  and  $V_{\rm BT}$ , for the buck and boost operations, respectively. Besides, the current-sensing circuit realizes the high-speed current sensing at the high switching operation.

The dynamic slope compensation (DSC) circuit produces the slope compensation signals,  $I_{\text{buck}(\text{comp})}$  and  $I_{\text{boost}(\text{comp})}$ , to avoid the subharmonic oscillation in the PCC or VCC methods, respectively. The mode detector circuit is used to determine the operation mode by generating the  $V_{\rm BB}$  signal in the PTE-BB converter based on the conditions between the battery and the output. The master and slave control scheme is implemented with the SPS mechanism to ensure smooth mode transition. As such, the signal  $V_{\rm BB}$  with a low value indicates the buck operation, while the boost operation is utilized when  $V_{\rm BB}$  is forced to high. Moreover, the dual-mode proportional-integral (PI) compensator [26] guarantees the on-chip compensation through the system pole-zero cancellation in the current-mode control. The clock generator carries out the system clock  $V_{\rm clk}$ with 5 MHz for high switching pulse width modulation (PWM) operation. The dead time and driver circuit, which are supplied by the supply voltage  $V_{\rm drive}$  generated through the maximum power selector, produce the control signals  $SW_A$ - $SW_F$ to drive the power switches,  $M_A$ – $M_F$ , respectively, thereby enhancing the driving ability and avoiding the shoot-through current.

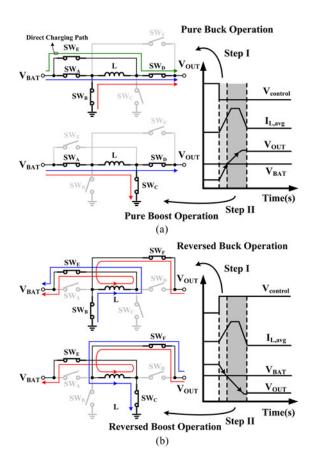

Fig. 4. F-DVS function contains fast (a) up-tracking and (b) down-tracking.

# III. SYSTEM OPERATION

## A. F-DVS Function

Fast transient response and short settling time are necessary to achieve the F-DVS function in the PTE-BB converter for the SoC system. Particularly, a high voltage supply is needed to provide better driving capability during the data transmission period. Fig. 4(a) shows the operating scheme of fast up-tracking with energy delivering path defined in the F-DVS function. The up-tracking process is divided into two steps in order to effectively control the inductor current. In step I, if  $V_{\rm BAT}$  is larger than  $V_{\rm OUT}$ , the PTE-BB converter operates in pure buck operation with a maximum charging current control. Furthermore, a direct charging path, which is composed of the power switches with  $M_E$  and  $M_D$ , is adopted to accelerate the tracking speed, especially under the condition wherein only a small voltage difference between  $V_{\rm BAT}$  and  $V_{\rm OUT}$  is derived at the beginning of the tracking response. In addition, once  $V_{\mathrm{OUT}}$  exceeds the value of  $V_{\rm BAT}$  in the up-tracking response, the control scheme ends the direct charging path and enters into step II with a pure boost operation. The operation is switched to the boost operation and uses a maximum charging current control until  $V_{\rm OUT}$ approaches the desired regulated voltage. Thus, with the twostep up-tracking procedure,  $V_{\mathrm{OUT}}$  can be raised up rapidly to meet the power request of the SoC system.

On the other hand, when the data transition ends, the system returns to the standby mode for power saving. The F-DVS

Fig. 5. Duty cycle modulation considers the noise effect in the BB converter when the value of  $V_{\rm BAT}$  is close to that of  $V_{\rm O\,U\,T}$ . (a) VCC method in the buck operation. (b) PCC method in the boost operation.

function provides a fast down-tracking scheme as shown in Fig. 4(b). The down-tracking process is also divided into two steps to effectively achieve voltage tracking. The PTE-BB converter operates the reversed buck operation in step I to transfer the excessive energy back to the input through inductor when  $V_{\rm OUT}$  is larger than  $V_{\rm BAT}$ , achieving a fast down-tracking response and the minimized power dissipation. Moreover, step II is activated when  $V_{\rm OUT}$  is lower than the value of  $V_{\rm BAT}$  that the PTE-BB converter can deliver the energy from  $C_{\rm OUT}$  to battery through the maximum charging current control. Finally, step II ends until the value of  $V_{\rm OUT}$  is close to the desired value. The power dissipation is minimized because of the recycled energy procedure during the down-tracking period. Therefore, the proposed PTE-BB converter simultaneously improves the voltage-tracking speed while extending the battery life.

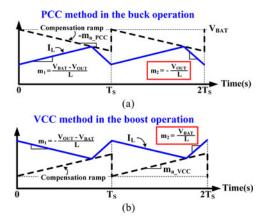

# B. PCC and VCC Methods for PTE-BB Converter

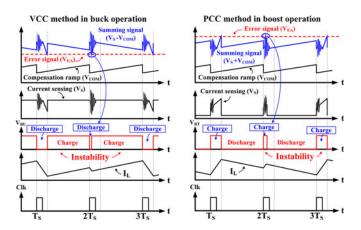

In the design of BB converter, it is difficult to maintain a low output voltage ripple when the value of  $V_{\rm OUT}$  is close to that of  $V_{\rm BAT}$ . If  $V_{\rm BAT}$  is a little larger than  $V_{\rm OUT}$ , the duty cycle of the buck operation would approaches nearly 100%, which is difficult to guarantee through the system control scheme because of the interference in duty modulation generated from the switching noise and the driver delay. Similarly, the duty cycle in the boost operation is also hard to approaches 0% when the value of  $V_{\rm BAT}$  is a little smaller than that of  $V_{\rm OUT}$ .

The current-sensing method in the current-mode control includes the PCC and VCC methods. If the VCC method is considered as the modulation method in the buck operation, the switching noise would have a serious influence on the duty modulation when  $V_{\rm BAT}$  and  $V_{\rm OUT}$  are nearly equal. Fig. 5(a) shows the instability caused by the switching noise effect in the buck operation with the VCC method, which leads to the increase of output voltage ripple. With the VCC method, the inductor starts to discharge through the positive trigger of the system clock  $V_{\rm clk}$ . The switching noise results in the instability due to the short inductor discharging period, which is limited by the large duty cycle. The large output ripple worsens the supply quality

Fig. 6. (a) Control method decision circuit. (b) Indication of the PCC method, VCC method, and SPS mechanism with different input/output voltage conditions.

of the BB converter. In commercial products, the blanking time used in the current-sensing circuit can prevent the interference with the undesired switching noise, but it induces a minimum value for the duty cycle. This means that the blanking time restricts the BB converter to extend the duty cycle once the value of  $V_{\rm BAT}$  is close to that of  $V_{\rm OUT}$ . As a result, the PCC method is more suitable than the VCC method in the buck operation.

As  $V_{\rm BAT}$  decreases, the operation changes from the buck operation to the boost operation when  $V_{\rm BAT}$  becomes smaller than  $V_{\rm OUT}$ . Thus, the duty cycle is reset from 100% to 0%. Fig. 5(b) shows the PCC method used in the boost operation. The switching noise causes system instability due to the short inductor charging period. The blanking time technique is also applied to solve the instability issue caused by the switching noise in high switching operation. However, it fails to work correctly once the duty cycle approaches 0%, indicating that the VCC method must be adopted in the boost operation.

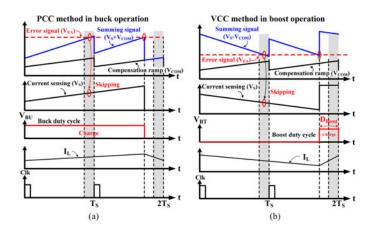

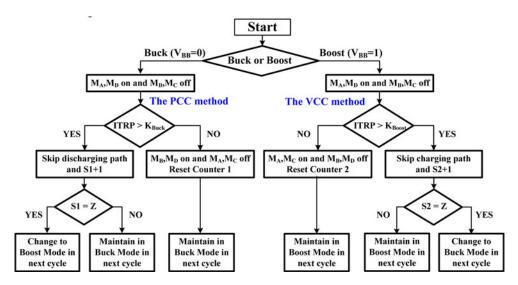

### C. Control Method Decision and SPS Mechanism

The BB converter aims to work properly with a small voltage difference between  $V_{\rm BAT}$  and  $V_{\rm OUT}$ . Nevertheless, the selection of either the PCC or VCC modulation methods determines the stability of BB converter shown in Fig. 5. The settling time of the voltage-tracking response may be extended due to the improper control method when the desired regulated voltage is set near  $V_{\rm BAT}$  that deteriorates the performance of SoC systems. Thus, the proposed PTE-BB converter combines both the PCC and VCC methods in the buck and boost operations, respectively, to derive a stable operation in the wide input voltage range as well as a small output voltage ripple.

The control method decision circuit shown in Fig. 6(a) modulates the duty cycle from the error signal  $V_{\rm EA}$ , the sensing signal

Fig. 7. Proposed PTE-BB converter uses the SPS mechanism. (a) PCC method in the buck operation. (b) VCC method in the boost operation.

$V_S$ , and the slope compensation signal  $V_{\rm COM}$ .  $V_{\rm COM}$  is derived from the compensation currents,  $I_{\rm bcuk(comp)}$  and  $I_{\rm boost(comp)}$ , in the buck and boost operations, respectively, to prevent subharmonic oscillation. Consequently,  $V_{\rm BU}$  and  $V_{\rm BT}$  can be used to trigger the buck and boost operations, respectively. As shown in Fig. 6(b), the PCC method operates in the buck operation because the VCC method suffers from the problem of having a short inductor discharging period if the value of  $V_{\rm BAT}$  is close to that of  $V_{\rm OUT}$ . Moreover, utilizing the VCC method in the boost operation is a better choice since the PCC method has a short inductor charging period when the low-duty cycle issue occurs.

The SPS mechanism depicted in Fig. 7 is utilized to extend the effective duty cycle, and thereby improving the regulation performance, minimizing the output voltage ripple, as well as eliminating the random transition between the two operations when the value of  $V_{\rm BAT}$  is close to that of  $V_{\rm OUT}$ . As a result, the power conversion efficiency can be enhanced. The PCC method in buck operation shown in Fig. 7(a) defines a 10% duty cycle at the end of a PWM switching cycle. When  $V_{\mathrm{BAT}}$  decreases to reach  $V_{\rm OUT}$  with an increasing duty cycle, the switching would be bypassed by means of prohibiting the inductor discharge period in order to extend the duty cycle. Therefore, the effective duty cycle is stretched so as to ensure the summing signal intersecting with the signal  $V_{\rm EA}$  within the period of the 90% duty cycle at the next PWM switching cycle. It can alleviate the instability of the BB converter and the switching noise derived from the power stage. Similarly, as shown in Fig. 7(b), the VCC method in the boost operation is achieved with the SPS mechanism to regulate the output voltage if  $V_{\rm BAT}$  continuously decreases to become much smaller than  $V_{\mathrm{OUT}}$ . The effective duty cycle can be extended to overcome the challenge of low-duty condition. In addition, the mode transition would occur if the continuous counting of the skip number exceeds an auxiliary value, leading to the achievement of the optimal transition boundary in the proposed PTE-BB converter. The blanking time is also used in the current-sensing procedure to abate the effect resulted from the switching noise; this is because the SPS mechanism can extend the effective duty cycle in the PTE-BB converter. Given that the reduction of the switching period can also improve the power conversion efficiency and guarantees the voltage regulation at the same time.

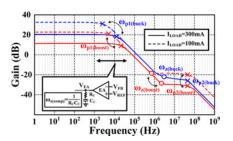

### D. System Compensation in the PTE-BB Converter

The current-mode PTE-BB converter can be achieved using both the PCC and VCC methods. However, the system loop compensation network must be adjusted according to the distinct control methods. The control-to-output transfer function [27] of the PCC method in the buck operation  $T_{\text{buck}}$  is expressed as, as shown (1), at the bottom of this page, where  $G_{\text{buck}}$  is the loop gain,  $M_{\text{buck}}$  is the inductor current slope, and  $M_{\text{comp\_buck}}$ is the slope compensation signal. The current-mode control can separate the complex poles generated by the off-chip inductor and capacitor at power stage so as to derive only a single lowfrequency pole  $\omega_{p1(\text{buck})}$ , which is load-dependent and inversely proportional to the output load resistance  $R_{LOAD}$  and the output capacitor  $C_{\rm OUT}$ . The first nondominant pole  $\omega_{p2({\rm buck})}$  is located near to the switching frequency because of the current-mode control. The utilization of the slope compensation can determine the location of  $\omega_{p2(\mathrm{buck})}$ . The equivalent series resistance (ESR) on the output capacitor also contributes a left-half plane (LHP) zero  $\omega_{z(\text{buck})}$ . The expressions of  $\omega_{p1(\text{buck})}$ ,  $\omega_{p2(\text{buck})}$ , and  $\omega_{z\,(\mathrm{buck})}$  are expressed in (2). As a result, the PI compensator can be adopted to compensate the system in the PCC method buck operation:

$$\omega_{p1(\text{buck})} = \frac{1}{C_{\text{OUT}}R_{\text{LOAD}}}$$

$$\omega_{p2(\text{buck})} = \frac{M_{\text{buck}}}{(M_{\text{buck}} + M_{\text{comp\_buck}})D_{\text{buck}}T}$$

$$\omega_{z(\text{buck})} = \frac{1}{R_{\text{ESR}}C_{\text{OUT}}}.$$

(2)

In addition, the control-to-output transfer function of the VCC method in the boost operation  $T_{\rm boost}$  is expressed as, as shown (3), at the bottom of this page, where  $G_{\rm boost}$  is the loop gain.  $M_{\rm boost}$  and  $M_{\rm comp\_boost}$  are the inductor current slope and the slope compensation signal, respectively. Similarly, the current-mode control in the boost operation generates a load-dependent pole  $\omega_{p1({\rm boost})}$  and a nondominant pole  $\omega_{p2({\rm boost})}$  that are affected by the slope compensation. However, a right-half plane (RHP) zero is derived at the power stage in the boost opera-

Fig. 8. Frequency response of the proposed PTE-BB converter with both the buck and boost operations under different load conditions.

tion, which deteriorates the system phase margin. However, it can be moved from RHP to LHP if the ESR on the output capacitor is carefully selected. Nevertheless, a large ESR, which may increase the output voltage ripple, is not suitable for SoC applications. Hence, a high-frequency RHP zero exists in the boost operation of the PTE-BB converter because the interference on the system bandwidth is alleviated by using the small off-chip inductor with high switching operation. The respective expressions of  $\omega_{p1(\mathrm{boost})}$ ,  $\omega_{p2(\mathrm{boost})}$ , and  $\omega_{z(\mathrm{boost})}$  are shown as follows:

$$\omega_{p1(\text{boost})} = \frac{2}{C_{\text{OUT}} R_{\text{LOAD}}}$$

$$\omega_{p2(\text{boost})} = \frac{M_{\text{boost}}}{(M_{\text{boost}} + M_{\text{comp\_boost}}) D_{\text{boost}} T}$$

$$\omega_{z(\text{boost})} = \frac{1}{(C_{\text{OUT}} R_{\text{ESR}} / (1 - D_{\text{boost}})) - (L / (1 - D_{\text{boost}}) R_{\text{LOAD}})}.$$

(4)

The control-to-output frequency responses of the PTE-BB converter with the PCC method in buck operation and the VCC method in boost operation are shown in Fig. 8. The proposed dual-mode PI compensator can be used to achieve system compensation to ensure a large system bandwidth and an adequate phase margin.

$$T_{\text{buck}}(s) = G_{\text{buck}}(s) \frac{1 + sR_{\text{ESR}}C_{\text{OUT}}}{(1 + sC_{\text{OUT}}R_{\text{LOAD}}) (1 + s(M_{\text{buck}} + M_{\text{comp\_buck}})D_{\text{buck}}T/M_{\text{buck}})}$$

$$= G_{\text{buck}}(s) \frac{1 + (s/\omega_{z(\text{buck})})}{(1 + (s/\omega_{p1(\text{buck})})) (1 + (s/\omega_{p2(\text{buck})}))}$$

(1)

$$T_{\text{boost}}(s) = G_{\text{boost}}(s) \frac{1 + s \left( C_{\text{OUT}} R_{\text{ESR}} / (1 - D_{\text{boost}}) - L / (1 - D_{\text{boost}}) R_{\text{LOAD}} \right)}{\left( 1 + s \left( C_{\text{OUT}} R_{\text{LOAD}} / 2 \right) \right) \left( 1 + s \left( M_{\text{boost}} + M_{\text{comp\_boost}} \right) D_{\text{boost}} T / M_{\text{boost}} \right)}$$

$$= G_{\text{boost}}(s) \frac{1 + s / \omega_{z(\text{boost})}}{\left( 1 + \left( s / \omega_{p1(\text{boost})} \right) \right) \left( 1 + \left( s / \omega_{p2(\text{boost})} \right) \right)}$$

(3)

Fig. 9. Slope compensation (a) in the buck operation with the PCC method and (b) in the boost operation with the VCC method.

Fig. 10. Schematic of the DSC circuit.

### IV. CIRCUIT IMPLEMENTATION

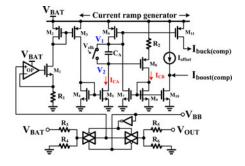

# A. DSC Circuit

Slope compensation is required to prevent subharmonic oscillation, and thereby ensuring system stability when the duty cycle in the current-mode control is larger than 50%. To compensate for the PCC and VCC methods in the buck and boost operations, respectively, two distinct slope compensation signals were utilized in the proposed PTE-BB converter. The slope compensation schemes for the PCC and VCC methods are shown in Fig. 9(a) and (b), respectively. The slope compensation coefficient  $m_{a \perp PCC}$  for the PCC method must be proportional to  $V_{\rm OUT}$  in the buck operation. On the other hand,  $V_{\rm BAT}$  is proportional to the slope compensation coefficient  $m_{a\_VCC}$  for the VCC method in the boost operation. As a result, the proposed DSC circuit can generate the slope compensation coefficient, which is adjusted by the  $V_{\rm BAT}$  and  $V_{\rm OUT}$  for the PCC and VCC methods, respectively. It can minimize the interference on the bandwidth of the current loop resulted from the variations of  $V_{\rm BAT}$ ,  $V_{\rm OUT}$ , or the switching noise.

Fig. 10 shows the DSC circuit, which generates the slope compensation signal according to the different operation modes. The voltage-to-current (V-I) converter consisting of the operational amplifier  $M_1$  and the resistor  $R_1$  converts the current  $I_{\rm CA}$  using  $V_{\rm OUT}$  and  $V_{\rm BAT}$  in the PCC method of the buck operation and the VCC method of the boost operation, respectively.  $V_{\rm clk}$  resets the charge on the capacitor  $C_A$  when it is set to high at the beginning of every switching cycle. When  $V_{\rm clk}$  is set to

Fig. 11. Schematic of the mode detector circuit with the SPS mechanism.

low,  $I_{\rm CA}$  starts to charge the capacitor  $C_A$ , which carries out a sawtooth waveform at node  $V_2$ . The voltage across the capacitor  $C_A$  is approximately equal to the voltage across the resistor  $R_2$  since the source–gate voltages of  $M_6$  and  $M_8$  are approximately equal. Hence, the MOSFET  $M_8$  and the resistor  $R_2$  form another  $V\!-\!I$  converter to generate a sawtooth current  $I_{\rm CB}$ . In the PCC method of the buck operation, the slope compensation signal  $I_{\rm buck(comp)}$  is derived from the current mirror structure  $I_{\rm CB}$  which is proportional to  $V_{\rm OUT}$  owing to the wide range duty cycle, as follows:

$$I_{\text{buck(comp)}} = I_{\text{CB}} = \frac{R_6}{(R_5 + R_6)} \cdot \frac{V_{\text{OUT}} \cdot \Delta t}{R_1 \cdot R_2 \cdot C_A}.$$

(5)

Similarly, to achieve the system slope compensation,  $I_{\rm CA}$  must be proportional to  $V_{\rm BAT}$  in the VCC method of the boost operation. Thus, the slope compensation signal  $I_{\rm boost(comp)}$  is derived as

$$I_{\text{boost(comp)}} = I_{\text{offset}} - \frac{R_4}{(R_3 + R_4)} \cdot \frac{V_{\text{BAT}} \cdot \Delta t}{R_1 \cdot R_2 \cdot C_A}.$$

(6)

In addition, as  $I_{\rm CA}$  increases, the voltage  $V_2$  decreases due to the discharge of capacitor  $C_A$ . Thus, the compensation currents,  $I_{\rm buck(comp)}$  and  $I_{\rm boost(comp)}$ , would increase and decrease, respectively, so as to dynamically adjust the slope compensation signal to improve the system response.

However, at the moment of transition between the buck and boost operations, the output voltage ripple may be increased because of the different operation modes. The slope compensation signal is added to the current-sensing signal in the PCC method, but is subtracted to the current-sensing signal in the VCC method owing to the opposite duty modulation scheme in order to achieve a stable current-mode operation. Thus, a voltage gap is realized, in which the summing signal becomes discontinuous and causes an abnormal operation and large output voltage ripple at the mode transition point. To achieve a smooth mode transition, the offset current  $I_{\rm offset}$ , as defined in (7), is

Fig. 12. Flow chart of the SPS mechanism in the proposed PTE-BB converter.

introduced to reduce the output voltage variation [28].  $I_{\rm offset}$  depends on the input and output voltages, which is adopted in the DSC circuit. The summing coefficients,  $k_1$  and  $k_2$ , are proportional to  $V_{\rm OUT}$  and  $V_{\rm BAT}$ , respectively:

$$I_{\text{offset}} = k_1 V_{\text{OUT}} + k_2 V_{\text{BAT}} = \frac{R_6}{(R_5 + R_6)} \cdot \frac{V_{\text{OUT}}}{R_1} + \frac{R_4}{(R_3 + R_4)} \cdot \frac{V_{\text{BAT}}}{R_1}.$$

(7)

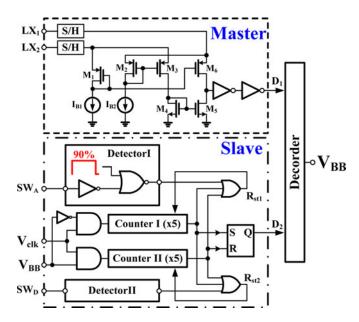

# B. Mode Detector Circuit

The mode detector circuit with the SPS mechanism shown in Fig. 11 is implemented to determine either the buck or the boost operation according to the relationship between  $V_{\rm BAT}$  and  $V_{\rm OUT}$ . To achieve an accurate mode transition between the two operations over a wide load range for minimizing output voltage ripple, the on-resistance  $R_{\rm SW}$  of each power MOSFET must be considered. Consequently, the theoretical boundary condition of the mode transition is depicted in

$$V_{\text{BAT}} - 2(I_{\text{load}} \times R_{\text{SW}}) = V_{\text{OUT}}, \quad \text{if } LX_1 = LX_2. \quad (8)$$

The operation of the mode transition is divided into the master and the slave controls. The master control works when  $V_{\rm BAT}$  and  $V_{\rm OUT}$  differ significantly from each other, operating with the simultaneous on state of power switches, A and D, and deciding the operation mode by comparing  $LX_1$  and  $LX_2$  directly. The two pairs of common-gate amplifiers form a comparator that realizes a push–pull stage at its output node in order to enhance the transient speed.

The slave controller consists of two counters and logic gates to improve the transition accuracy through the pulse-skip function when the value of  $V_{\rm BAT}$  is extremely close to that of  $V_{\rm OUT}$ . Unlike some prior arts including the BB mode as a buffer operation for smooth mode transition, the proposed SPS mechanism can skip energy paths automatically to extend the effective duty cycle to overcome the boundary condition in the BB converter over a wide voltage range.

In the buck operation, a pulse signal defined as 90% of the whole PWM duty cycle is triggered by the system clock  $V_{\rm clk}$ . Counter I calculates the number of skipping pulses to determine the mode transition for power saving. Detector I would output a reset pulse signal, which is derived from the NOR operation of the control signal SW<sub>A</sub> and the 90% duty cycle when the buck duty cycle exceeds the effective value to enable Counter I to prepare for mode transition. As a result, the PTE-BB converter switches from the buck operation to the boost operation when the number of skipping pulses exceeds the designed value. Similarly, the operation in the boost operation is also controlled by the same mechanism controlled by the Detector II and Counter II. It can also ensure the smooth mode transition when the value of  $V_{\rm BAT}$ is extremely close to that of  $V_{\rm OUT}$ . The flow chart of the SPS mechanism is depicted in Fig. 12. The variable ITRP represents the interconnection of the error signal and the summing signal. The 90% duty cycle in the PCC method of the buck operation and the VCC method of the boost operation are represented by  $K_{\rm Buck}$ and  $K_{\text{Boost}}$ , respectively. The variable Z is the designed value in the counter that determines the activity of mode transition between the buck and the boost operations.

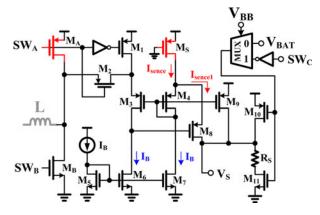

# C. Current-Sensing Circuit

A simple way of current sensing is achieved by inserting the sensing resistor into the series of the inductor current path. However, the efficiency is seriously deteriorated at the heavy load conditions. The proposed current-sensing circuit depicted in Fig. 13 can reduce unnecessary power loss without using power-dissipated sensing resistor.

The transistor  $M_S$  produces the sensing current  $I_{\rm sense}$  during the turn-on period of the power switch  $M_A$ . The source-to-drain voltages of  $M_A$  and  $M_S$  are approximately equal because of the implementation of the common-gate amplifier, which is composed of  $M_3$ – $M_7$ .  $M_1$  is ON and  $M_2$  is OFF during the turned-on period of  $M_A$ . Bias current  $I_B$  results in the current difference between the sensing currents,  $I_{\rm sense}$  and  $I_{\rm sense1}$ . To enhance the current-sensing accuracy, transistor  $M_9$ , which has the same

Fig. 13. Schematic of the current-sensing circuit.

Fig. 14. Dual-mode PI compensator.

aspect ratio as the current mirror structure of  $M_3$  and  $M_4$ , is added to provide a compensative current  $I_B$ . Consequently, the current-sensing signal is produced by the voltage signal  $V_S$  across the resistor  $R_1$ . On the other hand,  $V_S$  would be reset to  $V_{\rm BAT}$  by the multiplexer and the MOSFETs  $M_{10}$  and  $M_{11}$  at the charging period of the boost operation to achieve the VCC method.

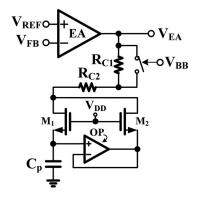

# D. Dual-Mode PI Compensator

As shown in Fig. 14, the proposed internal dual-mode PI compensator can maintain a stable closed-loop response in both the buck and boost operations compared with a conventional PI compensator [26]. The capacitor multiplier technique utilized to on-chip compensation achieves with only a small capacitor  $C_p$  that reduces the silicon area [29]. It generates the system dominant pole to ensure stability in both the buck and boost operations. In addition, when the PTE-BB converter operates in the PCC method of the buck operation, the switch is turned off to generate a low-frequency compensation zero to cancel the effect of the system pole  $\omega_{p1(\text{buck})}$ . Aside from this, the system load dependent pole in the boost operation  $\omega_{n1(\text{boost})}$ moves to higher frequencies compared with the buck operation under the same output load condition. The  $V_{\rm BB}$  signal forces the switch on in order to reduce the compensation resistance at the PI compensator. This means that the compensation zero in the boost operation is tracked to the higher frequencies in order to achieve the pole-zero cancellation for improving system stability. Thus,

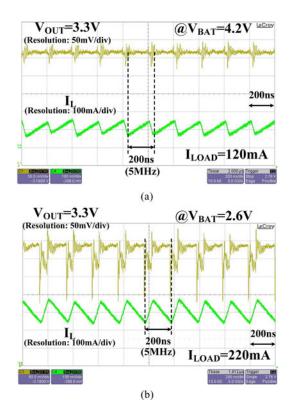

Fig. 15. Measured steady-state operation of the PTE-BB converter. (a) Buck operation with load current of 120 mA when  $V_{\rm BAT}=4.2$  V and  $V_{\rm OUT}=3.3$  V. (b) Boost operation with load current of 220 mA when  $V_{\rm BAT}=2.6$  V and  $V_{\rm OUT}=3.3$  V.

in both the buck and boost operations, the proposed dual-mode PI compensator carries out the same crossover frequency to achieve better performance even at the mode transient period.

## V. EXPERIMENTAL RESULTS

The proposed PTE-BB converter with F-DVS function was fabricated by 0.25- $\mu$ m CMOS process. Supply voltage  $V_{\rm BAT}$ is set in the range of 2.5-4.5 V defined by the range of Li-ion battery. The typical output voltage is 3.3 V, regulated by the switching frequency of 5 MHz so that the off-chip inductor and capacitor can be utilized with 1  $\mu$ H and 0.88  $\mu$ F, respectively. The small-size off-chip output filter can minimize the volume of the power module in portable devices. Fig. 15 shows the steadystate operation of the proposed PTE-BB converter. The regulated output voltage of 3.3 V under 4.2 V input voltage supply with a 120-mA load current is shown in Fig. 15(a). The switching frequency is kept at 5 MHz with a duty cycle of 78%. The boost operation is demonstrated in Fig. 15(b) with a regulated output voltage of 3.3 V under input voltage of 2.6 V. With duty cycle of 21% and 220-mA load current, the 5-MHz high switching operation is achieved.

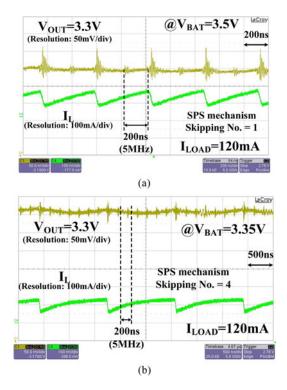

Fig. 16 shows the SPS mechanism in the buck operation with the PCC method. When  $V_{\rm BAT}$  is close to  $V_{\rm OUT}$  in the PTE-BB converter, the SPS mechanism can ensure the smooth transition response and avoid system instability resulting from high switching noise. When  $V_{\rm BAT}$  is lowered to 3.5 V with a fixed  $V_{\rm OUT}$  of 3.3 V as shown in Fig. 16(a), the SPS mechanism

Fig. 16. Measured SPS mechanism in the buck operation with load current of 120 mA. (a) If  $V_{\rm BAT}=3.5$  V and  $V_{\rm OUT}=3.3$  V, the skipping number is 1. (b) If  $V_{\rm BAT}=3.35$  V and  $V_{\rm OUT}=3.3$  V, the skipping number is 4.

is activated to skip the switching numbers at the power stage in order to extend the effective duty cycle. At this time, the PTE-BB converter operates in the transition region from the buck operation to the boost operation. Similarly, if the  $V_{\rm BAT}$  further decreases to 3.35 V as shown in Fig. 16(b), the number of the skip operation is increased during every effective switching cycle. Thus, the stable operation of the proposed high switching PTE-BB converter is guaranteed, and an adequate duty cycle is derived when the value of  $V_{\rm BAT}$  is close to that of  $V_{\rm OUT}$ .

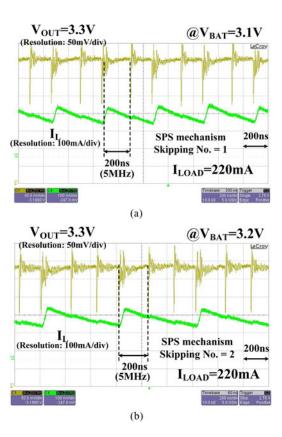

Fig. 17 shows the SPS mechanism in the boost operation with the VCC method. The switching number is decreased when the PTE-BB converter enters the transition region from the boost operation to the buck operation. The smaller voltage difference between  $V_{\rm BAT}$  and  $V_{\rm OUT}$  is derived, the more skipping number of the SPS mechanism is achieved. The equivalent duty cycle can yield the correct operation for the high switching PTE-BB converter. If the skipping number exceeds the defined value in the mode detector circuit, the operation mode can be switched from the boost operation to the buck operation in order to achieve a smooth transition response and enhance efficiency.

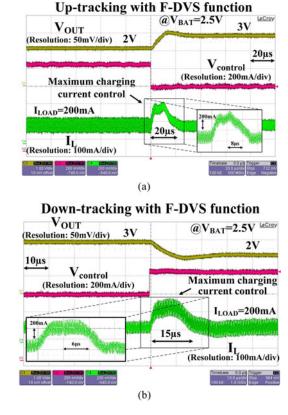

Fig. 18 shows the F-DVS function for the SoC system. The uptracking response shown in Fig. 18(a) demonstrates that  $V_{\rm OUT}$  arises from 2 to 3 V with the settling time of 20  $\mu$ s. The signal  $V_{\rm control}$ , which is generated by the DAC according to the demand from processor in the SoC, activates the tracking response for F-DVS function. The maximum charging current control works in both pure buck and boost operations. It helps regulate the inductor peak current and avoid the overcharge at the up-tracking response. Fig. 18(b) shows the down-tracking response when

Fig. 17. Measured SPS mechanism in the boost operation with load current of 220 mA. (a) If  $V_{\rm BAT}=3.1~{\rm V}$  and  $V_{\rm OUT}=3.3~{\rm V}$ , the skipping number is 1. (b) If  $V_{\rm BAT}=3.2~{\rm V}$  and  $V_{\rm OUT}=3.3~{\rm V}$ , the skipping number is 2.

Fig. 18. Measured F-DVS function. (a) Up-tracking response. (b) Downtracking response.

| Technology                              | 0.25 μm CMOS process                  |  |  |

|-----------------------------------------|---------------------------------------|--|--|

| Inductor / DCR                          | 1 μH / 100 mΩ (nominal)               |  |  |

| Capacitor / ESR                         | $0.88  \mu F / 50  m\Omega$ (nominal) |  |  |

| Switching frequency                     | 5 MHz                                 |  |  |

| Input voltage (V <sub>BAT</sub> )       | 2.5 V – 4.5 V                         |  |  |

| Output voltage (V <sub>OUT</sub> )      | 2 V – 4 V                             |  |  |

| Load current range (I <sub>LOAD</sub> ) | 100 mA – 400 mA                       |  |  |

| Up-tracking (from 2 V to 3 V)           | 20 μs                                 |  |  |

| Down-tracking (from 3 V to 2 V)         | 15 μs                                 |  |  |

| Power conversion efficiency             | Max. 91 %                             |  |  |

| Chip size                               | $4.86 \text{ mm}^2$                   |  |  |

TABLE I

DESIGN SPECIFICATIONS OF THE PROPOSED PTE-BB CONVERTER

TABLE II

COMPARISON OF THE PREVIOUS BB CONVERTER METHODOLOGIES

|                     | This work            | [1]                 | [10]                 | [14]                |

|---------------------|----------------------|---------------------|----------------------|---------------------|

| Technology          | 0.25 μm CMOS         | Discrete components | 0.25 μm CMOS         | 0.35 μm CMOS        |

| Control scheme      | Current-mode         | Voltage-mode        | Voltage-mode         | Tri-mode            |

| Inductor            | 1 μΗ                 | 2.2 μΗ              | 4.7 μΗ               | 10 μΗ               |

| Capacitor           | 0.88 μF              | 47 μΗ               | 47 μΗ                | 10 μΗ               |

| Switching frequency | 5 MHz                | 500 kHz             | 700 kHz              | 250 kHz*            |

| Input voltage       | 2.5 V – 4.5 V        | 2.4 V – 3.4 V       | 2.7 V – 4.5 V        | 1.6 V – 3.3 V       |

| Output voltage      | 2 V – 4 V            | 0.4 V – 4 V         | 3.3 V (nominal)      | 0.9 V - 3 V         |

| Max. load current   | 400 mA               | 800 mA              | 500 mA               | 800 mA              |

| Up-tracking         | 20 μs/V              | N / A               | N/A                  | 150 μs/V            |

| Down-tracking       | 15 μs/V              | N/A                 | N/A                  | 37 μs/V             |

| Peak efficiency     | 91 %                 | 62 %                | 96 %                 | 96.5 %              |

| Chip size           | 4.86 mm <sup>2</sup> | N / A               | 3.14 mm <sup>2</sup> | 1.3 mm <sup>2</sup> |

<sup>\*</sup> Switching frequency would vary according to the inductor current  $i_L$  in tri-mode control.

$V_{\rm OUT}$  decreases from 3 to 2 V with a settling time of 15  $\mu s$ . The measured inductor current waveform indicates the work of reversed buck and boost operations to accelerate the tracking response. Additionally, the recycled energy procedure during the down-tracking period minimizes the power dissipation in the proposed PTE-BB converter.

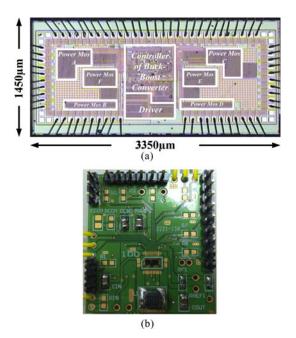

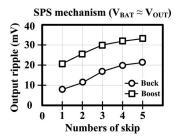

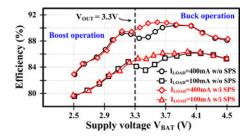

Fig. 19 shows the chip micrograph and the prototype of the proposed PTE-BB converter. The occupied silicon area is about 4.86 mm<sup>2</sup> owing to the use of six power switches to achieve the F-DVS operation for the SoC system. Fig. 20 shows the measured output voltage ripple with different skipping numbers when the value of  $V_{\rm BAT}$  is close to that of  $V_{\rm OUT}$ . The maximum skip number in the SPS mechanism is five in the proposed design. The output ripple in both the buck and boost operations is derived below the allowable value for improving the performance of the SoC system. Fig. 21 shows the power conversion efficiency with a peak value of 91%. The SPS mechanism skips the switching cycle in the mode transition period to extend the equivalent duty cycle, and thereby enhancing the power conversion efficiency. When  $V_{\mathrm{BAT}}$  is very close to  $V_{\mathrm{OUT}}$ , the SPS mechanism can even achieve an almost direct conduction from  $V_{\mathrm{BAT}}$  to  $V_{\mathrm{OUT}}$ . Thus, the switching number of power stage is reduced that the peak efficiency can be derived shown in Fig. 21. However, owing to the nonideal power loss, such as the conduction loss, in power stage, the actual mode transition point between the buck and the boost modes would become larger than that of the ideal value. Therefore, the measured peak efficiency of the proposed

Fig. 19. (a) Chip micrograph. (b) Prototype of the proposed PTE-BB converter.

PTE-BB converter with  $V_{\rm OUT}=3.3\,\rm V$  is derived at  $V_{\rm BAT}=3.6\,\rm V$ , rather than that at  $V_{\rm BAT}=3.3\,\rm V$ . The detailed design specifications are listed in Table I. Moreover, the comparisons of the prior BB converters are shown in Table II. The proposed

Fig. 20. Measured output voltage ripple with different skipping numbers in SPS mechanism.

Fig. 21. Measured power conversion efficiency of the proposed PTE-BB converter.

PTE-BB converter with the current-mode control can achieve the F-DVS operation, which is suitable for the SoC system.

### VI. CONCLUSION

The proposed high switching current-mode PTE-BB converter with F-DVS function was fabricated by 0.25- $\mu$ m CMOS process. To effectively power the SoC system, the F-DVS function rapidly adjusts the output voltage value to meet the different power request. In addition, when a small voltage difference exists in  $V_{\rm BAT}$  and  $V_{\rm OUT}$ , the utilization of the PCC and VCC methods in the buck and boost operations, respectively, can eliminate the system instability caused by switching noise to ensure a stable voltage regulation. Moreover, compared with the traditional method, the SPS mechanism helps to extend the effective duty cycle using pulse skipping to obtain a regulated output voltage in mode transition and enhance power conversion efficiency. The DSC circuit and the dual-mode PI compensator are proposed to stabilize the system in both buck and boost operations. The fast-tracking response and the recycling energy are achieved in the F-DVS function with a switching frequency of 5 MHz.

# ACKNOWLEDGMENT

The authors would like to thank Richtek Technology Corporation and Chunghwa Picture Tubes, Ltd., for their help.

### REFERENCES

- [1] B. Sahu and G. A. R. -Mora, "A low voltage, dynamic, non-inverting, synchronous buck-boost converter for portable applications," *IEEE Trans. Power Electron.*, vol. 19, no. 2, pp. 443–452, Mar. 2004.

- [2] S. Zhou and G. A. R. -Mora, "A high efficiency, soft switching DC–DC converter with adaptive current-ripple control for portable applications," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 53, no. 4, pp. 319–323, Apr. 2006.

- [3] W. R. Liou, M. L. Yeh, and Y. L. Kuo, "A high efficiency dual-mode buck converter IC for portable applications," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 667–677, Mar. 2008.

- [4] Datasheet "TPS63000: High Efficient Single Inductor Buck-Boost Converter with 1.8A Switches," Texas Instruments, 2008.

- [5] Datasheet "LTC3440: Micropower synchronous buck-boost DC/DC converter," Linear Technol. Corp., 2001.

- [6] Datasheet "LTC3454: 1A Synchronous Buck-boost High Current LED Driver," Linear Technol. Corp., 2005.

- [7] P. Midya, K. Haddad, and M. Miller, "Buck or boost tracking power converter," *IEEE Trans. Power Electron. Lett.*, vol. 2, no. 4, pp. 131–134, Dec. 2004.

- [8] X. Ren, X. Ruan, H. Qian, M. Li, and Q. Chen, "Three-mode dual-frequency two-edge modulation scheme for four-switch buck-boost converter," *IEEE Trans. Power Electron.*, vol. 24, no. 2, pp. 499–509, Feb. 2009.

- [9] J. Chen, D. Maksimovic, and R. W. Erickson, "Buck-boost PWM converters having two independently controlled switches," in *Proc. IEEE Power Electron. Spec. Conf. (PESC)*, 2001, pp. 17–21.

- [10] P.-C. Huang, W.-Q. Wu, H.-H. Ho, and K.-H. Chen, "Hybrid buck-boost feedforward and reduced average inductor current technique in fast line transient and high-efficiency buck-boost converter," *IEEE Trans. Power Electron.*, vol. 25, no. 3, pp. 719–730, Mar. 2010.

- [11] H.-J. Yang, K.-H. Chen, and Y.-P. Lee, "Feed-forward pulse width modulation for high line regulation buck or boost converter," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 2007, pp. 785–788.

- [12] B. Arbetter and D. Maksimovic, "Feed-forward pulse-width modulators for switching power converters," in *Proc. IEEE Power Electron. Spec. Conf. (PESC)*, 1995, pp. 601–607.

- [13] Y.-J. Lee, A. Khaligh, A. Chakraborty, and A. Emadi, "Digital combination of buck and boost converters to control a positive buck-boost converter and improve the output transients," *IEEE Trans. Power Electron.*, vol. 24, no. 5, pp. 1267–1279, May 2009.

- [14] F. Luo and D. Ma, "Design of digital tri-mode adaptive-output buck-boost power converter for power-efficient integrated systems," *IEEE Trans. Ind. Electron.*, vol. 57, no. 6, pp. 2151–2160, Jun. 2010.

- [15] B. Sahu and G. A. R. -Mora, "A high efficiency WCDMA RF power amplifier with adaptive dual mode buck-boost supply and bias-current control," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 3, pp. 238– 240. Mar. 2007.

- [16] J. N. Kitchen, C. Chu, S. Kiaei, and B. Bakkaloglu, "Combined linear and Δ-modulated switch-mode PA supply modulator for polar transmitters," *IEEE J. Solid State Circuits*, vol. 44, no. 2, pp. 404–413, Feb. 2009.

- [17] W.-Y. Chu, B. Bakkaloglu, and S. Kiaei, "A 10 MHz bandwidth, 2 mV ripple PA regulator for CDMA transmitters," *IEEE J. Solid State Circuits*, vol. 43, no. 12, pp. 2809–2819, Dec. 2008.

- [18] M.-K. Nguyen, Y.-G. Jung, Y.-C. Lim, and Y.-M. Kim, "A single-phase Z-source buck-boost matrix converter," *IEEE Trans. Power Electron.*, vol. 25, no. 2, pp. 453–462, Feb. 2010.

- [19] R. Paul, L. Corradini, and D. Maksimovic, "Modulated digitally controlled non-inverting buck-boost converter for WCDMA RF power amplifiers," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, Feb. 2009, pp. 533–539.

- [20] F. Gao, P. C. Loh, R. Teodorescu, F. Blaabjerg, and D. M. Vilathgamuwa, "Topological design and modulation strategy for buck-boost three-level inverters," *IEEE Trans. Power Electron.*, vol. 24, no. 7, pp. 1722–1732, Jul. 2009.

- [21] M. Barai, S. Sengupta, and J. Biswas, "Digital controller for DVS-enabled DC-DC converter," *IEEE Trans. Power Electron.*, vol. 25, no. 3, pp. 557–573, Mar. 2010.

- [22] S. Xiao, W. Qiu, G. Miller, T. X. Wu, and I. Batarseh, "An active compensator scheme for dynamic voltage scaling of voltage regulators," *IEEE Trans. Power Electron.*, vol. 24, no. 1, pp. 307–311, Jan. 2009.

- [23] A. Soto, A. D. Castro, P. Alou, J. A. Cobos, J. Uceda, and A. Lotfi, "Analysis of the buck converter for scaling the supply voltage of digital circuits," *IEEE Trans. Power Electron.*, vol. 22, no. 6, pp. 2432–2443, Nov. 2007.

- [24] S. Das, D. Roberts, S. Lee, S. Pant, D. Blaauw, T. Austin, K. Flautner, and T. Mudge, "A self-tuning DVS processor using delay-error detection and correction," *IEEE J. Solid-State Circuits*, vol. 41, no. 4, pp. 792–804, Apr. 2006.

- [25] J. E. -Marti, E. S. -Kilders, E. Maset, A. Ferreres, J. M. Blanes, A. Garrigos, J. Jordan, and V. Esteve, "Phase margin degradation of a peak current controlled converter at reduced duty cycle," *IEEE Trans. Power Electron.*, vol. 25, no. 4, pp. 863–874, Apr. 2010.

- [26] K.-H. Chen, C.-J. Chang, and T.-H. Liu, "Bidirectional current-mode capacitor multipliers for on-chip compensation," *IEEE Trans. Power Electron.*, vol. 23, no. 1, pp. 180–188, Jan. 2008.

- [27] R. W. Erickson and D. Maksimovic, Fundamentals of Power Electronics, 2nd ed. Norwell, MA: Kluwer, 2001.

- [28] Y.-J. Lee, A. Khaligh, and A. Emadi, "A compensation technique for smooth transitions in a noninverting buck-boost converter," *IEEE Trans. Power Electron.*, vol. 24, no. 4, pp. 1002–1015, Apr. 2009.

- [29] C.-Y. Hsieh and K.-H. Chen, "Adaptive pole-zero position (APZP) technique of regulated power supply for improving SNR," *IEEE Trans. Power Electron.*, vol. 23, no. 6, pp. 2949–2963, Nov. 2008.

Yu-Huei Lee (S'09) was born in Taipei, Taiwan. He received the B.S. and M.S. degrees from the Department of Electrical and Control Engineering, National Chiao Tung University, Hsinchu, Taiwan, in 2007 and 2009, respectively, where he is currently working toward the Ph.D. degree at the Institute of Electrical Control Engineering, National Chiao Tung University, Hsinchu, Taiwan.

He is a Faculty Member at the Mixed Signal and Power Management IC Laboratory, Institute of Electrical Control Engineering, National Chiao Tung Uni-

versity. His current research interests include the power management integrated circuit design, light-emitting diode driver IC design, and analog integrated circuits.

**Shao-Chang Huang** received the B.S. and M.S. degrees in electrical engineering from the National Cheng Kung University, Tainan, Taiwan, in 1994 and 1996, respectively.

From 1996 to 1998, he was an Officer in national compulsory military service. From 1998 to 1999, he was involved in thin-film-transistor device at ERSO in ITRI, Taiwan. From 1999 to 2006, he worked on ESD/Latch-up/IO research in UMC, Ltd., HBA, Ltd., TSMC, Ltd., and NOVATEK, Ltd. As a UMC Engineer, he worked on 90-nm process ESD solutions at

IBM, Fishkill, NY, in 2001. In 2006, he joined eMemory Technology, Hsinchu, Taiwan, where he is currently the ESD/IO Department Manager. He is the author or coauthor of more than eight papers published in journals and conferences, and holds more than 20 patents. His current research interests include ESD/Latch-up devices and circuits, and I/O related circuits.

Shih-Wei Wang was born in Hualien, Taiwan, in 1980. He received the B.S. degree from the Department of Electrical Engineering, National Taiwan University of Science and Technology, Taipei, Taiwan, in 2006, and the M.S. degree from the Department of Electrical and Control Engineering, National Chiao Tung University, Hsinchu, Taiwan, in 2010, where he is currently working toward the Ph.D. degree at the Institute of Electrical Control Engineering, National Chiao Tung University, Hsinchu, Taiwan.

His research interests include the design of switchmode power converters, linear regulators, analog integrated circuits, and mixedsignal integrated circuits.

**Wei-Chuan Wu** (S'09) was born in Changhua, Taiwan. He received the B.S. and M.S. degrees from the Department of Electrical and Control Engineering, National Chiao Tung University, Hsinchu, Taiwan, in 2007 and 2009, respectively.

He was a member of the Mixed Signal and Power Management IC Laboratory, National Chiao Tung University. He is currently with Richtek, Ltd., Hsinchu. His research interests include the design of power management circuit, LED driver ICs, and the analog integrated circuit designs.

**Ping-Ching Huang** (S'09) was born in Taipei, Taiwan. He received the B.S. and M.S. degrees from the Department of Electrical and Control Engineering, National Chiao Tung University, Hsinchu, Taiwan, in 2007 and 2009, respectively.

He was a member of the Mixed Signal and Power Management IC Laboratory, National Chiao Tung University. He is currently with Richtek, Ltd., Hsinchu. His research interests include the design of power management circuit, the analog integrated circuit designs, and LED driver ICs.

**Hsin-Hsin Ho** was born in Taipei, Taiwan. She received the B.S. degree in electrical and control engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2006, where she is currently working toward the Ph.D. degree in electrical and control engineering.

Her research area contains many projects of LED driver ICs and power management ICs at Low Power Mixed Signal Laboratory. Her interests include power management circuit designs, LED driver ICs, and analog integrated circuit designs.

Yuan-Tai Lai received the B.S. degree in applied chemistry from Providence University, Taichung, Taiwan, in 2000, the M.S. degree in chemistry from Chung Yuan Christian University, Jhongli City, Taiwan, in 2002, and the Ph.D. degree in chemical and materials engineering from National Central University, Jhongli City, in 2008.

He is a Project Manager at the Material Science Center, National Tsing Hua University, Hsinchu, Taiwan. He has been involved in the design and analysis of magnetic components, integration of inductors and

semiconductors for 3-D-system-in-package.

**Ke-Horng Chen** (M'04–SM'09) received the B.S., M.S., and Ph.D. degrees in electrical engineering from National Taiwan University, Taipei, Taiwan, in 1994, 1996, and 2003, respectively.

From 1996 to 1998, he was a part-time IC Designer at Philips, Taipei. From 1998 to 2000, he was an Application Engineer at Avanti, Ltd., Taiwan. From 2000 to 2003, he was a Project Manager at ACARD, Ltd., where he was involved in designing power management ICs. He is currently an Associate Professor in the Department of Electrical Engineering, National

Chiao Tung University, Hsinchu, Taiwan, where he organized a Mixed-Signal and Power Management IC Laboratory. He is the author or coauthor of more than 80 papers published in journals and conferences, and also holds several patents. His current research interests include power management ICs, mixed-signal circuit designs, display algorithm and driver designs of liquid crystal display (LCD) TV, red, green, and blue color sequential backlight designs for optically compensated bend panels, and low-voltage circuit designs.