# A Dual-Resonant Mode 10/22-GHz VCO With a Novel Inductive Switching Approach

Szu-Ling Liu, Kuan-Han Chen, and Albert Chin, Fellow, IEEE

Abstract—This paper presents a novel dual-band voltage-controlled oscillator (VCO) in a standard 0.18- $\mu$ m CMOS technology. With special design in the LC tank, the circuit exhibits two oscillation modes in different frequency bands. The frequency band selection is achieved by a switched coupled inductor with the tunable inductance and quality factor. This VCO can operate in a 10-GHz band with 7.6% tuning range and a 22-GHz band with 8% tuning range, while the core circuit draws a dc current of 8.44 mA from a 1.8-V supply voltage. The figures-of-merit at 10- and 22-GHz bands are -184.63 and -181.81 dBc/Hz, respectively. These performances are comparable with state-of-the-art dual-band LC-VCOs.

*Index Terms*—Dual-band voltage-controlled oscillator (VCO), dual resonance, self-resonance, switched *LC*-VCO, quality factor.

#### I. INTRODUCTION

D UE TO the ever-increasing demand of wire and wireless markets, various communication standards about 1-GHz and higher frequencies are rapidly developing. Therefore, the realization of multistandard operations with the minimal circuit implementations has become a crucial focus for circuit designers.

In a tunable/programmable microwave transceiver covering multiple frequency standards, a wideband or a multiband voltage-controlled oscillator (VCO) is an essential component. An intuitive strategy of building this circuit block is to combine several VCOs that work at different frequency ranges [1], [2]; however, the increasing of chip area, power dissipation, and circuit complexity reduce its suitability for portable applications. In contrast, a more attractive solution is to design a single VCO with a wide frequency range or the ability of operating in different frequencies. To achieve this goal, switched capacitor arrays [3]-[6] and switched inductors [7]-[10] have been incorporated in RF oscillators. In such switched LC-VCOs, the equivalent tank reactance is typically changed by the operation states of a switching transistor, and it subsequently selects the oscillation frequency of the circuit. However, traditional switched LC-resonators often exhibit inferior quality factors due to the parasitic effects of the switching transistor, resulting

Manuscript received March 21, 2012; accepted April 04, 2012. Date of publication May 22, 2012; date of current version June 26, 2012. This work was supported in part by the National Science Council of Taiwan.

S.-L. Liu and A. Chin are with the Department of Electronic Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 30010, Taiwan (e-mail: horison99@hotmail.com; albert\_achin@hotamil.com).

K.-H. Chen is with Orise Technology, Hsinchu 30078, Taiwan (e-mail: saikoa0709@gmail.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TMTT.2012.2195674

in stricter startup conditions and poor phase noise, especially in high-frequency operations above 10 GHz. An alternative inductive switching can be achieved by using magnetic coupling. where the equivalent inductance of the primary coil is changed by utilizing the tunable driving current in the secondary coil through magnetic coupling [11], [12]. This method can avoid using a switching transistor with significant parasitic effects, and it achieves a wide tuning range; however, the overall power consumption inevitably increases due to the additional driving current and therefore struggles to reach the energy efficient target. On the other hand, dual-band or multiband VCOs with the fundamental tone and the even-order harmonics can be realized by using the push-push technique [13], [14]. One advantage of such VCOs is to achieve a large tuning range in the high-order band, but the circuit also requires a high power supply to increase the weak high-order harmonic signals in general. Recently, dual-band LC-VCOs with fourth-order resonators have been proposed [15], [16]. Though these circuits can provide two resonant modes with the common LC tank, an effective band-switching method with less parasitic effects is still a critical consideration.

In this paper, we present a new type of dual-band LC-VCO that can generate two distinct resonant modes inherently. The operation principle significantly differs from the above techniques. The band-switching manner of this design is performed by a novel inductive switching approach utilizing the self-resonance mechanism, which avoids the drawbacks of the conventional switched LC-VCOs and does not require additional driving current.

This paper is organized as follows. Section II discusses the major concerns of common switched *LC*-resonators, in particular, the conventional switched inductor for high-frequency operations. Section III introduces the architecture of the proposed VCO and its dual-resonant behavior, the principle of the band-switching approach is also presented. Section IV describes the simulation results and circuit implementation details. Section V exhibits the measurement results and the circuit performances in comparison with state-of-the-art multiband VCOs. Finally, a conclusion is provided in Section VI.

# II. DESIGN ISSUES OF A SWITCHED LC TANK

A switched LC-resonator can be realized by inductive or capacitive switching methods. This section will investigate the major concerns of both strategies, according to two important considerations: frequency-switching range and quality factor.

#### A. Frequency-Switching Range

In a capacitive switching LC-VCO, if we temporarily ignore all capacitance contribution, except for the switched capacitor,

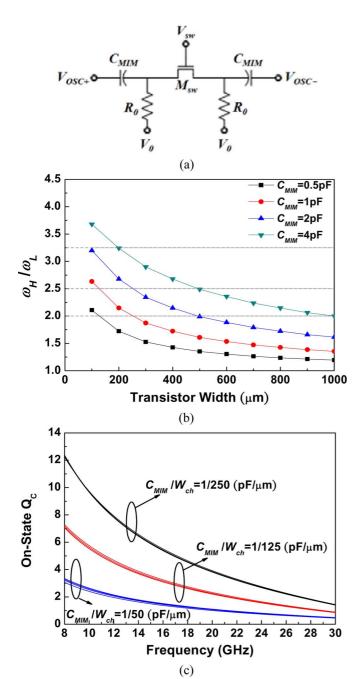

Fig. 1. (a) Commonly used switched capacitor. (b) Simulated (a)  $\omega_H/\omega_L$  and (c) on-state  $Q_C$  of this topology.

the ratio between the highest and lowest oscillation frequencies can be expressed as

$$\left(\frac{\omega_H}{\omega_L}\right)_{\text{Cap-Switching}} = \frac{\left(\frac{1}{L_T C_{\min}}\right)^{\frac{1}{2}}}{\left(\frac{1}{L_T C_{\max}}\right)^{\frac{1}{2}}} = \sqrt{1 + \frac{\delta C}{C_{\min}}} \quad (1)$$

where  $L_T$  is the tank inductance;  $C_{\rm max}$  and  $C_{\rm min}$  are the maximum and minimum capacitances of the switched capacitor, respectively, and  $\delta C = C_{\rm max} - C_{\rm min}$ . Fig. 1(a) shows the commonly used switched capacitor; according to (1), the simulated  $\omega_H/\omega_L$ 's of this configuration are displayed in Fig. 1(b), where  $R_0 = 10~{\rm k}\Omega$  and other component settings were based on

foundry's device models. The simulation reveals that the maximum achievable  $\omega_H/\omega_L$  of the capacitive switching method is about 4; besides, the frequency-switching range increases with increasing the ratio between the capacitance of the metal-insulator-metal (MIM) capacitor ( $C_{MIM}$ ) and the parasitic capacitance of the MOS switch  $(M_{sw})$ , which relies on either reducing the transistor width  $(W_{ch})$  or increasing the size of the MIM capacitor. However, both reducing  $W_{

m ch}$  and increasing  $C_{

m MIM}$  can significantly degrade the on-state capacitor quality factor  $(Q_C)$ at high frequency, as shown in Fig. 1(c). In addition to the inferior on-state  $Q_C$  at high frequency, the actual reachable  $\omega_H/\omega_L$ of the capacitive switching manner will be further decreased due to the capacitance exterior of the switched capacitor, such as the parasitic capacitance from metal connections and active devices. For example, the oscillation frequencies of a capacitive switched dual-band LC-VCO can be expressed as

$$f_{C1,C2} = \frac{1}{2\pi\sqrt{L_T(C_{\text{max,min}} + C_{\text{par}})}}$$

(2)

where  $C_{\mathrm{par}}$  represents the parasitic capacitance. To simplify the analysis, here we assume that the parasitic capacitance remains unchanged while the switched capacitor operates at the different states. Thus, if  $C_{\mathrm{min}}$  is k times of  $C_{\mathrm{par}}$  in the circuit and the target  $f_{C2}$  is two times of  $f_{C1}$ , the required  $C_{\mathrm{max}}/C_{\mathrm{min}}$  will be 4+3/k. In an LC tank with significant parasitic capacitance, the needful capacitance ratio will become very large, increasing the difficulty of the switched capacitor design.

Similarly, the two oscillation frequencies of an inductive switched dual-band VCO are

$$f_{L1,L2} = \frac{1}{2\pi\sqrt{L_{\text{max.min}}(C_T + C_{\text{par}})}}.$$

(3)

In (3),  $C_T$  is the tank capacitance;  $C_{\rm par}$  is the nonswitched parasitic capacitance, as defined in (2),  $L_{\rm max}$  and  $L_{\rm min}$  represent the maximum and minimum inductances of the switched inductor, respectively. For the design target of  $f_{L2}=2f_{L1}$ , the required  $L_{\rm max}/L_{\rm min}$  is 4. Though the oscillation frequencies in both switching methods are lowered by the parasitic capacitance, the switched inductor is still preferable to achieve a large frequency-switching range in dual-band LC-VCOs. Therefore, we adopted the inductive switching means to realize the major band-switching in this design. The capacitive tuning is only used for the finer tuning within each major band.

#### B. Inductor Quality Factor

If the operation frequency is above 10 GHz, inductive switching methods become the commonly used strategies of designing a switched LC-VCO rather than capacitive switching means due to the consideration of quality factor. For a spiral inductor in advanced CMOS processes, the inductor quality factor  $(Q_L)$  increases with increasing frequency and reaches the peak value at the frequency that ranges from 10 to 20 GHz, while  $Q_C$  only follows a decreasing trend as the frequency increases. However, for the typical switched inductor using a MOS switch, as shown in Fig. 2(a), the actual characteristics in high frequency will be strongly affected by the parasitic effects

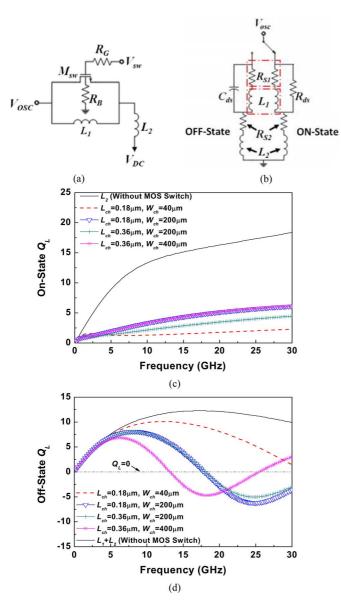

Fig. 2. Typical switched inductor of the: (a) circuit scheme, (b) simplified circuit model, (c) simulated on-state  $Q_L$ , and (d) simulated off-state  $Q_L$ .

of the switching transistor,  $M_{\rm sw}$ . To investigate the influence of the parasitic effects, the simplified circuit model of this switched inductor is illustrated in Fig. 2(b), where  $R_1$  and  $R_2$  are the series resistances of  $L_1$  and  $L_2$ , respectively. The on-state channel impedance of  $M_{\rm sw}$  is approximated as the resistance  $R_{\rm ds}$ , and the capacitance  $C_{\rm ds}$  is used to model the equivalent drain-to-source impedance when the transistor turns off.

By using the device models of a standard 0.18- $\mu$ m CMOS process, the simulated  $Q_L$ 's with the different channel-width-to-channel-length-ratios ( $W_{\rm ch}/L_{\rm ch}$ 's) of  $M_{\rm sw}$  are exhibited in Fig. 2(c) and (d). Here,  $R_G$  and  $R_B$  are the large resistors of 10 k $\Omega$  and chose  $L_1+L_2$  as approximately four times of  $L_2$  at 15 GHz as the simulation condition; the detailed inductor parameters are listed in Table I. According to the simulated results, the on-state  $Q_L$ 's are only slightly improved by increasing  $W_{\rm ch}/L_{\rm ch}$  of  $M_{\rm sw}$ , while the off-state  $Q_L$ 's suffer from significant degradation when the frequency is above 10 GHz. In the conditions of the same  $W_{\rm ch}/L_{\rm ch}$ , the on-state

TABLE I INDUCTOR PARAMETERS USED FOR THE SWITCHED INDUCTOR SIMULATION

|                           | $L_{I}$ | $L_2$ | $L_1+L_2$ |

|---------------------------|---------|-------|-----------|

| Number of Turns           | 1.75    | 0.5   | -         |

| Inner Radius (µm)         | 33      | 30    | -         |

| Line Width (µm)           | 6       | 6     | 6         |

| Inductance at 15 GHz (nH) | 0.65    | 0.22  | 0.88      |

| Q <sub>L</sub> at 15GHz   | 13.923  | 15.13 | 12.157    |

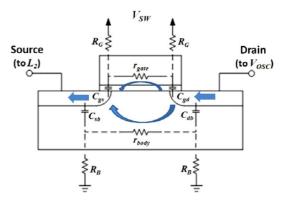

Fig. 3. Off-state parasitic *RC* effects in the switching transistor with large bias resistors at the gate and body terminals.

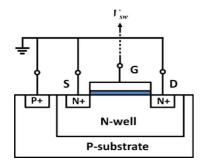

$Q_L$ 's are very close due to the similar  $R_{\rm on}$ 's, but the off-state  $Q_L$ 's of using the large MOS switch show the more rapid decreasing rate as frequency increases. These phenomena are mainly because the parasitic capacitance of  $M_{\mathrm{sw}}$  increases with increasing  $W_{\rm ch}$ . The parasitic capacitance not only limits the improvement of the on-state  $Q_L$ 's when  $W_{\rm ch}/L_{\rm ch}$ increases, but also causes the decreased off-state  $Q_L$ 's due to the reduced self-resonance frequency. In this simulation, although the gate and body terminals of  $M_{\rm sw}$  are biased via large resistors to decrease the equivalent gate capacitance and junction capacitance, the simulated self-resonance frequency is still very limited. The main reason can be explained by the cross-section view of the MOS switch, as shown in Fig. 3, where  $r_{\text{gate}}$  and  $r_{\text{body}}$  represent the small-signal resistances of the gate and P-well regions, respectively. If the gate and body terminals are isolated by large resistors, the equivalent  $C_{\rm gd}$  and  $C_{\rm db}$  are suppressed, but the capacitive effects still transfers to  $C_{ds}$  since  $r_{gate}$  and  $r_{body}$  become low-impedance paths, which restricts the improvement of the self-resonance frequency. Therefore, designing a high-frequency dual-band VCO with the conventional switched inductor still encounters the significant  $Q_L$  degradation issue. Thus, in the proposed dual-band VCO, a novel inductive switching technique with the different switching mechanism is utilized to select the operation frequency band.

## III. DESIGN CONCEPTS OF THE PROPOSED DUAL-BAND VCO

#### A. Basic Circuit Architecture

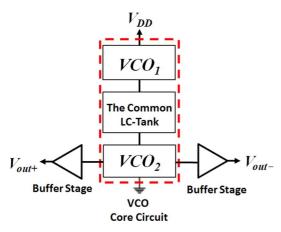

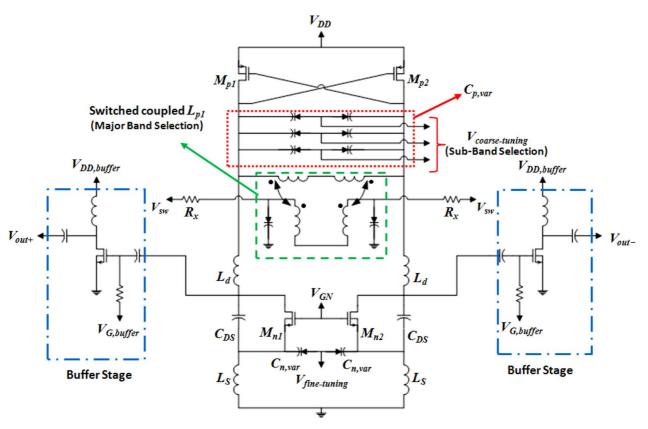

Fig. 4 shows the basic architecture of the proposed dual-band VCO. In this design, the core circuit is cascoded by two sub-VCOs driven by the same dc current,  $VCO_1$  and  $VCO_2$ ,

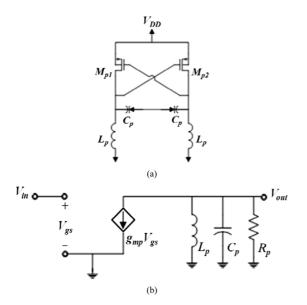

$VCO_1$  is a cross-coupled LC-VCO with pMOS transistor pairs, as shown in Fig. 5(a), where  $L_p$  and  $C_p$  represent the tank

Fig. 4. Basic architecture of the proposed VCO.

Fig. 5. VCO<sub>1</sub>. (a) Prototype circuit. (b) Simplified half-circuit

inductance and tank capacitance, respectively. The simplified half-circuit model of VCO<sub>1</sub> is displayed in Fig. 5(b), where the transistor is treated as a voltage-controlled current source and  $R_p$  represents the overall loss of the tank. Therefore, the transfer function between  $V_{\rm in}$  and  $V_{\rm out}$  can be provided by

$$\frac{V_{\text{out}}}{V_{\text{in}}} = -\frac{sL_p R_p g_{mp}}{s^2 L_p C_p R_p + sL_p + R_p}.$$

(4)

Equation (4) indicates that the circuit can resonate at the specific angular frequency  $\omega_p$ , while the transfer function  $V_{\rm out}/V_{\rm in} = -1$  as  $s = j\omega_p$ . With the proper arrangement in (4), the angular frequency  $\omega_p$  and the required transistor trans-conductance  $g_{mp}$  for oscillation can be derived as

$$\omega_p = \frac{1}{\sqrt{L_p C_p}}$$

$$g_{mp} = \frac{1}{R_p}.$$

(6)

$$g_{mp} = \frac{1}{R_p}. (6)$$

On the other hand, VCO<sub>2</sub> is constructed by two modified nMOS Colpitts oscillators, as shown in Fig. 6(a). The Colpitts

Fig. 6. VCO<sub>2</sub>. (a) Prototype circuit. (b) Simplified half-circuit.

architecture was used here due to its excellent cyclo-stationary noise properties, which can possibly improve phase-noise performance of the circuit [17]. The tail-current source in a traditional Colpitts oscillator is replaced by the on-chip inductor  $L_s$ to improve the voltage headroom and to avoid the additional transistor noise contribution. [18]. To derive the oscillation frequency and the start-up condition for this topology, Fig. 6(b) shows the simplified half-circuit of  $VCO_2$ , where  $I_{in}$  represents the stimulus current in the circuit;  $R_s$  and  $R_n$  represent the equivalent resistive loss at the source and drain terminals, respectively. Since the parasitic capacitances of the core transistor are much smaller than  $C_S$  and  $C_{DS}$ , the transistor is approximated as a single voltage-controlled current source,  $g_{mn}V_{gs}$ , by neglecting its parasitic capacitances and channel length modulation effect. From the small-signal analysis, the transfers function between  $I_{\rm in}$  and  $V_{\rm out}$  is provided by

$$\frac{V_{\text{out}}}{I_{\text{in}}} = \frac{s^2(sC_{\text{DS}} + g_{mn})}{c_4 s^4 + c_3 s^3 + c_2 s^2 + c_1 s + c_0}$$

(7)

where

$$c_{0} = \frac{1}{L_{n}L_{S}}$$

$$c_{1} = \frac{g_{mn}}{L_{n}} + \frac{1}{L_{n}R_{S}} + \frac{1}{L_{S}R_{n}}$$

$$c_{2} = \frac{g_{mn}R_{S} + 1}{R_{S}R_{n}} + \frac{L_{S}(C_{S} + C_{DS}) + L_{n}C_{DS}}{L_{n}L_{S}}$$

$$c_{3} = \frac{C_{S} + C_{DS}}{R_{n}} + \frac{C_{DS}}{R_{S}}$$

$$c_{4} = C_{S}C_{DS}.$$

The circuit oscillates if the transfer function  $V_{\rm out}/I_{\rm in}$  goes to infinite. If this condition can be met when  $s = j\omega_n$ , both the real and the imaginary parts of the denominator in (7) will be zero at the angular frequency  $\omega_n$ . In other words,

$$\omega_n^4 C_S C_{\rm DS} + \omega_n^2 \left[ \frac{g_{mn} R_S + 1}{R_n R_S} + \frac{L_S (C_S + C_{\rm DS}) + L_n C_{\rm DS}}{L_n L_S} \right] + \frac{1}{L_L L_S} = 0 \quad (8)$$

and

$$j\omega_n \left(\frac{g_{mn}}{L_n} + \frac{L_n R_S + L_S R_n}{L_n L_S R_n R_S}\right) - j\omega_n^3 \times \left(\frac{C_S + C_{DS}}{R_n} + \frac{C_{DS}}{R_S}\right) = 0 \quad (9)$$

since  $(g_{mn} + R_S^{-1})(L_n + L_S) \ll R_n(C_S + 2C_{DS})$  in typical designs, (8) yields

$$\omega_n^4 C_S C_{\rm DS} L_n L_S + \omega_n^2 [L_S (C_S + C_{\rm DS}) + L_n C_{\rm DS}] + 1 = 0$$

(10)

With the proper design such that  $L_SC_S\gg L_nC_{\rm DS}$ , the resonant angular frequency  $\omega_n$  in (10) can be approximated by

$$\omega_n \cong \sqrt{\frac{C_S + C_{\rm DS}}{L_n C_S C_{\rm DS}}} = \sqrt{\frac{1}{L_n C_n}}.$$

(11)

In (11), the equivalent tank capacitance  $C_n$  is introduced to simplify the analysis result, where  $C_n = C_S C_{\rm DS}/(C_S + C_{\rm DS})$ . Based on (9) and (11), the required transistor trans-conductance  $q_{mn}$  to satisfy the startup condition is given as

$$g_{mn} \cong \frac{[(C_S + C_{DS})R_S + C_{DS}R_n)]}{C_n R_S R_n} - \frac{L_n R_S + L_S R_n}{L_S L_n R_S R_n}.$$

(12)

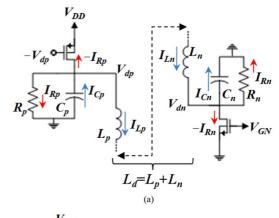

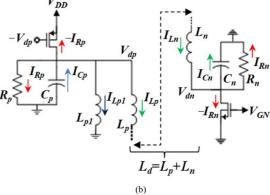

#### B. Mechanism of Dual-Frequency Oscillation

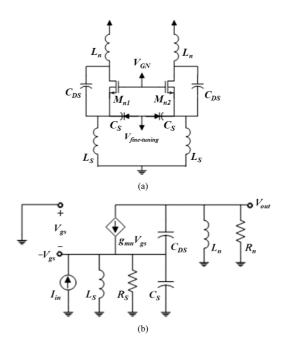

The preceding analysis is based on two LC-VCOs with separate tank inductances. In this design, alternatively, the tank inductances of  $VCO_1$  and  $VCO_2$  are not defined by individual components, but by the shared inductor  $L_d$ , therefore,

$$L_d = L_p + L_n. (13)$$

To establish a stable oscillation,  $VCO_1$  and  $VCO_2$  should resonate at the same frequency. Here, the shared inductor  $L_d$  plays the critical role to synchronize these two sub-VCOs since the two oscillators can lock each other's oscillation frequency by the consistent injection current through  $L_d$ , as shown in Fig. 7(a), where  $C_p$  and  $C_n$  represent the equivalent tank capacitances of  $VCO_1$  and  $VCO_2$ , as provided in (5) and (11), respectively. When  $VCO_1$  and  $VCO_2$  generate the synchronous oscillation at the angular frequency  $\omega_0$ , the equivalent tank inductances of these two sub-VCOs should satisfy

$$L_p C_p = L_n C_n = \omega_0^{-2}. (14)$$

From (13) and (14),  $L_p$  and  $L_n$  can be derived as

$$L_p = \left(\frac{C_n}{C_p + C_n}\right) L_d \tag{15}$$

$$L_n = \left(\frac{C_p}{C_p + C_n}\right) L_d. \tag{16}$$

The oscillation behavior of the circuit in Fig. 7(a) is similar to the two independent VCOs that resonate at the same frequency.

Fig. 7. Current flows in the: (a) half-circuit of the cascoded  $VCO_1$  and  $VCO_2$  and (b) half-circuit of the modified topology.

Based on Miller theorem [19], one can assume there is a virtual ground node within  $L_d$ , which divides  $L_d$  into  $L_p$  and  $L_n$ , as provided in (15) and (16), respectively. Therefore, the analysis in Section III-A can still be applied to this architecture.

However, while  $C_p$ ,  $C_n$  and  $L_d$  are defined, the values of  $L_p$  and  $L_n$  are uniquely decided through (15) and (16), respectively, so that the topology in Fig. 6(a) can only force the two sub-VCOs to oscillate at one specific frequency. For a dual-frequency operation, the circuit still requires the additional degree-of-freedom in the LC-tank design. Fig. 7(b) exhibits the modified architecture from the half-circuit in Fig. 7(a). This is the prototype used for the proposed dual-band LC-VCO, where the parallel inductor  $L_{p1}$  is added into the tank of VCO<sub>1</sub>. In this case, the synchronous conditions of the two sub-VCOs will be given by (13) and (17)

$$(L_p//L_{p1})C_p = L_n C_n = \omega_0^{-2}.$$

(17)

In fact, (14) is a special case of the infinite  $L_{p1}$  in (17). By solving (13) and (17) with the finite  $L_d$ ,  $L_{p1}$ ,  $C_p$  and  $C_n$ , the equivalent inductances of  $L_p$  and  $L_n$  can be expressed as the functions of  $L_d$ ,  $L_{p1}$ ,  $C_p$  and  $C_n$ , as provided in (18) and (19)

$$L_p = \left[ \frac{(\kappa_L - \kappa_C) + \sqrt{(\kappa_L - \kappa_C)^2 + 4\kappa_L}}{\kappa_L} \right] \cdot \frac{L_d}{2}$$

(18)

$$L_n = \left[ \frac{(\kappa_L + \kappa_C) - \sqrt{(\kappa_L - \kappa_C)^2 + 4\kappa_L}}{\kappa_L} \right] \cdot \frac{L_d}{2}$$

(19)

where  $\kappa_L$  is the inductance ratio between  $L_d$  and  $L_{p1}$ , and  $\kappa_C$  is the capacitance ratio between  $(C_p+C_n)$  and  $C_n$ .  $\kappa_C$  is always larger than unity since  $C_p$  and  $C_n$  are both positive capacitances. As  $\kappa_C$  approaches 1, the corresponding  $L_n$  value will be close to 0, which is equivalent to the oscillation not occurring in VCO<sub>2</sub>.

On the other hand, the other solution set of  $L_p$  and  $L_n$  from (13) and (17) can be expressed as

$$L_p = \left\lceil \frac{(\kappa_L - \kappa_C) - \sqrt{(\kappa_L - \kappa_C)^2 + 4\kappa_L}}{\kappa_L} \right\rceil \cdot \frac{L_d}{2} \quad (20)$$

$$L_n = \left\lceil \frac{(\kappa_L + \kappa_C) + \sqrt{(\kappa_L - \kappa_C)^2 + 4\kappa_L}}{\kappa_L} \right\rceil \cdot \frac{L_d}{2} \quad (21)$$

Though (20) gives the negative inductance for  $L_p$ , in any practical design with the positive inductance value of  $L_{p1}$ , the equivalent tank inductance of  $VCO_1, L_p//L_{p1}$ , is still a positive inductance if  $L_p + L_{p1} < 0$ , i.e.,

$$\frac{L_d}{\kappa_L} + \left[ \frac{(\kappa_L - \kappa_C) - \sqrt{(\kappa_L - \kappa_C)^2 + 4\kappa_L}}{\kappa_L} \right] \cdot \frac{L_d}{2} < 0.$$

(22)

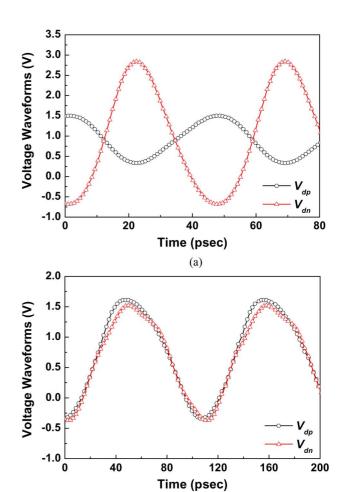

Equation (22) is held if  $\kappa_C > 1$ , which is true for all practical  $C_p$  and  $C_n$  as mentioned above, and therefore indicates that (20) and (21) are the acceptable solution set of the other oscillation mode. From the different products of  $L_n$  and  $C_n$ , the two oscillation modes apparently lead to distinct resonant frequencies. To further investigate the behaviors of both modes, the preliminary simulation for the topology in Fig. 7(b) was also performed by using an ADS simulator, as shown in Fig. 8. The mode of antiphase  $V_{dp}$  and  $V_{dn}$  corresponded with the solution set from (18) and (19), and the mode of in-phase  $V_{dp}$  and  $V_{dn}$  corresponds to the other condition from (20) and (21), which confirm that the dual-oscillation behavior can be realized by the above design methodology.

Theoretically, the frequency ratio between the high- and lowband carriers of the proposed dual-resonance *LC*-tank can be derived as

$$\left(\frac{\omega_H}{\omega_L}\right) = \sqrt{1 + \frac{2\Delta}{(\kappa_L + \kappa_C) - \Delta}} \tag{23}$$

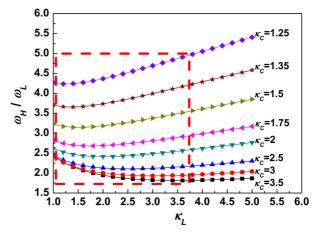

where  $\Delta = [(\kappa_L - \kappa_C)^2 + 4\kappa_L]^{1/2}$ . Although (23) has the similar form as (1), there is a major difference between these two equations that  $\omega_H/\omega_L$  in (23) is not only controlled by the tank capacitance, but also by the tank inductance; thus, there are two degrees-of-freedom ( $\kappa_L$  and  $\kappa_C$ ) that can be chosen for the required frequency-switching range. Fig. 9 exhibits the simulated  $\omega_H/\omega_L$  versus  $\kappa_L$ , where  $\omega_H/\omega_L$  from 1.75 to 5 can be obtained from different selections in the applicable  $\kappa_L$  and  $\kappa_C$  ranges.)

### C. Frequency-Switching Approach

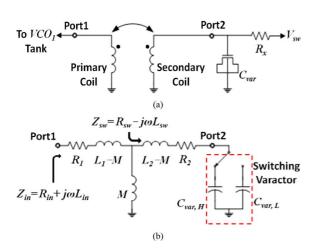

In addition to generating carrier signals with different frequencies, an effective method to select the oscillation modes is also required in the proposed dual-band VCO. To achieve this goal,  $L_{p1}$  in Fig. 7(b) was implemented by a two-port transformer with switchable input impedance at the primary

Fig. 8. Simulated voltage waveforms of the circuit topology in Fig. 5(b), as the exterior  $C_p=0.12$  pF,  $C_n=0.16$  pF, and  $L_d=L_{p1}=0.36$  nH. (a) Antiphase mode. (b) In-phase mode.

Fig. 9. Simulated  $\omega_H/\omega_L$  of the proposed dual-resonance LC-tank.

port  $(Z_{\rm in})$ . Its primary and secondary coils are connected to the tank of VCO<sub>1</sub> and the switching varactor, respectively, as shown in Fig. 10(a). Here,  $C_{\rm var}$  represents the capacitance of the switching varactor, which is governed by the controlled voltage  $V_{\rm sw}$  through the large resistor  $R_x$ . There are two apparent advantages of using transformer-based switched inductor: First, a transformer composed by the stacked inductor

Fig. 10. (a) Circuit scheme and (b) equivalent T-model of the two-port transformer and the switching varactor used for the switched  $L_{p1}$ .

Fig. 11. Cross-section view of an accumulation mode MOS varactor used for the switching varactor.

windings generally consumes the smaller area than the conventional switched inductor using two separate inductors. Second, in the transformer-based switched inductor, the bias levels of the switching device are separated from the LC tank, therefore alleviating the possible concern of the device breakdown under large-signal operation.

To comprehend the coupling effects between the primary and secondary coils, the equivalent T-model, as in [20], is adopted in the following analysis, as shown in Fig. 10(b), where  $L_1$  and  $L_2$  represent the self-inductances of the primary and secondary coils, respectively; M is the mutual inductance between  $L_1$  and  $L_2$ ;  $R_1$  represents the ohmic loss of the primary coil; and  $R_2$  represents the ohmic loss of both the secondary coil and switching varactor. When  $V_{\rm sw}$  is set to the high and low states, the varactor capacitances are switched to  $C_{\rm var,} H$  and  $C_{\rm var,} L$ , respectively. In this design, all varactors were implemented by accumulation-mode MOS varactors, as shown in Fig. 11. Here, the switching varactor only operates in the strong accumulation (at the high state) and the inversion (at the low state) modes to ensure the disturbance of  $C_{\rm var}$  due to voltage variation across the varactor can be neglected.

According to the T-model transformation,  $Z_{\rm in}$  at the high and low states of  $V_{\rm sw}$ , can be derived by

$$Z_{\text{in},H,L} = R_{\text{in},H,L} + j\omega L_{\text{in},H,L}$$

$$= R_1 + j\omega L_1 + \frac{\omega^2 M^2}{R_2 + j\omega L_2 + (j\omega C_{\text{var},H,L})^{-1}}$$

(24)

where

$$R_{\text{in},H,L} = R_1 + \frac{\omega^2 M^2 R_2}{R_2^2 + \left[\omega L_2 - (\omega C_{\text{var},H,L})^{-1}\right]^2}$$

$$= R_1 + R_{\text{sw},H,L} \qquad (25)$$

$$L_{\text{in},H,L} = L_1 - \frac{\omega M^2 \left[\omega L_2 - (\omega C_{\text{var},H,L})^{-1}\right]}{R_2^2 + \left[\omega L_2 - (\omega C_{\text{var},H,L})^{-1}\right]^2}$$

$$= L_1 - L_{\text{sw},H,L}. \qquad (26)$$

If the secondary coil and the switching varactor are properly designed so that  $R_2$  is small,  $R_{\rm in}$  can be effectively reduced and is mainly dominated by  $R_1$ , while the angular frequency is far from  $(L_2C_{\text{var},H})^{-1/2}$  and  $(L_2C_{\text{var},L})^{-1/2}$ . The actual resistance contribution from the switching device to the LC tank can be effectively suppressed through impedance transformation; which is another important merit of the transformer-based switched inductor. In contrast, when the excitation is near to the resonant frequency of the secondary coil and the switching varactor,  $R_{\rm in}$  will increase rapidly due to small  $R_2^2$  in the dominator of (25), leading to a severely decreased quality factor  $(Q_{Lp1})$ and preventing oscillation. Self-resonance generally is an adverse effect to the conventional switched inductor; however, in the proposed dual-band VCO, we utilized these properties to realize the band-switching from the two oscillation modes. With the proper design of the resonant frequency of  $L_2$  and  $C_{\text{var}}$ , the frequencies of the minimum  $Q_{Lp1}$ 's of  $Z_{in,H}$  and  $Z_{in,L}$  are set near the carrier frequencies of the two oscillation modes, respectively. While the circuit operates at the one of oscillation modes, the other mode can be forbidden due to the corresponding  $Q_{Lp1}$ being significantly suppressed, and vice versa. This capability of the undesired mode rejection is difficult to achieve by using the switching transistor. Though the switched inductor with the switching transistor can provide two inductance states while the equivalent impedance of the MOS switch is changed to the resistive (at the on-state) and the capacitive (at the off-state) types. The on-state channel resistance uniformly deteriorates  $Q_L$  at all frequencies, while the off-state parasitic capacitance mainly decreases  $Q_L$  when approaching the self-resonance frequency; these dissimilar characteristics are unfavorable to optimize  $Q_L$ 's of the two inductance states simultaneously.

Besides, (25) and (26) indicate that the real and imaginary parts of  $Z_{\rm in}$  will be close to  $R_1 + R_2(M/L_2)^2$  and  $\omega(L_1 - M^2/L_2)$  at high frequency, respectively. In other words, while the angular frequency is above the self-resonance frequencies of  $L_2$  and  $C_{\text{var}}$ , the corresponding  $Q_{Lp1}$ 's can rise again with increasing frequency. Hence, this band-switching approach is more conducive to high-frequency oscillator designs than using conventional switched LC-resonators. The predictions from (25) and (26) are based on the equivalent T-model of a two-port transformer that ignores the small parasitic capacitance between the two inductor windings. At very high frequencies,  $Q_{Lp1}$ 's will decreases due to the secondary self-resonance induced by the parasitic capacitance between  $L_1$  and  $L_2$ . With the proper design of the structure and the turn numbers for the two coils, such parasitic capacitance can be effectively reduced and the secondary self-resonance

Fig. 12. Full schematic of the proposed dual-band VCO.

frequency is significantly higher than the 10/22-GHz frequency bands of this circuit, which will be verified by the simulation in Section IV. Therefore, the preceding analysis from the T-model in Fig. 10(b) is still reliable for the operation frequency range of this VCO.

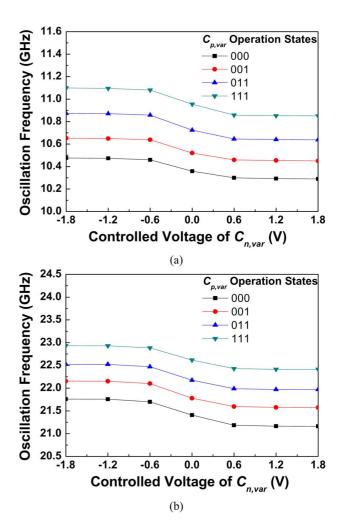

## IV. FABRICATION DETAILS AND MODELING

The full circuit architecture of the proposed dual-band VCO is shown in Fig. 12. The major band switching is realized by the switched coupled inductor  $L_{p1}$ . The capacitances of  $C_p$  in Fig. 5(a) and  $C_S$  in Fig. 6(a) were implemented by the varactor array  $C_{p,\mathrm{var}}$  and the fine-tuning varactor  $C_{n,\mathrm{var}}$ , respectively. The tuning range of both major bands is further divided into four overlapping sub-bands by three digital varactors in  $C_{p,\mathrm{var}}$ . The continuous tuning is performed by  $C_{n,\mathrm{var}}$ , while retaining small VCO gain  $(K_{\mathrm{VCO}})$  in each sub-band to obtain better phasenoise performance.

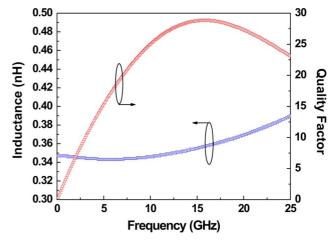

The inductor used for  $L_d$  was fabricated by the top metal layer (metal-6) in a standard 0.18-  $\mu$ m CMOS technology. It is a half-turn winding with a radius of 120  $\mu$ m and a linewidth of 15  $\mu$ m. The half-turn structure can minimize the parasitic inter-winding capacitance, ensuring the current continuity of  $I_{Lp}=I_{Ln}$  in Fig. 7(b). The inductance and quality factor of  $L_d$  were obtained via the electromagnetic simulation by using ADS Momentum, as shown in Fig. 13.

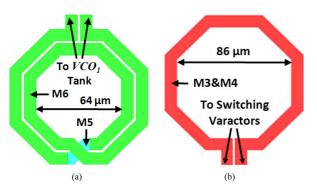

The structure of the switched coupled inductor  $L_{p1}$  is shown in Fig. 14. The primary coil is a differential inductor with a linewidth of 9  $\mu$ m, which was fabricated by the top metal layer with a bottom jumper built by metal-5. A double-turn

Fig. 13. Simulated inductance and quality factor of the inductor  $L_d$ .

structure was used in the primary coil to acquire a balance between sufficient inductance and small parasitic resistance. The secondary coil is a single-turn differential inductor with a linewidth of 9  $\mu$ m. It was placed underneath the outer winding of the primary coil. To reduce the series resistance and the parasitic capacitance between the two coils, the secondary coil was constructed by stacking metal-4 and metal-3 with via connections. Two switching varactors were connected to the secondary coil and used to select the oscillation mode, as described in Section III. The switching varactor size is mainly determined by the required frequency-switching range since the resonant frequencies of the secondary coil and the switching

Fig. 14. Layout structure of the: (a) primary coil and (b) secondary coil of the designed transformer used for  $L_{p1}$ .

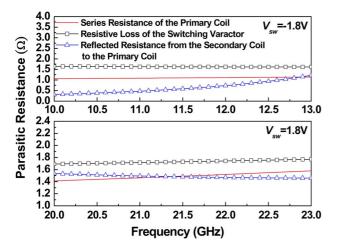

Fig. 15. Simulated series resistance of the primary coil  $(R_1)$ , the parasitic resistance of the switching varactor  $(R_{\rm var})$ , and the reflected resistance  $(R_{\rm sw})$  from the secondary coil to the primary coil.

varactor should be designed near the carrier frequencies of the two oscillation mode in the circuit, respectively. In this design, the switching varactor has a gate length of 0.5  $\mu$ m and a total width of 250  $\mu$ m.

Fig. 15 shows the simulated series resistance of the primary coil  $(R_{1})$ , the parasitic resistance of the switching varactor  $(R_{\rm var})$ , and the reflected resistance  $(R_{\rm sw})$  from the secondary coil to the primary coil. The advantage of using the transformer-based switched inductor is revealed in this simulation, where  $R_{\rm var}$  is smaller than 2  $\Omega$  in all operation frequency ranges, and the actual resistance contribution can be further suppressed through the impedance transformation. In the low-frequency oscillation mode  $(V_{\rm sw}=-1.8~{\rm V}),\,R_{\rm sw}<1~\Omega$  and is obviously lower than the series resistance of the primary coil; therefore  $R_{\rm in}$  is mainly governed by  $R_{\rm 1}$ . In the high-frequency oscillation mode  $(V_{\rm sw}=1.8~{\rm V}),\,R_{\rm sw}\sim1.5~\Omega$ , which is compatible to  $R_{\rm 1}$ . Hence, in both frequency bands of the proposed VCO, the influence of  $R_{\rm var}$  can be controlled in the acceptable level and does not significantly affect  $Q_L$ .

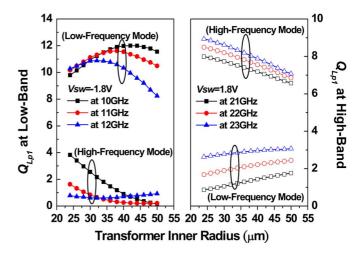

Fig. 16 shows the simulated  $Q_{Lp1}$  for the different inner radii of the transformer. According to this simulation, the optimized inner radius range is between 30–40  $\mu$ m. Adopting a larger radius will result in the decreased  $Q_{Lp1}$ 's in both oscillation modes, leading to stricter startup conditions and worse phase-noise performances. On the other hand, though

Fig. 16. Simulated  $Q_{Lp1}$  versus different radii of the transformer.

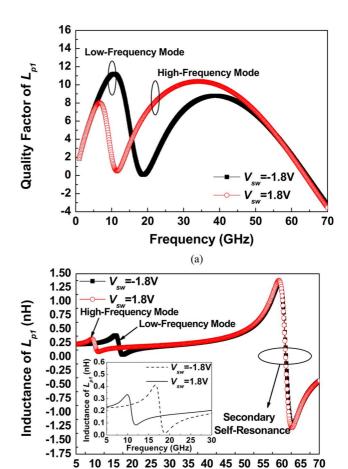

Fig. 17. Simulated: (a) quality factor and (b) inductance of the designed  $L_{p1}$ .

Frequency (GHz)

continued shrinking of the transformer radius can increase the high-band  $Q_{Lp1}$ , this approach also reduces the low-band  $Q_{Lp1}$  when the radius is below 30  $\mu$ m due to the over-reduced inductance of the primary coil. Here, we adopted a radius of 32  $\mu$ m for the designed transformer. The corresponding quality factors and inductances were simulated and are displayed in Fig. 17. In Fig. 17(a), the designate frequencies of the local

Fig. 18. Frequency sensitivity to: (a)  $\kappa_L$  and (b)  $\kappa_C$ .

Fig. 19. Microphotograph of the fabricated 10/22-GHz dual-band VCO.

minimum  $Q_{Lp1}$ 's are 10.7 and 18.1 GHz, which can be used to eliminate the undesired oscillation mode while keeping the desired mode. As the frequency continued increases, both  $Q_L$ 's

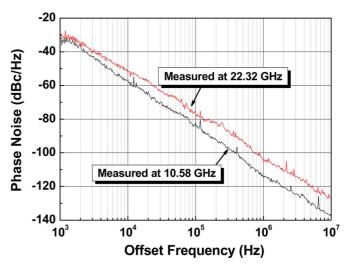

Fig. 20. Measured tuning characteristics at the: (a) low- and (b) high-band operations.

can rise again and reach the local maximum value around 35 GHz, as the prediction from (25) and (26) in Section III. At higher frequencies,  $Q_L$ 's will decrease due to the secondary self-resonance around 60 GHz, which is much higher than the self-resonance frequency of conventional switched inductors using a large MOS switch. Since the secondary self-resonance is caused by the parasitic capacitance between the primary and secondary coils and is uncorrelated with the varactor capacitance, the two secondary self-resonance frequencies of different oscillation modes are almost the same, as shown in Fig. 17(b).

Although the parasitic capacitance between the two coils can affect the accuracy of the T-model in Fig. 10(b) at very high frequency, the corresponding secondary self-resonance around 60 GHz apparently exceeds the typical frequency range of LC-VCOs in a 0.18- $\mu$ m CMOS technology. Therefore, we can still ignore this effect in the proposed switched inductor design.

Here we define that  $S_L$  and  $S_C$  are the partial derivative of the oscillation frequency to  $\kappa_L$  and the partial derivative of the oscillation frequency to  $\kappa_C$ , respectively. For the given  $L_d$  and  $C_n, S_L$  and  $S_C$  can be derived as

$$(S_L)_{H,L} = \pm \frac{\alpha}{2\pi\Delta} \cdot \frac{\left[ (\kappa_L - \kappa_C) \pm \Delta \right] - \frac{1}{\alpha}}{\left[ (\kappa_L + \kappa_C) \mp \Delta \right]^{\frac{3}{2}}} \cdot \sqrt{\frac{2\kappa_L}{L_d C_n}}$$

(27)

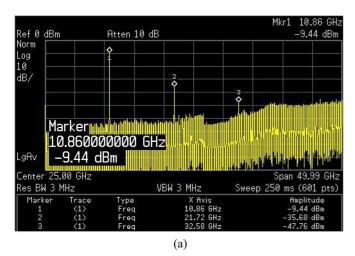

Fig. 21. Measured spectrum at the: (a) low- and (b) high-band operations.

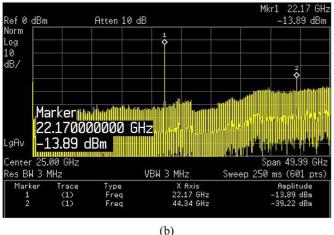

Fig. 22. Measured output power across the entire tuning range.

$$(S_C)_{H,L} = \mp \frac{1}{2\pi\Delta} \cdot \frac{(\kappa_L - \kappa_C) \pm \Delta}{[(\kappa_L + \kappa_C) \mp \Delta]^{\frac{3}{2}}} \cdot \sqrt{\frac{\kappa_L}{2L_dC_n}}$$

(28)

where  $\Delta = [(\kappa_L - \kappa_C)^2 + 4\kappa_L]^{1/2}$  and  $\alpha = \kappa_C/2\kappa_L$ . Since the expressions are too complicated to obtain direct design information, the simulated  $S_L$  and  $S_C$  are plotted in Fig. 18. In Fig. 18(a), the simulation shows that the low-band  $S_L$ 's

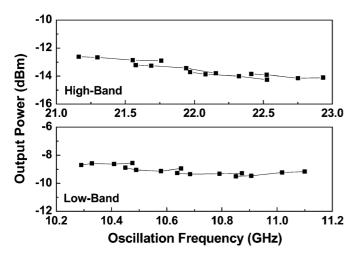

Fig. 23. Measured phase noise performance at 10.58 GHz (in the low-frequency band) and 22.32 GHz (in the high-frequency band).

Fig. 24. Measured phase noise across the entire tuning range.

decrease with increasing  $\kappa_L$ , while the high-band  $S_L$ 's are nearly invariant. Since the digital inductive tuning is only used to achieve the major band switching in the proposed VCO, adopting low  $S_L$ 's may be preferable to increase the frequency stability in both bands. However, the primary consideration of designing  $L_{p1}$  is still to improve the quality factor. According to the simulation in Fig. 16, choosing low  $L_{p1}$  is not conducive to the low-band  $Q_{Lp1}$  and reduces the suppression ability to the undesired oscillation mode for the low-band operation. Besides, adopting a small switched inductor also increases the inductance error due to parasitic effects in the practical layout. Therefore, the proper  $\kappa_L$ 's in both bands should be less than 3. In this switched inductor, the low- and high-band  $\kappa_L$ 's are about 1.5 and 2.2, respectively.

In a multiband LC-VCO using the switched LC-resonator, the fine frequency tuning generally is still achieved by the capacitive approach. Traditionally, the frequency sensitivity of the capacitive tuning can be approximately expressed as

$$\frac{\partial f_{\text{OSC}}}{\partial C_{\text{tunable}}} \cong -\frac{1}{4\pi\sqrt{L_T}(C_{\text{tunable}})^{\frac{3}{2}}}$$

(29)

| Refs.        | Technology     | Frequency<br>(GHz)        | V <sub>DD,core</sub> (V) | P <sub>DC,core</sub> (mW) | Tuning Range<br>(GHz) | P <sub>out</sub> (dBm) | Phase Noise<br>@1MHz Offset (dBc/Hz) | FOM<br>(dBc/Hz)      |        |

|--------------|----------------|---------------------------|--------------------------|---------------------------|-----------------------|------------------------|--------------------------------------|----------------------|--------|

| [13]         | 0.18μm<br>CMOS | 10.18-11.37               | 1.8                      | 11.826                    | 1.19                  | -6                     | -118.67                              | -188                 |        |

|              |                | 19.84-22.01               | 1.8                      | 40.32                     | 2.17                  | -6.83                  | -111.67                              | -181.5               |        |

|              |                | 39.33-43.67               | 2.2                      | 115.94                    | 4.34                  | -18                    | -102                                 | -174                 |        |

| [1.4]        | 0.18µm         | 15                        | 2                        | 52                        | 0.25                  | -8                     | -112.2                               | -178.56              |        |

| [14]         | CMOS           | 30                        | 2                        | 32                        | 0.5                   | -16                    | -104.1                               | -176.78              |        |

| [16]         | 0.18µm         | 4.78-5.19                 | 0.8                      | 2.18                      | 0.41                  | -8.59                  | -117.16                              | -187.2               |        |

|              | CMOS           | 12.19-12.61               |                          | 2.56                      | 0.42                  | -11.48                 | -112.15                              | -190.5               |        |

| [21]         | 0.13µm         | 20                        | 1.2                      | 1.2 5.4                   | 5.4                   | 1.85                   | -6.2                                 | -108.42              | 106.4  |

|              | CMOS           | 40                        |                          |                           | 3.7                   | -16.9                  | -102.4                               | -186.4               |        |

| [22]         | 0.13μm         | 24                        | 0.8                      | 11                        | 2.59                  |                        | -120 <sup>++</sup>                   | -177                 |        |

|              | CMOS           | 60                        | 1.2                      | 24                        | 4.32                  | -                      | -114**                               | -176                 |        |

| [23]         | 0.13µm         | 11.6-18.1                 | 1.2                      | 1.2                       | 20.20                 | 6.5                    |                                      | -107**               |        |

|              | CMOS           | 18.9-22                   |                          | 20-29                     | 3.1                   | -                      | -10/***                              | -                    |        |

| [24]         | 90nm           | 3.1-3.9                   | 1.2                      | 2.16-4.2                  | 0.8                   |                        | -122 <sup>+</sup>                    | -181*                |        |

|              | CMOS           | 8.8-11.2                  |                          | 1.2                       | 6.72-9.96             | 2.4                    | -                                    | -128+                | -181** |

| This<br>work | 0.18μm<br>CMOS | 10.29-11.1<br>21.16-22.93 | 1.8                      | 15.2                      | 0.81<br>1.77          | -9.1*<br>-13.5*        | -115.9*<br>-106.8*                   | -184.63*<br>-181.81* |        |

TABLE II

PERFORMANCE COMPARISONS OF HIGH-FREQUENCY MULTIBAND CMOS VCOs

average value of all frequency ranges

the best value in all frequency ranges

measured at 2.5 MHz offset

measured at 10 MHz offset

$$FOM = L\{\Delta f\} - 20\log_{10}(\frac{f_o}{\Delta f}) + 10\log_{10}(\frac{P_{DC,core}}{1 \text{mW}})$$

where  $C_{\text{tunable}}$  represents the tunable capacitance. Equation (29) shows that the frequency sensitivity of the typical capacitive tuning decreases with 1.5th power of increasing the varactor capacitance. While operating at the high-frequency mode, the proposed VCO can be regarded as two sub-VCOs with the common virtual ground. Therefore, the high-band  $S_C$ curves in Fig. 18(b) exhibit the similar trend as the frequency sensitivity of the conventional capacitive tuning; the changes of the high-band  $S_C$ 's are gradually saturated as  $\kappa_C > 3$ . Meanwhile, the relatively flat low-band  $S_C - \kappa_C$  characteristics occur at  $3 < \kappa_C < 3.5$ . Therefore, we selected  $3 < \kappa_C < 3.5$ for this design to improve the linearity of the frequency tuning in both bands, which is accomplished by the varactor arrays in  $VCO_1$ . Since Fig. 18(a) shows that the low-band  $S_L$  increases with increasing  $\kappa_C$ , and the high-band  $S_L$  follows the opposite trend with more rapid speed, choosing  $3 < \kappa_C < 3.5$  is also a benefit to optimize  $S_L$ 's in both frequency bands.

## V. EXPERIMENTAL RESULTS

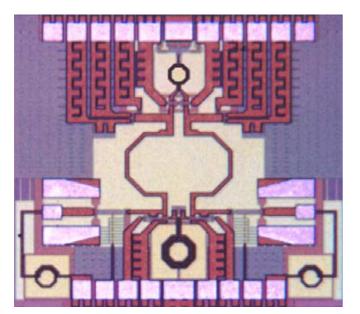

The proposed dual-band VCO was implemented in a standard 1P6M 0.18- $\mu$ m CMOS process. The chip microphotograph is shown in Fig. 19. The total chip area including the buffer transistors and the probing pads is  $1.25 \times 1.38 \text{ mm}^2$ . The core circuit area is approximately  $1.0 \times 0.75 \text{ mm}^2$ .

The circuit performances were characterized by on-wafer probing. While  $V_{GN}=0.85~\rm V$  with the supply voltages of 1.8 and 1.5 V, the core circuit and the buffer stages consume dc power of 15.2 and 14.1 mW, respectively. The circuit operates at the 10- and 22-GHz bands, while the controlled voltage applied to the switching varactors is set to -1.8 and  $1.8~\rm V$ , respectively, the coarse tuning is achieved by the digital varactors of  $C_{p,\rm var}$ , which operate at 0 or 1.8 V, and the fine tuning is performed by the varactor  $C_{n,\rm var}$ , as its controlled voltage ranges from  $-1.8~\rm to~1.8~\rm V$ . The tuning characteristics in both bands are illustrated in Fig. 20, where the low-band oscillation

frequency is from 10.29 to 11.11 GHz, and the high-band oscillation frequency is from 21.16 to 22.93 GHz.

The output spectrums were measured by an Agilent E4448 instrument and are shown in Fig. 21. In both oscillation modes, the measured spectrum only exhibits the fundamental carrier and the harmonics. The spurs due to undesired oscillation mode can be effectively suppressed and are below the noise floor of the measurement environment in both bands, therefore verifying the effectiveness of the proposed band-switching technique. Besides, the measured output signals also present the high-order rejections better than 25 dB in both bands. Fig. 22 shows the measured output power. The low-band carrier power is from -8.5 to -9.5 dBm, and the high-band carrier power is from -12.6 to -14.3 dBm. The average output powers in the 10- and 22-GHz band are -9.1 and -13.5 dBm, respectively.

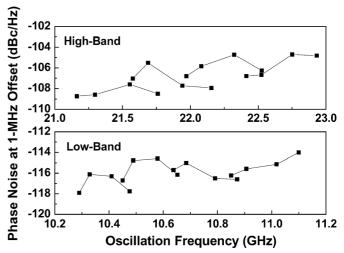

The close-in phase-noise characteristics were measured by an Agilent E5052 system and are shown in Fig. 23. To evaluate the circuit performance over the entire frequency range, phase noise at 1-MHz offset across both major bands was measured and displayed in Fig. 24, where the average phase noise in 10- and 22-GHz bands are -115.9 and -106.8 dBc/Hz, respectively.

Table II summarizes the performances of this circuit and other high-frequency multiband VCOs for comparison. The average figures-of-merit (FOMs) of the proposed VCO are -184.63 and -181.81 dBc/Hz for the low- and high-band operations, respectively. These performances are comparable with advanced multiband CMOS VCOs, indicating an expected balance between the circuit performance and the dissipated power.

## VI. CONCLUSION

A dual-band VCO that can operate at 10- and 22-GHz frequency bands has been designed and fabricated in a standard 0.18- $\mu$ m CMOS technology. This circuit utilizes the novel switching manner to control the oscillation modes and to realize the frequency-band switching. The average phase noises

are -115.9 and -106.8 dBc/Hz at 1-MHz offset frequency in 10- and 22-GHz bands, respectively. The FOMs are -184.63 and -181.81 dBc/Hz in 10- and 22-GHz bands, respectively, while the VCO core draws a dc current of 8.44 mA from a 1.8-V supply. The performances of this VCO compare well with the advanced high-frequency multiband VCOs.

#### ACKNOWLEDGMENT

The authors would like to thank the National Chip Implementation Center (CIC), Hsinchu, Taiwan, for chip fabrication.

#### REFERENCES

- A. Kral, F. Behbahani, and A. A. Abidi, "RF-CMOS oscillators with switched tuning," in *Proc. IEEE Custom Integr. Circuits Conf.*, 1998, pp. 555–558

- [2] A. Jayaraman, B. Terry, B. Fransis, P. Sullivan, M. Lindstrom, and J. O'Connor, "A fully integrated broadband direct-conversion receiver for DBS applications," in *IEEE Int. Solid-State Circuits Conf. Tech. Dig.*, Feb. 2000, pp. 140–141.

- [3] J. M. Mourant, J. Imbornonr, and T. Tewksbury, "A low phase noise monolithic VCO in SiGe BiCMOS," in *IEEE Radio Freq. Integr. Circuits Symp. Dig.*, Jun. 2000, pp. 65–68.

[4] S. Li, I. Kipnis, and M. Ismail, "A 10-GHz CMOS quadrature *LC*-VCO

- [4] S. Li, I. Kipnis, and M. Ismail, "A 10-GHz CMOS quadrature LC-VCO for multirate optical applications," *IEEE J. Solid-State Circuits*, vol. 38, no. 10, pp. 1626–1634, Oct. 2003.

- [5] A. D. Berny, A. M. Niknejad, and R. G. Meyer, "A 1.8-GHz LC-VCO with 1.3-GHz tuning range and digital amplitude calibration," *IEEE J. Solid-State Circuits*, vol. 40, no. 4, pp. 909–917, Apr. 2005.

- [6] Y. J. Moon, Y. S. Roh, C. Y. Jeong, and C. Yoo, "A 4.39–5.26 GHz LC-tank CMOS voltage-controlled oscillator with small VCO-gain variation," *IEEE Microw. Wireless Compon. Lett.*, vol. 19, no. 8, pp. 524–526, Aug. 2009.

- [7] F. Herzel, H. Erzgraber, and N. Ilkov, "A new approach to fully integrated CMOS LC-oscillator with a very large tuning range," in Proc. IEEE Custom Integr. Circuits Conf., May 2000, pp. 573–576.

- [8] L. Geynet, E. De Foucauld, P. Vincent, and G. Jacquemod, "Fully-in-tegrated multi-standard VCOs with switched LC tank and power controlled by body voltage in 130 nm CMOS/SOI," in IEEE Radio Freq. Integr. Circuits Symp. Dig., Jun. 2006, pp. 129–132.

- [9] S. M. Yim and K. K. O. Kenneth, "Switched resonators and their applications in a dual-band monolithic CMOS LC-tuned VCO," IEEE Trans. Microw. Theory Tech., vol. 54, no. 1, pp. 74–81, Jan. 2006.

- [10] H. L. Kao, D. Y. Yang, A. Chin, and S. P. McAlister, "A 2.4/5 GHz dual-band VCO using a variable inductor and switched resonator," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2007, pp. 1533–1536.

- [11] B. Çatlı and M. M. Hella, "A dual band, wide tuning range CMOS voltage controlled oscillator for multi-band radio," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2007, pp. 595–598.

- [12] G. Cusmai, M. Repossi, G. Albasini, and F. Svelto, "A 3.2-to-7.3 GHz quadrature oscillator with magnetic tuning," in *IEEE Int. Solid-State Circuits Conf. Tech. Dig.*, 2007, pp. 92–94.

- [13] S. Ko, J. G. Kim, S. E. Yoon, and S. Hong, "K- and Q-bands CMOS frequency sources with X-band quadrature VCO," *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 9, pp. 2789–2800, Sep. 2005.

- [14] H. H. Hsieh, Y. C. Hsu, and L. H. Lu, "A 15/30-GHz dual-band multiphase voltage-controlled oscillator in 0.18-μm CMOS," *IEEE Trans. Microw. Theory Tech.*, vol. 55, no. 3, pp. 474–483, Mar. 2007.

- [15] N. T. Tchamov, S. S. Broussev, I. S. Uzunov, and K. K. Rantala, "Dual band LC-VCO architecture with a fourth-order resonator," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 54, no. 3, pp. 277–281, Mar. 2007.

- [16] S. L. Jang, Y. K. Wu, C. C. Liu, and J. F. Huang, "A dual-band CMOS voltage-controlled oscillator implemented with dual-resonance *LC* tank," *IEEE Microw. Wireless Compon. Lett.*, vol. 19, no. 12, pp. 816–818, Dec. 2009.

- [17] R. Aparicio and A. Hajimiri, "A noise-shifting differential colpitts VCO," *IEEE J. Solid-State Circuits*, vol. 37, no. 12, pp. 1728–1736, Dec. 2002.

- [18] H. H. Hsieh and L. H. Lu, "A high-performance CMOS voltage-controlled oscillator for ultra-low-voltage operations," *IEEE Trans. Microw. Theory Tech.*, vol. 55, no. 3, pp. 467–473, Mar. 2007.

- [19] B. Razavi, Design of Analog CMOS Integrated Circuits. New York: McGraw-Hill, 2001.

- [20] M. Demirkan, S. P. Bruss, and R. R. Spencer, "Design of wide tuningrange CMOS VCOs using switched coupled-inductors," *IEEE J. Solid-State Circuits*, vol. 43, no. 5, pp. 1156–1163, May 2008.

- [21] R. M. Weng, T. J. Hsiao, and C. Y. Liu, "A dual-band voltage-controlled oscillator for SONET OC-768 application," in *Proc. IEEE Int. Circuits Syst. Symp.*, 2009, pp. 1297–1300.

- [23] S. Saberi and J. Paramesh, "A 11.5–22 GHz dual-resonance transformer-coupled quadrature VCO," in *IEEE Radio Freq. Integr. Circuits Symp. Dig.*, Jun. 2010, pp. 1–4.

- [24] J. Borremans, A. Bevilacqua, S. Bronckers, M. Dehan, M. Kuijk, P. Wambacq, and J. Craninckx, "A compact wideband front-end using a single-inductor dual-band VCO in 90 nm digital CMOS," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 2693–2619, Dec. 2008.

Szu-Ling Liu, photograph and biography not available at time of publication.

Kuan-Han Chen, photograph and biography not available at time of publication.

**Albert Chin** (SM'94–F'11) received the Ph.D. degree in electrical engineering from The University of Michigan at Ann Arbor, in 1989.

He was with AT&T-Bell Laboratories, the General Electric-Electronic Laboratory, and visited Texas Instruments Incorporated-SPDC. He is currently a Professor with the National Chiao Tung University, Hsinchu, Taiwan, and a Visiting Professor with the Si Nano Device Laboratory, National University of Singapore, Singapore. He was the Vice Executive Officer of the Diamond Project and Deputy Director of

the Multi-Disciplinary Research Center, National Chiao Tung University.

Dr. Chin has served as a panelist for the Device Research Conference. He has been a Distinguished Lecturer for the IEEE Electron Device Society, IEDM Executive Committee, etc.