# Impact of Quantum Confinement on Backgate-Bias Modulated Threshold-Voltage and Subthreshold Characteristics for Ultra-Thin-Body GeOI MOSFETs

Chang-Hung Yu, Student Member, IEEE, Yu-Sheng Wu, Student Member, IEEE, Vita Pi-Ho Hu, Student Member, IEEE, and Pin Su, Member, IEEE

Abstract—This paper investigates the impact of quantum confinement (QC) on the backgate-bias  $(V_{

m bg})$  modulated subthreshold and threshold-voltage  $(V_{

m th})$  characteristics of ultra-thin-body germanium-on-insulator (UTB GeOI) MOSFETs using an analytical solution of the Schrödinger equation verified with TCAD numerical simulation. Our study indicates that the OC effect reduces the sensitivity of the subthreshold swing to  $V_{

m bg}.$  In addition, the sensitivity of  $V_{

m th}$  to  $V_{

m bg}$  can be enhanced by the QC effect particularly for electrostatically well-behaved UTB MOSFETs with triangular potential well. Aside from that, the sensitivity of  $V_{

m th}$  roll-off to  $V_{

m bg}$  is reduced by the QC effect. Since Ge and Si channels exhibit different degrees of QC due to different quantization effective mass, the impact of QC has to be considered when one-to-one comparisons between GeOI and SOI MOSFETs regarding the backgate-bias modulated threshold-voltage and subthreshold characteristics are made. Our study may provide insights for multi- $V_{\rm th}$  device/circuit designs using advanced UTB GeOI technologies.

Index Terms—Backgate bias, germanium-on-insulator (GeOI), quantum confinement (QC), ultra-thin body (UTB).

## I. INTRODUCTION

**B** ECAUSE of the enhanced carrier transport property and current drive, germanium as a channel material has been proposed to enable the mobility scaling for CMOS devices [1]–[3]. The higher permittivity however makes Ge more susceptible to short-channel effects (SCEs). One of the promising solutions is to use the ultra-thin-body (UTB) structure with thin buried oxide (BOX). In addition to better control of SCEs, compatibility with mainstream planar CMOS technology, and small threshold voltage  $(V_{\rm th})$  variability due to the use of undoped (or lightly-doped) channel [4]–[6], using the UTB with thin

Manuscript received January 9, 2012; revised March 2, 2012; accepted March 22, 2012. Date of publication May 9, 2012; date of current version June 15, 2012. This work was supported in part by the National Science Council of Taiwan under contract NSC 100-2628-E-009-024-MY2 and in part by the Ministry of Education in Taiwan under the ATU program. The review of this paper was arranged by Editor H. S. Momose.

The authors are with the Department of Electronics Engineering & Institute of Electronics, National Chiao Tung University, Hsinchu 30010, Taiwan (e-mail: pinsu@faculty.nctu.edu.tw).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2012.2194499

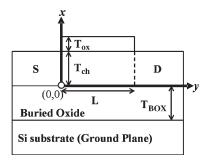

Fig. 1. Schematic sketch of a UTB structure with thin BOX. The origin point is located at the channel/BOX interface of the source/channel junction. L is the channel length.  $T_{\rm ch},\,T_{\rm ox}$ , and  $T_{\rm BOX}$  are the thicknesses of the channel, the gate oxide, and the BOX, respectively. The doping concentration of the Si ground plane is  $1\times 10^{20}$  cm $^{-3}$  (p-type).

BOX structure also enables more efficient  $V_{\rm th}$  modulation and power/performance optimization through backgate bias  $V_{\rm bg}$  [7], [8]. With the scaling of channel thickness  $T_{\rm ch}$ , the quantum-confinement (QC) effect along the channel-thickness direction may become significant and impact pertinent backgate-bias modulated  $V_{\rm th}$  and subthreshold characteristics of scaled UTB devices. In this paper, using an analytical solution of the Schrödinger equation [9] verified with TCAD numerical simulation, we investigate the impact of QC on the backgate modulation of UTB germanium-on-insulator (GeOI) MOSFETs. Our results will be also compared with the silicon-on-insulator (SOI) counterparts.

This paper is organized as follows: In Section II, we present the analytical solution of the Schrödinger equation for UTB MOSFETs with thin BOX under the subthreshold region. In Section III, we investigate the impact of QC on the backgate-bias modulated subthreshold swing (SS) of GeOI devices. The examination of the backgate-bias modulated  $V_{\rm th}$  characteristics considering the QC effect for UTB GeOI MOSFETs is presented in Section IV. Finally, the conclusions are drawn in Section V.

# II. QUANTUM-CONFINEMENT MODEL AND VERIFICATION

Fig. 1 shows a schematic sketch of a UTB structure with thin BOX and ground plane. To consider the QC effect along the channel-thickness (i.e., x) direction, the 1-D Schrödinger equation can be expressed as

$$-\frac{\hbar^2}{2m_x} \cdot \frac{d^2\Psi_j(x)}{dx^2} + E_C(x) \cdot \Psi_j(x) = E_j \cdot \Psi_j(x) \quad (1)$$

where  $E_j$  is the jth eigenenergy,  $\Psi_j$  is the corresponding wave function, and  $m_x$  is the carrier quantization effective mass [10]. For long-channel undoped UTB MOSFETs, the conduction band edge  $E_C(x)$  was usually treated as a triangular well in the past [11]. However, to account for the drain–source coupling for short-channel UTB MOSFETs, the conduction band edge  $E_C(x)$  in (1) should be treated as a parabolic well [12] with potential energy  $E_C(x) = \alpha x^2 + \beta x + \gamma$ , where  $\alpha$ ,  $\beta$ , and  $\gamma$  are channel-length-dependent coefficients and can be obtained from the channel potential solution of Poisson's equation under the subthreshold region [13]. Using the parabolic-well treatment, the solution of (1) can be expressed as [14]

$$\Psi_j = \sum_n d_n \cdot x^n \tag{2}$$

by using the power series method with the following coefficients  $d_n$ :

$$\begin{split} d_2 &= -\frac{m_x}{\hbar^2} (E_j - \gamma) \cdot d_0 \\ d_3 &= -\frac{m_x}{3\hbar^2} \left[ (E_j - \gamma) \cdot d_1 - \beta \cdot d_0 \right] \\ d_n &= -\frac{2m_x}{n(n-1)\hbar^2} \\ &\times \left[ (E_j - \gamma) \cdot d_{n-2} - \beta \cdot d_{n-3} - \alpha \cdot d_{n-4} \right], \ n \geq 4. \quad (3) \end{split}$$

The jth eigenenergy  $E_j$  can be determined by the boundary condition  $\Psi_j(x=0)=\Psi_j(x=T_{\rm ch})=0$  with x=0 and  $x=T_{\rm ch}$  defined as the interfaces of BOX/channel and channel/gate-oxide, respectively. Thus, the eigenenergies and the wave functions of short-channel UTB MOSFETs under the subthreshold region can be derived. Using the calculated eigenenergies and wave functions, we can calculate the channel electron density by [10]

$$n(x,y)$$

$$= N_{C,QM}(x,y) \cdot \exp\left(\frac{E_F(y) - E_C(x,y)}{kT}\right)$$

(4a)

$N_{C,QM}(x,y)$

$$= \sum_{\nu} \left\{ \frac{d_{\nu} m_{d,\nu} kT}{\pi \hbar^2} \cdot \sum_{j} \left[ \exp\left(\frac{E_C(x,y) - E_{j,\nu}}{kT}\right) \cdot |\Psi_{j,\nu}(x,y)|^2 \right] \right\}$$

(4b)

where  $\nu$  is the type of valley,  $d_{\nu}$  is the degeneracy of the valley,  $m_{d,\nu}$  is the corresponding density-of-state effective mass [10],

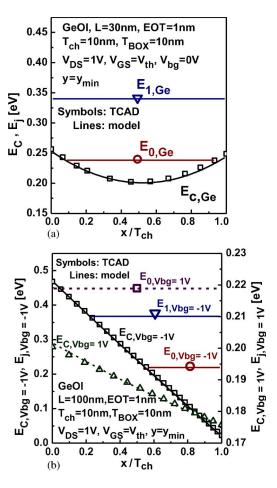

Fig. 2. Conduction band edge and quantized eigenenergies of UTB GeOI MOSFETs. (a) Short-channel devices with parabolic well at  $V_{\rm bg}=0~{\rm V.}~V_{\rm th}=0.18~{\rm V.}$  (b) Long-channel devices with triangular well for  $V_{\rm bg}=-1~{\rm V}$  and  $V_{\rm bg}=1~{\rm V.}$  The corresponding  $V_{\rm th}=0.66~{\rm V}$  for  $V_{\rm bg}=-1~{\rm V}$  and  $V_{\rm th}=0.33~{\rm V}$  for  $V_{\rm bg}=1~{\rm V.}~y_{\rm min}$  is where the minimum potential occurs for the carrier flow along the channel-length direction.

and  $E_F(y)$  is the quasi-Fermi level along the channel-length (i.e., y) direction. In other words, the impact of quantized eigenenergies and wave functions on the electron density is incorporated into the effective density of state for the conduction band  $(N_{C,QM})$  [15]. Using  $N_{C,QM}$ , the subthreshold drain current can be derived by [16], [17]

$$I_{DS} = \frac{q\mu_n W\left(\frac{kT}{q}\right) \cdot \left[1 - \exp\left(-\frac{qV_{DS}}{kT}\right)\right]}{\int_0^L \frac{dy}{\int_0^{T_{ch}} N_{C,QM}(x,y) \cdot \exp\left(\frac{-E_C(x,y)}{kT}\right) dx}}$$

(5)

where  $\mu_n$  is the electron mobility, W is the channel width, and kT/q is the thermal voltage.

We have verified our QC model using TCAD simulation that numerically solves the self-consistent solution of the 2-D Poisson and 1-D Schrödinger equations [18]. Fig. 2(a) and (b) show that, for both the parabolic potential well of short-channel devices and the triangular well of long-channel devices with forward and reverse  $V_{\rm bg}$ , the  $E_j$  values calculated by our model are fairly accurate. It should be noted that a scalable QC model with accurate channel-length and backgate-bias dependence is crucial to this study.

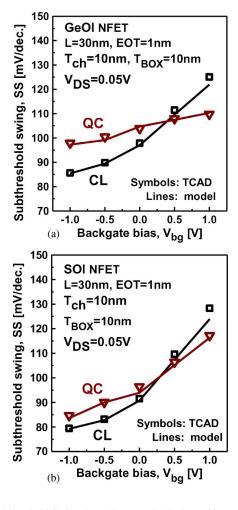

Fig. 3. Subthreshold Swing dependence on the backgate bias. (a) Impact of QC on the SS of the Ge device. (b) Impact of QC on the SS of the Si device.

# III. IMPACT OF QC ON BACKGATE-BIAS MODULATED SUBTRESHOLD SWING

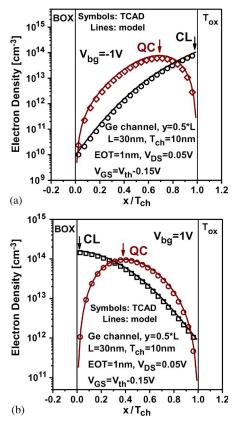

Fig. 3 compares the impact of QC on the backgate-bias modulated SS characteristic for GeOI and SOI devices. It can be seen that the SS significantly increases with increasing  $V_{\rm bg}$ (i.e., from reverse to forward backgate bias) under the classical (CL) condition. However, as the QC effect is considered, the sensitivity of SS to  $V_{

m bg}$  reduces. This can be explained by Fig. 4. In Fig. 4(a) with  $V_{\rm bg} = -1$  V, the electron conduction path under the CL condition is located at the frontgate interface. After considering the QC effect, the electron conduction path is shifted toward the channel center so that the SS increases. In Fig. 4(b) with  $V_{\rm bg}=1$  V, on the contrary, the electron conduction path under the CL condition is located at the backgate interface, whereas the QC effect brings the carriers toward the channel center and thus reduces the SS. As a consequence, the GeOI device shows reduced sensitivity of SS to  $V_{

m bg}$  when the QC effect is considered [see Fig. 3(a)]. Although the SOI device also shows reduced sensitivity of SS to  $V_{

m bg}$  due to the QC effect [see Fig. 3(b)], it should be noted that the GeOI device exhibits less sensitivity of SS to  $V_{\rm bg}$  than the SOI counterpart because Ge possesses smaller quantization effective mass than Si.

Fig. 4. Electron density distribution for the GeOI device in the subthreshold region under (a) reverse backgate bias with  $V_{\rm bg}=-1~{\rm V}$  and (b) forward backgate bias with  $V_{\rm bg}=1~{\rm V}$ . The arrow tip indicates the electron conduction path.

# IV. IMPACT OF QC ON BACKGATE-BIAS MODULATED $V_{ m th}$ CHARACTERISTICS

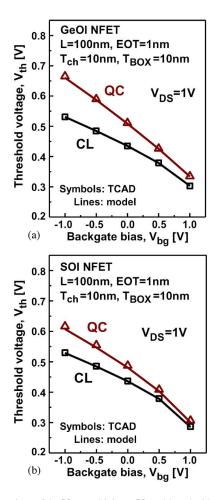

Fig. 5 compares the impact of QC on the backgate-bias modulated  $V_{\rm th}$  characteristic for UTB GeOI and SOI devices with L=100 nm. It can be seen that, as the QC effect is considered, the sensitivity of  $V_{\rm th}$  to  $V_{\rm bg}$  increases for both the GeOI and SOI devices. This is because an electrostatically well-behaved UTB MOSFET possesses a triangular channel potential well. As indicated in Fig. 2(b), the slope of the triangular well increases as  $V_{\rm bg}$  changes from forward to reverse bias. In other words, the impact of QC increases with decreasing  $V_{\rm bg}$ . It is also worth noting that the GeOI device exhibits higher sensitivity of  $V_{\rm th}$  to  $V_{\rm bg}$  than the SOI counterpart because of its smaller quantization effective mass.

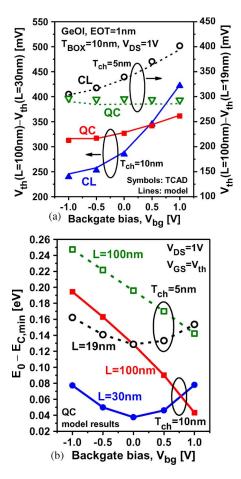

Fig. 6(a) shows the impact of QC on the backgate-bias modulated  $V_{\rm th}$  roll-off characteristic for GeOI devices with various channel thicknesses. It can be seen that the  $V_{\rm th}$  roll-off substantially increases with increasing  $V_{\rm bg}$  under the CL condition. This is because the carrier centroid is moved toward the backgate interface when  $V_{\rm bg}$  changes from reverse to forward bias for a GeOI NFET. As the QC effect is considered, however, the sensitivity of the  $V_{\rm th}$  roll-off to  $V_{\rm bg}$  is significantly reduced for the devices with  $T_{\rm ch}=10$  nm and  $T_{\rm ch}=5$  nm. This can be explained as follows. The QC-induced  $V_{\rm th}$  shift  $(\Delta V_{\rm th}^{\rm QM})$  can be approximated as

$$\Delta V_{\rm th}^{\rm QM} \approx {\rm SS} / \left( \ln 10 \cdot \frac{kT}{q} \right) \cdot \Delta \phi_s^{\rm QM}$$

(6)

Fig. 5. Comparison of the  $V_{\rm th}$  sensitivity to  $V_{\rm bg}$  with and without considering the QC effect for (a) Ge-channel and (b) Si-channel UTB devices with L=100 nm.

with  $\Delta\phi_s^{\mathrm{QM}}$  being the equivalent surface potential shift [19] due to the QC effect. For the devices with  $T_{\rm ch}=10$  nm, although the SS of the long-channel device (L = 100 nm) is smaller than that of the short-channel one (L = 30 nm), the ground-state eigenenergy  $(E_0 - E_{C,\min})$  (and, hence,  $\Delta \phi_s^{QM}$ ) of the longchannel device is essentially much larger than that of the shortchannel one at  $V_{\rm bg} = -1$  V, as shown in Fig. 6(b), due to its sharp triangular potential well (see Fig. 2). This results in larger  $\Delta V_{

m th}^{

m QM}$  for the long-channel device and explains why the QC increases the  $V_{

m th}$  roll-off of the GeOI devices with  $T_{

m ch}=10$  nm at  $V_{\rm bg} = -1$  V in Fig. 6(a). However,  $(E_0 - E_{C,\rm min})$  as well as  $\Delta V_{\rm th}^{\rm \bar{QM}}$  of the long-channel device substantially decrease with increasing  $V_{\rm bg}$ , as shown in Fig. 6(b), because of the strong  $V_{\rm bg}$ modulation of its triangular well [see Fig. 2(b)]. This explains why in Fig. 6(a) the sensitivity of the  $V_{\rm th}$  roll-off to  $V_{\rm bg}$  with  $T_{\rm ch}=10$  nm decreases as the QC effect is considered.

For the devices with  $T_{\rm ch}=5$  nm, it can be seen from Fig. 6(a) that the  $V_{\rm th}$  roll-off considering the QC effect is smaller than the CL one at  $V_{\rm bg}=1$  V. This is because the short-channel device (L=19 nm) possesses larger SS and, hence, larger QC-induced  $V_{\rm th}$  shift ( $\Delta V_{\rm th}^{\rm QM}$ ) than that of the long-channel device (L=100 nm). However, ( $E_0-E_{C,\rm min}$ ) as well as  $\Delta \phi_s^{\rm QM}$  of the long-channel device increase as  $V_{\rm bg}$  decreases from forward to reverse bias [see Fig. 6(b)] and

Fig. 6. (a) Sensitivity of  $V_{\rm th}$  roll-off to  $V_{\rm bg}$  is significantly reduced by the QC effect for UTB GeOI devices. The SS of the device designed with  $(T_{\rm ch}=5~{\rm nm},L=19~{\rm nm})$  is comparable with that of the device with  $(T_{\rm ch}=10~{\rm nm},L=30~{\rm nm})$  at  $V_{\rm bg}=0~{\rm V}$  under the CL condition. (b) Calculated  $V_{\rm bg}$  dependence of the ground-state eigenenergy for long- and short-channel UTB GeOI devices with  $T_{\rm ch}=10~{\rm nm}$  and  $T_{\rm ch}=5~{\rm nm}$ , respectively.

counterbalances the impact from SS. Therefore, the sensitivity of the  $V_{\rm th}$  roll-off to  $V_{\rm bg}$  for the GeOI devices with  $T_{\rm ch}=5$  nm is reduced as the QC effect is considered.

### V. CONCLUSION

Using an analytical solution of the Schrödinger equation verified with TCAD numerical simulation, we have demonstrated that the QC effect can significantly impact the pertinent backgate-bias modulated subthreshold and threshold-voltage characteristics of UTB GeOI devices. Our study has indicated that the QC effect reduces the sensitivity of SS to  $V_{

m bg}$ . In addition, the sensitivity of  $V_{

m th}$  to  $V_{

m bg}$  can be enhanced by the QC effect especially for electrostatically well-behaved UTB MOSFETs with triangular potential well. Aside from that, the sensitivity of  $V_{\rm th}$  roll-off to  $V_{\rm bg}$  is reduced by the QC effect. Since Ge and Si channels exhibit different degrees of QC due to different quantization effective mass, the impact of QC has to be considered when one-to-one comparisons between GeOI and SOI MOSFETs regarding the backgate-bias modulated threshold-voltage and subthreshold characteristics are made.

### REFERENCES

- [1] [Online]. Available: http://www.itrs.net/

- [2] E. Pop, C. O. Chui, S. Sinha, R. Dutton, and K. Goodson, "Electrothermal comparison and performance optimization of thin-body SOI and GOI MOSFETs," in *IEDM Tech. Dig.*, 2004, pp. 411–414.

- [3] S. W. Bedell, A. Majumdar, J. A. Ott, J. Arnold, K. Fogel, S. J. Koester, and D. K. Sadana, "Mobility scaling in short-channel length strained Ge-on-insulator P-MOSFETs," *IEEE Electron Device Lett.*, vol. 29, no. 7, pp. 811–813, Jul. 2008.

- [4] Q. Liu, A. Yagishita, N. Loubet, A. Khakifirooz, P. Kulkarni, T. Yamamoto, K. Cheng, M. Fujiwara, J. Cai, D. Dorman, S. Mehta, P. Khare, K. Yako, Y. Zhu, S. Mignot, S. Kanakasabapathy, S. Monfray, F. Boeuf, C. Koburger, H. Sunamura, S. Ponoth, A. Reznicek, B. Haran, A. Upham, R. Johnson, L. F. Edge, J. Kuss, T. Levin, N. Berliner, E. Leobandung, T. Skotnicki, M. Hane, H. Bu, K. Ishimaru, W. Kleemeier, M. Takayanagi, B. Doris, and R. Sampson, "Ultra-thin-body and BOX (UTBB) fully depleted (FD) device integration for 22 nm node and beyond," in VLSI Symp. Tech. Dig., Jun. 2010, pp. 61–62.

- [5] O. Weber, O. Faynot, F. Andrieu, C. Buj-Dufournet, F. Allain, P. Scheiblin, J. Foucher, N. Daval, D. Lafond, L. Tosti, L. Brevard, O. Rozeau, C. Fenouillet-Beranger, M. Marin, F. Boeuf, D. Delprat, K. Bourdelle, B.-Y. Nguyen, and S. Deleonibus, "High immunity to threshold voltage variability in undoped ultra-thin FDSOI MOSFETs and its physical understanding," in *IEDM Tech. Dig.*, Dec. 2008, pp. 1–4.

- [6] K. Cheng, A. Khakifirooz, P. Kulkarni, S. Kanakasabapathy, S. Schmitz, A. Reznicek, T. Adam, Y. Zhu, J. Li, J. Faltermeier, T. Furukawa, L. F. Edge, B. Haran, S.-C. Seo, P. Jamison, J. Holt, X. Li, R. Loesing, Z. Zhu, R. Johnson, A. Upham, T. Levin, M. Smalley, J. Herman, M. Di, J. Wang, D. Sadana, P. Kozlowski, H. Bu, B. Doris, and J. O'Neill, "Fully depleted extremely thin SOI technology fabricated by a novel integration scheme featuring implant-free, zero-silicon-loss, and faceted raised source/drain," in VLSI Symp. Tech. Dig., Jun. 2009, pp. 212–213.

- [7] F. Andrieu, O. Weber, J. Mazurier, O. Thomas, J.-P. Noel, C. Fenouillet-Beranger, J.-P. Mazellier, P. Perreau, T. Poiroux, Y. Morand, T. Morel, S. Allegret, V. Loup, S. Barnola, F. Martin, J.-F. Damlencourt, I. Servin, M. Casse, X. Garros, O. Rozeau, M.-A. Jaud, G. Cibrario, J. Cluzel, A. Toffoli, F. Allain, R. Kies, D. Lafond, V. Delaye, C. Tabone, L. Tosti, L. Brevard, P. Gaud, V. Paruchuri, K. K. Bourdelle, W. Schwarzenbach, O. Bonnin, B.-Y. Nguyen, B. Doris, F. Buf, T. Skotnicki, and O. Faynot, "Low leakage and low variability ultra-thin body and buried oxide (UT2B) SOI technology for 20 nm low power CMOS and beyond," in VLSI Symp. Tech. Dig., Jun. 2010, pp. 57–58.

- [8] C. Fenouillet-Béranger, O. Thomas, P. Perreau, J.-P. Noel, A. Bajolet, S. Haendler, L. Tosti, S. Barnola, R. Beneyton, C. Perrot, C. de Buttet, F. Abbate, F. Baron, B. Pernet, Y. Campidelli, L. Pinzelli, P. Gouraud, M. Casse, C. Borowiak, O. Weber, F. Andrieu, S. Denorme, F. Boeuf, O. Faynot, T. Skotnicki, K. K. Bourdelle, B. Y. Nguyen, and F. Boedt, "Efficient multi-VT FDSOI technology with UTBOX for low power circuit design," in VLSI Symp. Tech. Dig., Jun. 2010, pp. 65–66.

- [9] Y.-S. Wu, H.-Y. Hsieh, V. P.-H. Hu, and P. Su, "Impact of quantum confinement on short-channel effects for ultrathin-body Germanium-oninsulator MOSFETs," *IEEE Electron Device Lett.*, vol. 32, no. 1, pp. 18– 20, Jan. 2011.

- [10] F. Stern and W. E. Howard, "Properties of semiconductor surface inversion layers in the electric quantum limit," *Phys. Rev.*, vol. 163, no. 3, pp. 816–835, Nov. 1967.

- [11] V. P. Trivedi and J. G. Fossum, "Quantum-mechanical effects on the threshold voltage of undoped double-gate MOSFETs," *IEEE Electron Device Lett.*, vol. 26, no. 8, pp. 579–582, Aug. 2005.

- [12] Y.-S. Wu and P. Su, "Analytical quantum-confinement model for short-channel gate-all-around MOSFETs under subthreshold region," *IEEE Trans. Electron Devices*, vol. 56, no. 11, pp. 2720–2725, Nov. 2009.

- [13] V. P.-H. Hu, Y.-S. Wu, and P. Su, "Investigation of electrostatic integrity for ultrathin-body Germanium-on-nothing MOSFET," *IEEE Trans. Nanotechnol.*, vol. 10, no. 2, pp. 325–330, Mar. 2011.

- [14] D. G. Zill and M. R. Cullen, Differential Equations With Boundary Value Problems., 5th ed. Pacific Grove, CA: Brooks/Cole, 2001.

- [15] H. Ananthan and K. Roy, "A compact physical model for yield under gate length and body thickness variations in nanoscale double-gate CMOS," *IEEE Trans. Electron Devices*, vol. 53, no. 9, pp. 2151–2159, Sep. 2006.

- [16] Y.-S. Wu and P. Su, "Sensitivity of gate-all-around nanowire MOSFETs to process variation—A comparison with multigate MOSFETs," *IEEE Trans. Electron Devices*, vol. 55, no. 11, pp. 3042–3047, Nov. 2008.

- [17] X. Liang and Y. Taur, "A 2-D analytical solution for SCEs in DG MOSFETs," *IEEE Trans. Electron Devices*, vol. 51, no. 9, pp. 1385–1391, Sep. 2004.

- [18] ATLAS User's Manual, SILVACO, Santa Clara, CA, 2008.

- [19] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices. Cambridge, U.K.: Cambridge Univ. Press, 1998, p. 198.

**Chang-Hung Yu** (S'11) received the M.S. degree from the National Chiao Tung University, Hsinchu, Taiwan, in 2011. He is currently working toward the Ph.D. degree with the Institute of Electronics, National Chiao Tung University.

**Yu-Sheng Wu** (S'09) received the Ph.D. degree in electronics engineering from the National Chiao Tung University, Hsinchu, Taiwan, in 2011.

He is currently with Taiwan Semiconductor Manufacturing Company, Hsinchu, Taiwan.

**Vita Pi-Ho Hu** (S'09) received the Ph.D. degree from the National Chiao Tung University, Hsinchu, Taiwan, in 2011.

She is currently with the Department of Electronics Engineering and the Institute of Electronics, National Chiao Tung University.

**Pin Su** (S'98–M'02) received the Ph.D. degree from the University of California, Berkeley, Berkeley.

Since August 2003, he has been with the Department of Electronics Engineering, National Chiao Tung University, where he is currently a Full Professor.