# Experimental Verification of RF Stress Effect on Cascode Class-E PA Performance and Reliability

Jiann-Shiun Yuan, Senior Member, IEEE, Hsuan-Der Yen, Shuyu Chen, Student Member, IEEE, Ruey-Lue Wang, Guo-Wei Huang, Member, IEEE, Ying-Zong Juang, Chih-Ho Tu, Wen-Kuan Yeh, and Jun Ma

Abstract—A cascode class-E power amplifier (PA) operating at 5.2 GHz has been designed using Advanced Design System simulation. RF circuit performances such as output power and power-added efficiency before and after RF stress have been experimentally investigated. The measured output power, power-added efficiency, and linearity after high-input-power RF stress at elevated supply voltage show significant circuit degradations. The impact of hot-carrier injection and gate oxide soft breakdown on cascode class-E PA reliability is discussed.

Index Terms—Cascode class E, gate oxide breakdown, output power, power amplifier (PA), power efficiency, reliability.

#### I. Introduction

THE advancement in CMOS technology for high-frequency applications has made it a natural choice for integrated low-cost RF power amplifiers (PAs) for wireless communications ICs. Class-E PA topology has become popular due to its high power efficiency [1] and, therefore, a good candidate for low-cost high-integration portable communication systems such as cell phones, wireless local area networks, wireless sensor networks, global positioning systems, and Bluetooth applications.

A class-E amplifier with a shunt capacitor was introduced by Sokal and Sokal [2] and was examined by Raab in an analysis of idealized operation [3]. The active transistor in the class-E PA is used as a switch. The voltage and current waveforms are

Manuscript received July 27, 2011; revised September 6, 2011 and October 13, 2011; accepted October 13, 2011. Date of publication December 13, 2011; date of current version June 6, 2012.

- J.-S. Yuan and S. Chen are with the Department of Electrical Engineering and Computer Science, University of Central Florida, Orlando, FL 32816 USA (e-mail: yuanj@mail.ucf.edu).

- H.-D. Yen is with the Institute of Electronics Engineering, National Tsing Hua University, Hsinchu 300, Taiwan.

- R.-L. Wang is with the Department of Electronic Engineering, National Kaohsiung Normal University, Kaohsiung 824, Taiwan.

- G.-W. Huang is with the National Nano Device Laboratories, Hsinchu 300, Taiwan, and also with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan.

- Y.-Z. Juang is with the National Chip Implementation Center, National Applied Research Laboratories, Tainan 701, Taiwan.

- C.-H. Tu is with National Chung Cheng University, Chiayi 62102, Taiwan, and also with the National Chip Implementation Center, National Applied Research Laboratories, Tainan 701, Taiwan.

- W.-K. Yeh is with the Department of Electrical Engineering, National University of Kaohsiung, Kaohsiung 811, Taiwan.

- J. Ma is with Wuxi Bay Technology, Ltd., Wuxi 214000, China

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TDMR.2011.2179548

shaped by the LC tuning network such that they do not overlap, producing an ideal power efficiency value of 100%.

Due to aggressive scaling in device dimensions for improving speed and functionality, CMOS transistors in the deep submicrometer-to-nanometer regime have resulted in major reliability issues, including gate oxide breakdown [4] and channel hot-electron degradation [5], [6]. Class-E PA is very vulnerable to oxide stress because its drain voltage can approach more than three times of supply voltage  $V_{DD}$  ideally. To ensure the reliability of class-E PA operation,  $V_{DD}$  is conservatively selected to a lower value. However, low  $V_{DD}$  reduces a PA's output power and power efficiency.

A cascode topology is adopted in a class-E PA to divide the output voltage and decrease gate oxide stress effect [7]–[9]. The cascode topology is better than the noncascode structure due to reduced drain—gate voltage stress on the output transistor. In addition, a thick oxide of the cascode transistor may be used to alleviate oxide stress at the expense of reduced output voltage swing [10]. Note that prior publications [7]–[10] on class-E PA reliability issues focused on gate oxide stress, not on channel hot-electron injection. This motivates us to evaluate hot-electron effect on class-E PA degradations using experimental data and a mixed-mode device and circuit simulation.

In this paper, a cascode class-E PA is designed using an Advanced Design System simulation (ADS) simulation [11]. Measured PA performances after RF stress are analyzed. Section II illustrates the design of a cascode class-E PA operating at 5.2 GHz. The circuit performances, after the postlayout simulation, are demonstrated.

Section III presents RF stress experiments and class-E PA performance degradations after high input power and increased  $V_{DD}$  stress. Section IV discusses the reliability of cascode class-E PA subjected to hot-electron effect through the examination of impact ionization and lattice heating using the mixed-mode device and circuit simulation. Finally, conclusion is given in Section V.

### II. DESIGN OF A CASCODE CLASS-E PA

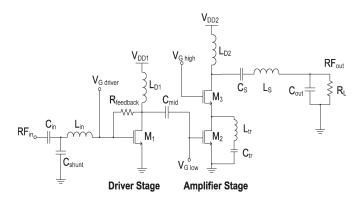

To evaluate the class-E PA reliability by experiments, a cascode class-E PA is designed for fabrication Fig. 1 shows the circuit schematics of a cascode class-E PA.

Using Taiwan Semiconductor Manufacturing Company (TSMC) 0.18- $\mu$ m mixed-signal CMOS technology, the class-E PA designed at 5.2 GHz is evaluated in the ADS simulation. Multifinger transistors with n-channel length of 0.18  $\mu$ m are

Fig. 1. Schematic of a cascode class-E PA.

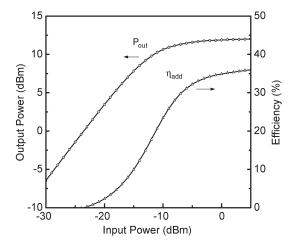

Fig. 2. Output power and power-added efficiency versus input power after postlayout simulation.

used. Driver transistor  $M_1$  has the channel width of 256  $\mu$ m. Main transistor  $M_2$  and cascode transistor  $M_3$  have the channel width of 512 and 544  $\mu$ m, respectively. The dc supply voltage  $V_{DD1}$  for the driver stage is set at 1 V. The supply voltage  $V_{DD2}$  for the main amplifier is selected to be at 2.4 V. To reduce power consumption, the gate of  $M_1$  is biased at 0.1 V (class-C mode of biasing). The gate dc voltages of  $M_2$  and  $M_3$  are at 0.7 and 1 V, respectively. The spiral inductor and capacitor values used in this design are  $L_{\rm in}=3.61$  nH,  $L_{D1}=1.47$  nH,  $L_{D2}=4.56$  nH,  $L_{\rm tr}=0.27$  nH,  $L_{S}=3.61$  nH,  $C_{\rm in}=398$  fF,  $C_{\rm shunt}=1.79$  pF,  $C_{\rm mid}=1.68$  pF,  $C_{\rm tr}=804$  fF,  $C_{S}=398$  fF, and  $C_{\rm OUT}=35.6$  fF. Feedback resistance  $R_{\rm feedback}$  is 600  $\Omega$ .

The cascode class-E PA was laid out using Cadence Virtuoso software [12], followed by successful Calibre DRC for design rule checking and LVS for layout versus schematic verification. The layout parasitic effects were extracted using the ADS Momentum (electromagnetic) simulation. The postlayout simulation result of output power and power-added efficiency ( $\eta$ add) as a function of input power is shown in Fig. 2.

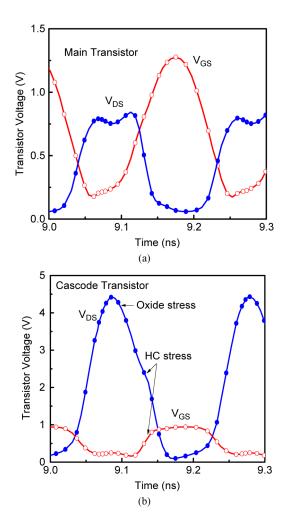

The gate–source and drain–source voltages as a function of time for the cascode and main transistors are shown in Fig. 3 to examine the electrical stress effect on this cascode class-E design. As shown in Fig. 3, the cascode transistor bears more voltage stress at the drain of  $M_3$  than that of main transistor  $M_2$ . At high input power, the cascode transistor could suffer

Fig. 3. (a) Simulated gate–source and drain–source voltages of the main transistor. In this simulation,  $P_{\rm in}=0$  dBm and  $V_{DD2}=2.4$  V. (b) Simulated gate–source and drain–source voltages of the cascode transistor. In this simulation,  $P_{\rm in}=0$  dBm and  $V_{DD2}=2.4$  V.

hot-electron effect when gate—source and drain—source voltages are high during switching transient [see Fig. 3(b)].

### III. RF STRESS EXPERIMENTS

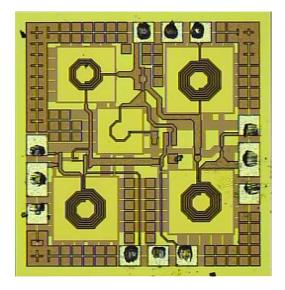

A silicon chip of the designed PA was fabricated using TSMC 0.18- $\mu$ m mixed-signal CMOS technology. The silicon chip is shown in Fig. 4, and its size is 820  $\times$  887  $\mu$ m<sup>2</sup>. In this figure, spiral inductors, capacitors, transistors, ground–signal–ground RF input and output pads, dc supply voltage pads, and gate bias pads are displayed.

The PA's performances before and after RF stress are measured. The measurement was performed at room temperature. The PA was then stressed with an RF input power value of 0 dBm and different  $V_{DD2}$  stress levels at 3.5, 4, or 4.5 V for 10 h. After continuous RF and elevated dc stresses, the RF parameters were measured again to compare with the experimental data obtained at the fresh circuit condition. For the circuit at the normal operation, dc biases of  $V_{G1} = 0.1 \text{ V}$ ,  $V_{G2} = 0.7 \text{ V}$ ,  $V_{DD1} = 1 \text{ V}$ , and  $V_{DD2} = 2.4 \text{ V}$  were used.

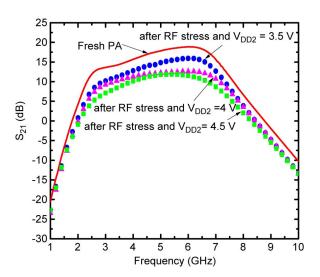

Fig. 5 shows the measured small-signal gain  $S_{21}$  versus frequency as a function of stress conditions. In Fig. 5, the solid

Fig. 4. Chip view of the cascode class-E PA used for RF stress and measurement.

Fig. 5. Measured  $S_{21}$  versus frequency before and after RF stress. During the RF stress,  $P_{\rm in}$  is at 0 dBm and  $V_{DD2}$  was kept at 3.5, 4, or 4.5 V.

line represents the fresh circuit result, the circles represent the PA's experimental data after 10 h of RF stress at  $V_{DD2}=3.5~\rm V$ , the triangles represent the data after 10 h of RF stress at  $V_{DD2}=4~\rm V$ , and the squares represent the measured result after 10 h of RF stress at  $V_{DD2}=4.5~\rm V$ . As shown in Fig. 5, the larger the elevated stress at high  $V_{DD2}$ , the larger the  $S_{21}$  degradation over a wide range of frequencies.

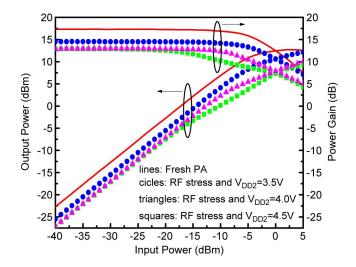

At 5.2 GHz, the measured output power and power gain are plotted in Fig. 6. The output power increases with input power and reaches a saturated output power value at high input power, thus making the power gain decrease at high input power. Both the output power and power gain decrease after RF stress, particularly when the  $V_{DD2}$  stress level is increased. The degradations of RF circuit performances are attributed to hotelectron effect on the output transistor. More detailed physical explanations are given in Section IV.

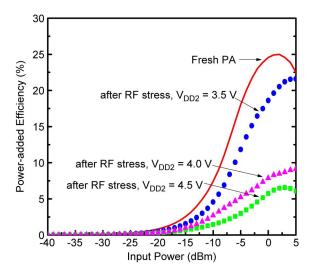

The measured power-added efficiency is illustrated in Fig. 7. Power-added efficiency increases with input power, reaches

Fig. 6. Measured output power and power gain versus input power before and after RF stress. During this RF stress,  $P_{\rm in}$  is at 0 dBm and  $V_{DD2}$  was kept at 3.5, 4, or 4.5 V.

Fig. 7. Measured power-added efficiency versus input power before and after RF stress at 5.2 GHz. During this RF stress,  $P_{\rm in}$  is at 0 dBm and  $V_{DD2}$  was kept at 3.5, 4, or 4.5 V.

saturation, and then decreases with input power due to reduced output power and increased dc power dissipation at very high input power. The power-added efficiency is defined as (RF output power–RF input power)/total dc power dissipation including the power stage's and driver stage's. Note that the power-added efficiency is lower than the drain efficiency because of additional power dissipation from the driver stage. At 5.2 GHz, the peak power-added efficiency of the fresh PA approaches 25% (a somewhat lower value than expected due to layout parasitic effect and additional dc power dissipation in the driver stage). After RF stress, the peak power efficiency significantly decreases, particularly when the  $V_{DD2}$  stress level is high.

Table I lists the small-signal gain  $S_{21}$  at 5.2 GHz, output power at the input power of 0 dBm, power gain (po/pi) at the input power of -20 dBm, and maximum power-added efficiency before and after RF stress. Their normalized parameter shifts such as  $\Delta S_{21}/S_{21}$ ,  $\Delta p_o/p_o$ ,  $\Delta (p_o/p_i)/(p_o/p_i)$ , and

| RF parameters                | S <sub>21</sub> @5.2 GHZ | p <sub>o</sub> @ p <sub>i</sub> =0dBm | p <sub>o</sub> @ p <sub>i</sub> =0dBm | peak η <sub>add</sub> |

|------------------------------|--------------------------|---------------------------------------|---------------------------------------|-----------------------|

| Fresh                        | 18.2 dB                  | 12.5 dBm                              | 17.3 dB                               | 25%                   |

| After RF stress <sup>1</sup> | 15.2 dB                  | 10.6 dBm                              | 14.5 dB                               | 21.6%                 |

| After RF stress <sup>2</sup> | 12.3 dB                  | 7.9 dBm                               | 12.9 dB                               | 9.1%                  |

| After RF stress <sup>3</sup> | 11.9 dB                  | 7.3 dBm                               | 12.5 dB                               | 6.6%                  |

| Change <sup>1</sup>          | -16.5%                   | -15.2%                                | -16.2%                                | -13.6%                |

| Change <sup>2</sup>          | -32.4%                   | -36.8%                                | -25.4%                                | -63.6%                |

| Change <sup>3</sup>          | -34.6%                   | -41.6%                                | -27.7%                                | -73.6%                |

TABLE I RF Parameter Degradations

$<sup>^{3}</sup>$  RF stress at  $p_{i} = 0$  dBm and  $V_{DD2} = 4.5V$  for 10 hours

Fig. 8. Measured  $S_{21}$  versus frequency before and after RF stress. During the RF stress,  $P_{\rm in}$  is at 0 dBm and  $V_{DD2}$  was kept at 3.5, 4, or 4.5 V.

$\Delta\eta_{\rm add}/\eta_{\rm add}\times 100\%$  from the fresh condition are also shown in Table I.

## IV. PHYSICAL INSIGHT THROUGH THE MIXED-MODE DEVICE AND CIRCUIT SIMULATION

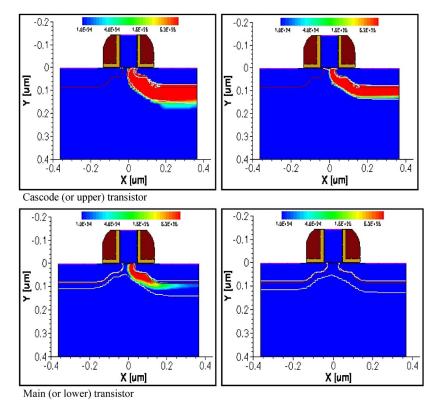

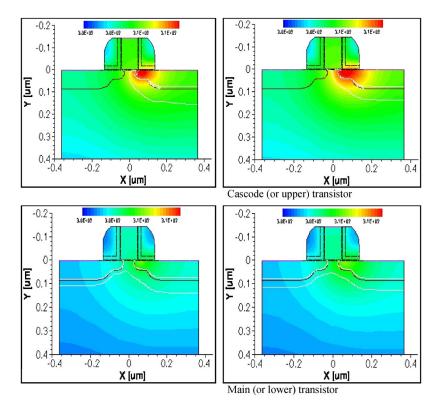

To evaluate the physical insight of hot-electron effect in the cascode PA, the Sentaurus TCAD software is used [13] and the class-E amplifier stage of the cascode PA in Fig. 1 is simulated. It is worth pointing out that the mixed-mode device and circuit simulation provides the examination of device physical insight under the practical circuit operation condition. Fig. 8 shows impact ionization rates for the cascode and main transistors with increased supply voltage  $V_{DD2}=3.5~\rm V$  for accelerated aging. As shown in Fig. 8, the impact ionization rates of the cascode transistor are much higher than those of the main transistor due to higher electric field at the drain of the cascode transistor. Larger drain–source voltage also makes impact ionization rates

at the peak of output voltage transient (see left figure) higher than those during output switching (see right figure), as shown in Fig. 8. High impact ionization rates near the drain of a MOS transistor ( $\sim 6.3 \times 10^{26} / \text{cm}^3/\text{s}$ ) suggest that a large amount of hot electrons may inject into the gate of the MOSFET. Some hot electrons could be trapped within the oxide without reaching the gate contact. The accumulated trapped electron charges over a period of time increase the threshold voltage of the MOSFET. In addition, the interfacial layer between the SiO<sub>2</sub> and Si interface near the drain region may be damaged or degraded by the channel hot electrons. Thus, the effective electron mobility of the MOSFET decreases. Consequently, the drain current and transconductance of the MOSFET decrease. The reduction in drain current could decrease the output power and efficiency of the PA, as demonstrated by the experimental data in Figs. 6 and 7.

Fig. 9 displays the lattice temperature of the cascode and main transistors. In the Sentaurus simulation, Thermodynamic,

<sup>&</sup>lt;sup>1</sup> RF stress at  $p_i = 0$  dBm and  $V_{DD2} = 3.5V$  for 10 hours

<sup>&</sup>lt;sup>2</sup> RF stress at  $p_i = 0$  dBm and  $V_{DD2} = 4.0 \text{V}$  for 10 hours

Fig. 9. Lattice temperature of (upper plots) the cascode transistor and (lower plots) the main transistor at (left figures) the maximum and (right figures) middle of the output voltage transient. In this mixed-mode device and circuit simulation,  $V_{DD2} = 3.5 \text{ V}$ .

Thermode, RecGenHeat, and AnalyticTEP models are used to account for lattice heating. The thermodynamic model extends the drift-diffusion approach to account for electrothermal effects. A Thermode is a boundary where the Dirichlet boundary condition is set for the lattice. RecGenHeat includes generation-recombination heat sources. AnalyticTEP gives analytical expression for thermoelectric power. The substrate of the nMOS is set to be at 300 K. In Fig. 9, the cascode transistor has a higher peak lattice temperature ( $\sim$ 310 K) than that in the main transistor because of larger drain-source voltage and power dissipation in the cascode transistor. The self-heating effect is enhanced during output voltage switching (see the right figures in Fig. 9) because of relatively high drain-source voltage and high drain current simultaneously. High temperature rise resulting from lattice self-heating could further reduce the drain current of the PA. Consequently, the output power and power-added efficiency of the PA degrade even more due to lattice heating. Note that it is well known that the class-E PA is vulnerable to the gate oxide breakdown due to very high drain-gate field stress. In this paper, however, we have demonstrated the experimental data in Section III that the cascode class-E PA is degraded by hot-electron effect during high output voltage switching. The mixed-mode device and circuit simulation of high impact ionization rates for the cascode transistor here supports the experimental finding of the PA degradation subjected to dc supply voltage for 10 h of continued RF stress at the input power of 0 dBm. Impact ionization leads to the formation of electron-hole pairs, i.e., electrons can be trapped in the gate oxide, whereas holes can generate interface states. Trapped electrons increase the threshold voltage of the n-channel MOSFET, whereas interface

states may degrade the effective channel electron mobility. For the PA performance degradation, threshold voltage shift is more important than mobility degradation [14]. Note that high-input-power RF stress could result in more degradation in hot-electron effect than that under dc stress [15].

Additional mixed-mode simulation at RF stress under  $V_{DD2} = 4.5 \text{ V}$  condition indicates that the peak impact ionization rates increase to  $6.3 \times 10^{27} / \text{cm}^3/\text{s}$  and the maximum lattice temperature of the cascade transistor is about 320 K. This suggests that the hot-electron effect and lattice heating are enhanced resulting from a higher drain electric field when  $V_{DD2}$  is at 4.5 V. High temperature from lattice heating, however, could reduce the hot-electron effect compared to that without selfheating [16]. On the other hand, high temperature enhances gate oxide breakdown, which is a strong function of temperature and electric field [17]. In our stress experiments, however, no noticeable increase in gate leakage current was detected when  $V_{DD2}$  was stressed at 3.5, 4, and 4.5 V. This suggests that no transistor oxide hard breakdown occurred since hard breakdown typically results in a sudden surge of gate current [18], [19] and could collapse RF performances. In addition, the ADS circuit simulation indicates that the peak drain-gate voltage of the cascode transistor with the oxide thickness of 4.08 nm results in a smaller electric field than the critical field for oxide breakdown [20]. The oxide under this high RF and elevated dc stresses at  $V_{DD2} = 4.5 \text{ V}$  may experience some kind of soft breakdown [20], which deteriorates the PA circuit performances further. Soft breakdown increases the gate leakage current noise due to formulation of random defects and conducting path within the oxide [21]. After soft breakdown, the nMOS transistor's threshold voltage is increased [22], [23]

due to more trapped charge or defect density in the oxide. The increase in threshold voltage causes a decrease in drain current. Consequently, the PA's output power and power efficiency decrease after soft breakdown (to the first order,  $\Delta P_o/P_o$  is proportional to  $\Delta I_D/I_D$  [14]).

### V. CONCLUSION

A cascode class-E PA at 5.2 GHz has been designed and fabricated. A mixed-mode device and circuit simulation is used to examine impact ionization rates and lattice heating of the cascode and main transistors in the circuit environment. The cascode transistor suffers more impact ionization and self-heating than the main transistor. The measured PA circuit performances after RF stress at different elevated  $V_{DD2}$ conditions are examined and compared with the experimental data obtained from the fresh circuit condition. The measured power gain, output power, power-added efficiency, and linearity are degraded after RF and increased dc stresses. The circuit performance degradations are larger at high  $V_{DD2}$  stress level. Hot-electron effect seems to be the dominant reliability mechanism for the degradation of cascode class-E PA evaluated at high input power and elevated supply voltage stress for 10 h. By increasing the cascode transistor's supply voltage from 3.5 to 4.5 V at high-input-power RF stress, soft breakdown may contribute additional degradation to the output power and power efficiency of the cascode class-E PA.

### ACKNOWLEDGMENT

The authors would like to thank K. Kutty for the circuit layout.

### REFERENCES

- [1] I. J. Bahl, Fundamental of RF and Microwave Transistor Amplifiers. New York: Wiley, 2009.

- [2] N. O. Sokal and A. D. Sokal, "Class E—A new class of high-efficiency tuned single-ended switching power amplifiers," *IEEE J. Solid-State Circuits*, vol. SSC-10, no. 3, pp. 168–176, Jun. 1975.

- [3] F. H. Raab, "Idealized operation of the class E tuned power amplifier," *IEEE Trans. Circuits Syst.*, vol. CAS-24, no. 12, pp. 725–735, Dec. 1977.

- [4] E. Miranda and J. Sune, "Electron transport through broken down ultrathin SiO2 layers in MOS devices," *Microelectron. Reliab.*, vol. 44, no. 1, pp. 1–23, 2004.

- [5] L. Pantisano, D. Schreurs, B. Kaczer, W. Jeamsaksiri, R. Venegas, R. Degraeve, K. P. Cheung, and G. Groeseneken, "RF performance vulnerability to hot carrier stress and consequent breakdown in low power 90 nm RFCMOS," in *IEDM Tech. Dig.*, 2003, pp. 181–184.

- [6] Z. Chen, K. Hess, J. Lee, J. W. Lyding, E. Rosenbaum, I. Kizilyalli, S. Chetlur, and R. Huang, "On the mechanism for interface trap generation in MOS transistors due to channel hot carrier stressing," *IEEE Electron Device Lett.*, vol. 21, no. 1, pp. 24–26, Jan. 2000.

- [7] A. Mazzanti, L. Larcher, R. Brama, and F. Svelto, "Analysis of reliability and power efficiency in cascode class-E PAs," *IEEE J. Solid-State Circuits*, vol. 41, no. 5, pp. 1222–1229, May 2006.

- [8] Y. Song, S. Lee, E. Cho, J. Lee, and S. Nam, "A CMOS class-E power amplifier with voltage stress relief and enhanced efficiency," *IEEE Trans. Microw. Theory Tech.*, vol. 58, no. 2, pp. 310–317, Feb. 2010.

- [9] L. Larcher, D. Sanzogni, R. Brama, A. Mazzanti, and F. Svelto, "Oxide breakdown after RF stress: Experimental analysis and effects on power amplifier operation," in *Proc. Int. Rel. Phys. Symp.*, 2006, pp. 283–288.

- [10] M. Apotolidou, M. P. van der Heijden, D. M. W. Leenaerts, J. Sonsky, A. Heringa, and I. Volokhine, "A 65 nm CMOS 30 dBm class-E RF power amplifier with 60% PAE and 40% PAE at 17 dB back-off," *IEEE J. Solid-State Circuits*, vol. 44, no. 5, pp. 1372–1379, May 2009.

- [11] [Online]. Available: http://www.agilent.com/find/eesof-ads

- [12] [Online]. Available: http://www.synopsys.com

- [13] B. M. Klaassen, "A unified mobility model for device simulation—I: Model equations and concentration dependence," *Solid State Electron.*, vol. 35, no. 7, pp. 953–959, 1992.

- [14] T. Quémerais, L. Moquillon, V. Huard, J.-M. Fournier, P. Benech, N. Corrao, and X. Mescot, "Hot-carrier stress effect on a CMOS 65-nm 60-GHz one-stage power amplifier," *IEEE Electron Device Lett.*, vol. 31, no. 9, pp. 927–929, Sep. 2010.

- [15] C.-H. Liu, R.-L. Wang, Y.-K. Su, C.-H. Tu, and Y.-Z. Juang, "Degradation of CMOS power cells after hot-carrier and load mismatch stresses," *IEEE Electron Device Lett.*, vol. 29, no. 9, pp. 1068–1070, Sep. 2008.

- [16] P. Aminzadeh, M. Alavi, and D. Scharfetter, "Temperature dependence of substrate current and hot carrier-induced degradation at low drain bias," in VLSI Symp. Tech. Dig., 1998, pp. 178–179.

- [17] M. Kimura, "Field and temperature acceleration model for timedependent dielectric breakdown," *IEEE Trans. Electron Devices*, vol. 46, no. 1, pp. 220–229, Jan. 1999.

- [18] T. Pompl, H. Wurzer, M. Kerber, and I. Eisele, "Investigation of ultrathin gate oxide reliability behavior by separate characterization of soft breakdown and hard breakdown," in *Int. Phys. Symp. Tech. Dig.*, 2000, pp. 40–47.

- [19] L. Pantisano and K. P Cheung, "The impact of postbreakdown gate leakage on MOSFET RF performances," *IEEE Electron Device Lett.*, vol. 22, no. 12, pp. 585–587, Dec. 2001.

- [20] C.-H. Liu, R.-L. Wang, and Y.-K. Su, "DC and RF degradation induced by high RF power stresses in 0.18-μm nMOSFETs," *IEEE Trans. Device Mater. Rel.*, vol. 10, no. 3, pp. 317–323, Sep. 2010.

- [21] P. Roussel, R. Degraeve, C. van den Bosch, B. Kaczer, and G. Groeseneken, "Accurate and robust noise-based trigger algorithm for soft breakdown detection in ultra thin oxides," in *Int. Rel. Phys. Symp. Tech. Dig.*, 2001, pp. 386–392.

- [22] A. Avellán and W. H. Krautschneider, "Impact of soft and hard breakdown on analog and digital circuits," *IEEE Trans. Device Mater. Rel.*, vol. 4, no. 4, pp. 676–680, Dec. 2004.

- [23] R. Rodríguez, J. H. Stathis, and B. P. Liner, "A model for gate-oxide breakdown in CMOS inverters," *IEEE Electron Device Lett.*, vol. 24, no. 2, pp. 114–116, Feb. 2003.

**Jiann-Shiun Yuan** (S'85–M'88–SM'92) received the M.S. and Ph.D. degrees from the University of Florida, Gainesville, in 1984 and 1988, respectively.

He was with Texas Instruments Incorporated, Dallas, TX, where he was involved in the 16-MB complementary metal—oxide—semiconductor dynamic random access memory design. Since 1990, after one year of industrial experience with Texas Instruments Incorporated, he has been with the faculty of the University of Central Florida (UCF), Orlando, where he is currently a Professor and the Director of

the Nanoelectronics Reliability Laboratory. He is the author of *Semiconductor Device Physics* and *Simulation* (New York: Plenum, 1998) and *SiGe, GaAs* and *InP Heterojunction Bipolar Transistors* (New York: Wiley, 1999) and has authored more than 260 papers in journals and conference proceedings. He supervised 17 Ph.D. dissertations and 30 M.S. theses at UCF. Since 1990, he has been conducting many research projects funded by the National Science Foundation, Motorola, Harris, Lucent Technologies, National Semiconductor, and Theses Logic.

Dr. Yuan is an Editor of the IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY and an IEEE Distinguished Lecturer for Electron Devices Society. He was the recipient of the 1993 Outstanding Engineering Educator Award from IEEE Florida Council; the 1995, 2004, and 2010 Teaching Award from UCF; the 2003 Research Award from UCF; and the 2003 Outstanding Engineering Award from IEEE Orlando Section. He is also a member of Eta Kappa Nu and Tau Beta Pi.

Hsuan-Der Yen was born in Kaohsiung, Taiwan, in 1983. He received the B.S. degree in electronics engineering from National Kaohsiung Marine University, Kaohsiung, in 2006 and the M.S. degree in electronics engineering from the National University of Kaohsiung, Kaohsiung, in 2008. He is currently working toward the Ph.D. degree in electronics engineering at National Tsing Hua University, Hsinchu, Taiwan.

From 2008 to present, he has been a Part-Time Worker with the National Nano Device Laboratories,

Hsinchu, where he designed an instrument control program for radio-frequency integrated-circuit (RFIC) measurement. In summer 2011, he was an Intern with Taiwan Semiconductor Manufacturing Company, Hsinchu, where he designed an automatic measurement procedure for RF device modeling and parameter extraction. His research interests are in the transceiver system, circuit design at RF and millimeter-wave frequencies, and instrument control program for RFIC measurement applications.

**Shuyu Chen** (S'10) received the B.S. degree in optical engineering from Zhejiang University, Hangzhou, China, in 2006 and the M.S. degree from Fudan University, Shanghai, China, in 2009. She is currently working toward the Ph.D. degree at the University of Central Florida (UCF), Orlando.

Since 2009, she has been a Research Assistant with the Nanoelectronics Reliability Laboratory, UCF. Her research interests include the design for reliability of radio-frequency (RF) circuits, device characterization, RF integrated-circuit design and

analysis, and full custom circuit design.

**Ruey-Lue Wang** received the B.Sc., M.Sc., and Ph.D. degrees from National Cheng Kung University, Tainan, Taiwan, in 1986, 1988, and 1992, respectively, all in electrical engineering.

He is currently an Associate Professor with the Department of Electronic Engineering, National Kaohsiung Normal University, Kaohsiung, Taiwan. His main research interests include radio-frequency and mixed-signal integrated circuits; semiconductor devices and device modeling; process technologies in biomedical, transducer, and radio-frequency appli-

cations; and readout circuits for sensors.

**Guo-Wei Huang** (S'94–M'97) was born in Taipei, Taiwan, in 1969. He received the B.S. and Ph.D. degrees in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 1991 and 1997, respectively.

In 1997, he joined the National Nano Device Laboratories, Hsinchu, where he is currently a Researcher and the Manager of the High-Frequency Technology Division. Since August 2011, he has been a Joint Professor with the Department of Electronics Engineering, National Chiao Tung Univer-

sity, Hsinchu. His current research interests focus on the characterization and modeling techniques of high-frequency devices, as well as characterization and verification of radio-frequency integrated-circuit/monolithic microwave integrated circuit.

**Ying-Zong Juang** received the M.S. and Ph.D. degrees in electrical engineering from National Cheng Kung University, Tainan, Taiwan, in 1992 and 1998, respectively.

He joined the National Chip Implementation Center (CIC), National Applied Research Laboratories, Tainan, Taiwan, in October 1998. At CIC, he has majored in the RF circuit design and device modeling works. Furthermore, from 2001 to 2004, he joined a project to develop the CMOS MEMS platform. Currently, he is a Researcher and the Director of

the Chip Implementation Service Division, CIC. His topics of interest include the technologies of wireless microsensing system. He has organized several projects, including Green system-on-a-chip, RFIP methodology, RF SiP, and 0.35-um/0.18-um CMOS MEMS/BioMEMS design environment.

**Chih-Ho Tu** was born in Tainan, Taiwan, in 1974. He received the M.S. degree in electronic engineering from Kun Shan University of Technology, Tainan, in 2004. He is currently working toward the Ph.D. degree in electrical engineering at National Chung Cheng University, Chiayi, Taiwan.

In 2000, he joined the National Chip Implementation Center (CIC), National Applied Research Laboratories, Tainan, Taiwan, where he has been involved in RF load pull system measurement and RF amplifier design. He is currently an Associate

Researcher with the Chip Implementation Service Division (CISD), CIC, where he is in charge of measurement techniques and environments relevant to RF power devices, amplifiers, and antenna.

Wen-Kuan Yeh was born in Hsinchu, Taiwan, in 1964. He received the B.S. degree in electronic engineering from Chung Yuan Christian University, Chung-Li, Taiwan, in 1988, the M.S. degree in electrical engineering from National Cheng Kung University, Tainan, Taiwan, in 1990, and the Ph.D. degree in electronics engineering from National Chiao Tung University, Hsinchu, in 1996.

He joined the Process Development Division, United Microelectronic Corporation Technology, as a member of the Research Staff in 1996–2000 to

research and develop logic, embedded DRAM, silicon-on-insulator (SOI), and 90-nm-transistor technology applications. He is currently a Full Professor with the Department of Electrical Engineering and the Dean of the College of Engineering, National University of Kaohsiung, Kaohsiung, Taiwan. His recent work is in the field of nanoscaled CMOSFETs, SOI MOSFET, and FinFET.

$\mbox{Dr.}$  Yeh is also the Vice Chair of IEEE Electron Devices Society Tainan Chapter.

**Jun Ma** received the M.S. degree in computer engineering from Florida International University, Miami, in 2005 and the Ph.D. degree in electrical engineering from the University of Central Florida, Orlando, in 2009.

He is currently with Wuxi Bay Technology, Ltd., Wuxi, China, as the Chief Executive Officer. In the late 2000s, he was a Research Assistant with the Nanoelectronics Reliability Laboratory, School of Electrical Engineering and Computer Science, UCF, where he published several journal and conference

papers on CMOS reliability issues such as hot electron, gate oxide breakdown, and the negative bias temperature instability on device and circuit performances. Currently, he continues his work on RF circuit design at Wuxi Bay Technology, Ltd.