Home Search Collections Journals About Contact us My IOPscience

Effect of Gate Length on Device Performances of AlSb/InAs High Electron Mobility Transistors Fabricated Using BCl<sub>3</sub> Dry Etching

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2012 Jpn. J. Appl. Phys. 51 060202

(http://iopscience.iop.org/1347-4065/51/6R/060202)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 28/04/2014 at 18:36

Please note that terms and conditions apply.

DOI: 10.1143/JJAP.51.060202

## Effect of Gate Length on Device Performances of AISb/InAs High Electron Mobility Transistors Fabricated Using BCI<sub>3</sub> Dry Etching

Chien-I Kuo<sup>1</sup>, Heng-Tung Hsu<sup>2</sup>, Ching-Yi Hsu<sup>3</sup>, Chia-Hui Yu<sup>1</sup>, Han-Chieh Ho<sup>4</sup>, Edward Yi Chang<sup>1,3</sup>, and Jen-Inn Chyi<sup>4</sup>

Received March 2, 2012; accepted March 26, 2012; published online May 22, 2012

In this paper, we present the development of a mesa isolation process for AlSb/InAs high electron mobility transistors (HEMTs) using inductively coupled plasma (ICP) etching with BCl<sub>3</sub> gas. Devices with different gate lengths ( $L_g$ : 60, 100, and 200 nm) fabricated by this dry etching technique show good DC and RF performances. With an appropriate  $L_g$ /gate-channel distance ratio, the 200-nm-gate has very high peak transconductances of 781 mS/mm at  $V_{DS} = 0.1 \, \text{V}$  and 2000 mS/mm at  $V_{DS} = 0.5 \, \text{V}$ . Moreover, an extrinsic current gain cutoff frequency of 137 GHz and maximum oscillation frequency of 97 GHz were achieved at a drain bias voltage  $V_{DS} = 0.3 \, \text{V}$ , indicating the great potential for such a device operating at high frequency with extremely low DC power consumption. © 2012 The Japan Society of Applied Physics

lectronic and optical devices based on binary alloys of the 6.1 Å family including InAs (6.058 Å), GaSb (6.096 Å), and AlSb (6.136 Å) have attracted much attention recently. Antimonide-based compound semiconductor AlSb/InAs high electron mobility transistors (Sb HEMTs) have been demonstrated for extremely low voltage operations due to the combination of high peak electron velocity ( $\sim 4 \times 10^7$  cm/s) at a low electric field and high channel conductivity with the high electron confinement barrier (1.35 eV) of the InAs/AlSb interface. In fact, these values for Sb HEMTs are nearly two times higher than those of In-rich In<sub>x</sub>Ga<sub>1-x</sub>As/InP HEMTs, demonstrating their great potential for phased-array and satellite systems, which require ultralow-power consumption. 3-5)

The  $Al_xGa_{1-x}Sb_yAs_{1-y}/InAs$  material system has proven to be a viable choice for advanced AlSb/InAs HEMTs with metamorphic growth on a GaAs substrate and an AlSb/AlGaSb buffer layer can eliminate the dislocations effectively. Unfortunately, AlSb is extremely liable to be oxidized in air. Additionally, wet etching of the AlSb and InAlAs stacked layers is hard to control to achieve the required depth and is not repeatable in mesa isolation steps. As a result, it is essential to develop a dry etching technique for a more controlled and less labor-intensive fabrication process.

Gate length scaling is a well-known technique to boost the operating frequency of devices. However, in some cases, scaling the gate length  $(L_{\rm g})$  alone may not be as effective as expected. It is thus our motivation to investigate the effect of gate length scaling on the device performance of Sb HEMTs.

In this study, we fabricate AlSb/InAs HEMTs with  $L_{\rm g}$  of 60, 100, and 200 nm using an ICP etcher with BCl<sub>3</sub> gas. The effect of  $L_{\rm g}$  on AlSb/InAs HEMTs performances has also been investigated. The fabricated devices demonstrate excellent DC and RF performances after dry etching, indicating the successful fabrication of AlSb/InAs HEMTs using this BCl<sub>3</sub> dry etching process for mesa etching.

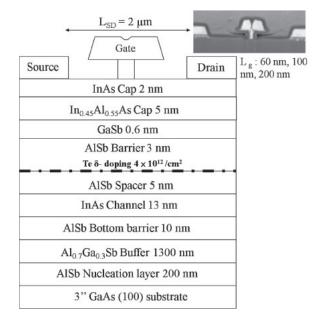

Figure 1 shows the epitaxial structure of the Sb HEMTs. The AlSb/InAs heterostructure was grown on a 3-in. GaAs substrate by solid-source molecular beam epitaxy (MBE). The composite AlSb/Al<sub>0.7</sub>Ga<sub>0.3</sub>Sb metamorphic buffer layer was utilized to accommodate the lattice mismatch between the GaAs substrate and device layer. Te planar doping was

**Fig. 1.** Epitaxial structure of the AlSb/InAs HEMT device. The inserted SEM image is the T-shaped gate after silicon nitride passivation. Devices with  $L_{\rm g}$  between 60 and 200 nm were fabricated.

employed in the AlSb barrier layer to attain high electron transfer efficiency and reduce the gate-to-channel distance. A 5-nm-thick  $In_{0.45}Al_{0.55}As$  layer was capped on the GaSb and AlSb layers to prevent air exposure and provide a chemically stable surface layer. The electron sheet carrier density and mobility at room temperature were measured to be  $1.7 \times 10^{12} \, \mathrm{cm}^{-2}$  and  $22,400 \, \mathrm{cm}^2 \, \mathrm{V}^{-1} \, \mathrm{s}^{-1}$ , respectively.

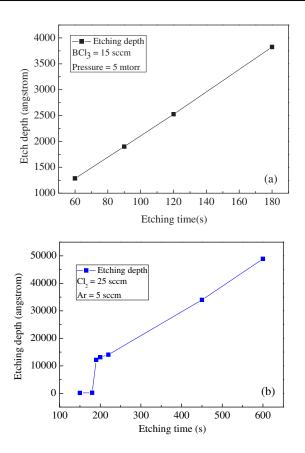

The fabrication process started with mesa isolation through a novel inductively coupled plasma (ICP) process using BCl<sub>3</sub> gas (ULVAC NE-950EX etcher) and the dry etching was stopped at the Al<sub>0.7</sub>Ga<sub>0.3</sub>Sb buffer layer. BCl<sub>3</sub> gas has been found to be more effective for etching AlGaSb than Cl<sub>2</sub>-based gases. The critical step in guaranteeing the performance of the fabricated Sb HEMTs is mesa formation by dry etching, which must be well controlled so that it stops at the Al<sub>0.7</sub>Ga<sub>0.3</sub>Sb buffer, where 30% Ga is added to avoid the oxidation of AlSb. Figure 2(a) shows the etching depth as a function of etching time for the device etched with BCl<sub>3</sub>

<sup>&</sup>lt;sup>1</sup> Department of Materials Science and Engineering, National Chiao-Tung University, Hsinchu, Taiwan 30010, R.O.C.

<sup>&</sup>lt;sup>2</sup> Department of Communications Engineering, Yuan Ze University, Chungli, Taiwan 32003, R.O.C.

<sup>&</sup>lt;sup>3</sup> Department of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan 30010, R.O.C.

<sup>&</sup>lt;sup>4</sup>Department of Electrical Engineering, National Central University, Jhongli, Taiwan 32001, R.O.C.

**Fig. 2.** (Color online) (a) Etch depth as a function of the etching time for the Sb HEMT using  $BCl_3$  and (b) etch depth as a function of the etching time for the Sb HEMT using  $Cl_2/Ar$ .

gas. The etching rate is well controlled to obtain shallow mesa isolation. The measured etch depth as a function of the etching time with Cl<sub>2</sub>/Ar mixed gas is depicted in Fig. 2(b). As observed from the figure, it is hard to control the etching depth using Cl<sub>2</sub>/Ar due to the drastic increase in depth when the etching time is approximately 200 s. The depth of the device mesa was measured to be approximately 1500 Å by KLA-Tencor P-10 surface profiler. Pd/Pt/Au ohmic contacts were evaporated and subsequently annealed at 300 °C for 30 s in N<sub>2</sub> ambient, resulting in a low contact resistance of 0.027  $\Omega$  mm and a sheet resistance of 157  $\Omega$ /sq. Non-recessed Pt/Ti/Pt/Au T-shaped gates were defined on the InAs cap layer using trilayer resist and electron beam lithography. The inserted scanning electron microscopy (SEM) image in Fig. 1 is the 60 nm T-shaped gate after silicon nitride passivation. Finally, a 100-nm-thick SiN passivation layer was deposited by low-temperature plasma-enhanced chemical vapor deposition (PECVD) to protect the devices.

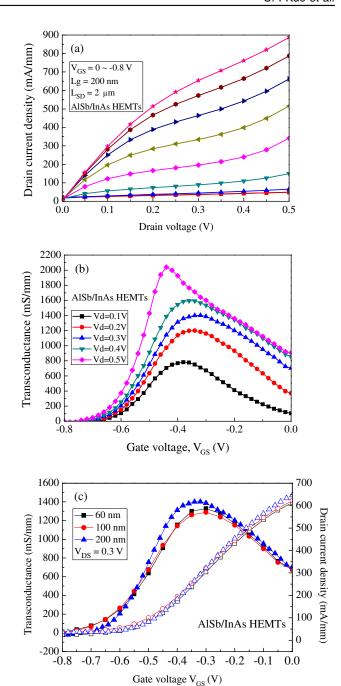

Figure 3(a) shows the drain–source current ( $I_{\rm DS}$ ) as a function of drain–source voltage ( $V_{\rm DS}$ ) with the gate–source voltage ( $V_{\rm GS}$ ) varied from 0 to  $-0.8\,\rm V$  for the 200-nm-gate and  $2\times20$ -µm²-width device. The device exhibits a maximum drain current density of 900 mA/mm at a gate bias of 0 V and a drain bias of 500 mV. Figure 3(b) shows the DC transconductance ( $g_{\rm m}$ ) as a function of gate voltage at different  $V_{\rm DS}$  for the same device. A maximum DC  $g_{\rm m}$  of 2000 mS/mm is achieved at the same bias. At room temperature, the measured on-resistance  $R_{\rm ON}$  was  $0.33\,\Omega\,\rm mm$ .

**Fig. 3.** (Color online) (a) Drain and (b) transfer characteristics of the 200 nm AlSb/InAs HEMT. The gate width is  $20 \times 2 \, \mu m$  and the sourcedrain spacing is  $2 \, \mu m$ . (c)  $g_m$  versus  $V_{\rm GS}$  with different gate lengths at  $V_{\rm DS} = 0.3 \, \rm V$ .

The IV characteristics in Fig. 3 illustrate the advantages of the Sb HEMT with low-voltage operation, low  $R_{\rm ON}$ , and high  $g_{\rm m}$ , which are necessary for ultralow-power and high-frequency applications. Such a high current density and  $g_{\rm m}$  value result from the high peak electron velocity at a low electric field and the high channel conductivity, which enable the operation of AlSb/InAs HEMTs at very low drain bias voltages. As observed from Fig. 3(b), the drastic increase in the  $g_{\rm m}$  peak value for  $V_{\rm DS}$  greater than 0.4 V is due to the impact ionization in the channel resulting from the staggered band lineup at InAs/AlSb heterojunctions. Since the staggered band alignment at such heterojunctions does

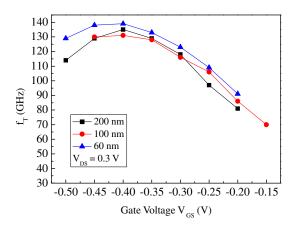

**Fig. 4.** (Color online)  $f_T$  as a function of gate voltage for different gate lengths.

not confine holes, electron flows into the channel, increasing the channel current and  $g_{\rm m}$ .<sup>10)</sup>

The transconductance and drain–source current plotted as a function of gate voltage for devices with different gate lengths at  $V_{\rm DS}=0.3\,\rm V$  is shown in Fig. 3(c). The peak  $g_{\rm m}$  of the 200 nm device (1401 mS/mm) is slightly higher than those of the 100 nm (1288 mS/mm) and 60 nm (1329 mS/mm) devices.

The *S*-parameter of the devices was measured from 2 to 110 GHz using an on-wafer probe system with an HP8510XF network analyzer. The extrinsic cutoff frequency ( $f_{\rm T}$ ) and maximum frequency of oscillation ( $f_{\rm max}$ ) were extracted from extrapolation of the measured current gain ( $H_{21}$ ) and Mason's unilateral gain (U) using a  $-20\,{\rm dB}/{\rm decade}$  slope. The 200 nm device exhibited  $f_{\rm T}$  and  $f_{\rm max}$  of 137 and 97 GHz at  $V_{\rm DS}=0.3$  V, respectively. These results also demonstrate the feasibility of BCl<sub>3</sub> dry etching for shallow mesa formation in Sb HEMTs fabrication.

$f_{\rm T}$  as a function of gate voltage for different gate lengths is shown in Fig. 4. As shown, high  $f_{\rm T}$  and  $f_{\rm max}$  were achieved at low bias levels for all devices due to the good transport properties in the InAs channel. Interestingly, it is observed that the 60 nm device does not significantly outperform the others as expected. The extracted intrinsic RF  $g_{\rm m}$  was  $1250\,{\rm mS/mm}$  for the 60 nm device,  $1175\,{\rm mS/mm}$  for the  $100\,{\rm nm}$  device, and  $1225\,{\rm mS/mm}$  for  $200\,{\rm nm}$  device, which showed a similar trend to that depicted in Fig. 4. Apparently, merely scaling the gate length is not enough to boost the

$f_{\rm T}$  if the gate-channel distance is not optimized with the  $L_{\rm g}$  aspect ratio, which agrees with the results of Guerra et al. Another reason for this phenomenon is the occurrence of the ballistic effect in the electron transport under the gate electrode for the 60 and 100 nm devices. (12)

In summary, an ICP dry etching process using BCl<sub>3</sub> gas has been developed to precisely control the etching depth for shallow mesa isolation in the fabrication of AlSb/InAs HEMTs. Effect of the gate lengths on device performances was also investigated. Good DC and RF performances, with an extrinsic  $f_{\rm T}/f_{\rm max}$  of 137/97 GHz, were achieved at  $V_{\rm DS}=0.3\,{\rm V}$  for  $2\times20\,{\rm \mu m}$  HEMTs with a 200 nm gate length. These results demonstrate the potential of Sb HEMTs for low-voltage operation at high frequencies.

**Acknowledgments** The authors would like to acknowledge the assistance and support from the National Science Council, Taiwan, R.O.C., under contract NSC 99-2221-E-009-MY3 and ULVAC Corporation, Taiwan Branch. Part of this work was also supported by the "Nanotechnology Network Project" of the Ministry of Education, Culture, Sports, Science and Technology, Japan (MEXT).

- B. R. Bennett, R. Magno, J. B. Boos, W. Kruppa, and M. G. Ancona: Solid-State Electron. 49 (2005) 1875.

- A. Nakagawa, H. Kroemer, and J. H. English: Appl. Phys. Lett. 54 (1989) 1893.

- 3) W. R. Deal, R. Tsai, M. D. Lange, J. B. Boos, B. R. Bennett, and A. Gutierrez: IEEE Microwave Wireless Components Lett. 15 (2005) 208.

- G. Moschetti, N. Wadefalk, P. A. Nilsson, Y. Roelens, A. Noudeviwa, L. Desplanque, X. Wallart, F. Danneville, G. Dambrine, S. Bollaert, and J. Grahn: Solid-State Electron. 64 (2011) 47.

- 5) Y.-C. Chou, J. M. Yang, C. H. Lin, J. Lee, M. Lange, R. Tsai, P. Nam, M. Nishimoto, A. Gutierrez, H. Quach, R. Lai, D. Farkas, M. Wojtowicz, P. Chin, M. Barsky, A. Oki, J. B. Boos, and B. R. Bennett: IEEE MTT-S, 2007, p. 461.

- J. B. Boos, W. Kruppa, B. R. Bennett, D. Park, S. W. Kirchoefer, R. Bass, and H. B. Dietrich: IEEE Trans. Electron Devices 45 (1998) 1869.

- A. Olivier, A. Noudeviwa, N. Wichmann, Y. Roelens, L. Desplanque, F. Danneville, G. Dambrine, X. Wallart, and S. Bollaert: Proc. 5th European Microwave Integrated Circuits Conf., 2010, p. 162.

- P. Nam, R. Tsai, M. Lange, W. Deal, J. Lee, C. Namba, P. Liu, R. Grundbacher, J. Wang, M. Barsky, A. Gutierrez-Aitken, and S. Olson: Proc. GaAs Mantech Conf., 2005.

- E. Lefebvre, M. Borg, M. Malmkvist, J. Grahn, L. Desplanque, X. Wallart, Y. Roelens, G. Dambrine, A. Cappy, and S. Bollaert: Proc. 19th Int. Conf. InP and Related Materials, 2007, p. 125.

- H. K. Lin, D. W. Fan, Y. C. Kin, P. C. Chiu, C. Y. Chien, P. W. Li, J. I. Chyi, C. H. Ko, T. M. Kuan, M. K. Hsieh, W. C. Lee, and C. H. Wann: Solid-State Electron. 54 (2010) 505.

- D. Guerra, R. Akis, F. A. Marino, D. K. Ferry, S. M. Goodnick, and M. Saraniti: IEEE Electron Device Lett. 31 (2010) 1217.

- G. Moschetti, P.-A. Nilsson, L. Desplanque, X. Wallart, H. Rodilla, J. Mateos, and J. Grahn: Proc. 22nd Int. Conf. InP and Related Materials, 2010.