Home Search Collections Journals About Contact us My IOPscience

Characteristics of n-Type Asymmetric Schottky-Barrier Transistors with Silicided Schottky-Barrier Source and Heavily n-Type Doped Channel and Drain

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2012 Jpn. J. Appl. Phys. 51 064301

(http://iopscience.iop.org/1347-4065/51/6R/064301)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 28/04/2014 at 18:36

Please note that terms and conditions apply.

DOI: 10.1143/JJAP.51.064301

# Characteristics of n-Type Asymmetric Schottky-Barrier Transistors with Silicided Schottky-Barrier Source and Heavily n-Type Doped Channel and Drain

Zer-Ming Lin<sup>1</sup>, Horng-Chih Lin<sup>1,2\*</sup>, and Tiao-Yuan Huang<sup>1</sup>

Received August 25, 2011; accepted March 17, 2012; published online May 14, 2012

In this study, we explore the operation of operation a novel asymmetric Schottky-barrier transistor (ASSBT) through using technology computer aided design (TCAD). The new ASSBT features a silicided Schottky-barrier (SB) source, with the channel and drain made of heavily n-doped silicon. By eliminating the SB drain junction contained in conventional symmetrical-type SB metal—oxide—semiconductor field-effect transistors (MOSFETs), a larger on-state current is achievable. Moreover, combined with the adoption of fully depleted thin-film channel, the off-state leakage current can be efficiently suppressed as well. In addition, we also comprehensively analyze the transport mechanisms dominating in different operational regions of this new ASSBT. A pseudo-subthreshold region that shows worse subthreshold swing (SS) than the subthreshold region is identified. A decrease in channel and/or gate oxide thicknesses can contribute to the improvement of the SS of this region. A modified form of scaling length ( $\lambda$ ) is also introduced to describe the impacts of structural parameters and gate configurations on the SS characteristics of this new ASSBT. © 2012 The Japan Society of Applied Physics

### 1. Introduction

Schottky-barrier (SB) metal-oxide-semiconductor (MOS) transistor with the source and drain (S/D) made of metallic silicides has been proposed as one of the promising candidates for replacing conventional doped S/D metaloxide-semiconductor field-effect transistors (MOSFETs), since silicided S/D can provide shallow and abrupt junctions with a low serious resistance. 1-5) Device operation mechanisms of conventional inversion-mode SB transistor with symmetrical S/D<sup>7)</sup> have been reported in the literature. Usually, a symmetric SB transistor (SSBT) that has silicided SB S/D suffers from a large leakage current due to the inherent ambipolar characteristics. 1-5) Such an issue could be addressed with an asymmetric SB transistor (ASSBT) proposed by Uchida et al. 1) In a previous work, devices with a silicided source and a heavily doped drain (i.e., with a conventional p-n junction) were built on a bulk substrate. The use of the doped drain junction in lieu of the silicided one greatly suppresses the leakage in the off-state.

On the other hand, for conventional MOSFETs, the provision of abrupt and uniform S/D junctions becomes increasingly difficult as the devices are continuously scaling down. To address this issue, junctionless transistors that have a heavily doped channel with doping concentrations higher than  $10^{19} \,\mathrm{cm}^{-3}$  and of the same type as that of the S/D have been proposed for nano scale complementary MOS (CMOS).<sup>8–10)</sup> In addition, junctionless transistors have also been proposed for applications in three-dimensional (3D) stacked NAND flash memories. 11) The combination of the heavily doped channel and SB S/D is a very intriguing research topic. In this work, by using technology computer aided design (TACD), 12) we propose and explore a new ASSBT that features SB only on the source side, while the channel and drain are both n<sup>+</sup>-doped. That is the drain is "junctionless-like". Our simulation results show that excellent on/off device characteristics are achieved with such a scheme. Dominant conduction mechanisms in different operation regions and the effects of channel thickness and gate oxide thickness are also studied.

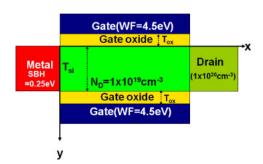

**Fig. 1.** (Color online) Schematic diagrams of the (a) SSBT with silicided SB S/D and (b) ASSBT with silicided SB only on the source side investigated in this work.  $T_{\rm si}=6\,{\rm nm},\,T_{\rm ox}=0.6\,{\rm nm},\,{\rm WF}=0.5\,{\rm eV},\,{\rm and}$  SBH = 0.25 eV. Channel doping  $N_{\rm D}=1\times10^{19}\,{\rm cm}^{-3}$ .

## 2. Subthreshold Characteristics of ASSBT

Figures 1(a) and 1(b) show the simulated device structures of single-gated (SG) SSBT and the proposed ASSBT, respectively, both with a heavily n<sup>+</sup>-doped channel. The former is with the symmetrical silicided SB source/drain while the latter has silicided SB formed only on the source side. In Fig. 1(b), the proposed new structure eliminates the need for the p-n drain junction in previously reported ASSBTs.<sup>7)</sup> Such a junctionless-like feature of the new ASSBT requires an ultra thin channel in order to effectively switch off the current conduction of the device. It should be noted that, although the channel doping of the proposed structure is of the same type as that of the drain, which is akin to that of conventional accumulation-mode (AM) device, the high channel doping (10<sup>19</sup> cm<sup>-3</sup>) of the present

<sup>&</sup>lt;sup>1</sup>Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan

<sup>&</sup>lt;sup>2</sup>National Nano Device Laboratories, Hsinchu 300, Taiwan

<sup>(</sup>a) Gate (WF=4.5eV) Metal Metal T<sub>si</sub>=6nm SBH =0.25e\ N<sub>D</sub>=1x10<sup>19</sup>cm<sup>-3</sup> **Buried oxide** У (b) Gate (WF=4.5eV) Gate oxide(Tox) 0.6nn T<sub>si</sub>=6nm Drain 1x1020cm N<sub>D</sub>=1x10<sup>19</sup>cm<sup>-3</sup> **Buried oxide** ý

<sup>\*</sup>E-mail address: hclin@faculty.nctu.edu.tw

**Table I.** Major parameters of SSBT and ASSBT used in simulation.

| Gate work function, WF (eV)                         | 4.5                |

|-----------------------------------------------------|--------------------|

| Gate oxide thickness, $T_{\rm ox}$ (nm)             | 0.6                |

| Silicon thin film thickness, $T_{si}$ (nm)          | 6                  |

| Doping concentration in drain (cm <sup>-3</sup> )   | $1 \times 10^{20}$ |

| Doping concentration in channel (cm <sup>-3</sup> ) | $1 \times 10^{19}$ |

| Schottky-barrier height, SBH (eV)                   | 0.25               |

|                                                     |                    |

structure makes its operation quite different. While conventional AM devices adopt a channel doping concentrations typically ranging from  $4\times 10^{16}$  and  $5\times 10^{17},^{13-15)}$  which are much lower than those of the drain. When an AM device is turned on, an accumulation layer (carrier concentration typically  $\geq 10^{19}\,\mathrm{cm}^{-3}\gg$  channel doping) is formed and current conduction take place near the oxide/channel interface. In contrast, current conduction in the present scheme in the on-state is mainly through the whole channel rather than close to the oxide interface (see later in the analysis part). Therefore, the operation characteristics are different from those of the AM devices.

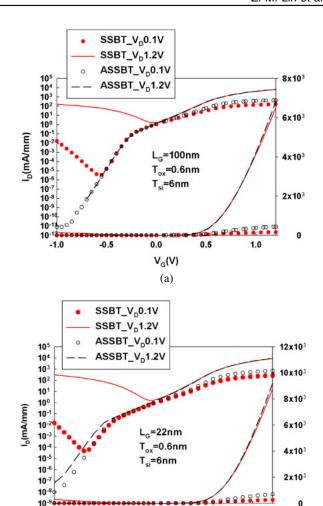

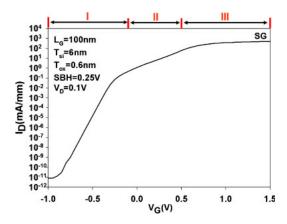

Detailed parameters used for the simulation of the devices are listed in Table I. The directions of x and y shown in Figs. 1(a) and 1(b) are parallel and perpendicular to the source-to-drain direction, respectively. A two-dimensional (2D) TCAD tool "DESSIS" 12) is employed in this work for the simulation analysis. The tunneling current conducting through the SB is examined using a non local tunneling model with with effective masses of 0.26 and  $0.36 m_0$  for electrons and holes, respectively. Figures 2(a) and 2(b) show comparisons of the calculated drain current-gate voltage  $(I_D-V_G)$  characteristics of SSBT and the new ASSBT with gate length  $(L_G)$  values of 100 and 22 nm, respectively. Similar to the conventional inversion-mode SB-MOSFETs, the SSBTs with a heavily n<sup>+</sup>-doped channel show ambipolar behavior, i.e., a large gate-induced drain leakage (GIDL)-like current is conducting in the off-state, 2) resulting in low on/off current ratios. In contrast, the ASSBT shows unipolar transfer characteristics with a significantly reduced off-state current, owing to the suppression of hole current injection from the drain side as gate voltage is sufficiently negative. Moreover, the on-state current of the ASSBT is also slightly improved, owing to the reduction of the drain resistance component. Although the  $I_D$ – $V_G$  characteristics of heavily n<sup>+</sup>-doped channel SB transistors appear similar to the conventional inversion-mode SB transistors, 2) their operational physical mechanisms are quite different. The most striking feature associated with the operation of the present devices is that they must be turned off by depleting the heavily doped channel. 16) The dominant transport mechanism depends on the operation condition. To help understand the situations, a typical  $I_D$ – $V_G$  curve of an ASSBT with an n<sup>+</sup>-doped channel is shown in Fig. 3, which is divided into three regions corresponding to different transport mechanisms. To elaborate on the mechanisms, electron density and electric potentials in the silicon channel along the y-direction near the source at x = 3 nm for various gate voltages are simulated, and the results are shown in Figs. 4-6 for regions I, II, and III, respectively. Moreover, the conduction band edges of the heavily n<sup>+</sup>-doped channel along the x-direction at y = 1 nm in regions I, II, and III are also individually

**Fig. 2.** (Color online) Comparison of the  $I_{\rm D}$ – $V_{\rm G}$  characteristics between SSBT and ASSBT with channel lengths of (a) 100 and (b) 22 nm.

$V_{G}(V)$

0.5

1.0

-0.5

Fig. 3. (Color online) Operation regions presented in the  $I_{\rm D}{-}V_{\rm G}$  characteristics of an ASSBT.

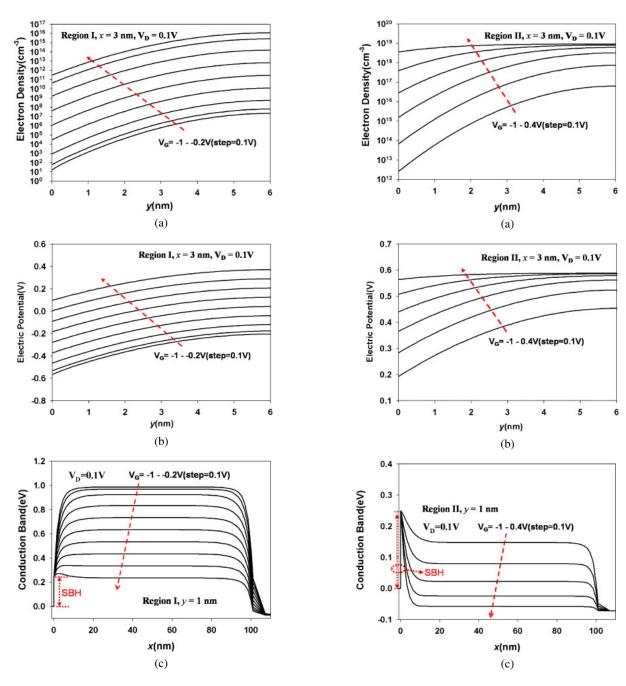

shown in Figs. 4(c), 5(c), and 6(c), respectively, to explain the impact of the SB profile on device operation. Region I is the subthreshold region and, as shown in Figs. 4(a) and 4(b), the carrier concentration is significantly reduced while the strength of electric field in the channel near the source is not

**Fig. 4.** (Color online) (a) Electron density and (b) electric potential through the silicon channel along the y-direction at x=3 nm, and (c) the potential diagram along the x-direction while the ASSBT is operated in region I.

**Fig. 5.** (Color online) (a) Electron density and (b) electric potential through the silicon channel along the *y*-direction at x = 3 nm, and (c) the potential diagram along the *x*-direction while the ASSBT is operated in region II.

high. The potential barrier for electrons in the source, as shown in Fig. 4(c), is much larger than the Schottky barrier height (SBH) at the source/channel interface. Thus, the injection of electrons from the source to the channel is mainly governed by the thermionic emission, similar to that of conventional MOS devices operated in the subthreshold regime. Moreover, by using extra small channel thickness ( $T_{\rm si}=6\,{\rm nm}$ ), a subthreshold swing (SS) close to the ideal value of 60 mV/dec is achieved. When gate voltage increases from region I to region II, which is also called the pseudo-subthreshold region, Fig. 5(a) shows the increase in carrier concentration accompanied by the increase in with the rise of electric potential, as shown in Fig. 5(b). In addition, as shown

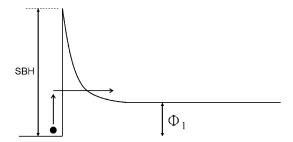

in Fig. 5(c), the potential at the channel center decreases to a level lower than the top of the SB; thus, its operational mechanism is determined by the thermionic field emission (TFE) in combination with thermionic emission and tunneling current,  $^{17)}$  as shown in Fig. 7. As can be noted in Fig. 5(c), the SBH is essentially not affected by gate voltage when operated in this region, so does the thermionic emission current component. On the other hand, the width of the barrier for the thermally activated electrons in the silicided SB source to the tunnel through as well as the potential at the channel center ( $\Phi_1$  in Fig. 7) is effectively modulated by gate voltage. As a result, the TFE current dominates the conduction in region II, resulting in a larger SS.

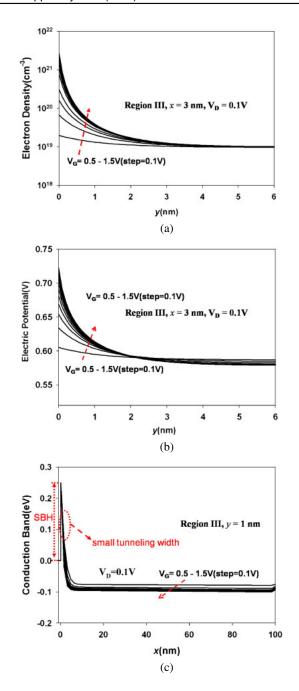

Fig. 6. (Color online) (a) Electron density and (b) electric potential through the silicon channel along the y-direction at x = 3 nm, and (c) the potential diagram along the x-direction while the ASSBT is operated in region III.

As the gate voltage increases further and reaches beyond flat-band voltage, the device is switched from region II to region III (i.e., the on-state) where a large number of electrons accumulate near the interface between the channel and gate oxide, as shown in Fig. 6(a). Under such a condition the tunneling barrier is so thin that the tunneling mechanism overwhelms the thermionic process. However, as gate voltage further increases, the tunneling width of the SB junction is not modulated effectively anymore, as illustrated in Fig. 6(c); therefore, the transport current of ASSBT gradually saturates.

## 3. Impacts of $T_{ox}$ and $T_{si}$ on SS

In the above section, we show that the ASSBT exhibits an

Fig. 7. Band diagram of the ASSBT operated in region II showing the thermionic field emission process.

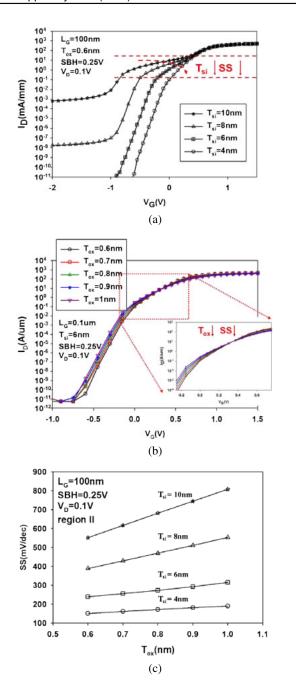

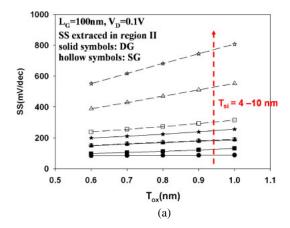

inferior SS in region II owing to the inefficient modulation of barrier height and the tunneling width of the SB junction. Since the SBH is 0.25 eV and is difficult for the gate bias to modulate, it is therefore desirable to enhance the capability of the gate bias in modulating the tunneling width of SB. In this section, we will demonstrate how a thinner channel and/or a thinner effective gate oxide yields improvement of SS in region II. Figures 8(a) and 8(b) show the  $I_D-V_G$ characteristics of ASSBTs with various channel and gate oxide thicknesses, respectively. SS extracted from region II of the transfer curves for devices with channel thicknesses varying from 4 to 10 nm is plotted as a function of  $T_{\rm ox}$  in Fig. 8(c). It can be seen that SS is improved as channel and gate oxide thicknesses decrease. The decrease in SS with decreasing  $T_{si}$  could be understood from the results shown in Fig. 5(b). In this figure, we can observe that the modulation of the potential by the gate bias is weakened in a deeper position. A reduction in channel thickness could thus enhance the overall gate controllability in modulating the tunneling width of the SB. A reduction in oxide thickness may have the same effect; thus, the SS is improved.

Similar trends were also observed in conventional inversion-mode SB transistors. 18-20) According to the previous studies, the electrostatic problem of conventional fully depleted inversion-mode SB MOSFETs could be solved by a simple 1D differential equation, which is expressed

$$\frac{d^2\Phi(x)}{dx^2} - \frac{\Phi(x) - V_g + V_{bi}}{\lambda^2} = \frac{\rho_{tot}(x)}{\varepsilon_{ci}},$$

(1)

$$\frac{d^2\Phi(x)}{dx^2} - \frac{\Phi(x) - V_{\rm g} + V_{\rm bi}}{\lambda^2} = \frac{\rho_{\rm tot}(x)}{\varepsilon_{\rm si}}, \qquad (1)$$

$$\lambda = \sqrt{T_{\rm si}T_{\rm ox}\left(\frac{\varepsilon_{\rm si}}{\varepsilon_{\rm ox}}\right)}, \qquad (2)$$

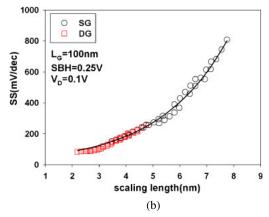

where  $\Phi(x)$ ,  $V_{\rm bi}$ ,  $V_{\rm g}$ , and  $\rho_{\rm tot}$  are the electric potential, buildin potential, applied gate voltage and mobile charges, respectively.  $\lambda$  is the scaling length and describes how the potential variation is exponentially screened. According to eqs. (1) and (2), decreases in  $T_{\rm si}$  and  $T_{\rm ox}$  lead to a smaller  $\lambda$ , which would in turn reduce the tunneling width of the SB and improve SS. For heavily n<sup>+</sup>-doped-channel ASSBT, the concept of scaling length " $\lambda$ " is still suitable to describe the impact of  $T_{si}$  and  $T_{ox}$  on SS while the device is operated in region II. However, a modification of  $\lambda$  is essential. From Fig. 5(a), it can be seen that the location of maximum electron concentration is deep in the channel. This is in contrast to the case of conventional inversion-mode SB MOSFET, and suggests that the effective gate oxide thickness is large for the n-type ASSBT with a heavily n<sup>+</sup>-

**Fig. 8.** (Color online)  $I_{\rm D}-V_{\rm G}$  characteristics of ASSBTs with various (a)  $T_{\rm si}$  and (b)  $T_{\rm ox}$  and (c) SS versus  $T_{\rm ox}$  with  $T_{\rm si}$  as a parameter for ASSBTs operated in region II.

doped channel. An empirical form for the modified  $\lambda$  can be expressed as:

$$\lambda = \sqrt{\frac{\varepsilon_{\rm si}}{\varepsilon_{\rm ox}} T_{\rm si} \left( \eta \frac{\varepsilon_{\rm ox}}{\varepsilon_{\rm si}} T_{\rm si} + T_{\rm ox.} \right)},\tag{3}$$

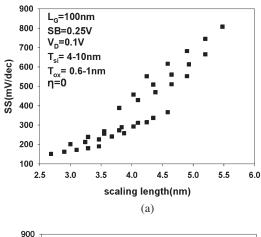

where  $\eta$  is the fitting parameter used to reflect the effective thicker gate oxide. If no modification is carried out on the effective gate oxide thickness for heavily n<sup>+</sup>-doped channel ASSBTs (i.e.,  $\eta=0$ ), the plot of SS versus  $\lambda$  of heavily n<sup>+</sup>-doped-channel ASSBTs with various  $T_{\rm si}$  and  $T_{\rm ox}$  cannot be arranged in the same regression curve, as shown in Fig. 9(a). However, as shown in Fig. 9(b), as the above mentioned modified form for  $\lambda$  ( $\eta=0.3$ ) is

**Fig. 9.** SS versus  $\lambda$  with (a)  $\eta=0$  and (b)  $\eta=0.3$ . In (b), the data are described well by a fitting curve.

Fig. 10. (Color online) Schematic diagram of the DG ASSBT with  ${\rm SBH} = 0.25\,{\rm eV}.$

implemented, the concept of  $\lambda$  can work well again to reflect the influence of gate oxide and channel thicknesses on SS in region II.

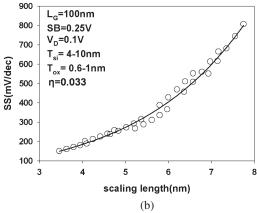

In order to further improve the SS of the ASSBT in region II, double-gated (DG) configuration is also investigated. Figure 10 shows a plot of the schematic 2D structure of the DG ASSBT with a heavily  $\rm n^+$ -doped channel. The comparison of SS between DG and SG devices is shown in Fig. 11(a), where the thicknesses of gate oxide and silicon channel are varied from 0.6 to 1 nm and 4 to 10 nm, respectively. Owing to the stronger gate control ability, significant improvement of SS is demonstrated for the DG configuration. Figure 11(b) shows the plot of SS versus  $\lambda$  of heavily  $\rm n^+$ -doped channel DG ASSBT, together with the results of devices with a SG configuration. It can be

**Fig. 11.** (Color online) (a) Comparison of SS between SG and DG ASSBTs with various  $T_{\rm si}$  and  $T_{\rm ox}$ . (b) SS versus  $\lambda$  for SG and DG ASSBTs with  $\eta=0.3$ .

noted that both DG and SG configurations fit in the same regression curve, which means that the concept of  $\lambda$  works well regardless of the gate configuration. Note that  $T_{\rm si}$  in eq. (3) is corrected to  $T_{\rm si}/2$  for DG configuration.

## 4. Conclusions

The new n-type ASSBT structure studied in this work, which features the SB source and junctionless-like drain, distinguishes itself from all the previously reported ASSBTs in the new junctionless-drain feature, combined with the fully depleted thin-film channel cannot only suppress off-state leakage but also eliminate the steps and issues associated with the formation of p—n junctions. Through TCAD simulation, we have explored the operation of the new ASSBT. As compared with the SSBT equipped with symmetrical silicided SB S/D, it is confirmed that the new ASSBT exhibits much reduced off-state current

and improved on-current. The dominant conduction mechanisms of the ASSBT are also studied. In addition to the subthreshold and on-state regions, a pseudo-subthreshold region in which thermionic field emission conduction process dominates is identified. A reduction in either the channel or gate oxide thickness contributes to the reduction of reducing the SS of pseudo-subthreshold region. Finally, the concept of scaling length  $(\lambda)$  is adopted but with a modified empirical form to reflect the impacts of gate oxide and channel thicknesses on the characteristics of the devices.

#### **Acknowledgments**

This work was supported in part by the Ministry of Education in Taiwan under ATU Program, and the National Science Council under contract No. NSC 99-2221-E-009-172 and No. NSC 99-2221-E-009-167-MY3.

- J. Kedzierski, P. Xuan, E. H. Anderson, J. Bokor, T.-J. King, and C. Hu: IEDM Tech. Dig., 2000, p. 57.

- 2) C. Wang, J. P. Snyder, and J. R. Tucker: Appl. Phys. Lett. 74 (1999) 1174.

- S. Zhu, H. Y. Yu, S. J. Whang, J. H. Chen, and C. Shen: IEEE Electron Device Lett. 25 (2004) 268.

- J. M. Larson and J. P. Snyder: IEEE Trans. Electron Devices 53 (2006) 1048.

- M. Nishisaka, Y. Ochiai, and T. Asano: Proc. Device Research Conf., 1998, p. 74.

- 6) H. C. Lin, K. L. Yeh, R. G. Huang, C. Y. Lin, and T. Y. Huang: IEEE Electron Device Lett. 22 (2001) 179.

- K. Uchida, K. Matsuzawa, J. Koga, S. I. Takagi, and A. Toriumi: Appl. Phys. Lett. 76 (2000) 3992.

- C. J. Su, T. I. Tsai, Y. L. Liou, Z. M. Lin, H. C. Lin, and T. S. Chao: IEEE Electron Device Lett. 32 (2011) 521.

- 9) C. W. Lee, I. Ferain, A. Afzalian, R. Yan, N. D. Akhavan, P. Razavi, and J. P. Colinge: Solid-State Electron. **54** (2010) 97.

- J. P. Colinge, C. W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A. M. Kelleher, B. McCarthy, and R. Murphy: Nat. Nanotechnol. 5 (2010) 225.

- 11) H.-T. Lue, T.-H. Hsu, Y.-H. Hsiao, S. P. Hong, M. T. Wu, F. H. Hsu, N. Z. Lien, S.-Y. Wang, J.-Y. Hsieh, L.-W. Yang, T. Yang, K.-C. Chen, K.-Y. Hsieh, and C.-Y. Lu: VLSI Tech. Symp. Tech. Dig., 2010, p. 131.

- 12) DESSIS Software Manual (Synopsys International, 2004).

- W. Cheng, A. Teramoto, M. Hirayama, S. Sugawa, and T. Ohmi: Jpn. J. Appl. Phys. 45 (2006) 3110.

- 14) A. Terao, D. Flandre, E. Lora-Tomayo, and F. Van der Wiele: IEEE Electron Device Lett. 12 (1991) 682.

- A. L. P. Rotondaro, U. K. Magnusson, C. Claeyes, D. Flandre, A. Terao, and J. P. Conlinge: IEEE Electron Devices 40 (1993) 727.

- 16) J. P. Colinge: Silicon Nanoelectronics Workshop, 2011, p. 69

- S. M. Sze and K. K. Ng: Physics of Semiconductor Devices (Wiley, New York, 2007) 3rd ed., p. 165.

- J. Knoch, M. Zhang, S. Mantl, and J. Appenzeller: IEEE Trans. Electron Devices 53 (2006) 1669.

- 19) J. Knoch and J. Appenzeller: Appl. Phys. Lett. 81 (2002) 3082.

- J. Knoch, M. Zhang, J. Appenzeller, and S. Mantl: Appl. Phys. A 87 (2007)