# Reliability Analysis of Symmetric Vertical-Channel Nickel-Salicided Poly-Si Thin-Film Transistors

Yi-Hong Wu, Je-Wei Lin, Yi-Hsien Lu, Rou-Han Kuo, Li-Chen Yen, Yi-Hsuan Chen, Chia-Chun Liao, Po-Yi Kuo, *Member, IEEE*, and Tien-Sheng Chao

Abstract-In this paper, a reliability analysis of symmetric Vertical-channel Ni-SAlicided poly-Si thin-film transistors (VSA-TFTs) is performed for the first time. First, we compare the drain-induced barrier-lowering effect (DIBL) of VSA-TFTs. The VSA-TFTs with thinner gate oxide thickness, an offset structure, and a longer floating n<sup>+</sup> region have better immunity to DIBL. Second, VSA-TFTs with a longer floating n<sup>+</sup> region also have better immunity under hot-carrier (HC) stress and self-heating (SH) stress. However, VSA-TFTs with a shorter floating n<sup>+</sup> region also have better immunity to positive gate bias (PGB) stress. Consequently, in order to optimize reliability characteristics, including SH stress, HC stress, and PGB stress, it is necessary to modulate the length of the floating n<sup>+</sup> region. Third, the PGB stress, rather than SH stress or HC stress, becomes a major issue for VSA-TFTs under the stress bias below 4 V. In other words, PGB stress will dominate the degradation behaviors when the stress bias is not high enough to achieve SH stress and HC stress. Finally, the worst degradation condition of VSA-TFTs under HC stress, similar to that of most TFT devices, occurs when the stress of  $V_G$  is less than half of  $V_D$ .

Index Terms—Hot-carrier (HC) stress, polycrystalline silicon thin-film transistors (poly-Si TFTs), positive gate bias (PGB) stress, self-heating (SH) stress, symmetric S/D, vertical channel.

#### I. INTRODUCTION

N THE LAST few decades, polycrystalline silicon thinfilm transistors (poly-Si TFTs) have attracted considerable attention because of their high field-effect mobility and potential applications, including active-matrix liquid crystal displays (AMLCDs), system on panel, nonvolatile memory, and 3-D circuit integration [1]–[5].

In order to obtain high-performance poly-Si TFTs for more high-level applications in the future, several studies for the enhancement of the devices' structure and characteristics have explored, such as high-k materials, double-channel structures, nanowire-channel devices, and sequential lateral solidification—crystallization processes [6]–[9]. We also propose a novel structure poly-Si TFT device to improve device characteristics, which is called the symmetric Vertical-channel Ni-SAlicided poly-Si TFT (VSA-TFT) [10], [11]. It has the

Manuscript received February 3, 2012; revised April 30, 2012 and May 3, 2012; accepted May 7, 2012. Date of publication June 11, 2012; date of current version July 19, 2012. This work was supported by the National Science Council of Taiwan under Contract NSC-100-2221-E-009-012-MY3. The review of this paper was arranged by Editor B. Kaczer.

The authors are with the National Chiao Tung University, Hsinchu 300, Taiwan.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2012.2199498

advantages of simple fabrication process, great potential for 3-D circuit integration, and easy scaling down of channel length without advanced photolithographic equipment.

The reliability of TFT devices is an important issue. Hence, before the practical application of such devices in AMLCDs or other high-level applications, their reliability characteristics must be clearly identified. Given this need, in this paper, we investigate the reliability characteristics of symmetric VSA-TFTs.

Several stress methods are generally used to understand the reliability characteristics of TFT devices, such as self-heating (SH) stress [12]–[15], hot-carrier (HC) stress [15]–[18], and bias temperature instability (BTI) stress [19]–[22]. In this paper, we compare the drain-induced barrier-lowering (DIBL) effect in Overlap, Offset, and GO-15-nm VSA-TFTs [11]. In addition, we investigate the reliability characteristics of VSA-TFTs, including SH stress, HC stress, and positive gate bias (PGB) stress.

#### II. EXPERIMENT

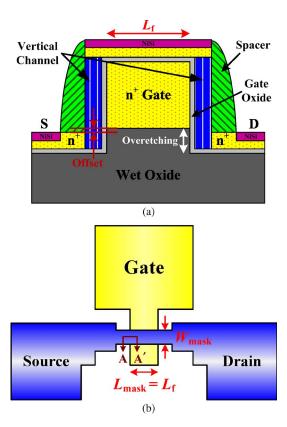

The key processes of VSA-TFTs were discussed in detail in our previous work [10], [11]. Fig. 1 displays the schematic cross section and top view of VSA-TFTs. The length of the floating  $\mathbf{n}^+$  region is defined by the mask channel length  $L_{\rm mask}$ , where the mask channel width  $W_{\rm mask}$  is equal to the effective channel width. The actual channel length of VSA-TFTs is defined as  $2\times$  the total thickness of the poly-Si gate, which is equal to  $0.4~\mu{\rm m}$ . The length of the floating  $\mathbf{n}^+$  region is defined by the mask channel length. Therefore, the length of the floating  $\mathbf{n}^+$  region is designated as " $L_{\rm mask}$ " in our previous work [10], [11]. In order to avoid confusing  $L_{\rm mask}$  with the actual channel length, we redesignate  $L_{\rm mask}$  as  $L_f$  in this paper.

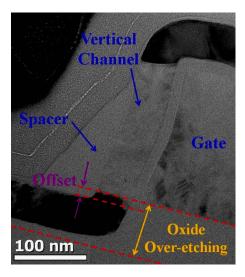

In this paper, we compare three kinds of VSA-TFTs, namely, Overlap, Offset, and GO-15-nm VSA-TFTs. The gate oxide thickness of the Overlap VSA-TFTs is 30 nm, and the overlap region between the gate and S/D edges is about 40 nm. The gate oxide thickness of the Offset VSA-TFTs is also 30 nm, but there is an offset region between the gate and S/D edges of about 40 nm instead of an overlap region. Fig. 2 shows the cross-sectional transmission electron microscope (TEM) microphotograph of the GO-15-nm VSA-TFTs [along the A-A' direction in Fig. 1(b)]. The gate oxide thickness of the GO-15-nm VSA-TFTs is 15 nm, and the offset region between the gate and S/D edges is about 15 nm. Finally, all the devices were fabricated with 10-min NH<sub>3</sub> plasma treatment to passivate the defects in the poly-Si channel film [23].

Fig. 1. (a) Schematic cross section and (b) top view of VSA-TFTs.

Fig. 2. Cross-sectional TEM microphotograph of GO-15-nm VSA-TFTs.

# III. RESULTS AND DISCUSSION

#### A. Device Performance and DIBL Effect

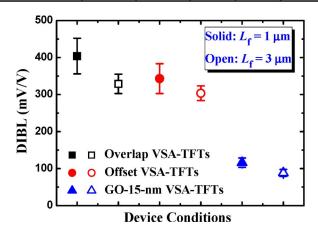

Several important parameters of Overlap, Offset, and GO-15-nm VSA-TFTs with 10-min NH $_3$  plasma treatment and  $L_f=3~\mu \mathrm{m}$  are listed in Table I. ON-state current  $I_{\mathrm{on}}$  is defined as the drain current at  $V_G=5~\mathrm{V}$  and  $V_D=0.1~\mathrm{V}$ , and OFF-state current  $I_{\mathrm{off}}$  is defined as the minimum drain current at  $V_D=0.1~\mathrm{V}$ . The GO-15-nm VSA-TFTs have better subthreshold swing (S.S.) and higher on/off current ratio than the other devices. More detailed discussions of the VSA-TFTs' performance are reported in our previous work [10], [11]. Fig. 3 exhibits the DIBL effects of Overlap, Offset, and GO-15-nm

TABLE I IMPORTANT PARAMETERS OF OVERLAP, OFFSET, AND GO-15-nm VSA-TFTS WITH 10-min NH3 PLASMA TREATMENT AND  $L_f=3~\mu{\rm m}$

|                      | S.S.<br>(mV/dec) | Mobility (cm <sup>2</sup> /V·s) | I <sub>off</sub> (pA) | I <sub>on</sub> (uA) | on/off<br>ratio   |

|----------------------|------------------|---------------------------------|-----------------------|----------------------|-------------------|

| Overlap<br>VSA-TFTs  | 315              | 70                              | 0.46                  | 9.93                 | > 10 <sup>7</sup> |

| Offset<br>VSA-TFTs   | 269              | 67                              | 0.04                  | 5.59                 | > 10 <sup>8</sup> |

| GO-15-nm<br>VSA-TFTs | 127              | 50                              | 0.05                  | 5.76                 | > 108             |

Fig. 3. DIBL effects of Overlap, Offset, and GO-15-nm VSA-TFTs with different  $L_f.\,$

VSA-TFTs with different  $L_f$ . The GO-15-nm VSA-TFTs with  $L_f=3~\mu\mathrm{m}$  have the lowest DIBL value (88 mV/V) among the devices studied. The gate oxide thickness of the GO-15-nm VSA-TFTs is thinner than that of the other VSA-TFTs, resulting in better gate-to-channel control ability. Additionally, VSA-TFTs with  $L_f=3~\mu\mathrm{m}$  also have better immunity to DIBL effect due to the increased effective channel length resulting from the longer floating n<sup>+</sup> region. Therefore, the GO-15-nm VSA-TFTs with  $L_f=3~\mu\mathrm{m}$  have better immunity to DIBL effect. By the same token, the Offset VSA-TFTs have better immunity to DIBL effect than the Overlap VSA-TFTs due to the longer effective channel length resulting from the offset region.

In order to understand the reliability characteristics of TFT devices, the SH stress, HC stress, and PGB stress are used to understand the degradation behaviors (more than 30 devices were used to compare).

## B. SH and HC Stressing

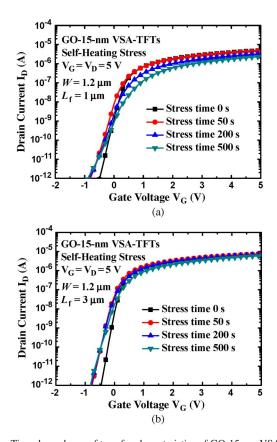

Fig. 4 shows the time dependence of the transfer characteristics of the GO-15-nm VSA-TFTs with (a)  $L_f=1~\mu{\rm m}$  and (b)  $L_f=3~\mu{\rm m}$  at  $V_D=0.1$  V under SH stress of  $V_G=5$  V,  $V_D=5$  V. It is obvious that  $I_{\rm on}$ , S.S., and  $V_{\rm th}$  are degraded after a long period of SH stressing. In addition, the device with  $L_f=1~\mu{\rm m}$  exhibits more serious degradation behavior than the device with  $L_f=3~\mu{\rm m}$ . The degradation behavior of SH stress is due to Joule heating and the damage generated along the entire channel [15]. Hence, the positive  $\Delta V_{\rm th}$  trends result from the degradation of S.S. and  $I_{\rm on}$  after SH stress.

Fig. 4. Time dependence of transfer characteristics of GO-15-nm VSA-TFTs with (a)  $L_f=1~\mu{\rm m}$  and (b)  $L_f=3~\mu{\rm m}$  at  $V_D=0.1~{\rm V}$  under SH stress of  $V_G=5~{\rm V}, V_D=5~{\rm V}.$

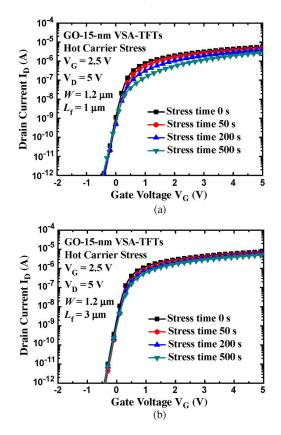

The threshold voltage shifts  $\Delta V_{\mathrm{th}}$  and on-state current change  $\Delta I_{\rm on}$  percentage as a function of stress time for GO-15-nm VSA-TFTs with different  $L_f$  under different SH stress biases are extracted, as shown in Fig. 5. In general,  $V_{\rm th}$ is defined as the applied gate voltage when the drain current achieves a normalized value. However, all the GO-15-nm VSA-TFTs have the same W/L. Therefore,  $V_{\rm th}$  is directly defined as the applied gate voltage when the drain current  $I_D = 20$  nA at  $V_D = 0.1$  V.  $I_{\rm on0}$  is the initial value of  $I_{\rm on}$ , and  $\Delta I_{\rm on}$  is the changes in  $I_{\rm on}$  after stress.  $\Delta V_{\rm th}$  and  $\Delta I_{\rm on}$  become significant when the stress biases are raised. The degradation behaviors are also more serious when  $L_f$  is decreased from 3 to 1  $\mu$ m. This is due to that the device with  $L_f = 3 \mu$ m has a longer electrical effective channel length, resulting in a slight reduction of drain currents under SH stress. The electrical effective channel length can be regarded as  $2\times$  the total thickness of the poly-Si gate  $+L_f$ . Thus, the device with  $L_f = 3 \,\mu \text{m}$  has a longer electrical effective channel length than the device with  $L_f = 1 \mu m$ . Hence, GO-15-nm VSA-TFTs with  $L_f = 3 \mu m$  have better immunity to SH degradation. Fig. 6 shows the time dependence of the transfer characteristics of GO-15-nm VSA-TFTs with (a)  $L_f = 1 \mu m$  and (b)  $L_f =$ 3  $\mu$ m at  $V_D=0.1$  V under HC stress of  $V_G=2.5$  V,  $V_D=5$  V. The S.S. characteristics and  $V_{

m th}$  are almost identical after stressing. However, negative  $\Delta I_{\rm on}$  is obvious after HC stress. The degradation behavior of HC stress is different from that of SH stress. This is due to the energetic HCs generated near the drain side under a high drain electric field, causing damage in the grain boundaries and poly-Si/SiO<sub>2</sub> interfaces [15], [24].

Fig. 5.  $\Delta V_{\rm th}$  and  $\Delta I_{\rm on}$  percentages as a function of stress time for GO-15-nm VSA-TFTs with different  $L_f$  under different SH stress biases.

Fig. 6. Time dependence of transfer characteristics of GO-15-nm VSA-TFTs with (a)  $L_f=1~\mu{\rm m}$  and (b)  $L_f=3~\mu{\rm m}$  at  $V_D=0.1~{\rm V}$  under HC stress of  $V_G=2.5~{\rm V}, V_D=5~{\rm V}.$

The damage to the grain boundaries and poly-Si/SiO $_2$  interfaces near the drain side strongly affects the ON-state carrier transport, leading to  $I_{\rm on}$  degradation. Because HC stress results in local damage near the drain side, there is less damage in the channel region under lower gate bias than with SH stress. Therefore, degradation of S.S. and  $\Delta V_{\rm th}$  is marginal under HC stressing. This SH and HC degradation phenomenon is consistent with the reported literature [12], [15], [16].

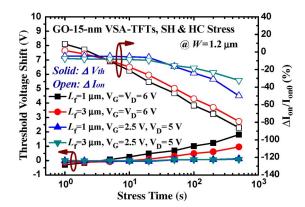

The  $\Delta V_{\rm th}$  and  $\Delta I_{\rm on}$  percentages as a function of stress time for GO-15-nm VSA-TFTs with different  $L_f$  under SH stress of  $V_G=6$  V,  $V_D=6$  V and HC stress of  $V_G=2.5$  V,  $V_D=5$  V are extracted, as shown in Fig. 7. Positive  $\Delta V_{\rm th}$  and negative  $\Delta I_{\rm on}$  after a long period of SH stressing are more serious

Fig. 7.  $\Delta V_{\rm th}$  and  $\Delta I_{\rm on}$  percentages as a function of stress time for GO-15-nm VSA-TFTs with different  $L_f$  under SH stress of  $V_G=6$  V,  $V_D=6$  V and HC stress of  $V_G=2.5$  V,  $V_D=5$  V.

than those after a long period of HC stressing. Furthermore, GO-15-nm VSA-TFTs with longer  $L_f=3~\mu\mathrm{m}$  not only have better immunity to SH degradation but also have better immunity to HC degradation due to the reduced drain currents [15] and suppressed electrical field near the drain, respectively [10]. Hence, Joule heating and the HC impact ionization rate may be mitigated by increasing  $L_f$ , leading to better immunity to SH and HC degradation.

#### C. PGB Stressing

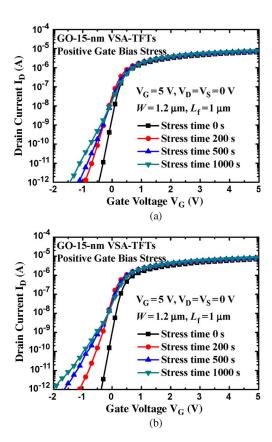

Fig. 8 shows the time dependence of the transfer characteristics of GO-15-nm VSA-TFTs with (a)  $L_f=1~\mu{\rm m}$  and (b)  $L_f=3~\mu{\rm m}$  at  $V_D=0.1~{\rm V}$  under PGB stress of  $V_G=5~{\rm V}, V_D=0~{\rm V}.$  Generally speaking, the devices will produce positive  $\Delta V_{\rm th}$  and negative  $\Delta I_{\rm on}$  after PGB stress. This indicates that electrons are trapped in the gate oxide under PGB stress. However, the trends of  $\Delta V_{\rm th}$  and  $\Delta I_{\rm on}$  in GO-15-nm VSA-TFTs under PGB stress conflict with reported results on the planar device [20]–[22]. In Fig. 8, it is evident that S.S. degradation, negative  $\Delta V_{\rm th}$ , and positive  $\Delta I_{\rm on}$  occur at the same time. These measured results indicate that the degradation mechanism of GO-15-nm VSA-TFTs under PGB stress of  $V_G=5~{\rm V}, V_D=0~{\rm V}$  was not consistent with electrons being trapped in the gate oxide.

In our VSA-TFTs, the actual channel length is defined as  $2\times$ the total thickness of the poly-Si gate. However, the electrical effective channel length can be regarded as  $2\times$  the total thickness of the poly-Si gate  $+L_f$ . The floating n<sup>+</sup> region above the n<sup>+</sup> gate also suffers PGB stress. Apparently, another mechanism dominates the degradation behavior. Ma et al. proposed that the accelerated electrons would collide with the weak bond of the grain boundaries and damage the poly-Si channel film, generate the trap states, increase S.S., and reduce  $I_{\rm on}$  under PBTI stress [20]. Cheng et al. and Lee et al. demonstrated that the TFT devices not only have Si-H bonds but also exhibit Si-N bond formation to terminate the dangling bonds in the grains and grain boundaries in the channel region after NH<sub>3</sub> plasma passivation [25], [26]. Many studies report that Si-H bonds are broken by HC stress and gate bias stress more easily than Si–N bonds [23], [26]–[30]. Liao et al. proposed that hydrogen may diffuse into the gate oxide and decrease the threshold voltage subsequently after the Si-H bond has been broken [22]. Furthermore, the stress bias of  $V_G = 5$  V is not high enough to

Fig. 8. Time dependence of transfer characteristics of GO-15-nm VSA-TFTs with (a)  $L_f=1~\mu{\rm m}$  and (b)  $L_f=3~\mu{\rm m}$  at  $V_D=0.1$  V under PGB stress of  $V_G=5$  V,  $V_D=0$  V.

Fig. 9.  $\Delta V_{\rm th}$  and  $\Delta I_{\rm on}$  percentages as a function of stress time for GO-15-nm VSA-TFTs with different  $L_f$  under different PGB stress.

cause Fowler–Nordheim (F–N) tunneling, leading to electrons being trapped in the gate oxide. Therefore, we believe that one of the reasons for negative  $\Delta V_{\rm th}$  is due to the break in the weak Si–H bonds and the diffusion of hydrogen into the gate oxide and channel film. Another reason for negative  $\Delta V_{\rm th}$  can be attributed to the degradation of S.S.

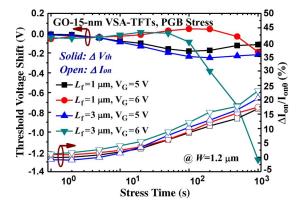

The  $\Delta V_{\rm th}$  and  $\Delta I_{\rm on}$  percentages as a function of stress time for GO-15-nm VSA-TFTs with different  $L_f$  under different PGB stress are extracted, as shown in Fig. 9. Fig. 9 shows that the negative  $\Delta V_{\rm th}$  of GO-15-nm VSA-TFTs with  $L_f=3~\mu{\rm m}$  is more serious than that of GO-15-nm VSA-TFTs with  $L_f=1~\mu{\rm m}$ . We posit that the GO-15-nm VSA-TFTs with  $L_f=3~\mu{\rm m}$  have more hydrogen diffused into the gate oxide than the GO-15-nm VSA-TFTs with  $L_f=1~\mu{\rm m}$ .

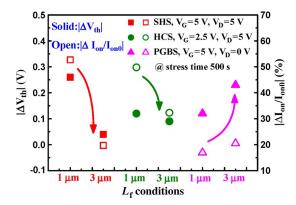

Fig. 10. Comparison the degradation behavior of SH stress, HC stress, and PGB stress of GO-15-nm VSA-TFTs with different  $L_f$ .

Because the GO-15-nm VSA-TFTs with  $L_f=3~\mu\mathrm{m}$  have a longer floating n<sup>+</sup> region and have more broken Si-H bonds after PGB stress, more hydrogen is diffused into the gate oxide, resulting in extra negative  $\Delta V_{\rm th}$ . Particularly, the negative  $\Delta V_{\rm th}$ trend of the stress bias at  $V_G = 6$  V for  $L_f = 3$   $\mu m$  and for  $L_f = 1 \,\mu\mathrm{m}$  occurs after 50 and 200 s, respectively. The negative  $\Delta V_{\rm th}$  of stress bias at  $V_G=6$  V for  $L_f=3~\mu{\rm m}$  after a long stress time is significant. This may be attributed to the greater number of broken Si-H bonds and more hydrogen diffusion into the gate oxide under higher gate stress bias. However, the negative  $\Delta V_{\rm th}$  trend of stress bias at  $V_G = 5$  V is more serious than when the stress bias at  $V_G = 6$  V after 10 s, as shown in Fig. 9. According to the measured results, it appears that the stress bias of  $V_G = 6$  V could generated more F-N and trap-assisted tunneling than the stress bias of  $V_G = 5$  V. Under a stress bias of  $V_G = 6$  V, the mechanism of broken Si-H bonds competes with F-N tunneling and trap-assisted tunneling. After a long stress time, the broken Si-H bonds are the main mechanisms in the more negative  $\Delta V_{\rm th}$ , particularly when  $L_f = 3 \mu \text{m}$ . Fig. 9 shows that GO-15-nm VSA-TFTs with  $L_f = 3 \,\mu \text{m}$  and stress bias at  $V_G = 6 \,\text{V}$  have more positive  $\Delta I_{\rm on}$  than GO-15-nm VSA-TFTs with  $L_f=1~\mu{\rm m}$  and with a stress bias of  $V_G = 5$  V.  $I_{\rm on}$  after stress becomes higher than the initial state, probably due to negative  $\Delta V_{\rm th}$ . However, the degradation behavior of PGB stress for different  $L_f$  is opposite that of SH stress and HC stress, as shown in Fig. 10. Hence, in order to optimize reliability characteristics, including SH stress, HC stress, and PGB stress, it is important to trade off the length of the floating n<sup>+</sup> region. Here, we find the best condition to be  $L_f = 2 \mu \text{m}$ .

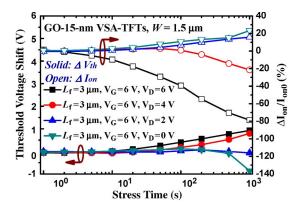

# D. Bias Dependent on SH, HC, and PGB Stressing

Fig. 11 shows the  $\Delta V_{\rm th}$  and  $\Delta I_{\rm on}$  percentages as a function of stress time for GO-15-nm VSA-TFTs under different stress biases with fixed  $V_G=6$  V and various  $V_D$ .  $\Delta V_{\rm th}$  changes from positive to negative as the  $V_D$  bias decreases due to reduced Joule heating rate. Furthermore, the  $V_G$  bias becomes increasingly important and dominates the degradation behaviors when the  $V_D$  bias is decreased. The  $\Delta I_{\rm on}$  behavior also shows the same trends.  $\Delta I_{\rm on}$  changes from negative to positive when the  $V_D$  bias is reduced. Hence, the degradation behavior is similar to that of PGB stress when the  $V_D$  bias is insufficiently high  $(V_D \le 2 \text{ V})$ .

Fig. 11.  $\Delta V_{\rm th}$  and  $\Delta I_{\rm on}$  percentages as a function of stress time for GO-15-nm VSA-TFTs under different stress biases with fixed  $V_G=6~{\rm V}$  and various  $V_D$ .

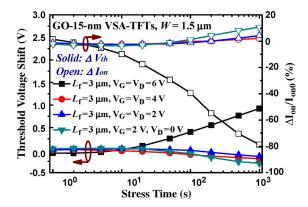

Fig. 12.  $\Delta V_{\rm th}$  and  $\Delta I_{\rm on}$  percentages as a function of stress time for GO-15-nm VSA-TFTs under different  $V_G=V_D$  stress bias and PSG stress of  $V_G=2~{\rm V}, V_D=0~{\rm V}.$

Fig. 12 shows the  $\Delta V_{\rm th}$  and  $\Delta I_{\rm on}$  percentages as a function of stress time for GO-15-nm VSA-TFTs under different  $V_G=V_D$  stress biases and PSG stress of  $V_G=2$  V,  $V_D=0$  V. Except for the stress bias of  $V_G=V_D=6$  V, all show negative  $\Delta V_{\rm th}$  and positive  $\Delta I_{\rm on}$ . Furthermore, the negative  $\Delta V_{\rm th}$  and positive  $\Delta I_{\rm on}$  of the stress bias of  $V_G=2$  V are more serious than those of the stress bias of  $V_G=V_D=4$  V and  $V_G=V_D=2$  V. This shows that PGB stress will dominate the degradation behavior when the stress bias is below 4 V (consistent with the results of Fig. 11). Hence, when the device completely operates at low voltage (below 4 V), the best condition for optimum reliability characteristics is  $L_f=1$   $\mu$ m.

In both bulk silicon and single-crystal silicon, the worst HC degradation occurs when the stress bias of  $V_G$  is about half of  $V_D$  since it has the highest rate of impact ionization. This can be obtained from the substrate current  $I_{\rm sub}$ . When  $I_{\rm sub}$  rises to the maximum value, the rate of impact ionization is highest [31]. However, the worst HC degradation in TFT devices always occurs when the stress bias of  $V_G$  is less than half of  $V_D$  [15], [22].

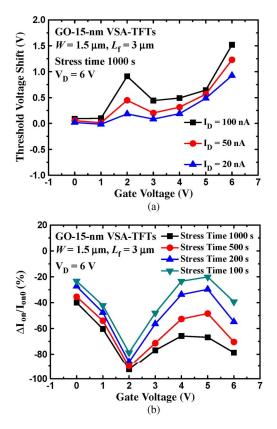

We sought to determine the worst HC degradation condition in our novel VSA-TFTs. Fig. 13 shows the (a) dependence of  $\Delta V_{\rm th}$  on  $V_G$  stress at fixed  $V_D=6$  V with different constant  $I_D$  and (b) dependence of  $\Delta I_{\rm on}$  on  $V_G$  stress at fixed  $V_D=6$  V with different stress times. Because S.S. is almost the same and negative  $\Delta I_{\rm on}$  is obvious after HC stress, we use different

Fig. 13. (a) Dependence of  $\Delta V_{\rm th}$  on  $V_G$  stress at fixed  $V_D=6$  V with different constant  $I_D$  and (b) dependence of  $\Delta I_{\rm on}$  on  $V_G$  stress at fixed  $V_D=6$  V with different stress times.

constant  $I_D$  to extract  $V_{\rm th}$ . Results indicate that the largest  $\Delta V_{\rm th}$  occurs when the stress bias of  $V_G=1/3~{\rm V}_D$  (except  $V_G=5$  and 6 V) under all constant  $I_D$ . It also indicates that the largest negative  $\Delta I_{\rm on}$  occurs when the stress bias of  $V_G=1/3~{\rm V}_D$  for all stress times. Thus, the worst HC degradation condition is  $V_G=1/3~{\rm V}_D$  for novel VSA-TFTs.

## IV. CONCLUSION

In this paper, we have investigated the DIBL effect and the reliability issues, including SH stress, HC stress, and PGB stress, for VSA-TFTs. The GO-15-nm VSA-TFTs have better immunity to DIBL effect than the Overlap and Offset VSA-TFTs. Additionally, VSA-TFTs with a longer floating  $\mathbf{n}^+$  region have better immunity to DIBL effect. In HC stress and SH stress, VSA-TFTs with a longer floating  $\mathbf{n}^+$  region also have better immunity. However, VSA-TFTs with a shorter floating  $\mathbf{n}^+$  region have better immunity to PGB stress. PGB stress will dominate the degradation behaviors when the stress bias is below 4 V. Consequently, the length of the floating  $\mathbf{n}^+$  region is the key parameter for reliability characteristics. Finally, the worst HC degradation condition of VSA-TFTs, which is similar to that of most TFT devices, occurs when the stress of  $V_G$  is less than half of  $V_D$ .

#### ACKNOWLEDGMENT

The authors would like to thank the Nano Facility Center of National Chiao Tung University and the National Nano Device Laboratory for providing process equipment.

#### REFERENCES

- S. D. Brotherton, "Polycrystalline silicon thin film transistors," Semicond. Sci. Technol., vol. 10, no. 6, pp. 721–738, Jun. 1995.

- [2] K. Werner, "The flowering of flat displays," *IEEE Spectr.*, vol. 34, no. 5, pp. 40–49, May 1997.

- [3] T. Y. Chiang, W. C. Y. Ma, Y. H. Wu, K. T. Wang, and T. S. Chao, "A novel PN-diode structure of SONOS-type TFT NVM with embedded siliconnanocrystals," *IEEE Electron Device Lett.*, vol. 31, no. 11, pp. 1239–1241, Nov. 2010.

- [4] Y. H. Lu, P. Y. Kuo, Y. H. Wu, Y. H. Chen, and T. S. Chao, "Novel GAA raised source/drain sub-10-nm poly-Si NW channel TFTs with self-aligned corked gate structure for 3-D IC applications," in *VLSI Symp. Tech. Dig.*, 2011, pp. 142–143.

- [5] H. Wang, M. Chan, S. Jagar, Y. Wang, and P. K. Ko, "Submicron super TFTs for 3-D VLSI applications," *IEEE Trans. Electron Devices*, vol. 21, no. 9, pp. 439–441, Sep. 2000.

- [6] M. J. Yang, C. H. Chien, Y. H. Lu, C. Y. Shen, and T. Y. Huang, "Electrical properties of low-temperature-compatible P-channel polycrystalline-silicon TFTs using high-κ gate dielectrics process," *IEEE Trans. Electron Devices*, vol. 55, no. 4, pp. 1027–1034, Apr. 2008.

- [7] F. T. Chien, C. M. Fang, C. N. Liao, C. W. Chen, C. H. Cheng, and Y. T. Tsai, "A novel high-performance poly-silicon thin-film transistor with a double-channel structure," *IEEE Electron Device Lett.*, vol. 29, no. 11, pp. 1229–1231, Nov. 2008.

- [8] Y. H. Lu, P. Y. Kuo, Y. H. Wu, Y. H. Chen, and T. S. Chao, "Novel sub-10-nm gate-all-around Si nanowire channels poly-Si TFTs with raised source/drain," *IEEE Electron Devices Lett.*, vol. 32, no. 2, pp. 173–175, Feb. 2011.

- [9] M. K. Kang, S. J. Kim, and H. J. Kim, "Improved uniformity of sequential lateral solidification thin-film transistors," *IEEE Electron Devices Lett.*, vol. 32, no. 6, pp. 767–769, Jun. 2011.

- [10] Y. H. Wu, P. Y. Kuo, Y. H. Lu, Y. H. Chen, and T. S. Chao, "Novel symmetric vertical channel nickel-salicided poly-Si thin-film transistors with high ON/OFF current ratio," *IEEE Electron Device Lett.*, vol. 31, no. 11, pp. 1233–1235, Nov. 2010.

- [11] Y. H. Wu, P. Y. Kuo, Y. H. Lu, Y. H. Chen, T. Y. Chiang, K. T. Wang, L. C. Yen, and T. S. Chao, "Symmetric vertical-channel nickel-salicided poly-Si thin-film transistors with self-aligned oxide overetching structures," *IEEE Trans. Electron Devices*, vol. 58, no. 7, pp. 2008–2013, Jul. 2011.

- [12] S. Inoue, H. Ohshima, and T. Shimoda, "Analysis of degradation phenomenon caused by self-heating in low-temperature-processed polycrystalline silicon thin film transistors," *Jpn. J. Appl. Phys.*, vol. 41, no. 11A, pp. 6313–6319, Nov. 2002.

- [13] A. Valletta, A. Moroni, L. Mariucci, A. Bonfiglietti, and G. Fortunato, "Self-heating effects in polycrystalline silicon thin film transistors," *Appl. Phys. Lett.*, vol. 89, no. 9, pp. 093509-1–093509-3, Aug. 2006.

- [14] K. Takechi, M. Nakata, H. Kanoh, S. Otsuki, and S. Kaneko, "Dependence of self-heating effects on operation conditions and device structures for polycrystalline silicon TFTs," *IEEE Trans. Electron Devices*, vol. 53, no. 2, pp. 251–257, Feb. 2006.

- [15] M. Xue, M. Wang, Z. Zhu, D. Zhang, and M. Wong, "Degradation behaviors of metal-induced laterally crystallized n-type polycrystalline silicon thin-film transistors under DC bias stresses," *IEEE Trans. Electron Devices*, vol. 54, no. 2, pp. 225–232, Feb. 2007.

- [16] F. V. Farmakis, J. Brini, G. Kamarinos, and C. A. Dimitriadis, "Anomalous turn-on voltage degradation during hot-carrier stress in polycrystalline silicon thin-film transistors," *IEEE Electron Device Lett.*, vol. 22, no. 2, pp. 74–76, Feb. 2001.

- [17] A. T. Hatzopoulos, D. H. Tassis, N. A. Hastas, C. A. Dimitriadis, and G. Kamarinos, "An analytical hot-carrier induced degradation," *IEEE Trans. Electron Devices*, vol. 52, no. 10, pp. 2182–2187, Oct. 2005.

- [18] A. T. Voutsas, D. N. Kouvatsos, L. Michalas, and G. J. Papaioannou, "Effect of silicon thickness on the degradation mechanisms of sequential laterally solidified polycrystalline silicon TFTs during hot-carrier stress," *IEEE Electron Device Lett.*, vol. 26, no. 3, pp. 181–184, Mar. 2005.

- [19] N. Bhat, M. Cao, and K. C. Saraswat, "Bias temperature instability in hydrogenated thin-film transistors," *IEEE Trans. Electron Devices*, vol. 44, no. 7, pp. 1102–1108, Jul. 1997.

- [20] M. W. Ma, C. Y. Chen, C. J. Su, W. C. Wu, Y. H. Wu, K. H. Kao, T. S. Chao, and T.-F. Lei, "Characteristics of PBTI and hot carrier stress for LTPS-TFT with high- $\kappa$  gate dielectric," *IEEE Electron Device Lett.*, vol. 29, no. 2, pp. 171–173, Feb. 2008.

- [21] M. W. Ma, C. Y. Chen, W. C. Wu, C. J. Su, K. H. Kao, T. S. Chao, and T.-F. Lei, "Reliability mechanisms of LTPS-TFT with HfO<sub>2</sub> gate dielectric: PBTI, NBTI, and hot-carrier stress," *IEEE Trans. Electron Devices*, vol. 55, no. 5, pp. 1153–1160, May 2008.

- [22] C. C. Liao, M. C. Lin, T. Y. Chiang, and T. S. Chao, "Effects of channel width and nitride passivation layer on electrical characteristics of polysilicon thin-film transistors," IEEE Trans. Electron Devices, vol. 58, no. 11, pp. 3812-3819, Nov. 2011.

- [23] F. S. Wang, M. J. Tsai, and H. C. Cheng, "The effects of NH<sub>3</sub> plasma passivation on polycrystalline silicon thin-film transistors," IEEE Electron Device Lett., vol. 16, no. 11, pp. 503-505, Nov. 1995.

- [24] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices, 2nd ed. Cambridge, U.K.: Cambridge Univ. Press, 2009, p. 197.

- [25] H. C. Cheng, F. S. Wang, and C. Y. Huang, "Effects of NH3 plasma passivation on n-channel polycrystalline silicon thin-film transistors," IEEE Trans. Electron Devices, vol. 44, no. 1, pp. 64-68, Jan. 1997.

- [26] Y. S. Lee, H. Y. Lin, T. F. Lei, T. Y. Huang, T. C. Chang, and C. Y. Chang, "Comparison of N2 and NH3 plasma passivation effects on polycrystalline silicon thin-film transistors," Jpn. J. Appl. Phys., vol. 37, no. 7A, pp. 3900-3903, Jul. 1998.

- [27] C. H. Kim, S. H. Jung, J. S. Yoo, and M. K. Han, "Poly-Si TFT fabricated by laser-induced in-situ fluorine passivation and laser doping," IEEE Electron Device Lett., vol. 22, no. 8, pp. 396-398, Aug. 2001.

- [28] H. Tu, T. C. Chang, P. T. Liu, H. W. Zan, Y. H. Tai, C. Y. Yang, Y. C. Wu, H. C. Liu, W. R. Chen, and C. Y. Chang, "Enhanced performance of poly-Si thin film transistors using fluorine ions implantation," Electrochem. Solid-State Lett., vol. 8, no. 9, pp. G246-G248, Jul. 2005.

- [29] M. W. Ma, C. Y. Chen, C. J. Su, W. C. Wu, Y. H. Wu, T. Y. Yang, K. H. Kao, T. S. Chao, and T.-F. Le, "Impacts of fluorine ion implantation with low-temperature solid-phase crystallized activation on high-  $\!\kappa$ LTPS-TFT," IEEE Electron Device Lett., vol. 29, no. 2, pp. 168-170, Feb. 2008.

- [30] C. P. Chang and Y. S. Wu, "Improved electrical performance of MILC poly-Si TFTs using CF4 plasma by etching surface of channel," IEEE Electron Device Lett., vol. 30, no. 2, pp. 130–132, Feb. 2009.

- [31] M. Wada, T. Shibata, M. Konaka, H. Iizuka, and R. L. M. Dang, "A twodimensional computer simulation of hot carrier effects in MOSFETs," in IEDM Tech. Dig., 1981, pp. 223-336.

Yi-Hong Wu is currently working toward the Ph.D. degree in the Department of Electrophysics, National Chiao Tung University, Hsinchu, Taiwan.

His research interests include the studies of LTPS-TFTs, novel structure TFTs, and non-volatile memory.

Je-Wei Lin is currently working toward the Ph.D. degree in the Department of Electrophysics, National Chiao Tung University, Hsinchu, Taiwan.

His research interests include the studies of high-efficiency monocrystalline silicon and metalinsulator-semiconductor solar cells.

electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2007.

He joined the Department of Electrophysics, National Chiao Tung University, where he has been a postdoctoral researcher since 2008.

Yi-Hsien Lu is currently working toward the Ph.D. degree in the Department of Electrophysics.

His current research topic is the fabrication and characterization of novel-structure poly-Si TFTs.

Rou-Han Kuo is currently working toward the M.S. degree in the Department of Electrophysics, National Chiao Tung University, Hsinchu, Taiwan.

Her current research topic is vertical-channel thinfilm transistors.

Li-Chen Yen is currently working toward the Ph.D. degree in the Department of Electrophysics, National Chiao Tung University, Hsinchu, Taiwan.

His research interest includes the studies of biosensors, NVM, and high-k technology.

Yi-Hsuan Chen is currently working toward the Ph.D. degree in the Department of Electrophysics.

Her research interests include the studies of LTPS-TFTs, T-FETs, and NVM.

Chia-Chun Liao is currently working toward the Ph.D. degree in the Department of Electrophysics.

His research interests include strain technique, PE-ALD for metal-gate/high-k application, and NVM.

Po-Yi Kuo (M'03) received the Ph.D. degree in

Tien-Sheng Chao received the Ph.D. degree in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 1992.

Since 2002, he has been a Professor at the Department of Electrophysics, National Chiao Tung University. He was engaged in developing thindielectrics preparations, cleaning processes, and complementary metal-oxide-semiconductor device fabrication