Home Search Collections Journals About Contact us My IOPscience

# Optical Studies of GaAs Nanowires Grown on Trenched Si(001) Substrate by Cathodoluminescence

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2012 Jpn. J. Appl. Phys. 51 06FG15

(http://iopscience.iop.org/1347-4065/51/6S/06FG15)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 28/04/2014 at 18:36

Please note that terms and conditions apply.

DOI: 10.1143/JJAP.51.06FG15

# Optical Studies of GaAs Nanowires Grown on Trenched Si(001) Substrate by Cathodoluminescence

Ling Lee, Kun-Feng Chien, Wen-Chung Fan, Wu-Ching Chou\*, Chih-Hsin Ko¹, Cheng-Hsien Wu¹, You-Ru Lin¹, Cheng-Tien Wan¹, Clement H. Wann¹, Chao-Wei Hsu², Yung-Feng Chen², and Yan-Kuin Su²

Department of Electrophysics, National Chiao Tung University, Hsinchu 300, Taiwan, Republic of China

Received November 30, 2011; accepted February 21, 2012; published online June 20, 2012

The strains in GaAs nanowires, which were grown from 1700- to 80-nm-wide trenches on the Si(001) wafer with SiO<sub>2</sub> masks, were investigated by cathodoluminescence. For 1700- to 500-nm-wide trenches, the in-plane tensile strain at 15 K decreases with the decreasing trench width. The strain increases abruptly when the trench width is 300 nm, and then decreases as the trench width is further decreased. The results revealed that the stress induced by the SiO<sub>2</sub> sidewalls dominates when the width is less than the depth of the trench. This approach provides an effective technique to measure the strain of a single nanowire and helps for the demonstration of selectively-grown GaAs with a designed strain.

© 2012 The Japan Society of Applied Physics

#### 1. Introduction

The development of a device-quality GaAs layer on Si substrates which benefits monolithic optoelectronic and high speed integrated circuits (IC) draws increasing attentions. <sup>1–5)</sup> The epitaxial growth encounters challenges from not only structural defects, <sup>6-8)</sup> but also the residual strain. <sup>9-11)</sup> A lattice mismatch of 4.2% between GaAs and Si at growth temperature is relaxed by dislocations at the interface. <sup>12)</sup> On the other hand the subsequent cooling to room temperature induces thermal strain owing to the large difference of the thermal expansion coefficient. <sup>13)</sup> The thermal strain shifts the bandgap energy and splits the near-band-edge emission. 14,15) In order to suppress the defects and to control the residual strain in GaAs, several approaches have been applied, including graded SiGe buffer layer, 16-18) bent and undercut substrates, <sup>19,20)</sup> and selective aspect ratio trapping. <sup>21–23)</sup> Although the defect-free GaAs nanowires grown from trenches with widths of 80 to 100 nm were achieved, 22,23) the influence of the trench on strains in GaAs nanowires is not completely understood yet. In this study, cathololuminescence (CL) was used to measure the strain of a single GaAs nanowire and discover the origin of the strain. The dependence of the strain on the aspect ratio, defined as the depth dividing by the width, of the trench was discussed, which can help for the future fabrication of GaAs nanowire with designed strain.

## 2. Experimental Methods

The specimen preparation began with a 250-nm-thick  $\rm SiO_2$  mask layer that was deposited on a  $\rm Si(001)$  wafer at room temperature. Trenches along the [110] direction with widths range between 80 and 1700 nm were fabricated using 193 nm immersion lithography and reactive ion etching. The wafer was not immersed in HF solution to reserve the  $\rm SiO_2$  trenches of about 250 nm depth before the growth of GaAs. The GaAs nanowires were deposited in these trenches using a commercial metalorganic chemical vapor deposition (MOCVD) system at 70 Torr. After a thermal annealing at 700 °C to remove residual native oxide and contaminations on Si surface, a low-temperature buffer layer at 430 °C

**Fig. 1.** Schematic structure of the GaAs nanowire grown from trenched Si substrate (a), and the cross-sectional SEM image for a single 300-nm-wide trench (b).

followed by a high-temperature top layer at 650 °C were grown. Figure 1(a) illustrates the schematic structure of GaAs nanowires embedded in trench and the cross-sectional scanning electron microscopy (SEM) image of a 300-nm-wide trench. The optical investigations were carried out by the temperature-dependent CL measurement using a JEOL JSM-7001F microscope which was operated at 16 keV and 15 nA. The CL signals were analyzed by a Horiba Jobin-Yvon iHR550 0.5 m monochromator and detected using an LN<sub>2</sub>-cooled charge-coupled device (CCD) with an energy resolution of 0.3 meV.

#### 3. Results and Discussion

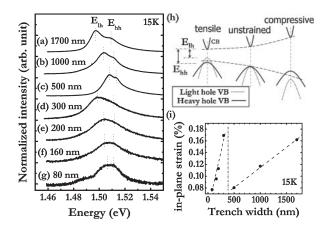

The optical properties of GaAs nanowires as a function of trench width were investigated by CL measurements at low temperature of 15 K. The electron beam was focused at the center of the nanowires and the CL spectra were shown in Figs. 2(a) to 2(g). At 15 K, the CL spectrum of GaAs grown from the 1700-nm-wide trench reveals two emission peaks at 1.508 and 1.497 eV, as shown in Fig. 2(a). The peak positions shift to lower energy, in comparison to that of the strain-free GaAs of 1.517 eV,  $^{24}$  indicating GaAs is under an in-plane tensile strain mainly from the bottom since the trench is 1700 nm wide and only 250 nm deep. Figure 2(h) shows the schematic band diagram near the  $\Gamma$  point of the strained GaAs.  $^{25,26}$  The in-plane tensile strain not only reduces the band gap energy, but also induces the splitting of heavy-hole (solid) and light-hole (dot) bands. The transition

<sup>&</sup>lt;sup>1</sup> Taiwan Semiconductor Manufacturing Co., Ltd., Hsinchu 300, Taiwan, Republic of China

<sup>&</sup>lt;sup>2</sup>Institute of Microelectronics, National Cheng Kung University, Tainan 701, Taiwan, Republic of China

<sup>(</sup>a) (b)

SiO<sub>2</sub> GaAs SiO<sub>2</sub> GaAs SiO<sub>2</sub> Si

Si substrate [110] 250 nm

<sup>\*</sup>E-mail address: wuchingchou@mail.nctu.edu.tw

**Fig. 2.** The 15 K CL spectra of GaAs nanowires grown from trenches with various widths (a) to (g). Schematic band structure of the unstrained, compressive and tensile strained GaAs (h), and the calculated strains at 15 K for GaAs nanowires with various widths (i).

energies from the conduction band to the heavy- and lighthole bands are expressed as  $E_{hh}$  and  $E_{lh}$ , respectively, and labeled in the CL spectra.  $E_{\rm hh}$  is larger than  $E_{\rm lh}$  due to the tensile strain. As the trench width decreases from 1700 to 1000 and 500 nm, as shown respectively in Figs. 2(b) and 2(c), the heavy- and light-hole emission energies shift to higher energies, which indicate a reduction of in-plane tensile strain for the narrower nanowires. However, if the trench width was further reduced, the CL spectrum of the 300-nm-wide nanowire reveals a larger red-shift than 500nm-wide nanowire. Two Gaussian-shaped functions were used to fit the spectrum of Fig. 2(d) and obtain peak positions at 1.511 and 1.499 eV for  $E_{hh}$  and  $E_{lh}$ , respectively. The origin of the abrupt increase of the in-plane tensile strain in the 300-nm-wide trench is induced by the large vertical compressive strain exerted by the SiO<sub>2</sub> sidewalls because the center of the GaAs nanowire is about 150 nm from the sidewalls and 250 nm from the bottom. In addition, as the trench width is further reduced from 200 [Fig. 2(e)] to 80 nm [Fig. 2(g)], an increase of  $E_{hh}$  and  $E_{lh}$ was observed again, which implies the reduction of the inplane tensile strain.

In order to calculate the in-plane tensile strain, the strain induced heavy-light hole splitting is analyzed as follows. The strain includes an isotropic component,  $\varepsilon_{\rm i}=2\varepsilon_{\parallel}+\varepsilon_{\perp}$ , and an anisotropic one,  $\varepsilon_{\rm a}=\varepsilon_{\parallel}-\varepsilon_{\perp}.^{27,28}$  The parameter  $\varepsilon_{\parallel}=[(a_{\rm Si}-a_{\rm GaAs})/a_{\rm Si}]$  represents the in-plane strain between GaAs and Si, where  $a_{\rm Si}$  and  $a_{\rm GaAs}$  are the lattice constant of Si and GaAs. The other parameter  $\varepsilon_{\perp}$  represents the vertical strain along the growth direction of [001] axis. The value is positive (negative) for tensile (compressive) strain. The isotropic tensile (compressive) component closes (open) the band gap, as shown in Fig. 2(h). Whereas, the anisotropic component lifts the degeneracy of the heavy and light hole band. The transition energy between the bottom of conduction band and the heavy-hole and light-hole band edge of the strained GaAs is expressed as<sup>28</sup>)

$$E_{\rm hh} - E_0 = a_{\rm H} \varepsilon_{\rm i} - a_{\rm S} \varepsilon_{\rm a}, \tag{1}$$

$$E_{\rm lh} - E_0 = a_{\rm H} \varepsilon_{\rm i} + a_{\rm S} \varepsilon_{\rm a}, \qquad (2)$$

where  $E_0$  represents the strain-free transition, while  $a_{\rm H}$  and  $a_{\rm S}$  represents the hydrostatic and shear component of the

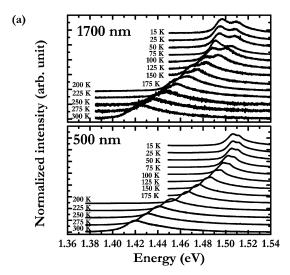

**Fig. 3.** Temperature dependent CL spectra for GaAs grown from 1700-and 500-nm-wide trenches (a), and the calculated temperature dependent strain (b). The solid lines were calculated by eqs. (1) and (2).

deformation potential. The values of  $a_{\rm H}$  and  $a_{\rm S}$  for GaAs are -8.93 and  $-1.76\,{\rm eV}$ , respectively.<sup>28)</sup>

According to eqs. (1) and (2) and the definition of  $\varepsilon_i$  and  $\varepsilon_a$ , the in-plane strains  $\varepsilon_{\parallel}$  at 15 K as a function of trench width were calculated and plotted in Fig. 2(i). For the 1700nm-wide GaAs nanowire, the in-plane tensile strain of  $\varepsilon_{\parallel} = 0.162\%$  can be calculated from the respective average peak energy and splitting of 1.502 eV and 11 meV. As the trench width decreases from 1700 to 500 nm, the in-plane tensile strain decreases to 0.080%. On the other hand, the vertical component  $\varepsilon_{\perp}$  increases from -0.150 to -0.075%, as the trench width decreases from 1700 to 500 nm. In this study, the thickness dependent strain evolution was not discussed since the electron beam was focused at the surface of nanowires. The tensile strain in the growth plane results a compressive strain along [001] axis. The ratio between  $\varepsilon_{\perp}$ and  $\varepsilon_{\parallel}$  is about  $-0.92 \pm 0.2$ , which is close to the relation of biaxial strain expressed by  $\varepsilon_{\perp}/\varepsilon_{\parallel} = -(2C_{12}/C_{11})$ , where  $C_{11}$  and  $C_{12}$  is the elastic compliance of GaAs with the value of  $1.190 \times 10^{12}$  and  $0.538 \times 10^{12}$  dyn·cm<sup>-2</sup>, respectively.<sup>28)</sup>

In order to understand the variation of the in-plane tensile strain with the trench width, the temperature dependent CL measurements were shown in Fig. 3(a) for the 1700- and 500-nm-wide GaAs nanowires. As temperature increases the heavy- and light-hole emission peaks exhibit a red shift, while the splitting decreases until they were unable to be distinguished at 225 K. By using eqs. (1) and (2), the inplane strains as a function of temperature were calculated, as shown in Fig. 3(b). A linear decrease with the increasing temperature is observed. For GaAs grown from a 1700-nm-

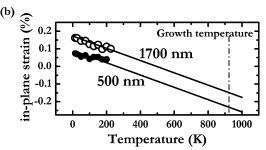

**Fig. 4.** The estimated strain at growth temperature (a) and the emission efficiency at 300 K for GaAs nanowires with different widths (b).

wide trench, it exhibits an in-plane tensile strain of 0.126% at  $100\,\mathrm{K}$  and 0.100% at  $225\,\mathrm{K}$ . By using the linear expansion coefficient  $\alpha = 5.73 \times 10^{-6}$  and  $2.26 \times 10^{-6}\,\mathrm{K}^{-1}$  for GaAs and Si,<sup>29)</sup> respectively, the calculated temperature dependent in-plane strains are shown by the solid lines of Fig. 3(b). The extrapolated strain at the growth temperature of  $650\,^{\circ}\mathrm{C}$  is -0.150%, indicating a compressive strain in GaAs. The inplane compressive strain at the growth temperature is attributed to the larger lattice of GaAs than that of Si, which results in a compression in the growth plane and a tension along the growth direction.

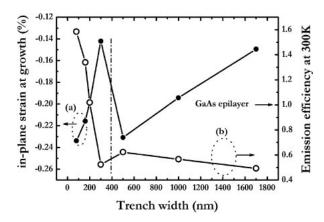

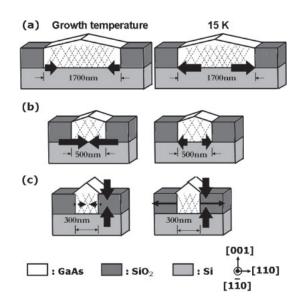

The dependence strain on the trench width and the influence of surrounding SiO2 sidewalls are discussed as follows. First, the in-plane compressive strain of the 1700nm-wide trench at  $650\,^{\circ}\text{C}$  is much smaller than the ideal lattice-mismatch of -4.3%. It implies that large part of the strain is released by the formation of structural defects such as threading dislocations. <sup>12)</sup> For the 500-nm-wide nanowire, a larger in-plane strain of -0.231% at the growth temperature was observed, as shown in Fig. 4(a), which implies less density of threading dislocation generated in the narrower nanowire. The reduction of the dislocations was confirmed by the increased room temperature emission efficiency, as shown in Fig. 4(b). The emission efficiency is defined as the ratio of the CL intensity to the volume of emission as we did in ref. 22. According to the experimental results, Figs. 5(a) and 5(b) schematically show the strains at the growth temperature and 15 K for GaAs nanowires embedded in the 1700- and 500-nm-wide trenches. The smaller strain relaxation of the 500 nm-wide nanowire implies a lower density of the threading dislocation.

As the trench width decreases from 500 to 300 nm, the in-plane compressive strain at the growth temperature decreases from -0.231 to -0.142%. The compensation of in-plane compression is attributed to an additional in-plane expansion, which is induced by a compression at the sidewall along [001] axis as shown in Fig. 5(c). Because the lattice constant of SiO<sub>2</sub> along [001] axis is much smaller than that of GaAs, <sup>30)</sup> the overgrown GaAs is under a vertical contraction at 650 °C. When the specimen cools down to 15 K, the small thermal coefficient of SiO<sub>2</sub>,  $5.00 \times 10^{-7}$  K<sup>-1</sup>, <sup>31)</sup> causes an extra compressive strain along the vertical direction, and results in a larger in-plane tension as shown in

**Fig. 5.** The schematic plots of strain at growth temperature and 15 K for GaAs nanowires with widths of 1700 (a), 500 (b), and 300 nm (c).

Fig. 2(i). As the trench width was further decreased from 300 to 200, 160 and 80 nm, a slightly increase of the average peak position and a reduction of splitting were observed. In comparison to the 300-nm-wide nanowire, the decrease of the trench width leads to an increasing in-plane compressive strain during growth. It is due to the smaller strain relaxation, improved crystal quality of less defect density, which results from the success of selective growth. This is corroborated by the significantly enhanced CL emission efficiency as shown in Fig. 4(b) and transmission electron microscopy images as reported previously.<sup>22)</sup> The highest value of emission efficiency occurs at the 80-nm-wide trench. It implies that the lowest density of defects. In brief, the highly spatial-resolved CL measurement provides an effective technique to derive the strain of a single nanowire and avoids the expansive and destructive TEM measurement. It helps for the development of GaAs monolithic devices with designed strain in the future.

### 4. Conclusions

The strain in GaAs nanowires, which were selectively grown from trenches on the Si(001) wafer with SiO<sub>2</sub> masks, is investigated in this study. The CL analyses estimate the strains at the growth temperature and investigate the dependence on the trench width. The in-plane compressive strain increases as the trench width decreases from 1700 to 500 nm owing to the lower density of defect. When the trench width (300 nm) is comparable to the depth (250 nm), the vertical contraction induced by SiO<sub>2</sub> sidewalls becomes dominant. This approach provides the feasibility of growing GaAs nanowires on patterned Si wafer with the designed strain.

#### **Acknowledgments**

This work was supported by the National Science Council under grant No. NSC 100-2119-M-009-003 and No. NSC 100-2731-M-009-001-NPI, Ministry of Education under grant number MOE-ATU 99W957 and Taiwan Semiconductor Manufacturing Co., Ltd.

- H. K. Choi, J. P. Mattia, G. W. Turner, and B. Y. Tsaur: IEEE Electron Device Lett. 9 (1988) 512.

- K. Eisenbeiser, R. Emrick, R. Droopad, Z. Yu, J. Finder, S. Rockwell, J. Holmes, C. Overgaard, and W. Ooms: IEEE Electron Device Lett. 23 (2002) 300.

- Z. Zhao, K. Yadavalli, Z. Hao, and K. L. Wang: Nanotechnology 20 (2009) 035304.

- 4) K. Tomioka, T. Tanaka, S. Hara, K. Hiruma, and T. Fukui: IEEE J. Sel. Top. Quantum Electron. 17 (2011) 1112.

- L. C. Chuang, F. G. Sedgwick, R. Chen, W. S. Ko, M. Moewe, K. W. Ng, T. D. Tran, and C. Chang-Hasnain: Nano Lett. 11 (2011) 385.

- 6) K. Morizane: J. Cryst. Growth 38 (1977) 249.

- 7) H. L. Tsai and Y. C. Kao: J. Appl. Phys. 67 (1990) 2862.

- A. Georgakilas, P. Panayotatos, J. Stoemenos, J. L. Mourrain, and A. Christou: J. Appl. Phys. 71 (1992) 2679.

- T. Egawa, Y. Hasegawa, T. Jimbo, and M. Umeno: Jpn. J. Appl. Phys. 31 (1992) 791.

- N. Tsukamoto, Y. Yazawa, J. Asano, and T. Minemura: Appl. Phys. Lett. 61 (1992) 810.

- 11) Y. K. Yang, M. Groenert, C. W. Leitz, A. J. Pitera, M. T. Currie, and E. A. Fitzgerald: J. Appl. Phys. 93 (2003) 3859.

- 12) N. Otsuka, C. Choi, Y. Nakamura, S. Nagakura, R. Fischer, C. K. Peng, and H. Morkoç: Appl. Phys. Lett. 49 (1986) 277.

- T. D. Harris, M. G. Lamont, R. Sauer, R. M. Lum, and J. K. Klingert: J. Appl. Phys. 64 (1988) 5110.

- Appl. Phys. 64 (1988) 5110.

Y. Hunag, P. Y. Yu, H. Lee, and S. Wang: Appl. Phys. Lett. 52 (1988) 579.

- Y. Chen, A. Freundlich, H. Kamada, and G. Neu: Appl. Phys. Lett. 54 (1989) 45.

- 16) R. M. Sieg, J. A. Carlin, J. J. Boeckl, S. A. Ringel, M. T. Currie, S. M. Ting, T. A. Langdo, G. Taraschi, E. A. Fitzgerald, and B. M. Keyes: Appl.

- Phys. Lett. **73** (1998) 3111.

- A. Vanamu, A. K. Datye, R. Dawson, and S. H. Zaidi: Appl. Phys. Lett. 88 (2006) 251909.

- 18) H. J. Oh, K. J. Choi, W. Y. Loh, T. Htoo, S. J. Chua, and B. J. Cho: J. Appl. Phys. 102 (2007) 054306.

- 19) S. Sakai: Appl. Phys. Lett. 51 (1987) 1069.

- 20) N. Wada, S. Sakai, and M. Fukui: Jpn. J. Appl. Phys. 33 (1994) 976.

- J. Z. Li, J. Bai, J. S. Park, B. Adekore, K. Fox, M. Carroll, A. Lochtefeld, and Z. Shellenbarger: Appl. Phys. Lett. 91 (2007) 021114.

- 22) L. Lee, W. C. Fan, J. T. Ku, W. H. Chang, W. K. Chen, W. C. Chou, C. H. Ko, C. H. Wu, Y. R. Lin, C. H. Wann, C. W. Hsu, Y. F. Chen, and Y. K. Su: Nanotechnology 21 (2010) 465701.

- 23) C. W. Hsu, Y. F. Chen, and Y. K. Su: Appl. Phys. Lett. 99 (2011) 133115.

- E. Grilli, M. Guzzi, R. Zamboni, and L. Pavesi: Phys. Rev. B 45 (1992) 1638.

- W. C. Chou, A. Twardowski, K. Chern-Yu, F. R. Chen, C. R. Hua, B. T. Jonker, W. Y. Yu, S. T. Lee, A. Petrou, and J. Warnock: J. Appl. Phys. 75 (1994) 2936.

- C. S. Yang, Y. P. Hsieh, M. C. Kuo, P. Y. Tseng, Z. W. Yeh, K. C. Chiu,

J. L. Shen, A. H. M. Chu, W. C. Chou, and W. H. Lin: Mater. Chem. Phys.

78 (2003) 602.

- G. Landa, R. Carles, C. Fontaine, E. Bedel, and A. Muñoz-Yagüe: J. Appl. Phys. 66 (1989) 196.

- 28) S. C. Jain, M. Willander, and H. Maes: Semicond. Sci. Technol. 11 (1996)

- S. M. Sze: *Physics of Semiconductor Devices* (Wiley, New York, 1981)

2nd ed.

- 30) A. J. C. Wilson and H. Lipson: Proc. Phys. Soc. 53 (1941) 245.

- 31) I. Blech and U. Cohen: J. Appl. Phys. 53 (1982) 4202.