## Bipolar resistive switching characteristics of Al-doped zinc tin oxide for nonvolatile memory applications

Yang-Shun Fan, Po-Tsun Liu, Li-Feng Teng, and Ching-Hui Hsu

Citation: Applied Physics Letters 101, 052901 (2012); doi: 10.1063/1.4742737

View online: http://dx.doi.org/10.1063/1.4742737

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/101/5?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Asymmetric resistive switching characteristics of In2O3:SiO2 cosputtered thin film memories

J. Vac. Sci. Technol. B 32, 020603 (2014); 10.1116/1.4863915

Well controlled multiple resistive switching states in the Al local doped HfO2 resistive random access memory device

J. Appl. Phys. 113, 164507 (2013); 10.1063/1.4803076

Bipolar resistive switching in an amorphous zinc tin oxide memristive device

J. Vac. Sci. Technol. B 31, 01A104 (2013); 10.1116/1.4767124

Unipolar resistive switching behavior of Pt/Li x Zn1 x O/Pt resistive random access memory devices controlled by various defect types

Appl. Phys. Lett. 101, 203501 (2012); 10.1063/1.4766725

Bipolar resistive switching with self-rectifying effects in Al/ZnO/Si structure

J. Appl. Phys. 111, 013702 (2012); 10.1063/1.3672811

## Bipolar resistive switching characteristics of Al-doped zinc tin oxide for nonvolatile memory applications

Yang-Shun Fan, Po-Tsun Liu, <sup>a)</sup> Li-Feng Teng, and Ching-Hui Hsu Department of Photonics and Display Institute, National Chiao Tung University, 1001 Ta-Hsueh Rd., HsinChu 300, Taiwan

(Received 17 March 2012; accepted 23 July 2012; published online 31 July 2012)

Resistive random access memory using Al-doped zinc tin oxide (AZTO) as resistive switching layer was prepared by radio-frequency magnetron sputtering at room temperature. The Ti/AZTO/Pt device exhibits reversible and robust bi-stable resistance switching behavior over hundreds of switching cycles within 2V sweep voltage. The Ti/AZTO/Pt device showed stable retention characteristics for over 10<sup>4</sup> s under read disturb stress condition. Besides, the electrical conduction mechanism was dominated by ohmic conduction in low resistance state, while the current transport behavior followed a trap-controlled space-charge-limited conduction process in high resistance state. © 2012 American Institute of Physics. [http://dx.doi.org/10.1063/1.4742737]

Resistive random access memory (RRAM) has attracted substantial attention for use in next-generation nonvolatile memory (NVM) applications owing to its superior performance, simple structure, low power consumption, favorable scalability, and fast switching.<sup>1–4</sup> Transparent amorphous metal oxide semiconductors (TAOS), including amorphous InGaZnO (a-IGZO) film that is used as the resistive switching layer of RRAM devices, exhibit remarkable resistance switching characteristics.<sup>5,6</sup> Moreover, the use of a-IGZO film for nonvolatile memory device will be easily integrated with the a-IGZO thin film transistor (a-IGZO TFT) backplane in the emerging transparent flat panel displays (FPDs) for system-on-panel (SoP) applications.<sup>7,8</sup> However, the TAOS target materials that comprise indium (In) and gallium (Ga) are in great demand for use in the manufacture of optoelectronic devices, such as thin film transistors, lightemitting diodes, lasers, solar cells, and radio-frequency (RF) circuits. 9-11 In this work, In- and Ga-free TAOS materials are utilized to demonstrated RRAM characteristics, with the ultimate benefit of decelerating the rapid consumption of the elements In and Ga in the Earth. Aluminum-doped zinc (Zn) tin (Sn) oxide (AZTO) was used as a resistive switching layer, which is also easily integrated with AZTO TFT array/ periphery circuits in FPDs. 12 Furthermore, the RRAM device in this work is as reliable as previously described IGZObased RRAM technologies, in terms of continuous switching endurance and data retention under the read disturb operation.<sup>5–7</sup>

Resistive memory devices with titanium (Ti)/AZTO/platinum (Pt) structures were fabricated at room temperature, as presented in the inset in Fig. 1(a). First, titanium oxide (TiO<sub>2</sub>) was deposited as a buffer layer by electron-gun (e-gun) evaporation on a silicon substrate to ensure strong adhesion. Then, a 50 nm-thick Pt layer, acting as the bottom electrode, was also formed by e-gun evaporation. A 50 nm-thick AZTO resistive switching layer was subsequently de-

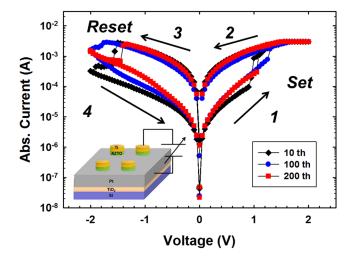

Figure 1 plots a typical bipolar resistance current-voltage (I-V) characteristic of the AZTO RRAM device under DC sweeping at room temperature. Applying positive DC sweeping voltages gradually activates the as-deposited memory cell, initially forming a conductive path; this process is called the "forming process." The current suddenly increases at the forming voltage, and the cell was shifted from the high resistance state (HRS) to the low resistance state (LRS). After the bias was swept over the re-set voltage

FIG. 1. Typical bipolar resistance switching I-V curves of the AZTO RRAM with Ti/AZTO/Pt device structure, measured at room temperature. The inset showing the resistive memory devices with titanium (Ti)/AZTO/platinum (Pt) structure.

posited by RF magnetron sputtering using an AZTO ceramic plate target that consisted of ZnO, SnO<sub>2</sub>, and Al<sub>2</sub>O<sub>3</sub> (67:30:3 mol. %). The Ar gas flow rate was set to 10 sccm, and the sputtering pressure and power were 3 m Torr and 80 W, respectively. Finally, a 50 nm-thick Ti layer was deposited, without breaking the vacuum, as the top electrode, to minimize the dispersions of resistive switching parameters. The size of a memory cell was determined using a shadow mask with a diameter of 0.6 mm. Electrical measurements were made using a Keithley 4200 semiconductor characterization analyzer in DC sweeping mode.

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: ptliu@mail.nctu.edu.tw. Tel.: 886-3-5712121, ext. 52994. FAX: 886-3-5735601.

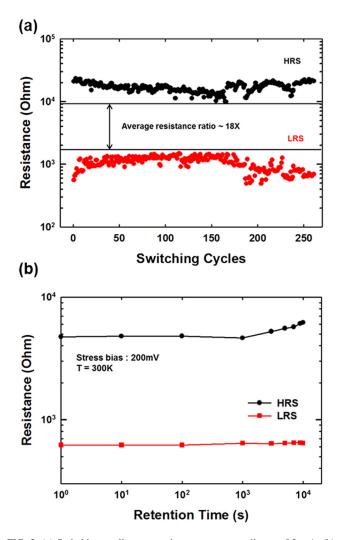

FIG. 2. (a) Switching cycling test under a current compliance of 3 mA. (b) Retention characteristics for the HRS and LRS at room temperature, as measured at  $0.2\,\mathrm{V}$  under a durable stress of  $200\,\mathrm{mV}$ .

of around  $-1.6 \,\mathrm{V}$ , the current dropped abruptly, where the memory cell switched from LRS to HRS. This process is called the "reset process." The cell returns to LRS when a positive bias that exceeds the set voltage ( $\sim 1.1 \text{ V}$ ) is applied, and a compliance current (CC) of 3 mA is applied to prevent permanent breakdown. The endurance and data retention of the proposed RRAM device were measured and analyzed. As presented in Figs. 2(a) and 2(b), the successive set/reset process in DC sweep mode and the resistance ratio of HRS to LRS (R<sub>HRS</sub>/R<sub>LRS</sub>) is 18 at a reading voltage of 0.2 V, and the resistance remains robust after 256 cycles of I-V sweeping. The data retention characteristics were investigated by performing a read disturb process by applying a sustained stress voltage of 200 mV in both HRS and LRS. Experimental results reveal no significant change in resistance in either case after  $10^4$  s.

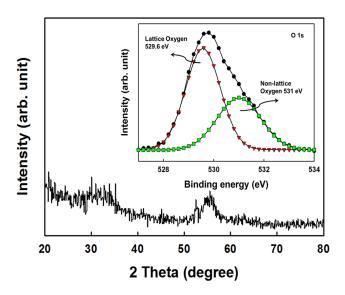

The crystalline quality of the as-deposited AZTO film was characterized by x-ray diffraction (XRD), as displayed in Fig. 3. The XRD pattern of the AZTO film includes not sharp peak, indicating that the AZTO film is amorphous. The inset in Fig. 3 shows O 1s peaks in the x-ray photoelectron spectrum (XPS), providing information on the chemical bonding states of AZTO film. The experimental data were fitted by summing two peaks. The peak at the lower energy, 529.6 eV,

FIG. 3. XRD patterns of the AZTO thin film. The inset represents the XPS spectra of the O 1s core levels in the AZTO film.

corresponds to the metal ion array, while the peak at the higher energy,  $531\,\mathrm{eV}$ , is associated with non-lattice oxygen ions ( $\mathrm{O^{2-}}$ ) in the deficient regions within the matrix of AZTO. The non-lattice oxygen ions are involved in charge transportation in the metal oxide-based RRAM device. <sup>14</sup>

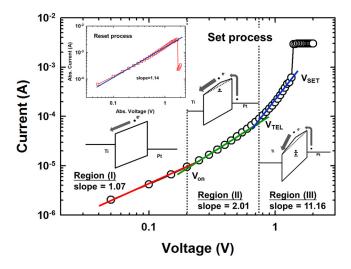

Not only is the material characterized, as described above, but also the mechanism of the flow of current in the AZTO RRAM device is explored by analyzing the I-V characteristics, which are plotted on Fig. 4 on a double-logarithmic scale. The inset represents the LRS in the reset process, in which the current depends linearly on the voltage with a slope of 1.14, indicating ohmic-like conduction. This result suggests that the reset process is caused by rupturing the conducting filaments that contain oxygen vacancies. The HRS in the set process, however, is slightly more complicated than the LRS. Precise curve fitting method was confirms that the setting process follows a trap-controlled space-charge-limited conduction (SCLC) process. The charge transport mechanisms can be described using three

FIG. 4. The conducting mechanism with double logarithmic plot, showing the space-charge-limited-current conduction dominant in HRS by curve fitting. The inset shows the conduction mechanism of LRS is an ohmic-like behavior.

regimes, which are ohmic-like behavior, the square-law regime, and the regime with a steep increase in current. In the low-voltage operation regime, electrons were thermally generated inside the AZTO film, and conduction was by hopping, resulting in ohmic-like transportation. When the voltage exceeded 0.2 V, electrons were injected from the bottom electrode and the current-voltage slope changed from 1.07 to 2.01. In this stage, shallow traps were gradually filled, and this process dominated the trap-controlled SCLC up to a voltage of  $\sim$ 0.8 V, which is the trap-filled-limited voltage (V<sub>TFL</sub>). As the applied voltage is further increased [region (III) in Fig. 4], the injected electron current begins to be dominated by the deep-level trap-controlled SCLC, leading to a huge increase in current. Eventually, the RRAM device switches to the LRS at  $V_{\rm set}$ .

In summary, resistive nonvolatile memory cells with a Ti/AZTO/Pt structure were fabricated at room temperature. The developed AZTO RRAM device exhibited bipolar switching behavior, remaining in a stable resistance state with exhibiting switching responses over 256 cycles, and a retention time of 10<sup>4</sup> s under a read disturb operation. The replacement of In and Ga-containing TAOS materials with AZTO film can effectively slow down the consumption of In and Ga elements, markedly reducing the cost of production of TAOS-based electrical devices. Moreover, the use of AZTO RRAMs in FPDs technology is potentially beneficial for the realization of SoP applications.

The authors would like to thank the National Chiao Tung University of Taiwan and the National Science Council

of the Republic of China under Contract No. NSC 100-2628-E-009-016-MY3.

- <sup>1</sup>A. Sawa, Mater. Today **11**, 28 (2008).

- <sup>2</sup>Y. Wu, B. Lee, and H. P. Wong, IEEE Electron Device Lett. **31**, 1449 (2010).

- <sup>3</sup>S. Kim, H. Moon, D. Gupta, S. Yoo, and Y. K. Choi, IEEE Trans. Electron Devices **56**, 696 (2009).

- <sup>4</sup>H. Y. Lee, P. S. Chen, T. Y. Wu, Y. S. Chen, C. C. Wang, P. J. Tzeng, C. H. Lin, F. Chen, C. H. Lien, and M. J. Tsai, IEDM Tech. Dig. **2008**, 297

- <sup>5</sup>Z. Q. Wang, H. Y. Xu, X. H. Li, X. T. Zhang, Y. X. Liu, and Y. C. Liu, IEEE Electron Device Lett. **32**, 1442 (2011).

- <sup>6</sup>C. H. Kim, Y. H. Jang, H. J. Hwang, C. H. Song, Y. S. Yang *et al.*, Appl. Phys. Lett. **97**, 062109 (2010).

- <sup>7</sup>P. T. Liu, L. F. Teng, Y. S. Fan, C. S. Fuh, Y. T. Chou, W. Y. Wang, and H. P. D. Shieh, in *Proceedings of the 16th OptoeElectronics and Communications Conference, Kaohsiung, Taiwan* (2011), pp. 91–92.

- <sup>8</sup>J. C. Lee and J. Y. Jeong, *International Conference on Integrated Circuit Design and Technology ICICDT '06*, Padova, Italy (2006), pp. 1–4.

- <sup>9</sup>S. K. Moore, IEEE Spectrum **45**(3), 60 (2008).

- <sup>10</sup>P. T. Liu, Y. T. Chou, and L. F. Teng, Appl. Phys. Lett. **95**, 233504 (2009).

- <sup>11</sup>P. T. Liu, Y. T. Chou, L. F. Teng, F. H. Li, and H. P. Shieh, Appl. Phys. Lett. 98, 052102 (2011).

- <sup>12</sup>D. H. Cho, S. Yang, C. Byun, J. Shin, M. K. Ryu, S. H. Ko Park, C. S. Hwang, S. M. Chung, W. S. Cheong, S. M. Yoon, and H. Y. Chu, Appl. Phys. Lett. **93**, 142111 (2008).

- <sup>13</sup>S. Y. Wang, D. Y. Lee, T. Y. Tseng, and C. Y. Lin, Appl. Phys. Lett. 95, 112904 (2009).

- <sup>14</sup>M. K. Yang, J. W. Park, T. K. Ko, and J. K. Lee, Appl. Phys. Lett. 95, 042105 (2009).

- <sup>15</sup>S. G. Park, M. K. Blanka, and Y. Nishi, IEEE Electron Device Lett. 32, 197 (2011).

- <sup>16</sup>K. M. Kim, B. J. Choi, Y. C. Shin, S. Choi, and C. S. Hwang, Appl. Phys. Lett. **91**, 012907 (2007).