# The Effects of NH<sub>3</sub> Plasma Passivation on Polysilicon Thin-Film Transistors

Fang-Shing Wang, Meng-Jin Tsai, and Huang-Chung Cheng, Member, IEEE

Abstract— The NH<sub>3</sub> plasma passivation has been performed for the first time on the polycrystalline silicon (poly-Si) thin-film transistors (TFT's). It is found that the TFT's after the NH<sub>3</sub> plasma passivation achieve better device performances, including the off-current below 0.1 pA/ $\mu$ m and the on/off current ratio higher than 10<sup>8</sup>, and also better hot-carrier reliability as well as thermal stability than the H<sub>2</sub>-plasma ones. These improvements were attributed to not only the hydrogen passivation of the grain-boundary dangling bonds, but also the nitrogen pile-up at SiO<sub>2</sub>/poly-Si interface and the strong Si-N bond formation to terminate the dangling bonds at the grain boundaries of the polysilicon films.

## I. Introduction

OLYCRYSTALLINE silicon (Poly-Si) thin-film transistors (TFT's) are of interest for a number of applications, such as ultra-large-scale-integration (ULSI) memories and large-area electronic devices (displays, sensors, etc.) [1], [2]. In these devices, defects either in the bulk or at grain boundaries play a critical role [3]. To obtain high-performance poly-Si TFT's, it is necessary to reduce the trap-states of the polysilicon films. It is now well known that hydrogenation leads to tie up the grain boundary dangling bonds with hydrogen, thereby significantly improve the characteristics of the poly-Si TFT's [4]. However, it had been observed that the characteristics of the poly-Si TFT's after the hydrogen passivation suffer a low hot-carrier endurance and a low thermal stability [5], [6]. In this letter, a simpler technique, NH<sub>3</sub>-plasma passivation, was employed to enhance both the electrical reliability and the thermal stability of the poly-Si TFT's.

## II. EXPERIMENTAL PROCEDURES

The poly-Si TFT's were fabricated on thermally oxidized silicon wafers. A 110 nm thick amorphous silicon ( $\alpha$ -Si) was initially deposited at 550°C by low-pressure chemical vapor deposition (LPCVD) using pure SiH<sub>4</sub>, and then furnace annealed at 600°C for 24 h in  $N_2$  ambient to recrystallize the silicon films. After defining the active islands, a 70 nm thick silicon-dioxide was thermally grown by dry oxidation. Another 300 nm polysilicon film was deposited at 620°C in an

Manuscript received April 27, 1995; revised August 1, 1995. This work was supported in part by the Republic of China National Science Council under Contract NSC-79-0425-E009-013.

F.-S. Wang and H.-C. Cheng are with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C.

M.-J. Tsai is with the United Microelectronics Corporation, Hsinchu 300, Taiwan, R.O.C.

IEEE Log Number 9414969.

LPCVD system and patterned to be the gates of the devices. A self-aligned POCl<sub>3</sub> doping was performed at 900 °C for 20 min to form the source, drain, and gate electrodes. Then, the samples were subjected to the NH<sub>3</sub> or H<sub>2</sub> plasma treatment in a parallel-plate plasma reactor at 300°C with a power density of 0.7 W/cm<sup>2</sup>. The plasma conditions for NH<sub>3</sub> and H<sub>2</sub> had been optimized to obtain the optimum device performance, respectively. After a plasma-enhanced CVD (PECVD) SiO<sub>2</sub> of a thickness about 500 nm was deposited, contact holes were opened and the Al films was deposited and then defined. The I-V curves of TFT's were measured by an HP 4145 semiconductor parameter analyzer at room temperature. The concentration of the nitrogen atom was measured by detecting the Si-N signals using a secondary ion mass spectroscopy (SIMS) with Cs<sup>+</sup> as the primary ion.

# III. RESULTS AND DISCUSSION

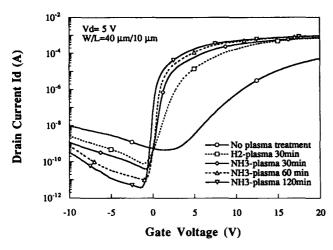

The  $I_d - V_q$  characteristics of the n-channel poly-Si TFT's with various NH<sub>3</sub>-plasma exposure times from 0 to 120 min are shown in Fig. 1. The transfer curves of the devices with a 30 min H<sub>2</sub>-plasma and without a plasma treatment are also shown for comparison. Table I lists the values of the minimum leakage current  $I_{\min}$ , the subthreshold swing SS, the on/off current ratio, the threshold voltage  $V_{th}$ , the field effect mobility  $\mu_{FE}$ , and the trap-state density  $N_t$ . The SS and  $\mu_{FE}$  were measured at  $V_d = 0.1$  V for  $W/L = 40 \ \mu \text{m}/10 \ \mu \text{m}$  devices. The  $V_{th}$  is defined at a fixed drain current  $I_d = I_{dn} \times W/L$ , for this work, where  $I_{\rm dn}$  is a normalized drain current, 10 nA [7]. The  $I_{\min}$  is the minimum value of the drain current measured at  $V_d = 5$  V. The  $N_t$  is obtained by extracting a straight line on the plot of  $\ln \left[ I_d / (V_q - V_{\rm FB}) \right]$  versus  $1/(V_q - V_{FB})^2$  at low source-drain voltage and high gate bias [8], [9]. It is obvious that the NH<sub>3</sub>-plasma and H<sub>2</sub>-plasma treatment both can effectively promote the performance of the TFT's. In addition, it seems that the devices treated by NH<sub>3</sub>plasma for 30 min have even better performance than that treated by H<sub>2</sub>-plasma. Moreover, as the exposure time to NH<sub>3</sub>plasma increases, the TFT's performance can be enhanced increasingly, such as  $I_{\min}$  and SS decreasing to 3.54 pA, and 200 mV/decade and  $\mu_{FE}$  and on/off current ratio increasing to 79.93 cm<sup>2</sup>/Vs and  $2.23 \times 10^8$ , respectively, for 120 min NH<sub>3</sub>plasma treated devices, unlike the earlier report that the TFT's exposed to H<sub>2</sub>-plasma exhibited saturation characteristics [10].

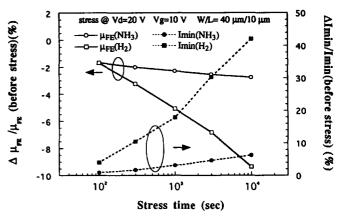

The hot-carrier reliability of the NH<sub>3</sub>-plasma-treated devices was also investigated. Fig. 2 shows the  $\mu_{FE}$  and  $I_{\min}$  variations for the devices with the NH<sub>3</sub> and H<sub>2</sub> plasma passivation, respectively, after they were stressed at  $V_d = 20$

Fig. 1 The transfer characteristics of polysilicon TFT's after applying NH<sub>3</sub> plasma treatments.

TABLE I THE VALUES OF  $I_{\min}$ , SS,  $\mu_{FE}$ ,  $V_{\rm th}$ , and  $N_t$  of the Polysilicon TFT's for Various Plasma Treatments

| Plasma<br>Gas   | Time<br>(min) | I <sub>min</sub><br>(pA) | SS<br>(V/dec.) | On/Off current<br>ratio (×10 <sup>6</sup> ) | V <sub>th</sub><br>(V) | μ <sub>FE</sub><br>(cm²/Vsec) | N <sub>t</sub><br>(×10 <sup>11</sup> cm <sup>-2</sup> ) |

|-----------------|---------------|--------------------------|----------------|---------------------------------------------|------------------------|-------------------------------|---------------------------------------------------------|

| -               | 0             | 463.6                    | 1.81           | 0.024                                       | 7.18                   | 11.35                         | 63.9                                                    |

| $H_2$           | 30            | 81.03                    | 0.61           | 4.11                                        | 1.46                   | 51.31                         | 14.8                                                    |

| $NH_3$          | 30            | 39.50                    | 0.34           | 14.2                                        | 0.72                   | 59.92                         | 13.9                                                    |

| NH <sub>3</sub> | 60            | 10.30                    | 0.28           | 71.0                                        | 0.46                   | 75.12                         | 8,67                                                    |

| NH <sub>3</sub> | 120           | 3.54                     | 0.20           | 223                                         | -0.02                  | 79.93                         | 5.66                                                    |

V,  $V_q = 10$  V for different stress durations. It is found that the  $\mu_{FE}$  decreases and  $I_{\min}$  increases with hot-carrier stress time, and the variations of the  $\mu_{FE}$  and  $I_{\min}$  for NH<sub>3</sub>plasma-treated devices are less than those for H<sub>2</sub>-plasmatreated samples. That is, the NH<sub>3</sub>-plasma passivated devices have better hot-carrier reliability than the H<sub>2</sub>-plasma ones. The performance degradation of both devices induced by hot carrier stress is thought to be due to the generation of poly-Si/SiO<sub>2</sub> acceptor-type interface states and the grain boundary states in the poly-Si channel layer [5], [11]. The hot-carrier endurance of NH<sub>3</sub>-plasma passivation is better than that of the H<sub>2</sub>-plasma passivation, suggesting that not only hydrogen atoms but also nitrogen atoms are diffusing into the poly-Si films. From the SIMS analysis, it is found that nitrogen atoms can even diffuse to the bottom of the channel region. It is possible that weak Si-H bonds in poly-Si channel and at poly-Si/SiO<sub>2</sub> interface had been replaced by strong Si-N bonds. It had been reported that with the nitrogen implantation in the poly-Si gate/SiO<sub>2</sub>/c-Si substrate MOS structure, a much smaller interface-state generation rate was obtained after highfield/current stress [12]. Momose et al. also showed that with the low concentration (<1 atom %) nitrogen incorporation in the NH<sub>3</sub> rapid thermal nitrided-oxide, both drivability and hot carrier reliability of MOSFET could be improved [13].

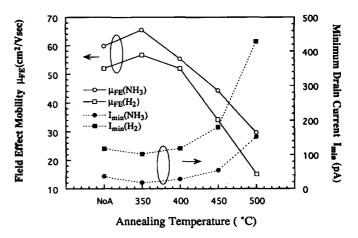

Fig. 3 shows the  $\mu_{FE}$  and  $I_{\min}$  after thermal annealing for different annealing temperatures range from 350°C to 500°C. For the 350°C annealed devices, there is a slightly increase in  $\mu_{FE}$  and a slightly decrease in  $I_{\min}$ . This is presumably because of the annihilation of plasma induced damages and/or hydrogen and nitrogen atoms indiffusion, leading to a further passivation effect. As the annealing

Fig. 2. The field effect mobility  $\mu_{FE}$  and minimum drain current  $I_{\min}$  for NH<sub>3</sub>- and H<sub>2</sub>-passivated devices as a function of stress time.

Fig. 3. The variation of field effect mobility  $\mu_{FE}$  and minimum drain current  $I_{\rm min}$  for NH<sub>3</sub>- and H<sub>2</sub>-passivated devices after thermal annealing at the temperature range from 300°C to 500 °C.

temperature continuously increases, the increase in  $I_{\min}$  and decrease in  $\mu_{FE}$  is attributed to the dehydrogenation effect since the hydrogen releases from the defect sites and causes the generation of trap states. But for the NH<sub>3</sub>-treated TFT's, lower degrees of  $\mu_{FE}$  and  $I_{\min}$  degradations are observed with respect to the H <sub>2</sub>-plasma ones. Even for 500°C annealing, the TFT's performance passivated with NH<sub>3</sub>-plasma still keeps the relatively good electrical properties. Therefore, it suggests that the strong Si-N bonds exist in NH<sub>3</sub>-passivated films and achieve superior thermal stability to weaker Si-H bonds.

## IV. CONCLUSIONS

The NH<sub>3</sub>-plasma passivation has been used to promote the electrical properties of poly-Si TFT's. It is found that the poly-Si TFT's after NH<sub>3</sub> plasma passivation exhibit significantly superior device characteristics, hot-carrier reliability, and thermal stability to those with the conventional H<sub>2</sub>-plasma passivation. Both the nitrogen pile-up at the SiO<sub>2</sub>/poly-Si interface and the strong Si-N bond formation to passivate the dangling bonds at the grain boundaries in the channel region are surmised to be the major causes.

## ACKNOWLEDGMENT

The authors thank the National Nano Device Laboratory and the Semiconductor Research Center at National Chiao Tung University for their technical support.

## REFERENCES

- W. G. Hawkins, "Polycrystalline-silicon devices technology for largearea electronics," *IEEE Trans. Electron Devices*, vol. ED-33, pp. 477-481, 1986.

- [2] P. Migliorato and D. B. Meakin, "Material properties and characteristics of polysilicon transistors for large area electronics," *Appl. Surf. Sci.*, vol. 30, p. 353, 1987.

- [3] K. Ono, T. Anoyama, N. Konishi, and K. Miyata, "Analysis of current-voltage characteristics of low-temperature-processed polysilicon thin film transistors," *IEEE Trans. Electron Devices*, vol. 39, pp. 792–802, 1992.

- [4] B. A. Khan and R. Pandya, "Activation-energy of source-drain current in hydrogenated and unhydrogenated polysilicon thin-films transistors," *IEEE Trans. Electron Devices*, vol. 37, pp. 1727–1734, 1990.

- IEEE Trans. Electron Devices, vol. 37, pp. 1727–1734, 1990.

[5] S. Banerjee, R. Sundaresan, H. Schichijo, and S. Malhi, "Hot-carrier degradation of n-channel polysilicon MOSFET's," IEEE Trans. Electron Devices, vol. 35, pp. 152–157, 1988.

- [6] M. Hack, A. G. Lewis, and I-W. Wu, "Physical models for degradation effects in polysilicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 40, pp. 890–897, 1993.

[7] A. G. Lewis, T. Y. Huang, R. H. Bruce, M. Koyanagi, A. Chiang

- [7] A. G. Lewis, T. Y. Huang, R. H. Bruce, M. Koyanagi, A. Chiang and I-W. Wu, "Polysilicon thin film transistors for analogue circuit applications," in *IEDM Tech. Dig.*, pp. 264–267, 1988.

- [8] J. Levinson, F. R. Shepherd, P. J. Scanlon, W. D. Westwood, G. Este, and M. Rider, "Conductivity behavior in polycrystalline semiconductor thin film transistors," J. Appl. Phys., vol. 53, pp. 1193–1202, 1982.

- [9] R. E. Proano, R. S. Misage, and D. G. Ast, "Development and electrical properties of undoped polycrystalline silicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 36, pp. 1915–1922, 1989.

- [10] H. N. Chern, C. L. Lee, and T. F. Lei, "The effects of H<sub>2</sub>-O<sub>2</sub>-plasma treatment on the characteristics of polysilicon thin film transistors," *IEEE Trans. Electron Devices*, vol. 40, pp. 2301-2306, 1993.

- [11] G. Fortunato, A. Pecora, G. Tallarida, L. Mariucci, C. Reita, and P. Migliorato, "Hot carrier effects in n-channel polycrystalline silicon thin-film transistors: a correlation between off-current and transconductance variations," *IEEE Trans. Electron Devices*, vol. 41, pp. 340–346, 1994.

- [12] S. Haddad and M. S. Liang, "Improvement of thin-gate oxide integrity using through-silicon-gate nitrogen ion implantation," *IEEE Electron Device Lett.*, vol. EDL-8, pp. 58-60, 1987.

- [13] H. S. Momose, T. Morimoto, Y. Ozawa, K. Yamabe, and H. Iwai, "Electrical characteristics of rapid thermal nitrided-oxide gate n- and p-MOSFET's with less than 1% atom nitrogen concentration," *IEEE Trans. Electron Devices*, vol. 41, pp. 546-552, 1994.