# Post-Polysilicon Gate-Process-Induced Degradation on Thin Gate Oxide

Chao Sung Lai, Tan Fu Lei, Chung Len Lee, Senior Member, IEEE, and Tien Sheng Chao

Abstract—The post-polysilicon gate-process-induced degradation on the underlying gate oxide is studied. The degradation includes an increase in the electron trapping rate and a decrease in the charge-to-breakdown,  $Q_{\rm bd}$ , of the gate oxide. It is found that  $N_2O$  nitrided gate oxide is more robust than  $O_2$  gate oxide in resisting the degradation. Also, to grow a thin polyoxide on the polysilicon-gate in  $N_2O$  rather than in  $O_2$  lessens the degradation on the underlying gate oxide. It is nitrogen, which diffuses through the polysilicon gate and piles up at both polysilicon/oxide and oxide/silicon-substrate interfaces, that improves the oxide quality for the  $N_2O$  process.

### I. INTRODUCTION

**F**OR EPROM and EEPROM memories, the device performance is primarily determined by the electrical properties of the gate oxide [1]. The tunneling oxide between the single-crystal substrate and the first polysilicon film requires a high  $Q_{\rm bd}$ . It was reported that for the polysilicon gate structure, a post polysilicon annealing results in degradation on  $Q_{\rm bd}$  [2]–[4]. The degradation is related to trap generation and stress built-up in the gate oxide during the high temperature annealing [2]–[4]. Recently, the use of  $N_2O$  as either an oxidant or as a post-oxidation annealing ambient to grow oxynitride has received much attention due to its good endurance to Fowler–Nordheim (F–N) stress [5]–[7]. This is due to the incorporation of nitrogen at the oxide/silicon-substrate interface [6]–[8]. However, the post-polysilicon gate-processinduced degradation on the thin gate oxide in the  $N_2O$  ambient has not been investigated.

In this letter, the degradation of the thin gate dielectrics induced by growing a thin oxide on the polysilicon gate in  $N_2O$  or  $O_2$  ambient is reported for the first time. It is found that  $N_2O$  nitrided gate oxide is more robust than  $O_2$  gate oxide in resisting the degradation. Also, growing a thin oxide on the polysilicon-gate in  $N_2O$  ambient lessens the degradation on the underlying gate oxide more than growing it in  $O_2$  ambient does.

### II. EXPERIMENTS

Poly-Si gate MOS capacitors were fabricated on  $\langle 100 \rangle$  p-Si, 15–20  $\Omega$  cm wafers. The O<sub>2</sub> gate oxide was grown in dry O<sub>2</sub>

Manuscript received March 25, 1995; revised July 13, 1995. This work was supported by the National Science Council of R.O.C. under Contract NSC-83-0404-E009-017.

C. S. Lai, T. F. Lei, and C. L. Lee are with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C.

T. S. Chao is with the National Nano Device Laboratory, Hsinchu 300, Taiwan, R.O.C.

IEEE Log Number 9414960.

at 900°C to a thickness of 85 Å. The  $N_2O$  nitrided oxide was first grown in dry  $O_2$  at 900°C followed by an anneal in  $N_2O$  for 20 min at the same temperature to control the final oxide thickness of 85 Å. The oxide thickness was determined by C–V measurement. For some samples, a thin polyoxide on the polysilicon gate was grown in  $O_2$  or  $N_2O$  ambient at 900°C for 30 min after 3000 Å polysilicon deposition, to simulate the inter-polyoxide in the EEPROM process [1], [2]. As shall be shown later, degradation was induced on the underlying gate dielectric by this thermal cycle.

The preparation sequences for these samples are summarized in Table I. Six groups of samples were prepared: three for  $O_2$  oxides and three for  $N_2O$  nitrided oxides. The  $O_2$  oxide samples are denoted as OP (without grown thin polyoxide), OPN (thin polyoxide grown in  $N_2O$ ), and OPO (thin polyoxide grown in  $O_2$ ). The  $N_2O$  nitrided oxide grown samples are denoted as ONP (without grown thin polyoxide), ONPN (thin polyoxide grown in  $O_2$ ), and ONPO (thin polyoxide grown in  $O_2$ ). The thin polyoxides were removed in a dilute HF solution and all samples were POCl<sub>3</sub>-doped at 950°C for 15 min and metallized and patterned to form MOS capacitors.

# III. RESULTS AND DISCUSSIONS

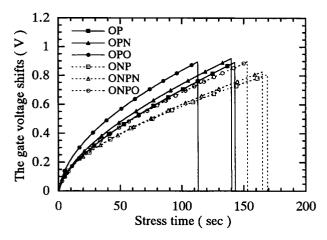

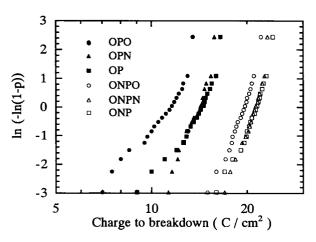

Fig. 1 shows the gate voltage shifts under constant current (100 mA/cm<sup>2</sup>) stressing. All N<sub>2</sub>O nitrided oxides showed smaller electron trapping rates than their corresponding O<sub>2</sub> oxides. This was due to nitrogen incorporation at the oxide/Sisubstrate interface of the N<sub>2</sub>O samples [6]-[8]. The OP and ONP samples, which had no thin polyoxides grown on the polysilicon gate, showed lower electron trapping rates than their corresponding samples: OPN, OPO, and ONPN, ONPO, respectively, which had thin polyoxides. Therefore, the process of growing a thin polyoxide on poly-Si gate causes degradation on the underlying gate oxide. The degradation is caused by stress built-up at polysilicon/oxide and oxide/silicon-substrate interfaces [4]. In this figure, it is also seen that N<sub>2</sub>O nitrided oxides (ONPN and ONPO) show less degradation than their corresponding O2 oxides (OPN and OPO). This indicates that N<sub>2</sub>O nitrided oxide is more robust than O<sub>2</sub> oxide. The degradation caused by growing a thin polyoxide in N2O (i.e., samples OPN and ONPN) is less than that caused by growing a thin polyoxide in O2 (i.e., samples OPO and ONPO). Therefore, growing the polysilicon-gate oxide in N<sub>2</sub>O lessens the degradation than growing it in O2. Fig. 2 shows Weibull plots of  $Q_{\rm bd}$  of all samples under 100 mA/cm<sup>2</sup> stressing for 40 capacitors. For O2 oxides, OPN showed little degradation on

TABLE I

THE PREPARATION SEQUENCES FOR SAMPLES IN THIS STUDY

| Samples | Gate dielectrics O <sub>2</sub> oxidation N <sub>2</sub> O annealing |   | Poly-Si gate | Thin poly-oxide grown on poly-Si gate     |

|---------|----------------------------------------------------------------------|---|--------------|-------------------------------------------|

| OP      | √                                                                    | - | ✓            | _                                         |

| OPN     | ✓                                                                    | - | ✓            | √(N <sub>2</sub> O)                       |

| OPO     | √                                                                    | - | ✓            | √(N <sub>2</sub> O)<br>√(O <sub>2</sub> ) |

| ONP     | ✓                                                                    | ✓ | ✓            | -                                         |

| ONPN    | √                                                                    | ✓ | ✓            | √(N <sub>2</sub> O)                       |

| ONPO    | √                                                                    | ✓ | ✓            | √(O <sub>2</sub> )                        |

Fig. 1. The gate voltage shifts under 100 mA/cm<sup>2</sup> stressing from gate injection for all samples. The gate area was  $5 \times 10^{-4}$  cm<sup>2</sup>.

Fig. 2. The Weibull plots for the  $Q_{\rm bd}$  of all samples. The stressing condition was 100 mA/cm<sup>2</sup> injected from the gate and the gate area was  $5 \times 10^{-4}$  cm<sup>2</sup>.

$Q_{\rm bd}$  but OPO had significant degradation. For N<sub>2</sub>O nitrided oxides, there was little degradation on ONPN and slight degradation on ONPO. This is consistent with the result of Fig. 1 since  $Q_{\rm bd}$  is related to electron trapping in the oxide [3].

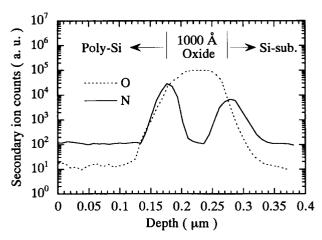

An OPN sample with a gate oxide of 100 nm thick was SIMS analyzed to obtain its oxygen and nitrogen depth profiles which were shown in Fig. 3. The use of a thick gate oxide is to ensure adequate depth resolution. For the SIMS sample, the  $N_2O$  annealing was done at  $900^{\circ}C$  for 60 min, which

Fig. 3. The nitrogen and oxygen SIMS profiles of an OPN sample with a gate oxide thickness of 1000 Å. The use of a thick gate oxide is to ensure adequate depth resolution. The post-polysilicon  $N_2O$  anneal condition was  $900^{\circ}C$  for 60 min. Nitrogen piled up at both the poly-Si/oxide and oxide/Si-substrate interfaces.

was 30 min longer than the 8.5 nm oxide (OPN sample). This nitrogen profile is quite similar to that of nitrogen ion implantation through-silicon-gate where the gate oxide integrity was significantly improved [9]. We conclude that during the  $N_2O$  annealing or oxidation, nitrogen diffuses through poly-Si gate and piles up at both the poly-Si/oxide and oxide/Si-substrate interfaces, improving the oxide quality.

# IV. SUMMARY

The post-polysilicon gate oxidation causes degradation on the underlying gate oxide. It causes both an increase in the electron trapping rate and a decrease in  $Q_{\rm bd}$ . For the underlying gate dielectric, it is found that  $N_2O$  nitrided gate oxide is more robust than  $O_2$  gate oxide in resisting this degradation. For the post-polysilicon gate oxidation, growing a thin oxide on poly-Si gate in  $N_2O$  rather than in  $O_2$  lessens the degradation on the underlying gate oxide. The nitrogen, which diffuses through the polysilicon gate and piles up at both oxide interfaces, results in superior reliability properties.

# ACKNOWLEDGMENT

The authors thank National Nano Device Laboratory for technological support.

## REFERENCES

- T. Ono, T. Mori, T. Ajioka, and T. Takayashiki, "Studies of thin poly-Si oxides for E and E2PROM," IEDM Tech. Dig., pp. 380-383, 1985.

- [2] M. Hendricks and C. Mavero, "Phosphorus doped poly siliocn for double poly structures," J. Electrochem. Soc., vol. 138, p. 1470, 1991.

- [3] S. Holland and C. Hu, "Correlation between breakdown and processinduced positive charge trapping in thin thermal SiO<sub>2</sub>," *J. Electrochem. Soc.*, vol. 133, p. 1705, 1986.

- [4] R. Mehta, A. B. Bhattacharyya, and D. N. Singh, "Post-growth process-induced degradation in thin gate oxides," *J. Appl. Phys.*, vol. 69, no. 12, p. 8247, 1991.

- [5] H. Hwang, W. Ting, D. L. Kwong, and J. Lee, "Electric and reliability characteristics of ultra thin oxynitride gate dielectric prepared by rapid thermal processing in N<sub>2</sub>O," *IEDM Tech. Dig.*, p. 421, 1990.

- [6] J. Ahn, W. Ting and D. L. Kwong, "Furnace nitridation of thermal SiO<sub>2</sub> in pure N<sub>2</sub>O ambient for ULSI MOS applications," *IEEE Electron Device Lett.*, vol. 13, p. 117, 1992.

[7] Z. Liu, H. J. Wann, P. K. Ko, C. Hu, and Y. C. Cheng, "Improvement of

- [7] Z. Liu, H. J. Wann, P. K. Ko, C. Hu, and Y. C. Cheng, "Improvement of charge trapping characteristics of N<sub>2</sub>O-annealed and reoxidized N<sub>2</sub>Oannealed thin oxides," *IEEE Electron Device Lett.*, vol. 13, p. 519, 1992.

- [8] A. Uchiyama, H. Fukuda, T. Hayashi, T. Iwabuchi, and S. Ohno, "High performance dual-gate sub-half micron CMOSFET's with 6 nm thick nitrided SiO<sub>2</sub> films in a N<sub>2</sub>O ambient," *IEDM Tech. Dig.*, p. 425, 1990.

- [9] S. Hadda and M. S. Liang, "Improvements of thin-gate oxide integrity using through-silicon-gate nitrogen ion implantation," *IEEE Electron Device Lett.*, vol. EDL-8, p. 58, 1987.