# Superior Low-Pressure-Oxidized Si<sub>3</sub>N<sub>4</sub> Films on Rapid-Thermal-Nitrided Poly-Si for High-Density DRAM's

H. C. Cheng, Member, IEEE, H. W. Liu, H. P. Su, and G. Hong

Abstract—High-performance stacked storage capacitors with small effective-oxide-thickness ( $t_{\rm ox,eff}$ ) as thin as 37 Å has been achieved using low-pressure-oxidized nitride films deposited on NH<sub>3</sub>-nitrided poly-Si electrodes. The capacitors exhibit excellent leakage property and time-dependent-dielectric-breakdown (TDDB) characteristics. Furthermore, this technique is promising for the 64- and 256-Mb dynamic-random-access-memory (DRAM) applications because the process temperatures never exceed 850°C.

## I. INTRODUCTION

TOR 64 Mb DRAM's and beyond, the drastic reduction in cell size has necessitated three dimensional cell structure and high-performance ultrathin capacitor dielectrics. The CVD-Ta<sub>2</sub>O<sub>5</sub> film on smooth poly-Si was shown to possess high capacitance, but high leakage current and process-induced degradation were inevitable and needed to be conquered [1]. Conventional oxide/nitride (ON) stacked dielectric has been extensively utilized as stacked cell capacitors because of its low defect density, high breakdown field and reliability. However, limitations of capacitance increase and leakage reduction still exist [2]. Many methods have been proposed to improve the properties of ON dielectric [3], [4]. The ON films fabricated by rapid-thermal-processing have been shown to express excellent characteristics for DRAM applications [5], [6]. Nevertheless, thermal stress and high temperature treatment will cause serious problems. Recently, a novel technique to fabricate superthin oxide/nitride/oxide (ONO) stacked dielectric has been proposed by oxidizing very thin Si<sub>3</sub>N<sub>4</sub> at low pressure on silicon substrate [7]. This dielectric exhibited not only high maximum attainable capacitance ( $t_{\rm ox, \, eff} \sim 46$ A) but also low leakage current and high reliability.

In this letter, by using rapid thermal nitridation (RTN) of smooth poly-Si films prior to  $Si_3N_4$  deposition to avoid the native oxide formation, [8], [9], high-performance dielectrics with even higher-capacitance ( $t_{ox, eff} \sim 37$  Å) can be fabricated after the low pressure oxidation of the nitride films under the processing temperature of  $850^{\circ}$ C.

Manuscript received June 19, 1995. This work was supported in part by the Republic of China National Science Council (R.O.C. NSC) under Contract NSC-83-0404-E009-050.

H. C. Cheng, H. W. Liu, and H. P. Su are with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, National Nano Device Laboratory, Hsinchu 300, Taiwan, R.O.C.

G. Hong is with the United Microelectronics Corporation, Hsinchu 300, Taiwan, R.O.C.

IEEE Log Number 9414970.

#### II. EXPERIMENTAL PROCEDURES

Capacitors with doped smooth poly-Si bottom electrodes were fabricated on Si substrates covered with SiO<sub>2</sub>. A 3000 Å-thick LPCVD poly-Si was deposited at 620°C using pure SiH<sub>4</sub> gas. Subsequently, POCl<sub>3</sub>-diffused, p-glass stripped and then these wafers were cleaned by standard RCA procedures. Prior to LPCVD Si<sub>3</sub>N<sub>4</sub> deposition, the samples received RTN in pure NH<sub>3</sub> at 850°C for 60 s. After 30 Å-thick Si<sub>3</sub>N<sub>4</sub> deposition, low-pressure oxidation was performed at 850°C, 0.5 Torr for 30 min, followed by top poly-Si deposition, doping, and patterning. Both the top and bottom poly-Si layers were POCl<sub>3</sub>-doped at 850°C. For comparison, capacitors with the 50 Å-thick pure Si<sub>3</sub>N<sub>4</sub> films on the RTN-treated poly-Si were formed. Consequently, capacitance-voltage (C-V) measurements revealed that the effective oxide thicknesses  $(t_{\rm ox, eff})$  for the dielectrics with low-pressure oxidized Si<sub>3</sub>N<sub>4</sub> and pure nitrides were 37.2 and 36.1 Å, respectively. In such a case, the effective oxide thickness is calculated from the capacitance using the oxide dielectric constant of 3.9. The breakdown field  $(E_{\rm bd})$  is defined as the breakdown voltage  $(V_{\rm bd})$  divided by  $t_{\rm ox,\,eff}$  and the effective electric field  $(E_{\rm eff})$ is therefore defined as the gate voltage divided by  $t_{\text{ox, eff}}$ .

## III. RESULTS AND DISCUSSION

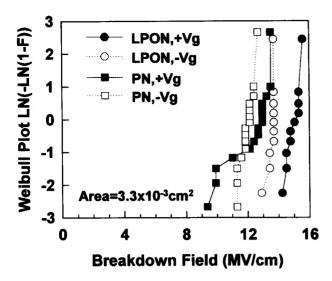

Fig. 1 compares the cumulative failure rates under rampvoltage test for the capacitors with the low-pressure-oxidized Si<sub>3</sub>N<sub>4</sub> (LPON) and pure nitride (PN) films under both gate polarities. For each type of samples, 15 capacitors were tested to construct the breakdown statistics. Obviously, the capacitors with LPON show larger breakdown fields  $(E_{\rm BD})$ for both polarities than those with PN. For the negative gatebias (-Vg), the Weibull distribution of the capacitors with LPON is similar to that with PN. In contrast, the capacitors with PN express a wider range of Weibull than those with LPON for positive gate-bias (+Vg). Low pressure oxidation of nitride films has been reported to be able to grow the oxide on the top and bottom of the nitride layers [7]. Therefore, an ONO structure is surmised to result in the higher and tighter electrical-breakdown-field  $(E_{\rm BD})$  distribution for the capacitors with LPON under both polarities. In addition, since the bottom native oxide has been eliminated by RTN, it is also found that all the capacitors with LPON and PN layers exhibit the breakdown field higher than 8 MV/cm. These results are consistent with previous research [4].

Fig. 1. The cumulative failure rates under ramp-voltage test for the capacitors with the low-pressure oxidized  $Si_3N_4$  (LPON) and pure nitride (PN) under both gate polarities.

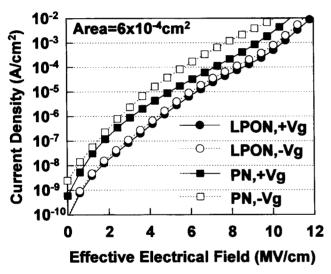

Fig. 2. The curves of current-density versus electrical-field (J-E) for the capacitors with LPON and PN biased at both gate polarities.

The curves of current-density versus electrical-field (J-E) for the capacitors with LPON and PN biased at both gate polarities are shown in Fig. 2. A significant reduction in leakage current is also observed for the capacitors with LPON for both gate polarities as compared to those with PN. RTN prior to Si<sub>3</sub>N<sub>4</sub> deposition has been reported to be a useful technique for reducing low-field leakage current [3]. However, low-pressure oxidation of nitride can further decrease leakage current without sacrificing the increased  $t_{

m ox,\,eff}.$  For the capacitors with LPON, the current densities at +1.65 V and -1.65 V are  $0.74 \times 10^{-6}$  A/cm<sup>2</sup> and  $1.04 \times 10^{-6}$  A/cm<sup>2</sup>, respectively, fulfilling the requirement of 64 Mb DRAM's. Moreover, the current densities at +0.75 V and -0.75 V are  $1.65 \times 10^{-8}$  A/cm<sup>2</sup> and  $2.10 \times 10^{-8}$ A/cm<sup>2</sup>, accordingly. The reduction in leakage current for the LPON is believed to be due to the formation of ONO stacked structure.

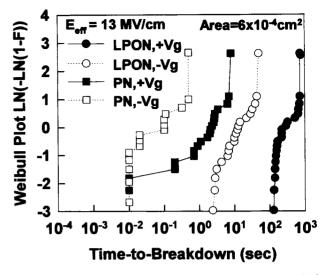

Fig. 3. Weibull plots of TDDB characteristics under constant electric field stress ( $E_{\rm eff}=13$  MV/cm) for the capacitors with LPON and PN under both gate polarities.

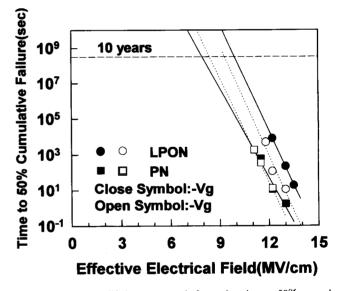

Fig. 4. The TDDB lifetime extracted from the time-to-50% cumulative-failure as a function of applied field  $E_{\rm eff}$  .

Weibull plots of TDDB characteristics under constant electric field stress ( $E_{\rm eff}=13~{\rm MV/cm}$ ) for the capacitors with LPON and PN under both gate polarities are shown in Fig. 3. Both gate biases were applied on the capacitors with an area of  $6\times 10^{-4}~{\rm cm}^2$ . The capacitors with LPON have a longer  $t_{\rm BD}$  as well as tighter  $t_{\rm BD}$  distribution than those with PN. This result is consistent with the outcome of the ramp-voltage tests, i.e., the breakdown field plots. Hence, LPON is an effective method for reducing the defect density and improving the reliability.

Fig. 4 shows the TDDB lifetime extracted from time-to-50% cumulative-failure as a function of applied  $E_{\rm eff}$ . The area of the measured capacitors is  $6\times 10^{-4}~{\rm cm}^2$ . Capacitors with LPON show much longer  $t_{\rm BD}$  than those with PN at the same effective electric field for both gate polarities. The long-term lifetime can be predicted by using this figure and the capacitors with LPON are estimated to survive long enough for more than 10 years at a stress field of  $\sim 10~{\rm MV/cm}$ .

## IV. CONCLUSIONS

In summary, the low-pressure oxidation of ultrathin nitrides on the RTN-treated smooth poly-Si exhibits high capacitance ( $t_{\rm ox, \, eff} \sim 37$  Å), low leakage current, and high reliability. Since the properties of the dielectrics can satisfy the requirements of 64 Mb DRAM's, this technology is promising for future high-density DRAM application.

## ACKNOWLEDGMENT

The authors thank the National Nano Device Laboratory of ROC NSC and the SRC of National Chiao Tung University for technical support.

## REFERENCES

- S. Kamiyama, P-Y. Lesaicherre, H. Suzuki, A. Sakai, I. Nishiyama, and A. Ishitani, "Ultrathin tantalum oxide capacitor dielectric layers fabricated using rapid thermal nitridation prior to low pressure chemical vapor deposition," J. Electrochem. Soc., vol. 140, no. 6, p. 161, 1993.

- [2] Z. A. Weinberg, K. J. Steein, T. N. Nguyen, and J. Y. Sun, "Ultrathin oxide-nitride-oxide films," *Appl. Phys. Lett.*, vol. 57, no. 12, p. 1248, 1991.

- [3] K. Ando, A. Ishitani, and K. Hamano, "Ultrathin silicon nitride films prepared by combining rapid thermal nitridation with low-pressure chemical vapor deposition," *Appl. Phys. Lett.*, vol. 59, no. 9, p. 1081, 1991

- [4] G. Q. Lo, D. L. Kwong, V. K. Mathew, and P. C. Fazan, "Highly reliable SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> dielectrics on rapid-thermal-nitrided rugged polysilicon for high-density DRAM's," *IEEE Electron Device Lett.*, vol. 13, no. 7, p. 372, 1992.

- [5] G. W. Yoon, G. Q. Lo, J. Kim, L. K. Han, and D. L. Kwong, "Formation of high quality storage capacitor dielectrics by in-situ rapid thermal reoxidation of Si<sub>3</sub>N<sub>4</sub> films in N<sub>2</sub>O ambient," *IEEE Electron Device Lett.*, vol. 15, no. 8, p. 266, 1994.

- [6] G. W. Yoon, J. Kim, L. K. Han, J. Yan, and D. L. Kwong, "Ultrathin (<30 Å) storage capacitor dielectrics prepared by in-situ multiprocessing and low pressure rapid thermal N<sub>2</sub>O reoxidation," in *Symp. VLSI Tech. Dig.*, p. 155, 1994.

- [7] H. P. Su, H. W. Liu, G. Hong, and H. C. Cheng, "Superthin O/N/O stacked dielectrics formed by oxidizing thin nitrides in low pressure oxygen for high-density memory devices," *IEEE Electron Device Lett.*, vol. 15, no. 11, p. 440, 1994.

- [8] K. Ando, A. Yokozawa, and A. Ishitani, "Ultrathin silicon nitride capacitors fabricated by in situ rapid thermal multi-processing for 256 Mb DRAM cells," Symp. VLSI Tech. Dig., p. 47, 1991.

- [9] N. Ajika, M. Ohi, H. Arima, T. Matsukawa, and N. Tsubouchi, "Enhanced reliability of native oxide free capacitor dielectrics on rapid thermal nitrided polysilicon," Symp. VLSI Tech. Dig., p. 63, 1991.