area performance of the proposed array is  $O(N^2 \log_2 N)$  and the time performance is  $O(\log_2 N)$ . Thus, the resulting (area × time)<sup>2</sup> is  $O(N^2 \log_2^3 N)$ , which is  $< O(N^3 \log_2^3 N)$  achieved by the arrays in [8, 9]. The features of high throughput performance and low areatime complexity make the proposed array useful for very high speed applications. It is also worth noting that the design for the 1-D IDCT can be directly applied to evaluate the 2-D IDCT based on row-column decomposition.

© IEE 1995 2 June 1995 Electronics Letters Online No: 19951276

Yu-Tai Chang and Chin-Liang Wang (National Tsing Hua University, Institute of Electrical Engineering, Hsinchu, Taiwan 30043, Republic of

Chin-Liang Wang: corresponding author

E-mail: clwang@ee.nthu.edu.tw

## References

- AHMED, N., NATARAJAN, T., and RAO, K.R.: 'Discrete cosine transform', *IEEE Trans.*, 1974, **C-23**, (1), pp. 90–93

TRIBOLET, J.M., and CROCHERIE, R.E.: 'Frequency domain coding of

- Speech', *IEEE Trans.*, 1979, **ASSP-27**, (5), pp. 512–530

CHEN, W.H., and SMITH, C.H.: 'Adaptive coding of monochrome and color images', *IEEE Trans.*, 1977, **COM-25**, (11), pp. 1285–1292

CLARKE, R.J.: 'Relation between the Karhunen-Loeve and cosine

- transform', *IEE Proc. F*, 1981, **128**, (6), pp. 359–360 KUNG, H.T.: 'Why systolic architectures?', *Computer*, 1982, **15**, (1),

- CHANG, L.W., and WU, M.C.: 'A unified systolic array for discrete

- cosine and sine transforms', IEEE Trans., 1991, SP-39, (1), pp. 192-194

- TOTZEK, U., and MATTHIESEN, F.: 'Two-dimensional discrete cosine transform with linear arrays'. Proc. Int. Conf. Systolic Arrays (Systolic Array Processors), 1989, pp. 388–397

WANG, C.-L., and CHEN, C.-Y.: 'High-throughput VLSI architectures

- WANG, C.-L., and CHEN, C.-Y.: 'High-throughput VLSI architectures for the 1-D and 2-D discrete cosine transforms', IEEE Trans. Circuits Syst. Video Technol., 1995, 5, (1), pp. 31-40

THOMPSON, C.D.: 'Fourier transforms in VLSI', IEEE Trans., 1983, C-32, (11), pp. 1047-1057

LI. W.: 'A new algorithm to compute the DCT and its inverse', IEEE Trans., 1991, SP-39, (6), pp. 1305-1313

## Unified array architecture for discrete cosine transform, sine transform and their inverses

Jiun-In Guo, Chingson Chen and Chein-Wei Jen

Indexing terms: Discrete cosine transforms. Sine transforms.

A unified array design for the discrete cosine transform, discrete sine transform and their inverses based on a new general formulation is presented. The presented design provides the flexibility to adaptively select different types of transforms in transform coding according to the characteristics of images for minimising the bit rate as much as possible.

Introduction: In transform coding, the discrete cosine transform (DCT) and discrete sine transform (DST) have been widely used owing to the good performance and acceptable computational complexity as compared with the statistically optimal Karhunen-Loeve transform (KLT) [1 - 3]. To meet the speed requirement of real-time applications, dedicated DCT or DST hardware designs are developed [4 - 8], (see references in [2, 3, 9]). Owing to the different properties of the transform kernels, there are different applications for the DCT and DST. For images with high correlation coefficients, e.g.  $\rho \ge 0.9$ , using DCT yields better performance. On the other hand, for images with low correlation coefficients, e.g.  $|\rho| < 0.5$ , using DST yields lower bit rates [2]. Therefore, to minimise the bit rates of encoded images in transform coding, a flexible transform hardware which can adaptively perform different transform functions is inevitable.

We present a unified array design for the DCT, DST, and their inverses according to a new general formulation. The presented design provides the flexibility to adaptively select different types of transforms in transform coding according to the characteristics of images such that the bit rate can be minimised as much as possible. Compared with the dedicated DCT or DST hardware designs proposed in the literature, the presented design possesses higher flexibility with respect to different characteristics of images and different applications.

Algorithm derivation: The DCT and DST of a 1-D N-point sequence  $\{y(n)\}\$  can be generally expressed as

$$Y(k)=\sqrt{\frac{2}{N}}\epsilon_k\sum_{n=i}^jy(n)C(n,k)\quad k=i,...,j \qquad (1)$$

and the inverse transforms can be shown as

$$y(n) = \sqrt{\frac{2}{N}} \sum_{k=1}^{j} \epsilon_k Y(k) C(n, k) \quad n = i, ..., j$$

(2)

$$\{i,j,C(n,k)\}\!=\!\left\{ \begin{array}{ll} 1\ N\!-\!1\,\cos\left(\frac{(2n+1)k\pi}{2N}\right)\ DCT/IDCT\\ 1\ N\ \sin\left(\frac{(2n-1)k\pi}{2N}\right)\ DST/IDST \end{array} \right\}$$

and  $\epsilon_k = 1/\sqrt{2}$  if k = 0 (for DCT/IDCT) or k = N (for DST/IDST) and  $\epsilon_k = 1$ , otherwise. If we neglect the scaling factor  $\sqrt{(2/N)}$  and introduce a variable x(n) for DCT/DST and a variable t(n) for IDCT/IDST, we can formulate eqns. 1 and 2 as

$$Y(k) = [2T(k) + \alpha(k)]\beta(k)$$

$$T(k) = \sum_{n=1}^{N-1} x(n) \cos\left(\frac{nk\pi}{N}\right) \quad k = 1, ..., N-1$$

$$Y(0) = \sum_{n=0}^{N-1} y(n)$$

$$Y(N) = \sum_{n=1}^{N} (-1)^{n+1} y(n)$$

(3)

$$t(n) = 2T(n) + \sqrt{2}\delta(n)$$

$$T(n) = \sum_{k=1}^{N-1} Z(k) \cos\left(\frac{nk\pi}{N}\right) \quad n = 1, ..., N-1 \quad (4)$$

ively, where

$$\begin{aligned} &\{\alpha(k),\beta(k),\delta(n),Z(k)\} = \\ &\{x(0) & \cos\left(\frac{k\pi}{2N}\right) & Y(0) & Y(k)\cos\left(\frac{k\pi}{2N}\right) & DCT/IDCT \\ &\{(-1)^kx(N) & -\sin\left(\frac{k\pi}{2N}\right) & (-1)^nY(N) & Y(k)\sin\left(\frac{k\pi}{2N}\right) & DST/IDST \end{aligned} \end{aligned}$$

and the variable

$$x(n)$$

is defined as

$$\begin{pmatrix} x(N-1) = y(N-1) \\ x(n) = y(n) - x(n+1) & n = 0, 1, ..., N-2 \end{pmatrix}$$

in the DCT case and

$$\begin{pmatrix} x(1) = y(1) \\ x(1) = y(1) \end{pmatrix}$$

(5)

$$\begin{pmatrix} x(1) = y(1) \\ x(n) = y(n) + x(n-1) & n = 2, 3, ..., N \end{pmatrix}$$

(6)

in the DST case. The relationship between the variables t(n) and

$$\begin{pmatrix} t(0) = 2y(0) \\ t(n) = y(n) + y(n+1) & n = 1, 2, ..., N-1 \end{pmatrix}$$

(7)

in the IDCT case and

$$t(N) = -y(N) t(n) = y(n+1) - y(n) \quad n = 1, 2, ..., N-1$$

(8)

in the IDST case. There is a common 1-D transform  $T(\cdot)$  in the above equations. That is, we can realise the DCT, DST, IDCT, and IDST based on a unified algorithm.

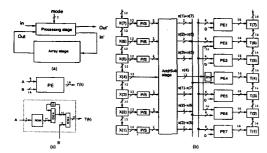

Architecture design: Based on the unified algorithm, we present an array design for the 1-D eight-point DCT, DST, IDCT and IDST. The design is composed of two parts: the array stage and the processing stage, as shown in Fig. 1a. The array stage, which realises the 1-D transform  $T(\cdot)$ , is implemented by using the distributed arithmetic (DA) scheme [7, 9], which is shown in Fig. 1b. The

Fig. 1 Block diagram of proposed array, architecture of array stage in proposed design and structure of PEs

- a Block diagram of proposed array

- b Architecture of array stage in proposed design c Structure of PEs

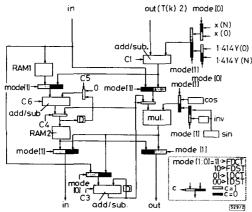

structure of the processing elements (PEs) which are composed of small ROMs and adders, is shown in Fig. 1c. Using the DA scheme can effectively reduce the hardware cost and give good numerical accuracy [7]. The processing stage performs all the preprocessing and postprocessing operations in the algorithm. It contains a multiplier, adder/subtractors, memory modules and multiplexing circuits, as shown in Fig. 2. The values of the control signals  $\{C_i, i = 1,..., 6\}$  are summarised in Table 1. This array design has been verified through the computer simulation of VER-ILOG codes.

Table 1: Values of control signals in processing stage

| Signal | 8 consecutive values | DCT      | DST      | IDCT     | IDST     |

|--------|----------------------|----------|----------|----------|----------|

| C1     | 10101010             |          | <b>-</b> |          | <b>√</b> |

|        | 00000000             | <b>√</b> | -        | <b>√</b> |          |

| C2     | 10000000             |          |          |          |          |

|        | 00000001             |          | 1        |          | -        |

|        | 00000000             | -        |          | 1        | <b>√</b> |

| C3     | 10101010             |          | 1        |          |          |

|        | 00000000             | <b>√</b> |          | ·        |          |

| C4     | 10000000             |          |          | <b>V</b> | <b>√</b> |

|        | 00000000             | <b>V</b> | 1        |          |          |

| C5     | 10000000             | <b>V</b> | <b>V</b> | 1        | <b>V</b> |

| C6     | 11111111             | <b>√</b> |          |          |          |

|        | 00000000             |          |          |          |          |

Fig. 2 Architecture of processing stage in proposed design

Conclusion: In the literature, there is a unified systolic array proposed for the DCT and DST [8]. The basic motivation of the design in [8] is the same as that of the presented design, but the methods are different. The design in [8] adopts a recursive algorithm to compute the DCT and DST, which eliminates the memory access time compared with the designs which store the transform kernels in memory. However, this memory access time is short since most DCT and DST designs use small memory modules. Moreover, the design in [8] should entail much hardware cost in VLSI implementation for the recursive generation of the transform kernels. In summary, the presented design not only possesses high functional flexibility, but also minimises the hardware cost.

© IEE 1995 Electronics Letters Online No: 19951254 31 May 1995

Jiun-In Guo (Department of Electronics Engineering, Lien-Ho Junior College of Technology, Miao-Li, Taiwan, Republic of China)

Chingson Chen and Chein-Wei Jen (Institute of Electronics, National Chiao-Tung University, Hsin-Chu, Taiwan, Republic of China)

## References

- AHMED, N., AHMED, N., NATARAJAN, T., and RAO, K.R.: 'Discrete cosine transform', *IEEE Trans.*, 1974, C-23, pp. 90-93

JAIN, A.K.: 'Fundamentals of digital image processing' (Prentice-

- Hall, Englewood Cliffs, NJ, 1989)

- RAO, K.R., and YIP, P.: 'Discrete cosine transform: Algorithms, advantages, applications' (Academic Press, Inc., 1990) GUO, J.I., LIU, C.M., and JEN, C.W.: 'New systolic arrays for prime

- length discrete cosine transform'. Proc. IEEE Workshop on Visual Signal Processing and Communications, 1991, pp. 67-70

- GUO, J.I., LIU, C.M., and JEN, C.W.: 'A memory-based approach to design and implement systolic arrays for DFT and DCT'. Proc. IEEE Int. Conf. on Acoustics, Speech, and Signal Processing, 1992, pp. v.621-v.624

- GUO, J.I., LIU, C.M., and JEN, C.W.: 'The efficient memory-based VLSI array designs for DFT and DCT', *IEEE Trans.*, 1992, CAS-II-39, pp. 723-733

- SUN, M.T., WU, L., and LIOU, M.L.: 'A concurrent architecture for VLSI implementation of discrete cosine transform', IEEE Trans., 1987, CAS-34, pp. 992-994

- CHANG, L.W., and WU, M.C.: 'A unified systolic array for discrete cosine and sine transforms', IEEE Trans., 1991, SP-39, pp. 192-

- WHITE, S.A.: 'Applications of distributed arithmetic to digital signal processing: A tutorial view', IEEE ASSP Mag., 1989, 6, pp. 4-19

## Relative permittivity measurement of thickfilm dielectrics at microwave frequencies

H. Huang, C.E. Free, K.E.G. Pitt, A.R. Berzins and G.P. Shorthouse

> Indexing terms: Permittivity measurement, Cavity resonators, Thick film capacitors, Microwave measurements

A novel extension of the resonant cavity technique used to measure relative permittivity at microwave frequencies is presented. The new technique is aimed particularly at the measurement of very thin dielectric layers and has been used to measure the permittivity of a thin dielectric layer printed onto a thick substrate whose permittivity is known. experimental data has been obtained for 100 µm thick dielectrics at X-band.

Introduction: Multilayer transmission lines using thin dielectric layers are commonly used as part of the high density interconnection structure found in modem multichip modules (MCMs). MCM devices are increasingly used for high speed data applications, and to properly characterise these devices, the performance of the dielectric layer at high frequencies needs to be precisely established [1, 2]. Various methods have been employed for the measurement of permittivity of sheet and plate materials at microwave frequencies [3 - 5]. In most cases, the sample under test is inserted in a transmission line system and the permittivity is deduced from measurement of the reflection and transmission coefficients using a vector network analyser. These methods are