# Nano-Roughening for Reliable N/MEMS Manufacture

Chia-Yeh Yang<sup>1,2</sup>, Y. T. Cheng<sup>1</sup>, and W. S. Hsu<sup>2</sup>

<sup>1</sup> Microsystems Integration Laboratory, Department of Electronics Engineering, National Chiao Tung University

<sup>2</sup>Department of Mechanical Engineering, National Chiao Tung University 1001 Ta Hsueh Road, Hsinchu, Taiwan, 300, ROC

\*ytcheng@mail.ncut.eud.tw

*Abstract*—This paper presents a nano-roughneneing technique to effectively modify bonding surface for ensuring for the continuation of hermetic encapsulation shrinkage from MEMS to NEMS. The roughening is realized via a non-uniform etch characteristic of PR which is etched then utilized as an etching mask for the following silicon etching process. UV adhesive bonding is utilized for the verification of the nano-roughening for NEMS hermetic encapsulation. The average roughnesses of silicon substarte before and after the modification are 0.4nm and 12.4nm respectively. The roughness increase can effectively provide more than 30% bonding strength enhancement and 8% leakage reduction.

Keywords Nano-roughening, NEMS Manufacture, Hermetic Encapsulation, UV Adhesive, Bonding

# I. INTRODUCTION

The advance of nanotechnology has disclosed a new era of (Nanoelectromechanical Systems) development. NEMS Nevertheless, poor efforts have been made on manufacturerelated researches. For instance, wafer-level processing is a key principle that can ensure the success of N/MEMS commercialization with low manufacturing cost. However, due to the large surface area-to-volume ratio and free-standing feature of N/MEMS devices, device structure would be susceptible to processing damages like the structural stiction or breakage induced by wafer dicing operation [1]. Thus, like MEMS fabrication, the incorporation of hermetic encapsulation into NEMS manufacture for wafer level processing has become increasingly significant. Previously, utilizing microshells to encapsulate as-fabricated MEMS devices in wafer-level via an appropriate wafer bonding technique has been a common approach for low cost manufacture application. The microshell provides mechanical support, thermal and electrical path, and hermetic seal for the MEMS devices.

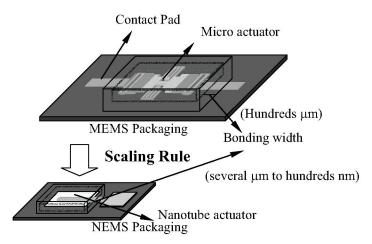

In the approach, several adhesive bonding techniques have been proposed and fascinated for MEMS hermetic encapsulation due to the characteristics of low-processing temperature and low-sealing cost [2,3]. However, like IC scaling rule, the conventional MEMS encapsulation size must shrink from sub-millimeter scale down to sub-micrometer one as shown in Fig. 1 in terms of the reduction of parasitic effect and manufacturing cost of NEM. In the bonding scheme, bonding strength will decrease with the cap size. Since the bonding width of a NEMS encapsulation is only several micrometers or even smaller, the strength reduction would evidently affect the reliability of encapsulation. Thus, this paper is to employ a nano-roughening method for the strength and reliability improvement of NEMS hermetic encapsulation. Via the modification of the bonding interface, the cap size can be reduced effectively.

Fig. 1. The scaling rule for the packaging transition from MEMS to NEMS. The bonding width has to shrink from hundreds micrometers to several micrometers or even smaller.

## II. FABRACTION PROCESS

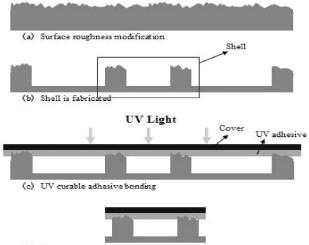

In the experiment, a glass-to-silicon hermetic encapsulation scheme using UV curable adhesive [2] is utilized as the demonstration vehicle for the investigation of nano-roughening effect. Two kinds of silicon surfaces, with and without nanoroughening treatment, are utilized for the comparison purpose. Figure 2 illustrates the fabrication of hermetic nanoencapsulation. The roughening is first accomplished on a 4" silicon wafer using the previously developed surface modification method which combines both spin-on photoresist (PR) and RIE etching [4].

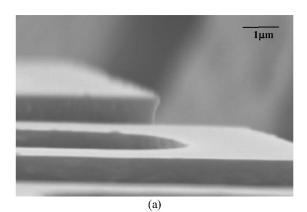

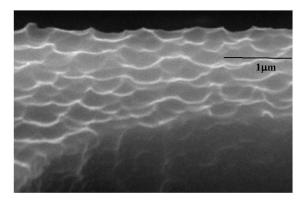

The nanopatterning first comes with  $0.5\mu$ m FH-6400 PR coating on a silicon substrate followed by 120°C baking for 5min. The PR coated surface is then reactive-ion-etched using 100W RF powered plasma at a 20mTorr of SF<sub>6</sub> and O<sub>2</sub> mixture with the gas flow ratio of 20 to 4 sccm. The roughening is realized via a non-uniform etch characteristic of PR. The etched PR is used as an etching mask underneath which the silicon is exposed and etched. After patterning on the silicon surface, residual resist is then removed using the mixture of sulfuric acid and hydro peroxide. Figure 3 shows the surfaces before and after roughening whose average roughnesses are 0.4 and 12.4nm respectively.

This work is supported by the National Science Council (Taiwan) under Grant NSC 94-2220-E-009-002, NSC 94-2212-E009-016, and and in part by MediaTek Research Center.

<sup>\*</sup>Contact author: ytcheng@mail.nctu.edu.tw.

(d) Success

Fig. 2. The process flow of the hermetic packaging. (a) surface roughening on a 4" silicon substrate using the surface modification method which combines both spin-on photoresist and RIE etching [4], (b) 9 $\mu$ m deep concave cavity fabrication using plasma etching, (c) silicon-to-glass bonding with UV curable adhesive (d) dicing operation.

(b)

Fig. 3. SEM micrographs of silicon surfaces (a) without, (b) with nanoroughening treatment.

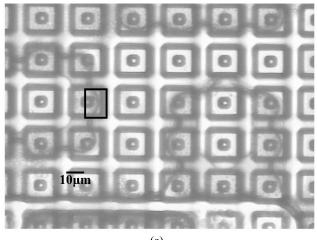

The roughened substrates are then plasma etched to form  $9\mu m$  deep microcavities to define bonding areas. Two different bonding widths, 2 and  $4\mu m$ , are chosen for bonding

characterization. At final, the substrate is tentatively adhered with another substrate, which is a flat Pyrex 7740 glass wafer spin-coated with a layer of  $3\mu$ m thick UV curable adhesive. After a 40mW/cm<sup>2</sup> flood exposure of UV light onto the two substrates for 90mins, the adhesive bond is formed and hermetically sealed microcavities are fabricated as shown in Fig. 4. The adhesive, LOCTITE product 3491, chosen for the testing is provided by Henkel company due to its low viscosity, single component, and excellent resistance to prolonged humidity or water immersion [5].

(a)

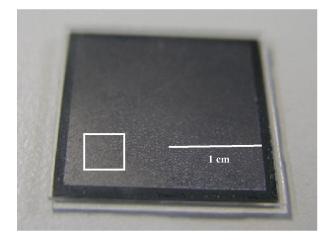

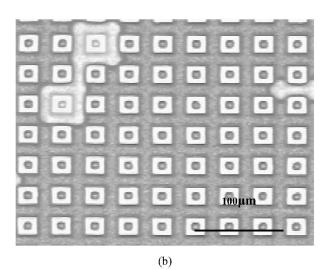

Fig. 4. Optical micrographs of silicon-to-glass bonding with UV curable adhesive. (a) overall view , (b) enlarged view. The microcavities is designed with a  $4\mu m$  wide bonding width.

## III. RESULTS AND DISCUSSION

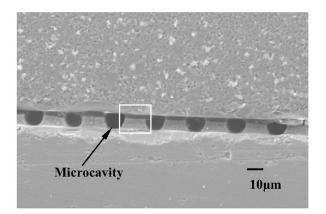

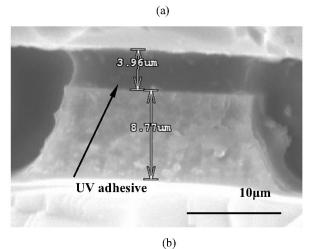

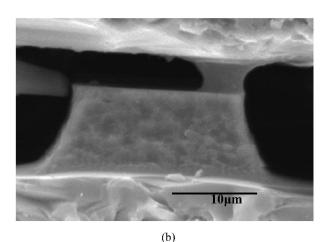

Figure 5 shows a uniform bond formed between two substrates while the adhesive is well UV-cured. The enlarged cross sectional view shows a layer of  $4\mu$ m thick cured adhesive is formed between silicon and glass substrates. The hermeticity of encapsulation is then examined by immersing the microcavities into water. Due to the contrast difference resulted by the refraction index difference between water and air, the failed encapsulation can be easily observed under an

optical microscope as shown in Fig. 6. Fig. 6(a) shows an optical micrograph of hermetic sealed microcavitites after leakage test. The darken region represents the leaky path with trapped moisture. The leakage is mainly caused by an incomplete bond formed in the bonding interface as shown Fig. 6(b). The testing result shows that the addition of nanoroughening can have about 8% failure rate reduction.

Fig. 5. SEM cross sectional micrograph of silicon-to-glass bonding with UV curable adhesive. (a) overall view , (b) enlarged view.

Fig. 6. Hermeticity test results (a) optical micrograph of the hermetic packages after leakage testing (b) enlarged SEM cross sectional view taken from the bonding interface of the failed package.

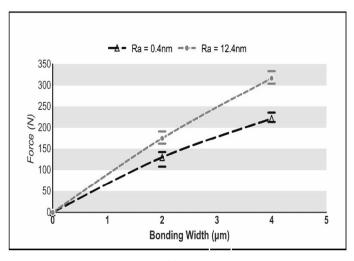

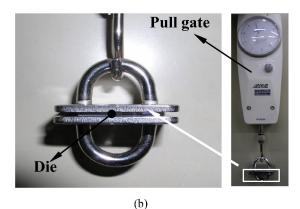

Fig. 7. Bonding strength characterization. (a) pull test results for the microcavities designed with 2 and  $4\mu m$  bonding width respectively, (b) pull test stage.

The bonding strength is characterized using a home-made pull testing stage shown in Fig. 7. The top and bottom sides of tested die are first glued to stainless plates. Then, a pull gate is connected to the plates and utilized to measure the bonding strength. The intrinsic bonding strength of Si-to-glass bond using UV adhesive is 7.29MPa. The strength is mainly limited by the poor adhesive force between the silicon or glass surface and the UV glue. Thus, the experiment further shows that UV curable adhesive bond with higher surface roughness has larger bonding force. The bonding strength can be enhanced up to 34.6% in the 2µm bonding width and 43.2% in the 4µm bonding width.

According to the stamp-and-stick test, it is found that the nano-roughening can provide a better adhesive characteristic to the UV glue as shown in Fig. 8. The darken region represents the surface covered with the glue after stamp-and-stick processing. The contrast indicates the non-uniform distribution of UV adhesive on the microcavitites. Thus, the microcavities with the surface roughening treatment can be uniformly coated with a layer of UV glue in comparison with the one without having the roughening. Since the stamp-and-stick process has been a common nano/microfabrication technique for various applications, such as microfluidic device fabrication and nanoimprinting [6,7], the result can further ensure the success of the applications via the utilization of nano-roughening.

| 10µm | 10µm |

|------|------|

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

Fig. 8. Stamp-and-stick test results: (a) and (b) show the silicon surface without nano-roughening before and after stamp-and-stick to UV curable adhesive, respectively. (c) and (d) show the silicon surface with nano-roughening before and after stamp-and-stick to UV curable adhesive, respectively.

## IV. CONCLUSION

This paper reveals the importance of employing nonroughening for reliable hermetic encapsulation of N/MEMS manufacture. The surface roughening is realized via a nonuniform etch characteristic of PR which is etched then utilized as an etching mask for the following silicon etching process. The roughening can enhance not only adhesive bonding strength, hermetic encapsulation yield for N/MEMS manufacture but also provide better sticky characteristics possible for nanoimprinting applications.

## ACKNOWLEDGMENT

Authors would like to express their appreciation to Mr. Hsiu-Luan Hsu at the Nano Facility Center of National Chiao Tung University for providing technical support. Authors would also like to thank Mr. Joseph Han at Henkel, Taiwan, Ltd. for providing UV curable adhesive and related technical assistance.

#### REFERENCES

- Y. C. Lee, B. A. Parviz, J. A. Chiou, and S. Chen, "Packaging for microelectromechanical and Nanoelectromechanical Systems", IEEE Tran. Adv. Pack., Vol. 26, pp. 217-226, 2003.

- [2] Z. H. Liang, Y. T. Cheng, W. S. Hsu, and Y. W. Lee, "A low temperature wafer-level hermetic MEMS package using UV curable adhesive", IEEE Elec. Comp. and Tech. Conf., pp. 1486-1491, 2004.

- [3] F. Sarvar, D. A. Hutt, and D. C. Whalley, "Application of adhesives in MEMS and MOEMS assembly: a review", Polymers and 2nd International IEEE Conference on Adhesives in Microelectronics and Photonics, POLYTRONIC 2002. pp.:22 – 28, 2002.

- [4] C. C. Lee, and W. S. Hsu, "Method on surface roughness modification to alleviate stiction of microstructures", J. Vacuum Science & Technology B, pp. 1505-1510, 2003.

- [5] LOCTITE Product 3491 description sheet, May, 1999.

- [6] S. Satyanarayana, R. N. Karnik, and A. Majumdar, "Stamp-and-Stick Room-Temperature Bonding Technique for Microdevices", IEEE/ASME JMEMS, pp. 392-399, 2005.

- [7] J. -H. Jeong, Y. -S. Sim, H. Sohn, and E. -S. Lee, "UV Nanoimprint Lithograph Using an Elementwise Embossed Stamp", IEEE ICMEMS'04, pp. -, 2004.