# Fundamental Study of 95 High-Lead Solder Bump on Substrates Pre-Soldered with Eutectic PbSn

Chih-Chiang Chang\*, Chun-Cheng Lin and C.Robert Kao

Department of Materials Science and Engineering, National Taiwan University,

No. 1, Sec. 4, Roosevelt Road, Taipei City, Taiwan, ROC

(\* E-mail: d96527006@ntu.edu.tw Phone/Fax: +886-2-3366-3746)

Abstract-This study investigated the intermixing of 95Pb5Sn solder bumps and 37Pb63Sn pre-solder in flip-chip solder joints. The reaction conditions included multiple reflows (up to 10) at 240 °C, whereby previously solder-coated parts are joined by heating without using additional solder. We found that the molten pre-solder had an irregular shape similar to a calyx (i.e., a cuplike structure) wrapped around a high-lead solder bump. The height to which the molten pre-solder ascended along the solid high-lead solder bump increased with the number of reflows. The molten pre-solder was able to reach the UBM/95Pb5Sn interface after three to five reflows. The molten pre-solder at the UBM/95Pb5Sn interface generated two important phenomena: (1) the molten solder dewetted (i.e., flowed away from the soldered surface) along the UBM/95Pb5Sn interface, particularly when the number of reflows was high, and (2) the molten pre-solder transported Cu atoms to the UBM/95Pb5Sn interface, which in turn caused the Ni-Sn compounds at the chip-side interface to change into (Cu<sub>0.6</sub>Ni<sub>0.4</sub>)<sub>6</sub>Sn<sub>5</sub>.

## 1. Introduction

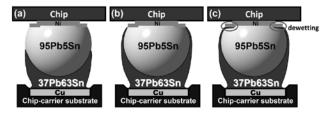

Flip-chip microelectronic assembly is one of the key packaging technologies in use today for the fabrication of electronic products. It is the dominant packaging solution for high-performance chips because it offers a shorter electrical connection length and a higher input/output interconnection density. High-lead solders such as 95Pb5Sn (wt.%, same below) have been used in flip-chip solder joints since this technology came into existence [1-3] and are exempt from the European Union's Restriction of Hazardous Substances requirements for their use in flip-chip devices. In flip-chip technology, organic chip-carrier substrates have a substantial cost advantage over ceramic substrates and are the only practical option for low-cost consumer electronics. However, high-lead solders have liquidus temperatures of around 320 °C, which could easily damage organic substrates. A "composite-solder" approach was proposed to overcome this problem [4]. This method uses solder with a lower melting point, such as 37Pb63Sn, in combination with a high-lead solder bump, as illustrated in Fig. 1. A much lower reflow temperature can consequently be used without the risk of damaging the organic substrates. In fact, the assembly process can be carried out with a peak reflow temperature of only 240 °C. Under such reflow conditions, 37Pb63Sn becomes molten but 95Pb5Sn does not melt. Nevertheless, molten 37Pb63Sn does have the capacity to dissolve some of the 95Pb5Sn solder bump during reflow. In other words, 37Pb63Sn and 95Pb5Sn will intermix during reflow. A literature search revealed that little is known about the intermixing of these two solders. The objective of this study was to investigate this intermixing phenomenon during the reflow stage.

## 2. Experimental

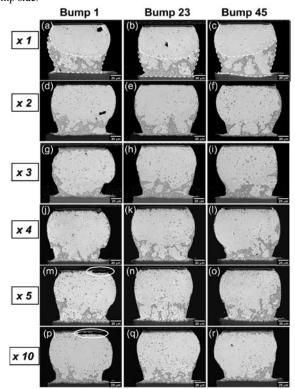

A schematic drawing of the flip-chip structure used in this study is shown in Fig. 1. On the chip side, an outer under-bump-metallization (UBM) layer composed of 3  $\mu$ m of Ni was in direct contact with a 95Pb5Sn solder bump. The 95Pb5Sn solder was electroplated onto the Ni layer and then reflowed at 350 °C to form a spherical bump with a nominal diameter of 95  $\mu$ m.

Figure. 1 Schematic drawing showing a 95Pb5Sn solder bump placed over a 37Pb63Sn pre-solder before assembly. Under the situation that the 95Pb5Sn in the solder bump and the 37Pb63Sn content in the printed solder paste are completely mixed, the overall composition will be 81Pb19Sn.

The top metal layer on the soldering pads was electroplated Cu. The pre-solder was screen-printed over this Cu layer. The mass ratio of the 95Pb5Sn solder in the solder bump relative to the 37Pb63Sn content in the screen-printed solder paste was 16:5. In this mass ratio, these two solders, when completely mixed, will from in an alloy with an overall composition of 81Pb19Sn.

The flip-chip assembly in this study was reflowed between one and ten times. The reflow during which the 37Pb63Sn solder paste first became molten and the substrate was bonded to the chip was considered the first reflow. The reflow used to form the 95Pb5Sn solder bump was not counted. Each reflow lasted 115 s, during which time the solder was molten and the peak reflow temperature was 240(±2) °C. The nominal ramp and cooling rates were both 1.5 °C/s.

The first reflow was monitored by a stereo-optical microscope to establish the melting process. After soldering was completed, the solder joints were mounted in epoxy and metallographically polished to reveal the interface and the internal microstructure. Image analysis software was used to measure the thickness of the layer of intermetallic compounds. The thickness of each layer was defined as the total area occupied by the intermetallic compound divided by the linear length of the interface. A scanning electron microscope (SEM) was used to examine the reaction zone for each solder joint, and a state-of-the-art field-emission electron probe microanalyzer (FE-EPMA, JEOL JXA-8500F, Tokyo, Japan) operated at 12 keV was used to identify the composition of the reaction products. During the microprobe measurement,  $K_{\alpha},$   $L_{\alpha},$  and  $L_{\alpha}$  X-rays were detected for Cu, Ag, and Sn, respectively. In the microprobe analysis, the concentrations of each of these elements were measured independently, and the total weight percentage was within 100 (± 1) wt.% in each case. For every data point, at least four measurements were made, and the average value was reported.

978-1-4244-4342-0/09/\$25.00 © 2009 IEEE

#### 3. Results and Discussion

#### 3.1 In situ reflow observation

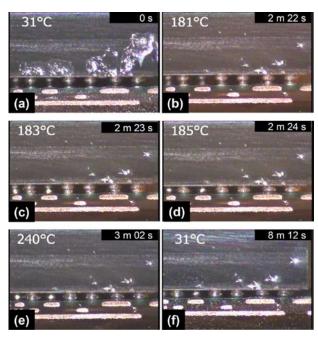

Figure 2 shows the sequence of events during the first reflow observed through a stereo microscope. The temperature and the time are shown at the upper-left-hand and upper-right-hand corners, respectively. The sample temperature was 31 °C when the reflow started, as shown in Fig. 2(a). The bright spheres represent the 95Pb5Sn solder bumps, and the dark regions immediately below the spheres represent the 37Pb63Sn solder paste. Figure 2(b) shows the microstructure 1 s before the solder paste began to melt; the temperature at this point was 181 °C. Figure 2(c) shows the exact moment when the temperature reached the eutectic point and when the solder paste started to melt. Because the solidus temperature of the high-lead solder bump was higher, the solder bump remained solid. As the solder paste became molten, its color changed from a dark color to that of shiny liquid metal. After another second, the molten 37Pb63Sn was displaced slightly to the side of the solid bumps, the standoff (i.e., the vertical distance between the chip and substrate) decreased, and the molten 37Pb63Sn climbed up the side of the solder-bump spheres, as shown in Fig. 2(d). The temperature at this point was 185 °C. When the peak reflow temperature was reached, the molten 37Pb63Sn climbed even higher up the side of the solder-bump spheres, as shown in Fig. 2(e). When the reflow ended, the standoff was the same as that at the peak reflow temperature, as shown in Fig. 2.

Figure. 2 In-situ observation of the first reflow process. (a) at 31 °C, (b) at 181°C, (c) at 183°C, (d) at 185 °C, (e) at 240 °C, and (f) at 31 °C. The number at the upper-right corner of each picture was the time (minutes and seconds) of the reflow.

A closer examination of the solidified solder joints revealed that the height to which 37Pb63Sn ascended along the 95Pb5Sn-solder-bump sphere was uneven. Figure. 3 shows that the shape of the solidified 37Pb63Sn solder was similar to that of a calyx (i.e., a cuplike structure) wrapped around the high-lead solder-bump sphere.

Figure. 3 Schematic drawing showing the calyx-shaped 37Pb63Sn presolder after the first reflow. The 37Pb63Sn wrapped around the high-lead solder bump.

### 3.2 Cross-sectional observation

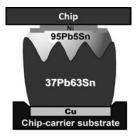

In this study, the flip-chip assembly had 45 solder bumps for each row of solder joints. The cross-sectional microstructures from the first outer row of each package were examined. These solder bumps were numbered left to right from 1 to 45. Accordingly, solder bumps 1, 23, and 45 were the left-corner, center, and right-corner bumps, respectively. Figure 4 shows the cross-sectional microstructures of bumps 1, 23, and 45 after 1-10 reflows. The darker regions in Fig. 4 are the Sn-rich phase, and the lighter regions are the Pb-rich phase. After the first reflow, the intermixing of 95Pb5Sn and 37Pb63Sn was relatively limited, and the boundary between these two solders could still be approximately delineated as shown by the dashed curve in Fig. 4(a)-(c). As the intermixing increased with the increase in reflows, it became increasingly more difficult to define a clear boundary between these two solders. Nevertheless, even after 10 reflows, these two solders still did not mix completely, as shown in Fig. 4(p)-(r). There was still a more Sn-rich phase on the substrate side and a more Pb-rich phase on the chip side.

Figure. 4 Cross-sectional views of the corner bumps (bump 1 and bump 45) and the center bump (bump 23) after 1-10 reflows. These bumps are from the first outer row of flip chip packages.

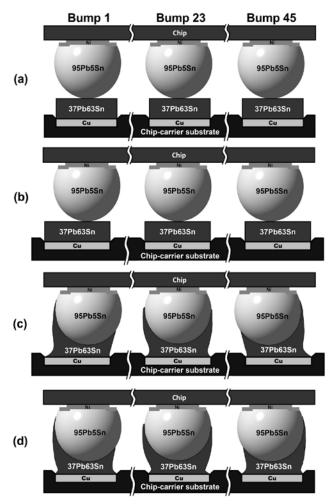

A clear difference can be seen between solder bumps 1, 23, and 45 when comparing the joint shapes. The solder joints for the center solder bump (bump 23) exhibited a symmetrical shape; however, the shape of the solder joints for solder bump 1 was asymmetrical and skewed slightly to the left. The solder joints for bump 45 were also asymmetrical, but they were skewed to the right. The schematic drawing shown in Fig. 5 helps clarify the difference in joint shapes. The solder bumps were perfectly aligned with the pre-solder on the substrate before reflow, as shown in Fig. 5(a). During reflow, as the oven temperature increased, the chip and the substrate expanded. The difference in the coefficient of thermal expansion between the silicon chip ( $\alpha = 2.6$  ppm/°C) and the chip-carrier substrate ( $\alpha = 15 \text{ ppm/}^{\circ}\text{C}$ ) caused the substrate to expand more than the chip. Consequently, the soldering pads on the chip side became misaligned with the substrate, as shown in Fig. 5(b). When the oven temperature rose beyond the eutectic temperature, the solder paste melted and climbed up along the high-lead solder bump, as shown in Fig. 5(c). During the cooling stage, the molten solder solidified, and the substrate contracted and slightly deformed the solder joints. These processes resulted in the final joint shapes shown in Fig. 5(d).

Figure. 5 Schematic drawings showing the joint shapes development during the reflow process for Bump 1 (left column), Bump 23 (central column), and Bump 45 (right column). (a) before reflow at room temperature, (b) before solder paste melting, (c) after solder paste melting, and (d) after reflow at room temperature.

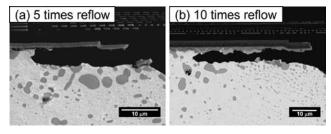

As the number of reflows increased, gaps between the UBM and the solder developed in some of the solder joints such as the ones shown in Fig. 4(m) and Fig. 4(p). Magnified views of these gaps are shown in Fig. 6. This phenomenon was attributed to the dewetting caused by the molten 37Pb63Sn, which climbed high enough to reach the chip side, as illustrated schematically in Fig. 7. After the first reflow, the molten solder only reached about half the height of the high-lead solder bump, as illustrated in Fig. 7(a). As the number of reflows increased, the tip of the molten solder climbed continuously higher and eventually reached the UBM/solder interface, as illustrated in Fig. 7(b). As the number of reflows continued to increase, the molten solder penetrated into the interface between the UBM and 95Pb5Sn, as illustrated in Fig. 7(c). During the cooling stage, the molten solder solidified, which was accompanied by a volume contraction. Because the bulk of the heat was drawn away from the substrate side, the molten solder solidified near the substrate side first. The last remaining molten solder was the solder near the UBM. The volume contraction occurred at the location of the last remaining molten solder (i.e., the tip of the calyx near the chip side), causing the formation of the gaps shown in Fig. 6. The formation of these gaps caused serious reliability concerns because the tip of the gap can serve as a site for the concentration of stress. Because these gaps had a tendency to develop in the samples with high reflow numbers, the application of reflows should be limited to less than five in products that are fabricated with composite solder joints.

Figure. 6 Magnified views showing the gap in Fig. 4 (m) and (p).

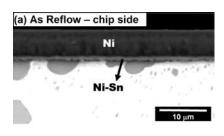

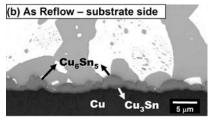

The interfacial reactions during reflow are described and discussed below. Figure 8(a) shows the microstructure of the chip-side interface after one reflow. There was only a very thin layer of intermetallic compound at the interface. The thickness of this layer was too thin to be positively identified by FE-EPMA. Because the FEEPMA detected only Ni and Sn signals, the layer was merely labeled as a Ni-Sn compound. Literature results carried out under similar situations suggest that this compound could very likely be Ni<sub>3</sub>Sn<sub>4</sub> [5–9]. Figure 8(b) shows that there were two intermetallic layers on the substrate side. The FE-EPMA measurement results showed that the outer layer was  $Cu_6Sn_5$ . The FE-EPMA did not detect a Ni signal in this  $Cu_6Sn_5$  layer. The layer between  $Cu_6Sn_5$  and Cu was very likely  $Cu_3Sn$  according to results found in similar studies [10–15].

Figure. 7 Schematic drawings showing the emergence of the gap caused by the de-wetting phenomenon. (a)-(c) represent increasing number of reflow.

Fig. 8 Cross-sectional micrographs showing the (a) chip side and (b) substrate side interfaces after the first reflow.

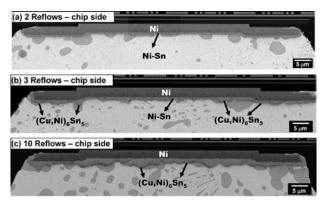

Additional reflows did not change the interfacial reaction on the substrate side, and the results were omitted here for the sake of brevity. Additional reflow, however, did produce substantial change on the chip-side interface, as shown in Fig. 9. After two reflows, the reaction product was the same as that obtained from one reflow (i.e., a Ni-Sn compound), as shown in Fig. 9(a). After three reflows, (Cu<sub>0.6</sub>Ni<sub>0.4</sub>)<sub>6</sub>Sn<sub>5</sub> replaced the Ni-Sn compound that formed along the outer rim of the solder joint, as shown in Fig. 9(b). The composition of this compound was determined by FE-EPMA measurements. In the central joint region, the Ni-Sn compound remained. After 10 reflows, the (Cu<sub>0.6</sub>Ni<sub>0.4</sub>)<sub>6</sub>Sn<sub>5</sub> compound had completely replaced the Ni-Sn compound, as showed in Fig. 9(c). Fig. 7 helps illustrate why the (Cu<sub>0.6</sub>Ni<sub>0.4</sub>)<sub>6</sub>Sn<sub>5</sub> compound initially formed along the outer rim. Cu atoms, which were needed to form this compound, came from the Cu soldering pad on the substrate side. The Cu atoms dissolved quickly during the reflow of the molten-Sn to solid-Cu reaction system [16]. Therefore, the melting of the pre-solder dissolved many Cu atoms during reflow. After multiple reflows, molten 37Pb63Sn reached the outer rim of the Ni UBM. Consequently, Cu atoms reached the outer rim of the solder joints first. Apparently, the Cu concentration was high enough to convert the intermetallic compound from Ni-Sn to (Cu<sub>0.6</sub>Ni<sub>0.4</sub>)<sub>6</sub>Sn<sub>5</sub>. The Cu concentration required to convert the compound was about 0.5 wt.% for lead-free solders [5-7]. The corresponding concentration for 37Pb63Sn, however, has not been established, but it should not significantly deviate from 0.6 wt.%.

Fig. 9 Cross-sectional micrographs showing the chip side interfaces after (a) 2 reflows. (b) 3 reflows, and (c) 10 reflows.

## 4. Summary

This study investigated the intermixing of 95Pb5Sn solder bumps and 37Pb63Sn pre-solder in flip-chip solder joints. During reflow, the molten pre-solder had a shape that was irregular and similar to a calyx wrapped around a high-lead solder bump. The shapes of the solder joints at the left, central, and right sides of the chip were different because of the difference in the coefficient of thermal expansion between the silicon chip and the chip-carrier substrate. The height at which the molten pre-solder climbed along the solid high-lead solder bump increased with the increase in the number of reflows. The molten pre-solder was able to reach the UBM/95Pb5Sn interface after three to five reflows. The molten pre-solder at the UBM/95Pb5Sn interface generated the following two important phenomena:

- (1) The molten solder dewetted along the UBM/95Pb5Sn interface, particularly when the number of reflows was high. This dewetting was considered to be a result of the volume shrinkage during the solder solidification stage.

- (2) The molten pre-solder transported Cu atoms to the UBM/95Pb5Sn interface. When enough Cu atoms reached the UBM/95Pb5Sn interface, the compound at the interface changed from Ni-Sn to (Cu<sub>0.6</sub>Ni<sub>0.4</sub>)<sub>6</sub>Sn<sub>5</sub>.

Acknowledgment. This work was supported by the National Science Council through grant NSC-97-2221-E-002-101-MY3.

#### References

- 1. E.M. Davis, W.E. Harding, R.S. Schwartz and J.J. Corning, *IBM J. Res. Develop.* 44, 56 (2000).

- 2. L.F. Miller, IBM J. Res. Develop. 13, 239 (1969).

- P.A. Totta and R.P. Sopher, *IBM J. Res. Develop.* 13, 226 (1969).

- 4. K.N. Tu, K. Zeng, Mater. Sci. Eng. R 34, 1 (2001).

- C.E. Ho, Y.L. Lin, and C.R. Kao, Chem. Mater. 14, 949 (2002).

- W.T. Chen, C.E. Ho, and C.R. Kao, J. Mater. Res. 17, 263 (2002).

- C.E. Ho, R.Y. Tsai, Y.L. Lin, and C.R. Kao, *J. Electron. Mater.* 31, 584 (2002).

- 8. C.M. Tsai, W.C. Luo, C.W. Chang, Y.C. Shieh, C.R. Kao, *J. Electron. Mater.* 33, 1424 (2004).

- 9. C.E. Ho, S.C. Yang, and C.R. Kao, *J. Mater. Sci. Mater. Electron.* 18, 155 (2007).

- A.J. Sunwoo, J.W. Morris and G.K. Lucey, *Metall. Trans. A* 23, 1323 (1992).

- W. Yang, L.E. Felton, and R.W. Messler, *J. Electron. Mater.* 24, 1465 (1995).

- 12. S. Choi, T.R. Bieler, J.P. Lucas, and K.N. Subramanian, *J. Electron. Mater.* 28, 1209 (1999).

- Y.W. Wang, Y.W. Lin, C.T. Tu, and C.R. Kao, *J. Alloy Compd.* 478, 121 (2009).

- Y.W. Wang, C.C. Chang, and C.R. Kao, J. Alloy Compd. 478 L1 (2009).

- Y.W. Wang, Y.W. Lin, and C.R. Kao, *Microelectron. Reliab*. 49, 248 (2009).

- M.L. Huang, T. Loeher, A. Ostmann and H. Reichl, *Appl. Phys. Lett.* 86, 181908 (2005).