# Single-Electron Emission of Traps in HfSiON as High-k Gate Dielectric for MOSFETs

C. T. Chan', C. J. Tang', C. H. Kuo', H. C. Ma', C. W. Tsai<sup>2</sup>, H. C.-H. Wang<sup>2</sup>, M. H. Chi<sup>2</sup>, and Tahui Wang<sup>4</sup>

<sup>1</sup>Dept. of Electronics Engineering, National Chiao Tung University

<sup>2</sup>Taiwan Semiconductor Manufacturing Company, Science-Based Industrial Park, Hsin-Chu, Taiwan e-mail: twang@cc.nctu.edu.tw

### ABSTRACT

A novel method for characterizing MOSFETs with HfSiON high-k gate dielectric is demonstrated for the first time by direct measurement of single-electron de-trapping. Individual high-k trapped electron emission is recorded, which is manifested by the step-like evolution of channel current. The physical path of electron de-trapping can be identified from the emission time of such single-electron de-trapping. The dependence of charge emission time on gate voltage and temperature is measured. An analytical model based on thermally assisted tunneling can predict the emission time behavior, trap activation energy, trap density, and total available traps in high-k gate dielectric.

[Keywords: high-k gate dielectric, HfSiON, traps, single electron emission, thermally-assisted tunneling]

### Introduction

As CMOS scaling continues with thinner gate oxides, the standby power increases to intolerable level as a result of direct tunneling current through the oxides. Thus, high dielectric constant (high-k) materials are emerging as a post-SiO<sub>2</sub> solution [1]. Recently, Hf-based silicate dielectric (HfSiON) has been successfully integrated in CMOS as gate dielectric (with EOT~1.5nm) for low power applications with good reliability, comparable mobility (to SiO<sub>2</sub>), and greatly reduced gate leakage [2]. The characterization of high-k gate dielectric is usually performed by a charge pumping (CP) technique [3]. However, the resolution of CP is limited due to the mixture of interface traps and traps in high-k gate dielectric bulk.

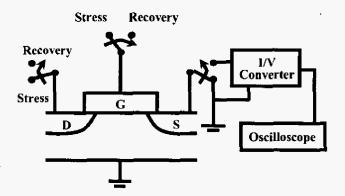

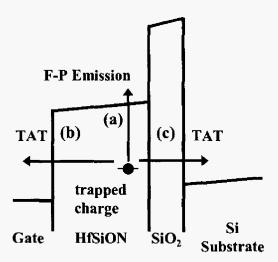

Figure 1. Experimental setup to measure high-k trapped charge emission times. In stress phase, V<sub>g</sub>=0.7V, V<sub>d</sub>=0V for 0.1s. In recovery phase, V<sub>g</sub>=0.25~0.55V, and V<sub>d</sub>=0.2V, and drain current temporal evolution is recorded by an digital oscilloscope. The high-speed switches minimize the delay between phase transitions down to µs.

In this study, we will demonstrate a novel technique for direct measurement of single-electron de-trapping in nMOSFETs with HfSiON gate dielectric [2]. Due to the discrete nature of trapped charge emission, the charge emission time can be clearly measured, and the physical path of de-trapping can be identified from the charge emission time. An analytical model based on tunneling can predict the behavior of electron emission, trap activation energy, trap density, and total available traps in high-k dielectric.

# SINGLE-ELECTRON EMISSION TIME OF TRAPS IN HFSION

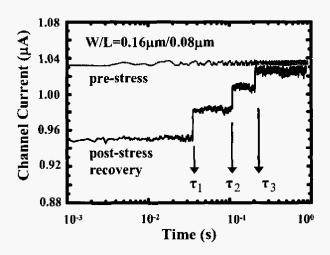

Figure 2. Pre- and post-stress current evolutions in a high-k nMOSFET with W/L=0.16 $\mu$ m/0.08 $\mu$ m. The measurement bias is  $V_e$ =0.3V and  $V_d$ =0.2V. Each current jump in the post-stress recovery corresponds to a single trapped charge escape from the high-k gate dielectric. Only three electrons are trapped during stress. The charge emission times in recovery phase are denoted by  $\tau_1$ ,  $\tau_2$ , and  $\tau_3$  in the figure.

The trapped charge behavior in high-k gate dielectric is studied by "stress" and "recovery" as shown in Fig. 1, where the temporal evolution of drain current is recorded by a digital oscilloscope and the time delay during phase transition is minimized by high-speed switches down to  $\mu s$ . The transient measurement setup is tested on MOSFETs with SiO2 as gate dielectric, stable I-t characteristics ensure that this method induces no spurious current transient. In "stress" phase,  $V_g$  is 0.7V for 100ms and electrons are injected and trapped into the high-k dielectric. In "recovery" phase, the drain current is measured with  $V_g\left(@0.25$  - 0.55V) and  $V_d\left(@0.2V\right)$ . The drain current of a small area post-stress nMOSFET (W/L=0.16/0.08 $\mu$ m) (Fig.2) increases in steps and finally saturates to a level

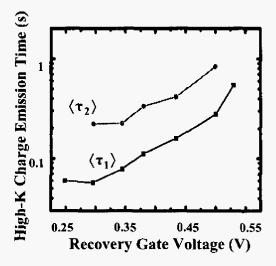

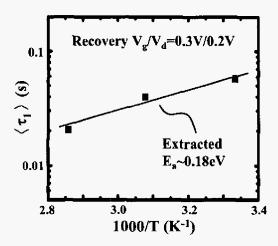

close to the pre-stress level (Fig. 2). In this study, each drain current step corresponds to a "single" electron de-trapping from the high-k dielectric. Interestingly, the time of occurrence for each electron de-trapping (i.e.  $\tau_1$ ,  $\tau_2$ , and  $\tau_3$ ) (or referred to as emission time) increases with  $V_g$  applied in "recovery" (Fig. 3). Ten measurements of each  $V_g$  bias on the same device were made to take an average. Furthermore, as expected, the emission time of electron de-trapping is found to decrease at elevated temperature (Fig. 4). The extracted activation energy is about 0.18eV. The above data indicates the mechanism of electron trapping/de-trapping in high-k gate dielectric as discussed next.

Figure 3.  $V_g$  dependence of averaged high-k trapped charge emission times  $\langle \tau_1 \rangle$  and  $\langle \tau_2 \rangle$  in recovery phase. Ten measurements on the same device are made to take average.

Figure 4. Temperature dependence of  $\langle \tau_1 \rangle$ . A straight line in the Arrhenius plot implies a thermal process is involved in trapped charge emission. The extracted activation energy is  $\sim 0.18 \text{eV}$ .

## RESULTS AND DISCUSSION

# Trapped Electron Emission Mechanism

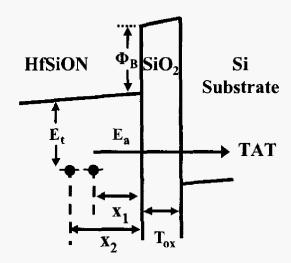

The observed longer electron emission time at larger  $V_g$  (Fig. 3) suggests the dominant path of charge emission toward Si substrate. There are three possible paths for electron de-trapping as illustrated in the energy band diagram in Fig. 5, i.e. Frenkel-Poole (F-P) emission (path a), SRH-like thermally-assisted-tunneling (TAT) (path b) [4-6] toward the gate electrode, and TAT toward the Si substrate (path c). The de-trapping path (a) is ruled out, since the activation energy for F-P mechanism should be equal to the trap energy,  $E_t$  (>1eV), and the extracted  $E_a$  is only 0.18eV. The detrapping path (b) is ruled out too since a larger  $V_g$  would accelerate the electron emission toward the gate electrode resulting in a shorter emission time. The observed emission time is just the opposite (Fig. 3). Temperature dependence (Fig. 4) with extracted activation energy of 0.18eV confirms the role of thermal process in charge emission.

Figure 5. Energy band diagram in recovery phase. Various charge escape paths are illustrated: (a) Frenkel-Poole (F-P) emission, (b) thermally-assisted-tunneling (TAT) to the gate, and (c) TAT to the Si substrate. From V<sub>g</sub> dependence and temperature dependence of charge emission time in Fig. 3 and Fig. 4, only (c) should be considered.

# Analytical Model for Electron De-trapping

An analytical model of the TAT mechanism is developed with energy band diagram and trap distance illustrated in Fig. 6:

$$\tau_i^{-1} = v \exp(-\alpha_{ox} T_{ox}) \exp(-\alpha_k x_i)$$

Eq. (1)

where

$$v = [N_C(1 - f_c)]v_{th}[\sigma_0 \exp(\frac{-E_a}{kT})]$$

Eq.(1a)

$$\alpha_{ox} = \frac{2\sqrt{2m_{ox}^*q(E_t + \Phi_B)}}{\hbar} \; ; \; \alpha_k = \frac{2\sqrt{2m_k^*qE_t}}{\hbar} \qquad \quad Eq.(1b)$$

Eq. (1) reveals the nature of tunneling for trapped electron emission time,  $t_i$ . The pre-factor v, a lumped parameter referred to as the "attempt-to-escape frequency" can be re-written as in Eq. (1a) [4]

where  $N_C$  is the effective density-of-state in the Si conduction band,  $N_C(1-f_c)$  is the amount of available states in Si substrate for outturneling electrons from high-k traps,  $\sigma_0$  and  $E_a$  represent the trap cross-section and the activation energy. Other variables have their usual definitions. The Fermi-Dirac distribution ( $f_c$ ) in the Si conduction band is a function of  $V_g$  in "recovery." A smaller recovery  $V_g$  leads to a lower surface carrier density (a smaller  $f_c$ ) and thus a shorter electron emission time. As the recovery  $V_g$  drops below the threshold voltage ( $V_1$ ), decrease in the emission time tends to saturates since  $f_c$  approaches zero. The electron nearest to the interface of Si substrate will be the first electron for de-trapping to occur. With respect to the temperature effect, a small recovery  $V_g$  (<0.25V), where  $f_c$ ~0, was chosen for measurement of the trap activation energy,  $E_a$ , shown in Fig. 4. The extracted activation energy from the Arrhenius plot is 0.18eV.

## High-k Trap Density and Total Available Traps

The high-k trap density can be evaluated through the analytical model, Eq. (1). By comparing

$$\tau_1 = v^{-1} \exp(\alpha_{ox} T_{ox}) \exp(\alpha_k x_1)$$

$$\tau_2 = v^{-1} \exp(\alpha_{ox} T_{ox}) \exp(\alpha_k x_2)$$

Figure 6. Schematic representation of gate dielectric band diagram in recovery phase and trap positions. E<sub>a</sub> is the activation energy for TAT, and the proposed model is described in detail in the text.

we obtain

$$\frac{\tau_2}{\tau_1} = \exp[\alpha_k(x_2 - x_1)]$$

Eq. (2)

and the high-k trap density (N<sub>t</sub>) is readily calculated as

$$N_1 = \frac{1}{(x_2 - x_1)WL} = \frac{1}{WL \frac{1}{\alpha_0} ln(\frac{\tau_2}{\tau_1})}$$

Eq.(3)

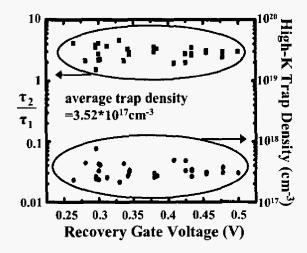

Eq. (2) predicts that the ratio of emission times (e.g.  $\tau_2$  to  $\tau_1$ ) is only related to the physical distance of trap sites away from the interface. Figure 7 indeed shows the ratio of  $\tau_2/\tau_1$  (10 readings of each gate bias on the same device) is constant and independent of recovery  $V_g$ . The average high-k trap density calculated from Eq. (3) (assuming

$m_k^* \sim 0.18 m_0 [7]$ ) is  $\sim 3.5*10^{17} cm^{-3}$ , or equivalently, an areal density of  $\sim 8.8*10^{10} cm^{-2}$ . This small trap density can hardly be resolved by CP due to a comparable interface trap density [3]. It should be pointed out that the extracted trap density, according to Eq. (3), is not affected by variables such as  $T_{ox}$ ,  $m_{ox}^*$  and  $E_a$ . The total available number of traps in high-k gate dielectric of each device is related to high-k thickness, trap density, and transistor size. The observed 3 electrons trapped in the nMOS after the "stress" in this study are less than the total available traps ( $\sim 10$ ) as calculated from the estimated trap density and transistor size.

Figure 7. The ratio of  $\tau_2$  to  $\tau_1$  versus gate voltage in recovery phase. Note that  $\tau_2/\tau_1$  remains almost unchanged with respect to Vg. The extracted high-k trap density from Eq.(2) is also given. Totally, 10 devices are measured in the figure.

## Gate Length Effects

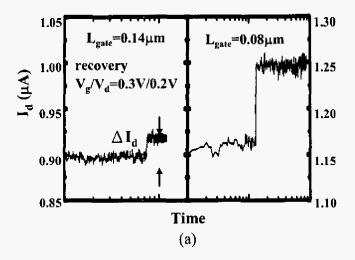

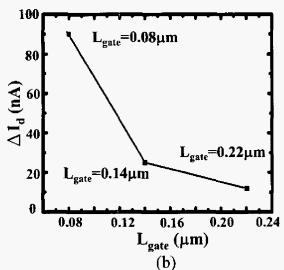

The experiment was conducted on devices with different gate lengths, 0.08  $\mu$ m, 0.14  $\mu$ m, and 0.22  $\mu$ m. It is found that while step-like current recovery traces due to single-electron de-trapping are still observed for all lengths, the amplitude of the drain current step ( $\Delta I_d$ ) decreases with longer gate lengths, as shown in Fig. 8. This trend is consistent with the Random Telegraph Signal theory [8] and implies that the impact of the trapped electron in the high-k dielectric spreads over the entire channel. Thus, a single-electron emission can be observed only when the device size is small enough and the high-k is clean enough!

## **CONCLUSIONS**

Single electron emission in HfSiON gate dielectric is observed. The emission times can be used to identify the de-trapping mechanism. The extracted high-k trap density and trap activation energy from this method is around ~3.5\*10<sup>17</sup>cm<sup>-3</sup> and 0.18eV, respectively. The proposed technique is a powerful tool to characterize trap in high-k gate dielectric for advanced CMOS.

## ACKNOWLEDGEMENT

The authors would like to acknowledge financial support from National Science Council under contract no.NSC93-2215-E009-032 and from TSMC/NCTU JDP program.

Figure 8. (a) Comparison of the current jump amplitude for  $L_{gate}$ =0.08 $\mu$ m and for  $L_{gate}$ =0.14 $\mu$ m. (b) The amplitude of charge escape induced current jump versus  $L_{gate}$ .

### REFERENCES

- [1] H. Iwai, S. Ohmi, S. Akama, C. Ohshima, A. Kikuchi, I. Kashiwagi, J. Taguchi, H. Yamamoto, J. Tonotani, Y. Kim, I. Ueda, A. Kuriyama, and Y. Yoshihara, "Advanced Gate Dielectric Materials for Sub-100nm CMOS," in proceedings of International Electron Device Meeting, 2002, pp. 625-628.

- [2] H. C.-H. Wang, S.-J. Chen, M.-F. Wang, P.-Y. Tsai, C. W. Tsai, T.-W. Wang, S. M. Ting, T.-H. Hou, P.-S. Lim, H.-J. Lin, Y. Jin, H.-J. Tao, S.-C. Chen, C. H. Diaz, M.-S. Liang, and C. Hu, "Low Power Device Technology with SiGe Channel, HfSiON, and Poly-Si Gate," in proceedings of International Electron Device Meeting, 2004, pp. 161-164.

- [3] R. Degraeve, A. Kerber, Ph. Roussel, E. Cartier, T. Kauerauf, L. Pantisano, and G. Groeseneken, "Effect of Bulk Trap Density on HfO<sub>2</sub> Reliability and Yield," in proceedings of International Electron Device Meeting, 2003, pp. 935-938.

- [4] R. R. Hearing, and E. N. Adams, "Theory and Application of Thermally Stimulated Current in Photoconductors," Physical Review, Vol. 117, NO. 2, pp. 451-454, 1960

- [5] K. A. Nasyrov, V. A. Gritsenko, M. K. Kim, H. S. Chae, S. D. Chae, W. I. Ryu, J. H. Sok, J.-W. Lee, and B. M. Kim, "Charge Transport Mechanism in Metal-Nitride-Oxide-Silicon Structures," IEEE Electron Device Letter, Vol. 25, NO. 6, pp. 336-338, 2002.

- [6] O. K. Lui, and P. Migliorato, "A New Generation-Recombination Model for Device Simulation Including the Poole-Frenkel Effect and Phonon-Assisted Tunneling," Solid State Electronics, Vol. 41, pp. 575-583, 1997.

- [7] Y. T. Hou, M. F. Li, H. Y. Yu, Y. Jin, and D.-L. Kwong, "Quantum Tunneling and Scalability of HfO<sub>2</sub> and HfAlO Gate Stacks," in proceedings of International Electron Device Meeting, 2002, pp. 731-734.

- [8] M.-H. Tsai, T. P. Ma, and T. R. Hook, "Channel Length Dependence of Random Telegraph Signal in Sub-Micron MOSFET's," IEEE Electron Device Letter, Vol. 15, NO. 12, pp. 504-506, 1994.