# Low-Temperature Processed MOSFET's with Liquid Phase Deposited $SiO_{2-x}F_x$ as Gate Insulator

Ching-Fa Yeh, Shyue-Shyh Lin, and Tzy-Yan Hong

Abstract—Device performances of MOSFET's with  $SiO_{2-x}F_x$  gate oxides prepared by an extremely low-temperature (15°C) liquid phase deposition (LPD) method were investigated. The electrical characteristics, including threshold voltage of 2.1 V, peak effective mobility ( $\mu_{\rm eff}$ ) of 525 cm²/V·s, and subthreshold swing of 134 mV/decade, show the devices exhibit comparable performance to other low-temperature processed MOSFET's. This demonstrates that LPD  $SiO_{2-x}F_x$  can be a suitable candidate for future gate insulators in low-temperature processed MOSFET's.

# I. INTRODUCTION

URRENT demand for reduced device dimensions, and increasingly complex device structures, have stressed the need for low-temperature processing [1]–[5], while high-temperature processing can redistribute impurities and thus generate defects. This is especially true during MOSFET gate oxide formation where many defects in high-temperature thermally grown SiO<sub>2</sub> film are responsible for early breakdowns [6], [7]. To date, a few MOSFET studies have looked at deposition of gate oxide at low temperatures [2]–[5]. Although they demonstrated some benefits, some of the methods still required high-temperature post-deposition treatment to improve device performance [2], [4]. In addition, all needed expensive apparatus and complex processing to prepare the low-temperature gate oxide.

Recently, a novel room-temperature liquid phase deposition (LPD) technique using inexpensive apparatus was developed for silicon oxide  $(SiO_{2-x}F_x)$  [8], [9], where the fluorine will be naturally incorporated into the film during deposition. The LPD  $SiO_{2-x}F_x$  also showed comparable performance of breakdown field and leakage current to other low-temperature prepared oxides. Because it had been reported that the fluorine incorporated in the MOSFET gate oxide evidently improves the interface characteristics and increases immunity to hotelectron induced stress [10]–[12]. Thus, we were interested in applying this low-temperature  $SiO_{2-x}F_x$  processing method to MOSFET gate insulators. This paper presents the electrical characteristics of MOSFET's made with such a new LPD gate oxide, and compares them with those of other types of low-temperature processed MOSFET's.

Manuscript received November 30, 1994; revised April 14, 1995. This work was supported by the National Science Council, Republic of China, under Contract NSC-83-0404-E-009-121.

C.-F. Yeh, S.-S. Lin, and T.-Y. Hong are with the National Chiao Tung University, Department of Electronic Engineering and Institute of Electronics, Hsinchu 300, Taiwan, Republic of China.

IEEE Log Number 9412362.

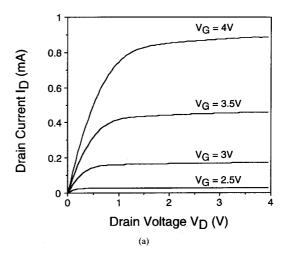

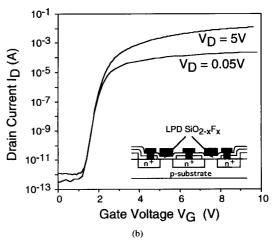

Fig. 1. The typical (a)  $I_D$ – $V_D$ , and (b)  $I_D$ – $V_G$  characteristics of MOSFET's with LPD  $\mathrm{SiO}_{2-x}\mathrm{F}_x$  gate oxide. The inset in (b) shows the cross-sectional view of the fabricated device.

## II. EXPERIMENTAL

N-channel MOSFET's with aluminum gates were fabricated on 1–5  $\Omega$ ·cm, (100), p-type silicon substrates. A typical cross-sectional view of the fabricated device is shown in the inset of Fig. 1(b). The channel length (L) and channel width (Z) are 20  $\mu$ m and 942  $\mu$ m, respectively. The fabrication used conventional four-mask processes without channel implantation. 100 nm-thick LPD  $\mathrm{SiO}_{2-x}\mathrm{F}_x$  formed at 15°C was first

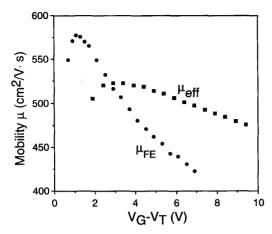

Fig. 2. Effective mobility ( $\mu_{\rm eff}$ ) and field-effect mobility ( $\mu_{\rm FE}$ ) versus  $V_G$ – $V_T$  of MOSFET's with LPD gate oxide.

used as gate insulator. Specifics concerning the deposition process of LPD oxide were the same as those in our previous works [8], [9]. Because the fluorine disappeared and the film became denser as the LPD  $SiO_{2-x}F_x$  was treated at a temperature over 700°C [8], the processing temperature had to be carefully controlled to avoid affecting the LPD oxide. So in our MOSFET processes, thermal diffusion of phosphorus for the source and drain regions was adopted and performed before gate oxide deposition. In addition, we adopted an aluminum gate to replace the polycrystalline silicon gate, because aluminum evaporation has hardly any thermal effect on LPD oxide. Post-metal annealing at 400°C was the only high temperature process used after LPD oxide deposition. The resulting MOSFET electrical characteristics, such as draincurrent  $(I_D)$  versus drain-voltage  $(V_D)$  or gate-voltage  $(V_G)$ were measured, and the device parameters including threshold voltage  $(V_T)$ , subthreshold swing (S), and mobility  $(\mu)$  were all analyzed. The interface state density  $(D_{it})$  was also investigated with MOS capacitors by high-frequency method [13].

## III. RESULTS AND DISCUSSION

An Auger electron spectroscopy (AES) depth-profile of LPD oxide film has revealed that fluorine is uniformly distributed in the film [14]. The mechanism of fluorine incorporation has also been proposed [14]. Fig. 1(a) shows the typical  $I_D$ - $V_D$  characteristics of our MOSFET with  $V_G$  varied in the range from 2 V to 4 V in 0.5 V steps. The  $I_D$ - $V_D$ curve exhibiting triode characteristics and current saturation phenomena well, reveals a typical drain characteristic for a long-channel MOSFET. Because there is no current flowing at  $V_G = 2$  V, we know that the  $V_T$  will be larger than 2 V. With accurate plotting of transconductance  $(g_m)$  versus  $V_G$ , the 2.1 V of  $V_T$  was obtained to confirm the above result. The fact that this value of  $V_T$  is lower than the 4 V of in other studies [2] indicates that there are fewer fixed oxide charges contained in the LPD oxide. The typical  $I_D$ - $V_G$  characteristics of our MOSFET with  $V_D = 0.05 \text{ V}$  and 5 V, are also shown in

TABLE I SUMMARIES OF DEVICE PERFORMANCES FOR MOSFET'S UTILIZING VARIOUS GATE OXIDE DEPOSITION METHODS

|                                                                | LPD gate<br>oxide         | O2-Ar sputter-<br>deposited gate oxide | PECVD gate<br>oxide [5]    |

|----------------------------------------------------------------|---------------------------|----------------------------------------|----------------------------|

| Gate electrode Deposition temperature Post-annealing           | Aluminum<br>20°C<br>400°C | Polysilicon<br>200°C<br>800°C          | Aluminum<br>350°C<br>400°C |

| Temperature<br>Midgap Dit (eV <sup>-1</sup> cm <sup>-2</sup> ) | 1.8 × 10 <sup>11</sup>    | 5.0 × 10 <sup>10</sup>                 | 2.7 × 10 <sup>11</sup>     |

| Threshold voltage V <sub>T</sub> (V)                           | 2                         | 4                                      | _                          |

| Subthreshold slope<br>(mV/decade)                              | 134                       | 170                                    |                            |

| Peak mobility μ <sub>FE</sub><br>(cm <sup>2</sup> /V·s)        | 580                       | 700                                    | 413                        |

Fig. 1(b), shown the drain current varies exponentially with  $V_G$  in the subthreshold region. And the curves in the subthreshold region show virtually no dependence on the drain voltage. The peak transconductance calculated at  $V_D=0.05~\rm V$  is  $3.68\times10^{-5}~\rm s$ . Moreover, the subthreshold slope calculated from the  $I_D$ - $V_G$  curve is 134 mV/decade, which reveals superior to the 170 mV/decade recorded in other studies [2]. Although above results shows that our devices exhibit worse electrical characteristics than those conventional ones with thermal oxide, they exhibit comparable performance to other low-temperature processed MOSFET's.

Since the MOSFET mobility is strongly influenced by the surface states at or near the interface and by the morphology of Si/SiO2 interface, it is essential to evaluate the mobility when investigating the interface quality. Fig. 2 shows the effective mobility ( $\mu_{\rm eff}$ ) and field-effect mobility ( $\mu_{\rm FE}$ ) versus the  $V_G$ - $V_T$ . The  $\mu_{\rm eff}$  and the  $\mu_{\rm FE}$  are given by  $\mu_{\rm eff}$  $g_D \cdot L/Z \cdot C_{ox} \cdot (V_G - V_T)$  and  $\mu_{\text{FE}} = g_m \cdot L/Z \cdot C_{ox} \cdot V_D$ , respectively, where  $q_D$  is the channel conductance,  $C_{ox}$  is the gate capacitance per unit area. The mobility curves are highly consistent with those of MOSFET's with thermal gate oxide [15]. The peak  $\mu_{\text{eff}}$  is 525 cm<sup>2</sup>/V · s, while the peak  $\mu_{\rm FE}$  is 580 cm<sup>2</sup>/V · s. The  $\mu_{\rm FE}$  is lower than  $\mu_{\rm eff}$  over almost the entire gate voltage region, because the derivation of  $\mu_{\rm FE}$ neglects the dependence of gate voltage [16]. The fact that mobility decreasing with gate voltage can be attributed to the enhanced surface roughness scattering with increased gate voltage [15]. In comparison with other words, our peak  $\mu_{\rm FE}$  is larger than 413 cm<sup>2</sup>/V · s [5] but is less than 700 cm<sup>2</sup>/V · s [2] of other works. These results show that the interface properties of Si/LPD  $SiO_{2-x}F_x$  are superior to those of Si/PECVD  $SiO_2$ but inferior to those of Si/O<sub>2</sub>-Ar sputter-deposited oxide. As compared in Table I, the  $D_{it}$  of our device is lower than that of sputtered oxide device, but higher than that of PECVD oxide device. The least  $D_{it}$  for the sputter-oxide device may be attributed to a high-temperature annealing, which was performed at 800°C after oxide deposition. And our devices having less  $D_{it}$  may be due to fluorine incorporation. It is because fluorine can passivate some interfacial dangling bonds, as well as remove some weak Si-Si or Si-O bonds, via Si-F formation [10]. However, it is impossible to directly prove the fact because we can not prepare any LPD oxide without fluorine incorporation. It is expected that the reliability of our devices will show better than other devices without fluorinated gate insulator. The study has been in progress.

### IV. CONCLUSION

We have applied a novel room-temperature LPD  ${\rm SiO}_{2-x}F_x$  to low-temperature processed MOSFET without high-temperature annealing. Its  $I_D - V_D$  and  $I_D - V_G$  curves exhibit excellent triode-like characteristics and subthreshold characteristics, respectively. All the device parameters were compared well to those of other low-temperature processed MOSFET's. These results reveal the great possibility of applying LPD  ${\rm SiO}_{2-x}F_x$  as a gate insulator in low-temperature processed MOSFET's in the future.

### REFERENCES

- D. A. Baglee, "A review of recent developments in thin gate dielectric for VLSI," J. Vac. Sci. Technol. A, vol. 4, p. 1002, 1986.

- [2] S. Suyama, A. Okamoto, and T. Serikawa, "Electrical characteristics of MOSFET's utilizing oxygen-argon sputter-deposited gate oxide films," *IEEE Trans. Electron Devices*, vol. ED-34, no. 10, p. 2124, 1987.

- [3] J. Stasiak, J. Batey, and E. Tierney, "Fabrication of thin gate MOSFET's using low-temperature plasma-enhanced chemical-vapor-deposited SiO<sub>2</sub>," *IEEE Trans. Electron Devices.*, vol. ED-34, no. 11, p. 2367, 1987.

- [4] J. Lee, I.-C. Chen, and C. Hu, "Electrical characteristics of MOSFET's using low-temperature chemical-vapor-deposited oxide," *IEEE Electron Device Lett.*, vol. 9, no. 7, p. 324, 1988.

- [5] J. Stasiak, J. Batey, E. Tierney, and J. Li, "High-quality deposited gate oxide MOSFET's and the importance of surface preparation," *IEEE Electron Device Lett.*, vol. 10, no. 6, p. 245, 1989.

- Electron Device Lett., vol. 10, no. 6, p. 245, 1989.

K. Yamabe and K. Taniguchi, "Time-dependent dielectric breakdown of thin thermally grown SiO<sub>2</sub> films," *IEEE Trans. Electron Devices.*, vol. ED-32, no. 2, p. 423, 1985.

- [7] H. Abe, F. Kiyosumi, K. Yoshioka, and M. Ino, "Analysis of defects in thin SiO<sub>2</sub> thermally grown on Si substrate," in *IEDM Tech. Dig.*, 1985, p. 372.

- p. 372.

[8] C. F. Yeh, S. S. Lin, C. L. Chern, and Y. C. Yang, "Novel technique for SiO<sub>2</sub> formed by liquid-phase deposition for low-temperature processed polysilicon TFT," *IEEE Electron Device Lett.*, vol. 14, p. 403, 1993.

- [9] C. F. Yeh, S. S. Lin, T. Z. Yang, C. L. Chern, and Y. C. Yang, "Performance and off-state current mechanisms of low-temperature processed polysilicon thin-film transistors with liquid phase deposited SiO<sub>2</sub> gate insulator," *IEEE Trans. Electron Devices*, vol. 41, p. 173, 1994

- [10] D. N. Kouvatsos, F. A. Stevie, and R. J. Jaccodine, "Interface state density reduction and effect of oxidation temperature on fluorine incorporation and profiling for fluorinated metal oxide semiconductor capacitors," J. Electrochem. Soc., vol. 140, p. 1160, 1993.

[11] P. J. Wright and K. C. Saraswat, "The effect of fluorine in silicon dioxide

- [11] P. J. Wright and K. C. Saraswat, "The effect of fluorine in silicon dioxide gate dielectric," *IEEE Electron Devices*, vol. 36, p. 879, 1989.

[12] Y. Nishioka, Y. Ohji, K. Ohyu, T. P. Ma, K. Mukai, and N. Natuaki,

- [12] Y. Nishioka, Y. Ohji, K. Ohyu, T. P. Ma, K. Mukai, and N. Natuaki, "Hot-electron hardened Si-gate MOSFET utilizing F implantation," *IEEE Electron Device Lett.*, vol. 10, p. 141, 1989.

- [13] E. H. Nicollian and J. R. Brews, MOS (Metal Oxide Semiconductor)

Physics and Technology New York: John Wiley, 1982.

- Physics and Technology. New York: John Wiley, 1982.

[14] C. F. Yeh, C. L. Chen, and G. H. Lin, "The Physicochemical properties and growth mechanism of oxide (SiO<sub>2-x</sub>F<sub>x</sub>) by liquid phase deposition with H<sub>2</sub>O addition only," J. Electrochem. Soc., vol. 141, p. 3177, 1994.

[15] S. C. Sun and J. D. Plummer, "Electron mobility in inversion and

- [15] S. C. Sun and J. D. Plummer, "Electron mobility in inversion and accumulation layers on thermally oxidized silicon surface," *IEEE Trans. Electron Devices*, vol. ED-27, no. 8, p. 1497, 1980.

- [16] J. S. Kang and D. K. Schroder, "Effective and field-effect mobilities in Si MOSFET's," Solid-State Electron., vol. 32, no. 8, p. 679, 1989.