# Enhanced H<sub>2</sub>-Plasma Effects on Polysilicon Thin-Film Transistors with Thin ONO Gate-Dielectrics

Chien Kuo Yang, Student Member, IEEE, Chung Len Lee, Senior Member, IEEE, and Tan Fu Lei

Abstract—This letter reports that passivation effects of the  $\rm H_2$ -plasma on the polysilicon thin-film transistors (TFT's) were greatly enhanced if the TFT's have a thin  $\rm Si_3N_4$  film on their gate-dielectrics. Compared to the conventional devices with only the  $\rm SiO_2$  gate dielectric, the TFT's with  $\rm Si_3N_4$  have much more improvement on their subthreshold swing and field-effect mobility after  $\rm H_2$ -plasma treatment.

#### I. INTRODUCTION

T<sub>2</sub>-PLASMA passivation has become a well-accepted method to improve the electrical properties of polysilicon thin-film transistors [1], [2]. Recently, there has been increasing interest in studying the mechanism of H2-plasma passivation [2]-[5]. In addition, how to enhance the passivation effect of H2-plasma on TFT's has also become an important issue [6], [7]. Although it had been reported that H<sub>2</sub>-plasma had a better passivation effect on polysilicon TFT's with gate oxynitrides formed by NH<sub>3</sub> [7], the reason of the enhanced hydrogenation has not been clearly found yet. Also the stacked SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> (ONO) structure has been proposed to reduce the gate leakage [8]. It had been confirmed that an LPCVD silicon nitride layer could act as an effective barrier against hydrogen diffusion [4]. Therefore, it is interesting to study the H<sub>2</sub>-plasma effects on the polysilicon TFT's without and with an thin Si<sub>3</sub>N<sub>4</sub> film on their gatedielectrics. In this work, it is found that the H<sub>2</sub>-plasma passivation effect is dramatically enhanced on the TFT's with the thin ONO gate dielectric as compared with the devices with only the thermally grown thin gate-oxide.

#### II. EXPERIMENTAL PROCEDURES

The polysilicon TFT's were fabricated on thermally oxidized silicon wafers. A 60 nm amorphous-silicon film was initially deposited by an LPCVD system at 550°C and then annealed at 600°C for 24 hr. The active regions were defined by plasma etching. After a 19.2 nm bottom oxide was grown in wet  $\rm O_2$  at 850°C, a 10 nm  $\rm Si_3N_4$  film was deposited by a conventional LPCVD reactor with the source gases of  $\rm SiH_2Cl_2$  and  $\rm NH_3$  at 750°C, followed by reoxidation in wet  $\rm O_2$  at

Manuscript received November 15, 1994; revised January 20, 1995. This work was supported by the National Science Council of the Republic of China through Contract NSC-83-0404-E009-017

The authors are with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, and National Nano Device Laboratory, Hsinchu 300, Taiwan, R.O.C.

IEEE Log Number 9411768.

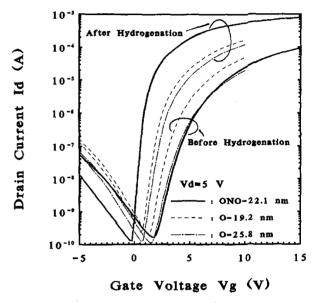

Fig. 1.  $I_d$ - $V_g$  characteristics at  $V_d=5$  V of the TFT's without and with a 60 min H<sub>2</sub>-plasma treatment. All devices were measured at the dimension of W/L =  $40\,\mu\mathrm{m}/10\,\mu\mathrm{m}$ .

$850^{\circ}\text{C}$  for 5 min. The equivalent oxide thickness of the ONO film is 22.1 nm. Then, another 300 nm polysilicon film was deposited and patterned to be the gate of the device. After the dielectrics above source/drain regions were stripped off, a self-aligned POCl<sub>3</sub> doping was performed at  $850^{\circ}\text{C}$  to form the source, drain, and gate electrodes. For comparison, devices with only SiO<sub>2</sub> as the gate dielectric of the thicknesses of 19.2 and 25.8 nm were also made. The gate-oxides were also thermally grown in wet O<sub>2</sub> at  $850^{\circ}\text{C}$ . After contact holes were opened, Al was deposited and then patterned. Finally, plasma hydrogenation was applied with an H<sub>2</sub> and N<sub>2</sub> gas mixture in a commercial 13.5-MHz parallel-plate plasma reactor at 300°C for 20–80 min.

## III. RESULTS AND DISCUSSIONS

Fig. 1 shows the typical  $I_d$ - $V_g$  characteristics of the TFT's with and without the H<sub>2</sub>-plasma treatment. Table I compiles the values of the subthreshold swing S, the threshold voltage  $V_{\rm th}$ , the field effect mobility  $\mu$ , and the effective trap density  $N_t$  [9], derived from the corresponding devices of Fig. 1 at  $V_d=0.1$  V. It is seen that for the device with the ONO

TABLE I The Values of  $S, V_{\mathrm{th}}, \mu,$  and  $N_t$  of the Polysilicon TFT's with Different Gate-Dielectrics

| Conditions  | S (mV/decade)                   |                | Vth (V)            |                  | μ (cm <sup>2</sup> / Vsec)      |                  | Nt (x10 <sup>12</sup> cm <sup>2</sup> eV <sup>-1</sup> ) |                |

|-------------|---------------------------------|----------------|--------------------|------------------|---------------------------------|------------------|----------------------------------------------------------|----------------|

|             | before<br>H <sub>2</sub> -plasi | after<br>malhr | before<br>Hg-plass | after<br>na 1 hr | before<br>H <sub>2</sub> -plass | after<br>ma 1 hr | before<br>H <sub>2</sub> -plas                           | after<br>malhr |

| ONO-22.1 nm | 642                             | 187            | 4.75               | 0.47             | 4.6                             | 32.2             | 9.53                                                     | 2.08           |

| O -19.2 nm  | 495                             | 302            | 3.46               | 1.90             | 4.5                             | 9.3              | 8.22                                                     | 4.58           |

| O -25.8 nm  | 631                             | 397            | 4.62               | 2.33             | 3.3                             | 10.1             | 8.03                                                     | 4.77           |

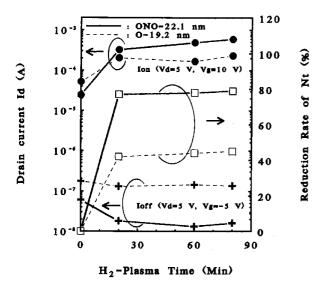

Fig. 2. The ON- and OFF-state drain currents and the  $N_t$  reduction rate as a function of the  $\rm H_2$ -plasma-exposure time for the devices with different gate-dielectrics.

gate-dielectric, the H<sub>2</sub>-plasma effect was drastically enhanced, especially on its improvement of S and  $\mu$ . Fig. 2 shows the ON- and OFF-state drain currents and the  $N_t$  reduction rate as a function of the H<sub>2</sub>-plasma-exposure time for the devices with different gate-dielectrics, respectively. It is found that the ONO device had a much better effect in responding to the H<sub>2</sub>-plasma treatment. The drivability and leakage of the ONO devices were more effectively improved. Moreover, the  $N_t$ reduction rate of the ONO device was also considerably larger than those without a thin Si<sub>3</sub>N<sub>4</sub> film on their gate-dielectrics. Fig. 2 also shows that after a 20 min H<sub>2</sub>-plasma treatment, the improvements of all the devices almost reached a saturation state and further increasing the H<sub>2</sub>-plasma-exposure time did not improve the devices too much. Two possible mechanisms could be used to explain the above results. One is that for the ONO device, the Si<sub>3</sub>N<sub>4</sub> film prevented hydrogen out-diffusion during the plasma treatment. This made the hydrogenation effect more effective. On the other hand, since it is generally recognized that the strain-bond band-tail states influence the field effect mobility [2], the large improvement on  $\mu$  suggests that the thin Si<sub>3</sub>N<sub>4</sub> in the ONO gate-dielectric played an important role in reducing the band-tail states during the  $\rm H_2$ -plasma. Hence, the other possible mechanism is the relaxation of the strained bonds due to the existence of  $\rm Si_3N_4$ . It is speculated that the mechanical stress [10], [11] caused by the existence of  $\rm Si_3N_4$  might be helpful to break the strained bonds at the poly- $\rm Si/SiO_2$  interface and in the polysilicon film to relax the network. This speculation can be supported further by the fact that for the ONO devices, they had higher  $N_t$  before hydrogenation as shown in Table I. During hydrogenation, the  $\rm H_2$ -plasma passivated the dangling bonds and relaxed the silicon network more effectively.

## IV. CONCLUSION

In this letter, it is reported that the effect of the  $H_2$ -plasma hydrogenation on improving the electrical characteristics of the polysilicon TFT's is greatly enhanced if the TFT's have a thin  $\mathrm{Si}_3\mathrm{N}_4$  film on their gate dielectrics. Compared to the TFT's with only the  $\mathrm{SiO}_2$  gate dielectric, the ONO device has a larger  $N_t$  before hydrogenation but a much more improved  $\mu$  after hydrogenation. This experimental result suggests that the deposited thin  $\mathrm{Si}_3\mathrm{N}_4$  film plays a very important role in further reducing the strained bonds of the active layer during the  $\mathrm{H}_2$ -plasma treatment.

## REFERENCES

- [1] M. Rodder and S. Aur, "Utilization of plasma hydrogenation in stacked SRAM's with poly-Si PMOSFET's and bulk-Si NMOSFET's," *IEEE Electron Device Lett.*, vol. 12, no. 5, pp. 233–235, 1991.

- [2] I. W. Wu, T. Y. Huang, W. B. Jackson, A. G. Lewis, and A. Chiang, "Passivation kinetics of two types of defects in polysilicon TFT by plasma hydrogenation," *IEEE Electron Device Lett.*, vol. 12, no. 4, pp. 181–183, 1991.

- [3] U. Mitra, B. Rossi, and B. Khan, "Mechanism of plasma hydrogenation of polysilicon thin film transistors," *J. Electrochem. Soc.*, vol. 138, no. 11, pp. 3420–3424, Nov. 1991.

- [4] W. B. Jackson, N. M. Johnson, C. C. Tsai, I. -W. Wu, A. Chiang, and D. Smith, "Hydrogen diffusion in polycrystalline silicon thin films," Appl. Phys. Lett., vol. 61, no. 14, pp. 1670–1672, 1992.

- [5] Y. S. Kim, K. Y. Choi, S. K. Lee, B. H. Min, and M. K. Han, "Structural dimension effects of plasma hydrogenation on low-temperature poly-Si thin film transistors," *Jpn. J. Appl. Phys.*, vol. 33, pp. 649–653, 1994.

- [6] H. N. Chern, C. L. Lee, and T. F. Lei, "H<sub>2</sub>/O<sub>2</sub> plasma on polysilicon thin film transistor," *IEEE Electron Device Lett.*, vol. 14, no. 5, pp. 115-117, 1993.

- [7] C. K. Yang, T. F. Lei, and C. L. Lee, "The combined effects of low pressure NH<sub>3</sub>-annealing and H<sub>2</sub> plasma hydrogenation on polysilicon thin-film transistors," *IEEE Electron Device Lett.*, vol. 15, no. 10, pp. 389–390, 1994.

- [8] N. Lifshitz and S. Luryi, "Enhanced channel mobility in polysilicon thin film transistors," *IEEE Electron Device Lett.*, vol. 15, no. 8, pp. 274–276, 1994.

- [9] M. Rodder and D. A. Antoniadis, "Comparison of different techniques for passivation of small-grain polycrystalline-Si MOSFET's," *IEEE Electron Device Lett.*, vol. EDL-6, no. 11, pp. 570-572, 1985.

- [10] S. Isomae, "Stress in silicon at Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> film edges and viscoelastic behavior of SiO<sub>2</sub> films," *J. Appl. Phys.*, vol. 57, no. 2, pp. 217–223, 1085

- [11] R. P. Vasquez and A. Madhukar, "Strain-dependent defect formation kinetics and a correlation between flatband voltage and nitrogen distribution in thermally nitrided SiO<sub>x</sub>N<sub>y</sub>/Si structures," Appl. Phys. Lett., vol. 47, pp. 998–1000, 1985.