# Direct Formation of Wafer Scale Graphene Thin Layers on Insulating Substrates by Chemical Vapor Deposition

Ching-Yuan Su,<sup>†</sup> Ang-Yu Lu,<sup>†,‡</sup> Chih-Yu Wu,<sup>†</sup> Yi-Te Li,<sup>§</sup> Keng-Ku Liu,<sup>†</sup> Wenjing Zhang,<sup>†</sup> Shi-Yen Lin,<sup>†</sup> Zheng-Yu Juang,<sup>†</sup> Yuan-Liang Zhong,<sup>§</sup> Fu-Rong Chen,<sup>‡</sup> and Lain-Jong Li\*,<sup>†,†</sup>

Supporting Information

**ABSTRACT:** Direct formation of high-quality and wafer scale graphene thin layers on insulating gate dielectrics such as  $\mathrm{SiO}_2$  is emergent for graphene electronics using Si-wafer compatible fabrication. Here, we report that in a chemical vapor deposition process the carbon species dissociated on Cu surfaces not only result in graphene layers on top of the catalytic Cu thin films but also diffuse through Cu grain boundaries to the interface between Cu and underlying dielectrics. Optimization of the process parameters leads to a continuous and large-area graphene thin layers directly formed on top of the dielectrics. The bottom-gated transistor characteristics for the graphene films

have shown quite comparable carrier mobility compared to the top-layer graphene. The proposed method allows us to achieve wafer-sized graphene on versatile insulating substrates without the need of graphene transfer.

KEYWORDS: Graphene, chemical vapor deposition, Raman spectroscopy, transparent conductive film, graphitization

$\mathbf{C}$  ingle- and few-layer graphene films $^{1-4}$  are promising materials for post-silicon electronics because of their high carrier mobility and great potential of integrating bottom-up nanomaterial synthesis with top-down lithographic fabrication at wafer scale.<sup>5</sup> Many approaches have been used to obtain graphene layers, including mechanical and liquid phase exfoliation from graphite, 1,6,7 epitaxial growth on crystalline substrate, 8-11 and reduction from graphene oxides. 12-17 Recent developments in chemical vapor deposition (CVD) have allowed successful production of large scale graphene layers on catalytic metal substrates,  $^{18-25}$  greatly encouraging the utilizing of graphene in practical fabrications. To date, large area CVD graphene has all been produced on metal substrates and it is necessary to transfer the as-grown graphene onto desired substrates. In such a wet-transfer process, for example, graphene films are capped with a supporting polymer layer, followed by metal substrate etching and polymer/ graphene transfer to receiving substrates. The wet-transfer process is perhaps unfavorable in current Si-wafer fabrication processes. Hence, many efforts have been made to avoid the wet-transfer processes. Ismach et al. reported that the chemical vapor deposited graphene on Cu layer can be directly transferred onto underlying dielectrics surfaces by dewetting and evaporating the Cu layers with an extended period of thermal annealing. <sup>26</sup> Levendorf et al. developed a method to allow the patterned graphene on Cu to directly settle on dielectrics after etching the metal layers underneath graphene. <sup>27</sup> However, these transfer processes may be only feasible for the graphene with small lateral sizes. Also, some additional mechanical stress on graphene is

anticipated during the transfer process. Recently, organic polymers coated on insulators have been thermally converted to few-layer graphene by a Ni capping layer. 28 Lee et al. have observed that graphene layers can be formed at the Ni and SiO2 interface using plasma-enhanced CVD although the interface graphene is thick and defective.<sup>29</sup> It has been shown that the formation of graphene on Ni is due to the segregation or precipitation process of the carbon species dissolved in Ni.<sup>30</sup> Due to this effect, the carbon precipitation is a nonequilibrium process and it may be challenging to get uniform graphene films by using Ni as a catalytic metal. Here we report that high-quality and uniform wafer scale graphene thin layers can be directly formed at the interface between Cu and insulators using a CVD method. The key idea is to deposit a thin Cu catalytic layer ( $\sim$ 300 nm thick) on the target insulating substrates such as SiO<sub>2</sub> and quartz. By controlling the synthetic parameters, the carbon species dissociated from methane diffuse through the Cu grain boundaries to the Cu-substrate interface. Moreover, to avoid the dewetting or evaporation of Cu, our CVD process temperature is set at 900 °C, significantly lower than the 1000 °C used in other reports. Most importantly, in addition to the structural characterization data such as Raman spectra and STM images, we have also reported the electrical characteristics for the bottom-layer graphene.

Received: April 23, 2011

Revised: August 1, 2011

Published: August 11, 2011

<sup>&</sup>lt;sup>†</sup>Research Center for Applied Sciences, Academia Sinica, Taipei, 11529, Taiwan

<sup>&</sup>lt;sup>†</sup>Department of Engineering and System Science, National Tsing Hua University, 101, Section 2 Kuang Fu Road, Hsinchu 300, Taiwan

<sup>&</sup>lt;sup>§</sup>Department of Physics and Center for Nanotechnology, Chung Yuan Christian University, Chung-Li 32023, Taiwan

Department of Photonics, National Chiao Tung University, HsinChu 300, Taiwan

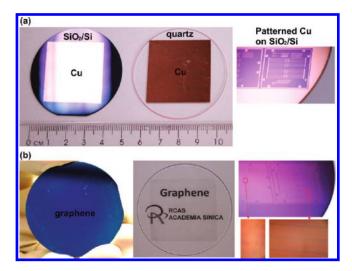

**Figure 1.** (a) Photos of 2 in. insulating substrates: Cu on  $SiO_2$  (300 nm)/Si, Cu on quartz, and patterned Cu on  $SiO_2$  (300 nm)/Si. (b) Photos of the asgrown bottom layer graphene on the corresponding substrates shown in (a).

This work may stimulate further developments in utilizing graphene for silicon-wafer compatible production.

**Results and Discussion.** It is known that the methane molecules dissociate on Cu surfaces at high temperature. 22,30,31 In this report, we observe that the carbon species not only result in graphene layers on top of the catalytic Cu thin films (top layer graphene) but also diffuse though Cu grain boundaries and directly form a graphene layer at the Cu-dielectric interface (bottom layer graphene). A conventional quartz tubular furnace was adopted to synthesize the bottom layer graphene films. To be able to directly form a graphene layer on an insulating substrate (SiO<sub>2</sub>/Si, quartz or sapphire), a 300 nm Cu thin film layer was deposited on the insulating substrate and methane was used as the carbon source. After the substrate was loaded into the furnace, it was heated to 750 °C in a hydrogen atmosphere (H<sub>2</sub>, 415 sccm; Ar, 400 sccm) at 500 Torr followed by thermal annealing at the same temperature for 25 min to remove native oxides on Cu. The furnace was then heated to the process temperature 900 °C in a pure H<sub>2</sub> gas environment (H<sub>2</sub>, 15 sccm; pressure, 800 mTorr). After the temperature reached 900 °C, the gas condition was switched to a methane/hydrogen gas mixture ( $CH_4 =$ 75 sccm and  $H_2 = 15$  sccm) for 5 min at 800 mTorr to grow graphene layers. During the cooling stage, the furnace was cooled to room temperature with a cooling rate  $\sim$ 20 °C/min, where the gas condition was maintained as the same from the beginning of growth stage to the end of cooling stage. By contrast to the conventional graphene growth temperature 1000  $^{\circ}$ C on top of Cu foils,  $^{22}$  we used a relatively lower process temperature (900  $^{\circ}$ C) to avoid the evaporation and dewetting of Cu film as observed by Ismach et al. 26 Note that growth pressure is preferably not lower than 800 mTorr. Otherwise, Cu dewetting becomes pronounced due to the fast evaporation of Cu. Meanwhile, the high-temperature process 1000 °C in a H<sub>2</sub> environment shall largely degrade the quality of underlying SiO2, leading to large gate leakage current if the SiO<sub>2</sub> is used directly as a gate dielectric material. With the optimized CVD synthetic condition, the bottom layer graphene can be continuous in a wafer scale.

Figure 1a shows the photos of several 2 in. substrates prepared for bottom layer graphene growth, including Cu on  $SiO_2$  (300 nm)/Si, Cu on quartz, and patterned Cu on  $SiO_2$  (300 nm)/Si. All these wafers were subjected to the synthetic condition mentioned above for growing bottom layer graphene. Figure 1b demonstrates the

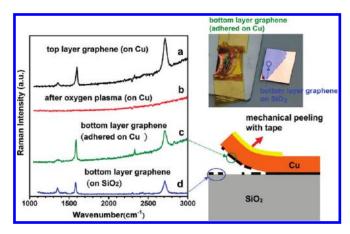

**Figure 2.** The Raman spectra for (a) as-grown top layer graphene on Cu and (b) the sample after oxygen plasma stripping, where all the top layer graphene is removed. After mechanical peeling of the Cu layer, some bottom layer graphene can be found on Cu as shown in (c), and the rest of the film stays on SiO<sub>2</sub> surfaces as evidenced by Raman curve (d).

photos of the as-grown bottom layer graphene after removing the top layer graphene by oxygen plasma (power, 60 W for 6 min) and the Cu layers by Fe(NO<sub>3</sub>)<sub>3</sub> wet etching. These photos in Figure 1 demonstrate that our growth process is able to directly form a large area and continuous thin graphene layers on top of arbitrary insulating substrates. Figure 1 shows that patterned graphene is also obtainable if patterned Cu films are used for bottom layer graphene growth. Raman measurement has been performed to further confirm that the bottom layer graphene we observed in Figure 1 was not unintentionally transferred (or settled down) from the top layer graphene. The Raman curve a in Figure 2 was taken from the asgrown top layer graphene on Cu, where G ( $\sim$ 1598 cm<sup>-1</sup>) and 2D  $(\sim 2712~{\rm cm}^{-1})$  bands were clearly observed. After oxygen plasma treatment, all the Raman features for graphene vanished (curve b), demonstrating that top layer graphene was totally removed. The presence of bottom layer graphene actually weakens the interfacial adhesion between Cu and underlying SiO2; hence, mechanical peeling of the Cu layer can be done using adhesive tapes. We observe that part of the bottom layer graphene is lifted by Cu film (Raman curve c) and the rest of graphene stays on SiO<sub>2</sub> substrates (Raman curve d) as shown in the photo and schematic illustration in Figure 2. These results confirm the formation of graphene layer at the Cu-insulator interface. Figure S1 in the Supporting Information further shows that the growth of graphene on several other insulators such as sapphire and ST-cut quartz is feasible.

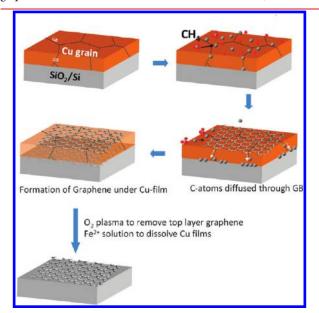

Figure 3 schematically illustrates the growth mechanism of the graphene layers in between the catalytic Cu thin film and underlying insulating substrates. The methane molecules are dissociated into carbon species on the Cu surface. It is known that the carbon atoms possess a very low solubility in Cu; hence, they migrate on Cu surfaces to form large-area and continuous thin graphene films.<sup>22</sup> Meanwhile, some of these carbon species can better diffuse through the Cu grain boundaries and reach the interface between the Cu and underlying insulators. We note that there is no graphene growth underlying Cu film if methane is absent during the growth process, suggesting the bottom layer graphene formation is related to the methane precursors rather than other possible carbon impurities. Also, 300 nm of Cu thin film is close to the optimized condition for bottom layer graphene growth. Decrease in Cu thickness shall lead to pronounced dewetting of Cu from insulators as observed by Ismach et al.<sup>26</sup> even at 900 °C. Further increase in Cu film thickness

results in poor continuity of the bottom layer graphene or even no graphene formation at the Cu-insulator interface, which is

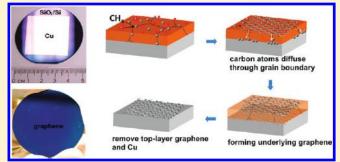

**Figure 3.** The schematic illustration of the growth. Step 1: Formation of Cu grains after thermal annealing. Step2: The  $\mathrm{CH_4}$  precursors dissociate into carbon species and migrate on Cu surfaces, where some of the carbon species diffuse downward through Cu grain boundary (GB). Step 3: The graphene layer formed on the Cu surface; meanwhile, the carbon atoms continue to diffuse through Cu GB and segregate at the Cu—insulator interface. Step 4: The graphitization of carbon atoms underlying Cu film leads to the formation of bottom layer graphene. Step 5: The large-area and continues graphene layers can be obtained directly on substrate after removing the top layer graphene, followed by wet-etching of Cu thin film.

expected due to the length increase of carbon diffusion path from top Cu surface to the bottom interface. This observation also suggests that the formation mechanism of the bottom layer graphene underlying Cu metals is likely different from the carbon dissolution—surface segregation mechanism proposed for graphene growth on Ni surfaces. <sup>21,30</sup>

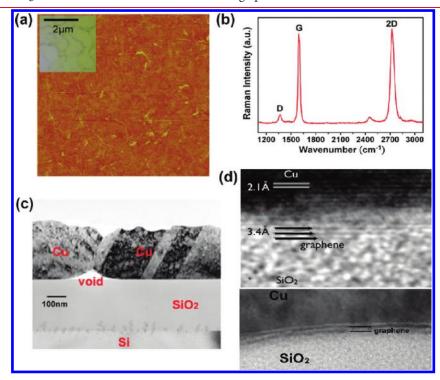

Figure 4a shows the typical atomic force microscope (AFM) image for the bottom layer graphene grown on a SiO<sub>2</sub>/Si substrate. It is clearly seen that the SiO<sub>2</sub> substrate is fully covered with the graphene layers. We show in Figure S2 (Supporting Information) the effect of growth time on the size of the obtained bottom layer graphene, where the nucleation process occurs in the beginning, followed by the graphene domain growth. We find that once our process parameters are adjusted to get large-area continuous bottom layer graphene, the film is always few-layered. The growth of bottom layer graphene seems to be not selflimited at the monolayer. Actually Yan et al. have also observed the breaking of self-limit growth on Cu surfaces, where the graphene domain boundaries and impurities in the first grown graphene layer could serve as nucleation sites for growth of additional graphene layers on top of the first layer. 24 We believe this is the main reason that we can grow wafer scale few-layer bottom graphene. Figure S3 in the Supporting Information shows that the film thickness obtained from the AFM crosssection measurements is around 1.34 nm, suggesting that the bottom layer graphene is thin (about 2 to 3 layered). It is also noted that a wrinkle-like structure exists in the AFM image (Figure 4a), where the domain size surrounded by the wrinkles is similar to the Cu grain size as revealed in the optical micrograph (Figure 4a inset). Figure 4c displays the low magnification TEM cross section of the Cu/SiO2 after graphene growth, where we clearly observe the void formed between two Cu grains. The graphene and excess carbon materials may accumulate at the

Figure 4. (a) Typical AFM image for the bottom layer graphene grown on a  $SiO_2/Si$ . (Insert) Optical micrograph of the Cu layer after graphene growth. Note that graphene is not visible but Cu grains can be identified. (b) Raman spectrum (excited by 473 nm laser) for the bottom layer graphene, where D, G, and 2D bands are indicated in the figure. (c) Low-magnification and (d) high-magnification TEM for the Cu—graphene— $SiO_2$  cross section.

void area during the growth and Cu etching process. Meanwhile, the channels between Cu grains, which may be the major C diffusion routes, are also observed in Figure 4c. Figure 4d shows the high magnification TEM image for the Cu-graphene-SiO<sub>2</sub> interface, where we can identify the presence of trilayer and bilayer graphene. This is the direct evidence for bottom layer graphene at the interface between copper and silicon dioxide. Figure S4 in the Supporting Information displays the scanning tunneling microscopy (STM) image for the bottom layer graphene on SiO<sub>2</sub>/Si. The STM measurement was carried out in a Veeco STM base operated with the constant current mode in ambient condition. We can see hexagonal carbon lattice in most of the area. Occasionally, the A-B stacked (i.e., Bernal stacked) bilayer graphene can be observed as indicated by a circle, where the atomic configuration was schematically shown in the inset.<sup>3</sup> It is noteworthy that not all the area shows a clear A-B stacking feature in STM, suggesting other stacking configurations also exist. Figure 4b displays the typical Raman spectrum (excited by 473 nm laser) for the bottom layer graphene. The graphene sheet exhibits an intense G band at around 1590 cm<sup>-1</sup> and a sharp 2D band at around 2720 cm<sup>-1</sup>, suggesting that the bottom layer graphene is highly graphitized, which is consistent with the STM observation in Figure S4, Supporting Information. Note that there is still a weak D band observed in the Raman spectrum. Figure S5a in the Supporting Information shows the Raman map constructed by plotting the intensity ratio of 2D and G band, I(2D)/I(G), which has been used to indicate the number of layers for CVD graphene. 21 The Raman I(2D)/I(G) mapping consistently suggests that the bottom layer graphene is thin and continuous, likely ranging from two to three layers. One may be interested in comparing the top and bottom layer graphene, and we show in Figure S5b (Supporting Information) the Raman spectra for both the top and the bottom layer graphene obtained from our optimized reaction process (for bottom layer graphene). In brief, both layers similarly exhibit a small D band, which is likely unavoidable due to the high CH<sub>4</sub>/H<sub>2</sub> gas ratio and lower growth temperature (900 °C) optimized for obtaining large-area bottom graphene. To understand more about the growth behaviors of bottom layer graphene, some systematic investigations on growth parameters, such as the growth temperature and the thickness of Cu thin film, have been performed (see Figure S6, Supporting Information, for the Raman results). In brief, lower growth temperature (e.g., 850 °C) was not able to form a continuous film underlying Cu and the Raman D band of the film is high, likely due to the poor graphitization at low temperature. When the temperature is higher than 950 °C, the defect level of the film is also high. This could be due to the segregation of carbon species to the Cu-insulator interface being faster than the graphitization.

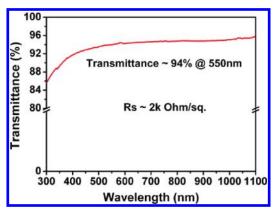

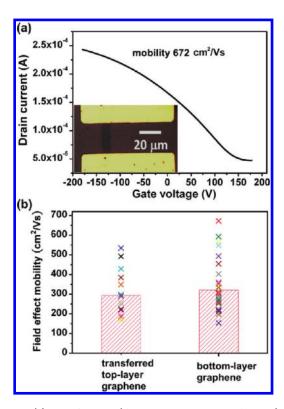

Figure 5 shows the optical measurement results for the bottom layer graphene directly grown on quartz. It has been reported that one layer graphene absorbs  $\sim\!2.3\%$  of light.  $^{33}$  The bottom layer graphene absorbs about 5.2% of light, which consistently suggests that the graphene layer we obtained is on average about two layered. The sheet resistance  $(R_{\rm s})$  data obtained in a four-point probe system for our bottom-layer graphene is  $\sim\!\!2~{\rm k}\Omega/{\rm sq}$ . To evaluate the electrical performance of these graphene sheets, the bottom layer graphene on  ${\rm SiO_2/Si}$  was patterned into a strip with the width around  $10~\mu{\rm m}$  using conventional photolithography. The bottom-gate operated transistors were fabricated by evaporating Au electrodes directly on top of the patterned graphene. Figure 6a demonstrates the transfer curve (drain current  $I_{\rm d}$  vs gate voltage  $V_{\rm g}$ ) for the device prepared.

Figure 5. The optical transmittance for a bottom layer graphene grown on a 2 in. quartz substrate. The sheet resistance of as-grown bottom layer graphene is  $\sim 2 \ k\Omega/\text{sq}$  (with  $\sim 94\%$  transmittance). The inset shows that the as-grown wafer scale graphene film is conductive.

**Figure 6.** (a) Transfer curve (drain current  $I_{\rm d}$  vs gate voltage  $V_{\rm g}$ ) for a device prepared from a patterned bottom layer graphene film. Inset shows the photograph of the device. (b) Statistical field-effect mobility data for the devices made from top layer graphene (process condition was separately optimized for single-layer graphene on Cu and then transferred onto SiO<sub>2</sub>/Si for device fabrication) and bottom layer graphene (as discussed in text). The bar chart with red-shaded box shows the average value of mobility for transferred top-layer graphene (17 devices tested) and bottom-layer graphene (35 devices tested).

Inset shows the top view of the device. The field-effect mobility of holes was extracted based on the slope  $\Delta I_{\rm d}/\Delta V_{\rm g}$  fitted to the linear regime of the transfer curves using the equation  $\mu=(L/WC_{\rm ox}V_{\rm d})-(\Delta I_{\rm d}/\Delta V_{\rm g})$ , where L and W are the channel length and width and  $C_{\rm ox}$  is the gate capacitance. The effective field effect mobility for the graphene device can be up to 670 cm²/( $V \cdot s$ ) in ambient. We note that the neutrality point (valley point of the transfer curve) for most

of our devices is beyond 100 V (the maxima  $V_{\rm g}$  we applied), suggesting that the graphene sheets are heavily p-doped. It is known that p-doping of graphene in ambient has been well explained by intrinsic graphene screening of charge at the graphene/SiO<sub>2</sub> substrate interface. 35,36 Ryu et al. have demonstrated that thermal annealing induces a pronounced distortion in the graphene sheet on SiO2. This structural deformation closely coupled to silicon dioxide at room temperature. When exposed to atmosphere, it greatly promotes hole doping caused by ambient O<sub>2</sub> and moisture. It is noted that our graphene was directly grown on SiO<sub>2</sub> at 900 °C; therefore, the heavy p-doping in our case is anticipated. Figure 6b compares the statistical results of field effect mobility for the devices prepared from the bottom layer graphene and those from the top layer graphene (process condition was separately optimized for single-layer graphene on Cu and typical transfer processes<sup>22</sup> were adopted to transfer top layer graphene onto SiO<sub>2</sub>/Si for device fabrication). These results show that the field effect mobility for these two types of film, i.e. single-layered top graphene and few-layered bottom graphene, are roughly comparable in our device structure. The mobility value reported here is likely limited by other factors such as photoresist residues, metal contact, or etching process.

**Conclusions.** In conclusion, we report the first direct synthesis of wafer scale graphene thin layers on arbitrary insulating substrates using a CVD method with the assistance of Cu thin film. The growth mechanism of bottom layer graphene underlying Cu has also been proposed. The sheet resistance values are obtained directly on the substrate used in CVD growth without the need of performing graphene transfer. Most importantly we have also obtained the field effect mobility for the bottom layer graphene directly using the  $SiO_2/Si$  as the bottom gate. We hope this work shall stimulate more research efforts in direct formation of graphene films on insulators for Si-wafer compatible device fabrications.

#### ASSOCIATED CONTENT

Supporting Information. Raman spectra and AFM images. This material is available free of charge via the Internet at http://pubs.acs.org

#### AUTHOR INFORMATION

## **Corresponding Author**

\*E-mail: (L. J. Li) lanceli@gate.sinica.edu.tw.

## ACKNOWLEDGMENT

C.-Y. Su and A.-Y. Lu contributed equally to this work. This research was supported by the Research Center for Applied Science, Academia Sinica (Nano program) and National Science Council Taiwan (NSC-99-2112-M-001-021-MY3 and 99-2738-M-001-001)

### **■** REFERENCES

- (1) Geim, A. K.; Novoselov, K. S. Nat. Mater. 2007, 6 (3), 183–191.

- (2) Castro Neto, A. H.; Guinea, F.; Peres, N. M. R.; Novoselov, K. S.; Geim, A. K. *Rev. Mod. Phys.* **2009**, *81* (1), 109.

- (3) Schwierz, F. Nat Nano 2010, 5 (7), 487-496.

- (4) Wilson, N. R.; Macpherson, J. V. Nat Nano 2009, 4 (8), 483-491.

- (5) Lin, Y.-M.; Dimitrakopoulos, C.; Jenkins, K. A.; Farmer, D. B.; Chiu, H.-Y.; Grill, A.; Avouris, P. *Science* **2010**, 327 (5966), 662.

- (6) Su, C.-Y.; Lu, A.-Y.; Xu, Y.; Chen, F.-R.; Khlobystov, A. N.; Li, L.-J. ACS Nano **2011**, 5 (3), 2332–2339.

- (7) Hernandez, Y.; Nicolosi, V.; Lotya, M.; Blighe, F. M.; Sun, Z.; De, S.; McGovern, I. T.; Holland, B.; Byrne, M.; Gun'Ko, Y. K.; Boland, J. J.;

Niraj, P.; Duesberg, G.; Krishnamurthy, S.; Goodhue, R.; Hutchison, J.; Scardaci, V.; Ferrari, A. C.; Coleman, J. N. *Nat. Nanotechnol.* **2008**, *3* (9), 563–568

- (8) Sutter, P. W.; Flege, J.-I.; Sutter, E. A. Nat. Mater. 2008, 7 (5), 406–411.

- (9) Berger, C.; Song, Z.; Li, X.; Wu, X.; Brown, N.; Naud, C.; Mayou, D.; Li, T.; Hass, J.; Marchenkov, A. N.; Conrad, E. H.; First, P. N.; de Heer, W. A. *Science* **2006**, *312* (5777), 1191–1196.

- (10) Emtsev, K. V.; Speck, F.; Seyller, T.; Ley, L.; Riley, J. D. *Phys. Rev. B* **2008**, *77* (15), 155303.

- (11) Hass, J.; et al. J. Phys.: Condens. Matter 2008, 20 (32), 323202.

- (12) Su, C.-Y.; Xu, Y.; Zhang, W.; Zhao, J.; Liu, A.; Tang, X.; Tsai, C.-H.; Huang, Y.; Li, L.-J. ACS Nano 2010, 4 (9), 5285–5292.

- (13) Williams, G.; Seger, B.; Kamat, P. V. ACS Nano 2008, 2 (7), 1487–1491.

- (14) Green, A. A.; Hersam, M. C. Nano Lett. 2009, 9 (12), 4031-4036.

- (15) Cote, L. J.; Kim, F.; Huang, J. J. Am. Chem. Soc. 2008, 131 (3), 1043–1049.

- (16) Li, D.; Muller, M. B.; Gilje, S.; Kaner, R. B.; Wallace, G. G. Nat. Nanotechnol. **2008**, 3 (2), 101–105.

- (17) Gao, W.; Alemany, L. B.; Ci, L.; Ajayan, P. M. Nat. Chem. 2009, 1 (5), 403–408.

- (18) Coraux, J.; NDiaye, A. T.; Busse, C.; Michely, T. Nano Lett. **2008**, 8 (2), 565–570.

- (19) Kim, K. S.; Zhao, Y.; Jang, H.; Lee, S. Y.; Kim, J. M.; Kim, K. S.; Ahn, J.-H.; Kim, P.; Choi, J.-Y.; Hong, B. H. *Nature* **2009**, 457 (7230), 706–710

- (20) Lee, Y.; Bae, S.; Jang, H.; Jang, S.; Zhu, S.-E.; Sim, S. H.; Song, Y. I.; Hong, B. H.; Ahn, J.-H. *Nano Lett.* **2010**, *10* (2), 490–493.

- (21) Reina, A.; Jia, X.; Ho, J.; Nezich, D.; Son, H.; Bulovic, V.; Dresselhaus, M. S.; Kong, J. *Nano Lett.* **2008**, *9* (1), 30–35.

- (22) Li, X.; Cai, W.; An, J.; Kim, S.; Nah, J.; Yang, D.; Piner, R.; Velamakanni, A.; Jung, I.; Tutuc, E.; Banerjee, S. K.; Colombo, L.; Ruoff, R. S. Science **2009**, 324 (5932), 1312–1314.

- (23) Lee, S.; Lee, K.; Zhong, Z. Nano Lett. 2010, 10 (11), 4702-4707.

- (24) Yan, K.; Peng, H.; Zhou, Y.; Li, H.; Liu, Z. Nano Lett. 2011, 11 (3), 1106–1110.

- (25) Sun, Z.; Yan, Z.; Yao, J.; Beitler, E.; Zhu, Y.; Tour, J. M. Nature **2010**advance online publication.

- (26) Ismach, A.; Druzgalski, C.; Penwell, S.; Schwartzberg, A.; Zheng, M.; Javey, A.; Bokor, J.; Zhang, Y. *Nano Lett.* **2010**, *10* (5), 1542–1548.

- (27) Levendorf, M. P.; Ruiz-Vargas, C. S.; Garg, S.; Park, J. Nano Lett. **2009**, 9 (12), 4479–4483.

- (28) Byun, S.-J.; Lim, H.; Shin, G.-Y.; Han, T.-H.; Oh, S. H.; Ahn, J.-H.; Choi, H. C.; Lee, T.-W. J. Phys. Chem. Lett. **2011**, 2 (5), 493–497.

- (29) Lee, C. S.; Baraton, L.; He, Z.; Maurice, J. L.; Chaigneau, M.; Pribat, D.; Cojocaru, C. S. *Proc. SPIE* **2010**, *7761*, *776*10P.

- (30) Li, X.; Cai, W.; Colombo, L.; Ruoff, R. S. Nano Lett. 2009, 9 (12), 4268–4272.

- (31) Vlassiouk, I.; Regmi, M; Fulvio, P.; Dai, S.; Datskos, P.; Eres, G.; Smirnov, S. ACS Nano **2011**, *5*, 6069–6076.

- (32) Varchon, F; Mallet, P; Magaud, L; Veuillen, J. Y. Rotational Disorder in Few-Layer Graphene Films on 6H-SiC(000–1): A Scanning Tunneling Microscopy Study. *Phys. Rev. B* **2008**, *77*, 165415.

- (33) Nair, R. R.; Blake, P.; Grigorenko, A. N.; Novoselov, K. S.; Booth, T. J.; Stauber, T.; Peres, N. M. R.; Geim, A. K. *Science* **2008**, 320 (5881), 1308.

- (34) Lee, C. W.; Weng, C.-H.; Wei, L.; Chen, Y.; Chan-Park, M. B.; Tsai, C.-H.; Leou, K.-C.; Poa, C. H. P.; Wang, J.; Li, L.-J. *J. Phys. Chem. C* **2008**, *112* (32), 12089–12091.

- (35) Shi, Y.; Dong, X.; Chen, P.; Wang, J.; Li, L.-J. Phys. Rev. B 2009, 115402.

- (36) Datta, S. S.; Strachan, D. R.; Mele, E. J.; Johnson, A. T. C. *Nano Lett.* **2009**, *9*, 7–11.

- (37) Ryu, S.; Liu, L.; Berciaud, S.; Yu, Y.-J.; Liu, H.; Kim, P.; Flynn, G. W.; Brus, L. E. *Nano Lett.* **2010**, *10*, 4944–4951.