# Mobility and oxide breakdown behavior in ultra-thin oxide with atomically smooth interface

Y. C. Cheng, W. J. Chen, B. C. Lin, C. Tsai, and Albert Chin

Dept. Of Electronics Eng., National Chiao Tung Univ., Hsinchu, Taiwan

<sup>1</sup>Dept. Of Mechanical Materials Eng., National Yun-Lin Polytechnic Inst., Huwei, Taiwan China

Tel: +886-3573-1841; Fax: +886-3572-4361; E-mail: achin@cc.nctu.edu.tw

#### Abstract

The device performance made by thin gate oxide is related to the oxide thickness uniformity and the interface smoothness. Unfortunately, native oxide roughens the initial surface before thermal oxidation. In this paper, we have designed a leak-tight low-pressure N<sub>2</sub>O oxidation system, and the native oxide is desorbed *in-situ* under H<sub>2</sub> environment. Atomically smooth oxide and Si interface of ultra-thin oxides (11-38Å) were achieved as observed by high-resolutional TEM. Significant mobility enhancement over large gate field is obtained by reducing interface roughness scattering. The oxide reliability is also improved by this smoother interface between Si and oxide.

### I. INTRODUCTION

Scaling down the thickness of gate oxide [1]-[6] is one of the most important factors to continuously improve both CMOS devices and circuit performance. Ultra-thin 15Å-oxide [4] has demonstrated excellent device performance and direct-tunneling oxide with thickness less than 30Å is required for deca-nano CMOS technology. However, the presence of native oxide becomes an increasing concern for these thin oxides; it is reported that the naive oxide will strongly degrade the oxide reliability. To avoid the native oxide formation, several oxidation processes have been proposed recently, including a closed wet cleaning environment and H-terminated Si. Another native oxide related problem for these thin oxides is the interface roughness. The interface roughness can strongly affect the carrier transport that can be

characterized by measuring the electron mobility of MOSFET's [7]-[9]. Furthermore, electron mobility is an important parameter related to current drive and operation speed of MOSFET's. In this paper, we have developed a new oxidation process. Very smooth interface of oxide/Si is achieved by in-situ desorbing the native oxide in a low-pressure oxidation system before initiating thermal oxidation. Atomically smooth interface between oxide and Si is observed by highresolution TEM for oxide thickness of 11 and 38Å. The atomically smooth oxide is further characterized by measuring the electron mobility. Significant mobility increase is observed in these oxides with atomically smooth interface. Because the smooth interface and uniform thickness of oxide, the reliability is also much improved.

### II. EXPERIMENTAL

We have designed a low-pressure oxidation system to desorb native oxide *in-situ* before initiating the growth of thermal oxide. A leaktight reactor design and a high flow rate of hydrogen are used to avoid pre-matured growth of native oxide during temperature ramping up. Similar process procedure has been used in LPCVD to grow high quality Si epitaxy at 550°C [10]. After desorbing the native oxide by hydrogen bake, thermal oxides were grown at 900°C using N<sub>2</sub>O. To achieve better thickness controllability, the oxides were grown under a reduced pressure of 4.5 torr. Another merit of oxides grown under reduced pressure is the increased mean-free-path of oxygen molecules.

Therefore excellent thickness uniformity of variation less than 0.5Å is obtained across 4-inch wafer for a typical 20Å oxide. By using the above process, ultra-thin 11Å oxide can be continuously obtained. To reduce the initial Si surface roughness, a modified RCA cleaning is used with lower NH<sub>4</sub>OH and HF contents to achieve a smoother surface before oxidation. As measured by AFM, the RMS roughness is in a range between 1.5 to 2Å. For comparison purpose, control samples were grown under similar condition except without *in-situ* cleaning the native oxide. These oxides were further characterized by high-resolution TEM, interface mobility, and stress measurement.

#### III. RESULTS AND DISCUSSION

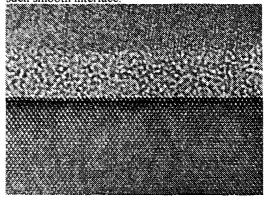

As mentioned above, one of the most important factors for oxide is the thickness uniformity and the related interface smoothness. Because of the uniform thickness, electric field can be evenly distributed over the whole oxide. On the other hand, a rough interface will generate local high electric field and therefore large current will flow through these areas and create reliability problem. Furthermore, the smooth interface is essential to achieve better electron mobility and switching speed of devices. Therefore we have first measured the interface roughness between oxide and Si. We have used cross-sectional TEM to observe this interface roughness. Fig. 1 presents the cross-sectional picture of the 38Å oxide with in-situ native oxide cleaned by hydrogen bake. The oxide thickness can be measured from the atomic image of single crystalline Si underneath the oxide; the distance between two adjacent planes in (111) direction is 3.1Å. It is important to note that atomically smooth interface between oxide and Si can be achieved and this is the best reported interface smoothness of oxide. Because such smooth interface is almost impossible to achieve after wet cleaning even using the modified RCA cleaning process, surface Si atom migration, after desorbing native oxide under a hydrogen environment, may be the mechanism to achieve such smooth interface.

Fig. 1. High-resolutional TEM image of the 38Å oxide with *in-situ* native oxide cleaned.

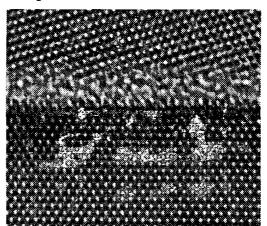

Because our process can *in-situ* desorb the native oxide, ultra-thin thermal oxide can be grown on fresh Si surface with thickness comparable to native oxide. Fig. 2 shows the cross-sectional TEM image of this ultra-thin 11Å oxide. One important feature is that the 11Å oxide is oxidized only by two atomic Si layers. Therefore this 11Å oxide may set up the ultimate and practical limit for further oxide thickness scaling.

Fig. 2. High-resolutional TEM image of the 11Å oxide with *in-situ* native oxide cleaned.

Because the interface roughness is one of the dominant factors to limit the electron mobility over wide electric field range, we have further investigated the electron mobility improvement of these oxides with atomically smooth interface.

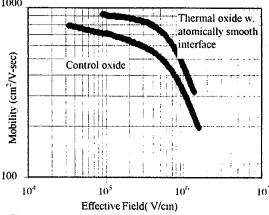

Fig. 3. Dependence of electron mobility on normal electric field of the 70Å oxides. Both samples are fabricated in the same lot and the only difference is the additional hydrogen bake step to desorb native oxide.

Fig. 3 shows the comparison of measured mobilities of control oxide grown by conventional method and the oxide with atomically smooth interface, respectively. The mobility is calculated from the measured channel conductance of wide gate MOSFET's. The thickness of both oxides is about 70Å. The electron mobility of control oxide follows the typical mobility and field dependence [7]-[9]. In contrast, near 30% increased mobility is measured over wide effective normal field from the MOSFET with atomically smooth interface. This is the best reported mobility value at the same effective normal field. Because both wafers from control oxide and atomically smooth oxide were processed at the same lot, the measured electron mobility enhancement is not processrelated. Therefore the mobility enhancement is strongly related to the improved interface smoothness as observed by cross-sectional TEM. Further, the measured mobility improvement is consistent to the theoretical prediction; the interface roughness dominates the high-field electron mobility that is also observed in measured data. It is important to note that the 30% mobility improvement related device performance enhancement is equivalent to the improvement by one generation of VLSI technology with 70% reduction of gate length.

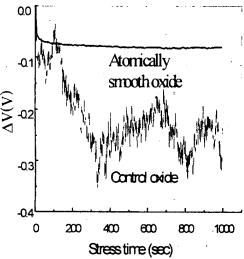

Fig. 4. Dependence of voltage change on stress time of the 27A oxides under a constant current density of 10A/cm<sup>2</sup>. The voltage noise in control oxide is the typical soft breakdown phenomenon.

Another important factor testing the oxide integrity will be the reliability. Fig. 4 shows the oxide stress data under a large applied constant current density of 10A/cm<sup>2</sup>. Because of the small change in voltage, we have plotted the voltage change instead of voltage value. A large current density is used here because no measurable change can be observed under lower current density stress for oxide with atomically smooth interface. For both oxides, there is no hard breakdown can be observed even under a large injected charge of 104 C/cm2. Instead of hard breakdown, control oxide shows a soft breakdown behavior that is generally observed in thin oxides. In sharp contrast, oxide with atomically smooth interface did not show any soft

breakdown behavior. Although possible mechanism of soft breakdown is still not understood, a smoother oxide surface may distribute the applied electric field more uniformly and therefore reduce the possibility of soft breakdown.

## IV. CONCLUSIONS

In conclusion, we have developed a new oxidation process to achieve atomically smooth interface between oxide and Si. Electron mobility improvement as much as 30% is obtained by using these smooth oxides, while the related MOSFET performance improvement is equivalent to one VLSI generation. In addition to the measured higher electron mobility, much improved oxide reliability is also achieved and no soft breakdown can be measured even under a large charge injection of  $10^4$  C/cm<sup>2</sup>.

## ACKNOWLEDGMENTS

We would like to thank the helpful discussion from Prof. K. C. Hsieh at the Dept. of Electrical engineering, Univ. of Illinois, and thank the continuous support from Prof. T. F. Lei at our Department. This work has been supported by NSC (87-2215-E-009-069) of Taiwan.

### Reference:

- [1] H. Hwang, W. Ting, D. L. Kwong, and J. Lee, "Improved reliability characteristics of submicrometer nMOSFETs with oxynitride gate dielectric prepared by rapid thermal oxidation in N<sub>2</sub>O," *IEEE Electron Device Lett.*, vol. 12, no 9, pp. 495-497, 1991.

- [2] M. Bhat, D. Wristers, J. Yan, L. K. Han, J. Fulford, D. L. Kwong, "Performance and hot-carrier reliability of N- and P-MOSFETs with rapid thermally NO-nitrided SiO<sub>2</sub> gate dielectrics," in *IEDM Tech. Dig.*, 1994, pp. 329-332.

- [3] C. T. Liu, Y. Ma, H. Luftman, and S. J. Hillenius, "Preventing boron penetration through 25-Å gate oxides with nitrogen implant in the Si substrates," IEEE Electron

- Device Lett., vol. 18, no 5, pp. 212-214, 1997

- [4] H. S. Momose, M. Ono, T. Yoshitomi, T. Ohguro, S. Nakamura, M. Saito, and H. Iwai, "1.5 nm direct-tunneling gate oxide Si MOSFET's," *IEEE Trans. Electron Devices*, vol. 43, no.8, pp. 1233-1241, 1996.

- [5] W. R. Anderson, D. R. Lombardi, R. G. Wheeler, T. P. Ma, "Determination of Si/SiO<sub>2</sub> interface roughness using weak localization," IEEE Electron Device Lett., vol. 14, no 7, pp. 351-353, 1993.

- [6] K. F. Lee, R. H. Yan, D. Y. Jeon, G. M. Chin, Y. O. Kim, D. M. Tennant, B. Razavi, H. D. Lin, Y. G. Wey, E. H. Westerwick M. D. Morris, R. W. Johnson, T. M. Liu, M. Tarsia, M. Cerullo, R. G. Swartz, and A. Ourmazd, "Room temperature 0.1 μm CMOS technology with 11.8 ps gate delay," in *IEDM Tech. Dig.*, 1993, pp. 131-134.

- [7] J. Hauser, "Extraction of experimental mobility data for MOS devices," *IEEE Trans. Electron Devices*, vol. 43, no. 11, pp. 1981-1988, 1996.

- [8] S. C. Sun and J. D. Plummer, "Electron mobility in inversion and accumulation layers on thermally oxidized silicon surfaces," *IEEE Trans. Electron Devices*, vol. 27, no. 8, pp. 1497-1508, 1980.

- [9] H. Shin, G. M. Yeric, A. F. Tasch, and C. M. Maziar, "Physically-based models for effective mobility and local-field mobility of electrons in MOS inversion layers," Solid-State Electron., vol. 34, no.6, pp. 545-552, 1991

- [10] A. Chin, B. C. Lin, and W. J. Chen, "High quality epitaxial Si grown by a simple lowpressure chemical vapor deposition at 550 degrees C," *Appl. Phys. Lett.*, vol. 69, no. 11, pp. 1617-1620, 1996.