**Fig. 3**  $Ta_{36}Si_{14}N_{30}$  etch depth against time with 150mtorr pressure, 40sccm total flow rate, 62.5%  $O_2$  concentration in CHF<sub>3</sub>+ $O_2$ , for several cathode power densities

● 0.43 W/cm<sup>2</sup> ■ 0.55 W/cm<sup>2</sup> ▲ 0.66 W/cm<sup>2</sup>

results in the delay increasing back up to 0.8min. The maximum etch rate shown in Fig. 2 at 62.5% O2 concentration corresponds to minimum delay. Thus, fast removal of Ta<sub>36</sub>Si<sub>14</sub>N<sub>50</sub> also implies fast removal of the surface native oxide. Fig. 3 shows etch rate as a function of time for several power densities at the optimum 62.5% O concentration. Increased power densities result in higher etch rates presumably due to higher production of reactive F species. Increased power densities also tend to give lower time delays due to faster removal of the native oxide as a result of increased chemical etching and/or sputter etching.

Maximum etch rate of Ta<sub>36</sub>Si<sub>14</sub>N<sub>50</sub> in CF<sub>4</sub>+O<sub>2</sub> was found to occur for 15% O2 concentration [4]. The higher O2 concentrations required to produce maximum Ta<sub>36</sub>Si<sub>14</sub>N<sub>50</sub> etch rate for CHF<sub>3</sub>+O<sub>2</sub> mixtures may be due to the greater tendency for plasma polymer formation for CHF3 than for CF4 [9]. In general, higher power levels and O, concentrations were required for CHF, than for CF<sub>4</sub> to achieve comparable etch rates.

Fig. 4 Scanning electron micrograph of  $Ta_{36}Si_{14}N_{50}$  patterned sample etched with 0.43 W/cm<sup>2</sup> cathode power density, 150mtorr pressure, 40sccm total flow rate, 62.5%  $O_2$  concentration in  $CHF_3+O_2$

Fig. 4 shows a scanning electron micrograph of a patterned Ta<sub>36</sub>Si<sub>14</sub>N<sub>50</sub> sample etched in CHF<sub>3</sub>+O<sub>2</sub>. The etched region at the lower left area of the photograph is observed to be about as smooth as the masked region.

In summary, reactive ion etching of Ta<sub>36</sub>Si<sub>14</sub>N<sub>50</sub> diffusion barrier layers was successfully performed in CHF3+O2 plasmas. The presence of a native surface oxide results in an initial delay for the commencement of etching. Maximum etch rate is achieved at 62.5% O<sub>2</sub> concentration, which also corresponds to minimum etch delay time.

Acknowledgment: The authors acknowledge R. Thompson for performing the sample patterning.

17 January 1995

Electronics Letters Online No: 19950363

G.F. McLane and L. Casas (Army Research Laboratory, Ft. Monmouth, NJ 07703, USA)

J.S. Reid and M.-A. Nicolet (California Institute of Technology, Pasadena, CA 91125, USA)

## References

- KOLAWA, E., and NICOLET, M.-A.: 'Amorphous Ta-Si-N thin-film alloys as diffusion barrier in Al/Si metallizations', J. Vac. Sci. Technol., 1990, A8, pp. 3006-3010

- KOLAWA, E., CHEN, J.S., REID, J.S., POKELA, P.J., and NICOLET, M.-A.: Tantalum-based diffusion barriers in Si/Cu VLSI metallizations', J. Appl. Phys., 1991, 70, pp. 1369-1373

- MOLARIUS, J.M., MOLARIUS, J.M., KOLAWA, E., MORISHITA, K., NICOLET, M.-A., TANDON, J.L., LEAVITT, J.A., and MCINTYRE, L.C.: 'Tantalum-based encapsulants for thermal annealing of GaAs', J. Electrochem. Soc., 1991, **138**, pp. 834–837

- MCLANE, G.F., CASAS, L., REID, J.S., KOLAWA, E., and NICOLET, M.-A.: 'Reactive ion etching of Ta-Si-N diffusion barriers in CF<sub>4</sub>+O<sub>2</sub>', J.

- Vac. Sci. Technol., 1994, **B12**, pp. 2352–2355 SUN, S.P., and MURARKA, S.P.: 'Reactive-ion etching of TaSi<sub>2</sub>/n' polysilicon barriers', J. Electrochem. Soc., 1988, **135**, pp. 2353–2357 RILEY, P.E., and HANSON, D.A.: 'Comparison of etch rates of silicon

- nitride, silicon dioxide, and polycrystalline silicon upon O2 dilution

- of CF<sub>4</sub> plasmas', J. Vac. Sci. Technol., 1989, **B7**, pp. 1352-1356 MELE, T.C., NULMAN, J., and KRUSIUS, J.P.: 'Selective and anisotropic reactive ion etch of LPCVD silicon nitride with CHF3 based gases', J. Vac. Sci. Technol., 1984, B2, pp. 684-687

- KUO, Y.: 'Reactive ion etching of sputter deposited tantalum with CF<sub>4</sub>, CF<sub>3</sub>Cl and CHF<sub>3</sub>', Jpn. J. Appl. Phys., 1993, **32**, pp. 179–185 OEHRLEIN, G.S., ZHANG, Y., VENDER, D., and HAVERLAG, M.:

- 'Fluorocarbon high-density plasmas. II. Silicon dioxide and silicon etching using  $CF_4$  and  $CHF_3$ , J. Vac. Sci. Technol., 1994, A12, pp. 333–344

## Recessed-gate AlGaAs/InGaAs/GaAs pseudormorphic HEMT with Si-planar-doped etch stop layer

W.H. Lan, W.J. Lin, C.K. Peng, S.S. Chen and S.L. Tu

Indexing terms: High electron mobility transistors. Etching

An improved slot etch technique based on an Si planar doped layer has been applied to gate recessing in the fabrication of AlGaAs/InGaAs/GaAs pseudomorphic high electron mobility transistors (HEMTs). The devices exhibited comparable gm with much better breakdown and leakage behaviour than conventional pseudomorphic HEMT devices

As a class of field effect transistor (FET), high electron mobility transistors (HEMT) are of great interest due to their high speed and high frequency applications [1]. To date, many HEMT products have been developed which use the GaAs/AlGaAS material system. To improve HEMT performance and obtain higher frequencies of operation, an InGaAs channel with higher electron velocity can be used [2]. Many pseudomorphic and lattice-matched structures with superior transport properties have been investigated [3, 4].

To enable the device to withstand higher overshoot voltage, and experience less gate leakage, gate recess etching is a critical step in the fabrication of FETs. Many improvements, such as the selective wet/dry etch and directional etch techniques, have been developed [5, 6]. In this Letter we introduce one Si planar doped layer as the

recess-controlled layer and demonstrate that a high performance InGaAs FET can be fabricated using this method.

Our pseudomorphic structure consists of a 400 Å (Si)GaAs cap layer ( $N_d = 3 \times 10^{18} {\rm cm}^{-3}$ ), 50 Å Al<sub>0.3</sub>Ga<sub>0.7</sub>As, (upper) planar doped Si layer ( $8 \times 10^{12} {\rm cm}^{-2}$ ), 300 Å Al<sub>0.3</sub>Ga<sub>0.7</sub>As, (lower) planar doped Si layer ( $1.7 \times 10^{13} {\rm cm}^{-2}$ ), 60 Å Al<sub>0.3</sub>Ga<sub>0.7</sub>As, 150 Å In<sub>0.15</sub>Ga<sub>0.85</sub>As , and a 0.5 µm GaAs buffer layer. The device layers are grown on a seminsulating (100) GaAs substrate in an MBE system (RLBER 32P). The mobility determined from Hall measurement is  $1900 {\rm cm}^2/{\rm Vs}$  and  $2900 {\rm cm}^2/{\rm Vs}$  at 300 and 77 K, respectively.

We begin device fabrication with a mesa etch, followed by AuGe/Ni/Au ohmic contact deposition, patterning, and furnace annealing at 460°C for 3min in a hydrogen environment. Specific contact resistance and the overall sheet resistance were determined to be  $7\pm2\times10^{-7}\Omega\text{cm}^2$  and  $3.4\pm0.2~\Omega\mu\text{m}$  using the transmission line method (TLM) [7]. After gate photolithography, the cap layer and AlGaAs layer are removed with 2:1:300 NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O etchant with an estimated etching rate of 2.8Å/s. This etch is stopped when it meets the Si planar doped plane. After the 3min slot etch, the Si planar doped plane was removed with 1:10 NH<sub>4</sub>F: H<sub>2</sub>O etchant in 8s, followed by 2:1:300 NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O etchant to ensure an enhancement mode device. The gate structure was completed with the gate metal (Al) deposition followed by the lift-off technique. Chromium-gold (Cr-Au) deposition was used to complete the interconnection layer.

The device TLM measurements were carried out using an HP 3457A multimeter. The device DC properties were measured with an HP41450. The microwave S-parameter measurements were performed from 0.45 to 26.5GHz with CASCADE microwave wafer probes and an HP 8510 automatic network analyser.

Fig. 1 Drain saturation current against gate-recess etch time of 'fat' device

$L_g = 50 \,\mathrm{mm}, \ W_g = 200 \,\mathrm{mm}$

Fig. 1 shows the saturation current as a function of gate recess etch time during recessing of the 'fat' device with 50 \mum gate length  $(L_{\nu})$ , 200 µm gate width  $(W_{\nu})$  and 2.5 µm gate to drain/ source spacing. After the saturation current reaches a stable value (around 55 mA in this Figure), we believe that it reaches the Si planar-doped plane. Thus, the Si planar-doped layer acts as an etch stop layer with respect to this etchant. The remaining etching causes slot (sidewall) etching to the drain and source sides. This etching process, like anisotropic etching, will increase the sidewall etch distance.

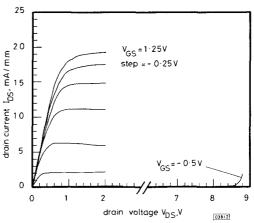

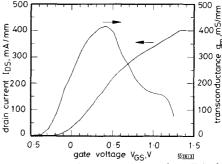

Fig. 2 shows the typical device drain current  $(I_{DS})$  against drain-source voltage  $(V_{DS})$  of our pseudomorphic HEMT device with  $L_g=0.9\mu \mathrm{m}$  and  $W_g=50\mu \mathrm{m}$ . The distance between the gate and drain/source is  $1.5/1.2\mu \mathrm{m}$ . The drain-source breakdown voltage  $(BV_{DS})$  defined at 10% of maximum  $I_{DS})$  above  $8.5\mathrm{V}$  can be observed. This result is comparable to around 6V of the device without the upper Si planar doped layer processed as a control experiment using the same etchant. The measured extrinsic transconductance  $(g_m)$  as a function of gate bias is shown in Fig. 3, with a maximum transconductance of over  $400\mathrm{mS/mm}$  and maximum  $I_{DS}$  of  $380\mathrm{mA/mm}$ . It is also comparable to  $350\mathrm{mS/mm}$   $(g_m)$  and  $280\mathrm{mA/mm}$  (maximum  $I_{DS})$  of the device without the upper

Fig. 2 Current-voltage characteristics ( $I_{DS}$  against  $V_{DS}$ ) of St-doped planar doped InGaAs HEMT with  $V_{GS} = -0.25\,V/{\rm step}$  of the 0.9 µm gate length device

Si-planar doped layer. The gate-drain/source reverse bias current was also reduced (<10 $\mu$ A at -7V), which is an expected result due to the minor DX centres of the undoped high energy gap material (Al<sub>0.3</sub>Ga<sub>0.7</sub>As) [8].

Fig. 3 Extrinsic transconductance against gate voltage ( $V_{\rm GS}$ ) of 0.9  $\mu$ m gate length device at 300 K

In summary, we have presented a method for fabricating pseudomorphic InGaAs HEMTs with Si planar doped layer to control the slot etch. High performances with high transconductance and low leakage current and high breakdown voltage can be achieved. This introduced Si planar-doped layer with high effective carrier concentration also reduces the specific contact resistance. The cutoff frequency as high as 34GHz for the 0.9µm gate length device shows that a high performance HEMT can be made using this proposed slot etching technique.

© IEE 1995 Electronics Letters Online No: 19950374

W.H. Lan, C.K. Peng, and S.L. Tu (Material R&D Center, Chung Shan Institute of Science and Technology, Lung Tan, Taiwan, Republic of China)

W.J. Lin (Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, Republic of China)

S.S. Chen (Institute of Materials Science and Engineering, National Chiao Tung University, Hsinchu, Taiwan, Republic of China)

## References

- BALLINGALL, J.M., MARTIN, P.A., MAZUROWSKI, J., HO, P., CHAO, P.C., SMITH, P.M., and DUH, K.H.G.: 'Pseudomorphic InGaAs high electron mobility transistors', *Thin Solid Films*, 1993, 231, pp. 95–106

- 2 ROSENBERG, J.J., BENLAMRI, M., KIRCHNER, P.D., WOODALL, J.M., and PETITIT, G.D.: 'An In<sub>0.15</sub>Ga<sub>0.85</sub>As/GaAs pseudomorphic single quantum well HEMT', IEEE Electron. Device Lett., 1985, 6, (11), pp. 491–493

- 3 SHIEH, H.-M., HSU, W.-C., HSU, R.-T., WU, C.-L., and WU, T.-S.: 'A high-performance d-doped GaAs/In, Ga1-, As pseudomorphic high electron mobility transistor utilising a graded In, Ga1-, As channel', IEEE Electron. Device Lett., 1993, 14, (12), pp. 581–583

- 4 WU, C.S., REN, F., PEARTON, S.J., HU, M., PAO, C.K., and WANG, R.F.: 'Dry etch gate recess high breakdown voltage power P-HEMTs', Electron. Lett., 1994, 30, (21), pp. 1803–1805

- 5 AGARWALA, S., NUMMILA, K., ADESIDA, I., CANEAU, C., and BHAT, R.: 'InAlAs/InGaAs heterostructure FETs processed with selective reactive-ion-etching gate-recess technology', *IEEE Electron. Device Lett.*, 1993, 14, (9), pp. 425–427

- 6 GREENBERG, D.R., DEL AMAMO, J.A., and BHAT, R.: 'A recessed-gate InAlAs/n+-InP HFET with an InP etch-stop layer', *IEEE Electron. Device Lett.*, 1992, 13, (3), pp. 137-139

- WILLIAMS, R.E.: 'Gallium arsenide processing techniques' (Artech House, Inc., 1984), pp. 241–251

ETIENNE, B., and THIERRY MIEG, V.: 'Reduction in the concentration

- 8 ETIENNE, B., and THIERRY MIEG, V.: 'Reduction in the concentration of DX centers in Si-doped GaAlAs using the planar doping technique', Appl. Phys. Lett., 1988, 52, (15), pp. 1237–1239

## Fuzzy control of power converters based on quasilinear modelling

C.K. Li, W.L. Lee and Y.W. Chou

Indexing terms: Fuzzy control, Power convertors

Unlike feedback control by the fuzzy PID method, a new fuzzy control algorithm based on quasilinear modelling of the DC-DC converter is proposed. Investigation is carried out using a buckboost converter. Simulation results demonstrated that the converter can be regulated with improved performance even whaen subjected to input disturbance and load variation.

Introduction: Switching DC-DC converters are highly nonlinear and time-varying in nature. Most controller designs are based on a linearised model with perturbation around a fixed steady-state operating point [1, 2]. A quasilinear model [3] which does not assume a fixed operating point considers the operating point as a function of the input signal. This model can describe a nonlinear system with better accuracy, and even be subjected to great disturbance. The proposed fuzzy quasilinear controller (FQLC) is based on this accurate model together with the state feedback method.

Quasilinear modelling and control: A DC-DC converter can be represented in the discrete-time domain using the following difference equation:

$$x_{n+1} = \Phi x_n + \Psi e_n \tag{1}$$

where  $x = [v_c \ i_t]^T$  is the state vector, e is the input voltage, and  $\Phi \in \mathbb{R}^{2d}$  and  $\Psi \in \mathbb{R}^2$  are the state transition matrices. With the assumption that the DC-DC converter can reach its steady-state operating point, (X, E, D), the converter's state variables will vary about its operating point and the dynamics of this system can be approximated by the following Taylor expansion:

proximated by the following Taylor expansion:

$$\Delta x_{n+1} \simeq \frac{\partial x_{n+1}}{\partial x_n} \bigg|_{x_n = X} \Delta x_n + \frac{\partial x_{n+1}}{\partial e_n} \bigg|_{\epsilon_n = E} \Delta e_n + \frac{\partial x_{n+1}}{\partial d} \bigg|_{d = D} \Delta D \tag{2}$$

The state vector  $x_{n+1}$  is a function of  $x_n$ ,  $e_n$  and d. The following state equation can accurately describe the system only if  $\Delta x_n$ ,  $\Delta e_n$  and  $\Delta d$  are small:

$$\Delta x_{n+1} = \Phi(D)\Delta x_n + [\Phi'(D)X + \Psi'(D)E]\Delta d + \Psi(D)\Delta e_n$$

(3)

Quasilinear modelling does not assume  $\Delta e_n$  to be a small quantity. Any variation of input signal e will affect the operating point  $(x_{op}, d_{op})$  if the output is to be regulated to follow a reference voltage  $V_{ref}$ . The above equation is simplified into

$$\Delta x_{n+1} = \Phi(d_{op})\Delta x_n + \Gamma(d_{op}, x_{op}, e)\Delta d \qquad ($$

where  $\Gamma(d_{op}, x_{op}, e) = \Phi'(d_{op})x_{op} + \Psi'(x_{op})e$ . The state feedback control law,  $\Delta d = K\Delta x_n$ , is used to reduce eqn. 4 into the following state equation:

$$\Delta x_{n+1} = [\Phi(d_{op}) + \Gamma(d_{op}, x_{op}, e)K(e)]\Delta x_n \qquad (5)$$

With the controller based on pole assignment and the desired poles of  $\lambda_1$  and  $\lambda_2$  being considered, the appropriate feedback coefficients can be evaluated to be:

$$k_1 = \frac{(\lambda_1 + \lambda_2 - \phi_{11} - \phi_{22})(\gamma_2 \phi_{11} - \gamma_1 \phi_{21}) - \gamma_2 (\lambda_1 \lambda_2 + \phi_{12} \phi_{21} - \phi_{11} \phi_{22})}{\lambda_1 \lambda_2 (\phi_{11} - \phi_{22}) - \lambda_1^2 \phi_{21} + \lambda_2^2 \phi_{12}}$$

(6

$$k_{2} = \frac{-(\lambda_{1} + \lambda_{2} - \phi_{11} - \phi_{22})(\gamma_{1}\phi_{22} - \gamma_{1}\phi_{12}) - \gamma_{1}(\lambda_{1}\lambda_{2} + \phi_{12}\phi_{21} - \phi_{11}\phi_{22})}{\lambda_{1}\lambda_{2}(\phi_{11} - \phi_{22}) - \lambda_{1}^{2}\phi_{21} + \lambda_{2}^{2}\phi_{12}}$$

(7)

Fuzzy quasilinear control algorithm: In the design of the fuzzy control algorithm, the input linguistic variable  $\Delta e$  is considered. The universe of discourse is  $\Delta E$  and the corresponding fuzzy term sets are  $\Delta E_1$  to  $\Delta E_n$ . The membership function  $\mu$  is a mapping  $\mu_{\Delta E}$ .  $\Delta e \rightarrow [0,1]|\Delta e \in \Delta E$ , where 1 represents full membership and 0 represents no membership to any fuzzy term set  $\Delta E_n$ . The proposed FQLC contains a feedforward path to continuously monitor any disturbance of input voltage, relocates the operating point and modifies the feedback gains  $k_1$  and  $k_2$  accordingly. The usual inference process is adopted. The following fuzzy relation and the composition rule of inference are used:

$$\mu_R(\Delta e, \Delta k) = \max_{i j} (\min(\mu_{\Delta E_i}(\Delta e), \mu_{\Delta K_j}(\Delta k)))$$

(8)

$$\mu_{\Delta K}(\Delta k) = \max_{\Delta e} (\min(\mu_{\Delta E}(\Delta e), \mu_R(\Delta e, \Delta k))$$

(9)

All the output fuzzy term sets are summed to form a resultant output set and defuzzified into a crisp value best representing the output set to produce a real control action. In the design here, a centre of gravity method is used for defuzzification and the control output is determined by the following formula:

$$\Delta k^* = \frac{\sum\limits_{i=1}^{n_k} \Delta k_i \mu_{\Delta K}(\Delta k_i)}{\sum\limits_{i=1}^{n_k} \mu_{\Delta K}(\Delta k_i)}$$

(10)

By tuning feedback gains heuristically, steady-state error can be eliminated and a good dynamic response can be obtained.

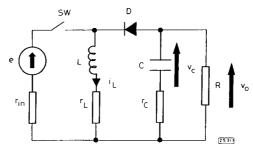

Fig. 1 Schematic diagram of buck-boost converter

Simulation results: The Runge-Kutta fourth-order method is used to solve the three sets of differential equations according to the state conditions of the buck-boost circuit. These conditions are: (a) switch ON, diode OFF, (b) switch OFF, diode ON; (c) switch OFF, diode OFF. The converter under consideration is shown in Fig. 1 and has a nominal output voltage  $V_{ref} = 30 \text{V}$ , input resistance  $r_{in} = 0.2 \Omega$ , nominal input voltage E = 20 V, switching frequency f = 5 kHz, load resistance  $R = 20 \Omega$ , capacitance C = 1.45 mF with parasitic resistance  $r_C = 1.18 \Omega$  and inductance L = 0.42 mH with parasitic resistance  $r_L = 0.07 \Omega$ . The transient response of the converter is studied under the following conditions: (i) nominal input voltage superimposed by a 10 V peak-topeak sinusiodal signal; (ii) a step load change from  $20 \Omega$  to  $10 \Omega$  at time = 50.5 ms.

For the quasilinear design, the desired eigenvalues chosen are 0.7 and 0.95. For the FQLC design, the nominal feedback coefficients of  $k_{1,n}=-0.0400$  and  $k_{2,n}=0.0032$  are used with  $\Delta e=e-E,$   $\Delta k_1=k_1-k_{1,n}$  and  $\Delta k_2=k_2-k_{2,n}$ . After optimisation, the linguistic rules are tabulated in Table 1.