ELSEVIER

Contents lists available at SciVerse ScienceDirect

## Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

# Polycrystalline silicon thin-film transistor with nickel-titanium oxide by sol-gel spin-coating and nitrogen implantation

Shih-Chieh Wu<sup>a</sup>, Tuo-Hung Hou<sup>a,\*</sup>, Shiow-Huey Chuang<sup>b</sup>, Hsin-Chih Chou<sup>b</sup>, Tien-Sheng Chao<sup>c</sup>, Tan-Fu Lei<sup>a</sup>

- <sup>a</sup> Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, 1001 University Road, Hsinchu 300, Taiwan, ROC

- <sup>b</sup> Department of Applied Chemistry, National University of Kaohsiung, 700, Kaohsiung University Rd., Nanzih District 811, Kaohsiung, Taiwan, ROC

- <sup>c</sup>Department of Electrophysics, National Chiao-Tung University, 1001 University Road, Hsinchu 300, Taiwan, ROC

#### ARTICLE INFO

Article history:

Available online 12 July 2012

Keywords: Nickel-titanium oxide (NiTiO $_3$ ) High- $\kappa$  gate dielectric Nitrogen implantation Thin-film transistors (TFTs)

#### ABSTRACT

This study demonstrates polycrystalline silicon thin-film transistors (poly-Si TFTs) integrated with a high- $\kappa$  nickel-titanium oxide (NiTiO3) gate dielectric using sol-gel spin-coating and nitrogen channel implantation. This novel fabrication method of the high- $\kappa$  NiTiO3 gate dielectric offers thin equivalent-oxide thickness and high gate capacitance density, favorable for increasing the current driving capability. Introducing nitrogen ions into the poly-Si using implantation effectively passivates the trap states not only in the poly-Si channel but also at the gate dielectric/poly-Si interface. The poly-Si NiTiO3 TFTs with nitrogen implantation exhibit significantly improved electrical characteristics, including lower threshold voltage, a steeper subthreshold swing, higher field-effect mobility, a larger on/off current ratio, and less threshold-voltage roll-off. Furthermore, the nitrogen implantation improves the reliability of poly-Si NiTiO3 TFTs against hot-carrier stress and positive bias temperature instability.

© 2012 Elsevier Ltd. All rights reserved.

## 1. Introduction

Polycrystalline silicon thin-film transistors (poly-Si TFTs) have attracted considerable attention because of their applications on peripheral driving circuits of system-on-panel (SOP) and high-performance active matrix liquid crystal displays (AM-LCDs), as well as active matrix organic light-emitting diode displays (AM-OLEDs) [1,2]. Poly-Si TFTs demonstrate numerous advantages such as higher driving current, larger field-effect mobility, and improved reliability, as compared with conventional amorphous silicon thin-film transistors ( $\alpha$ -Si TFTs). Because a low process temperature below 600 °C is necessary to fabricate poly-Si TFTs on glass substrates of commercial flat-panel displays, the solid-phase crystallization (SPC) technique is widely adopted for phase transformation from amorphous to polycrystalline silicon at low cost [3]. However, the driving current of the SPC poly-Si TFTs with conventional thick SiO<sub>2</sub> gate dielectrics is limited. Although the thickness scaling of SiO<sub>2</sub> boosts the driving current, it also unavoidably increases gate leakage current [4]. High- $\kappa$  gate dielectrics can increase gate capacitance while maintaining sufficient physical thickness. Therefore, the poly-Si TFTs with high- $\kappa$  gate dielectrics not only increase the driving current but also suppress the gate leakage current simultaneously.

Several techniques, including atomic layer deposition (ALD), physical vapor deposition (PVD), and chemical vapor deposition (CVD), have been developed to deposit high- $\kappa$  gate dielectrics. Another simple fabrication method, sol-gel spin-coating, has also been used to form high- $\kappa$  gate dielectrics, charge trapping layers of memory devices and active channel layers of oxide-based transistors [5–7]. The sol-gel spin-coating method is attractive because of its inexpensive precursors and simple facilities requiring no high vacuum. Additionally, the low process temperature of the sol-gel spin-coating method is compatible with the fabrication on glass substrates. Several high- $\kappa$  materials, including Al<sub>2</sub>O<sub>3</sub> and Ta<sub>2</sub>O<sub>5</sub>, have been proposed to replace conventional SiO<sub>2</sub> in poly-Si TFTs [8,9]. However, the device performance was compromised by the lower dielectric constant of  $Al_2O_3$  ( $\kappa$  < 9) and the narrow bandgap of Ta<sub>2</sub>O<sub>5</sub>. By contrast, NiTiO<sub>3</sub> fabricated using sputter methods was shown to have high dielectric constant, low leakage current and excellent reliability [10]. Furthermore, NiTiO<sub>3</sub> prepared by sol-gel spin-coating was proposed to be the high- $\kappa$  gate dielectric of poly-Si TFTs [11].

The poly-Si TFTs with high- $\kappa$  gate dielectrics is known to suffer from undesirable off-state leakage current because of field-enhanced emission through grain-boundary trap states [12]. Several methods have been proposed to reduce the grain-boundary trap states. The hydrogen-based plasma treatment technique has been most widely used [13]. However, the hydrogenated poly-Si TFTs is subjected to long-term device instability under electrical stress

<sup>\*</sup> Corresponding author. Tel.: +886 3 5712121. E-mail address: thhou@mail.nctu.edu.tw (T.-H. Hou).

because of the weak Si–H bonds [14,15]. Nitrogen channel implantation has also been proposed to passivate the trap states at the grain boundaries [16,17]. Additionally, robust Si–N bonds significantly improve the device reliability.

This paper reports a high-performance and highly reliable n-channel poly-Si TFT with a sol–gel spin-coating NiTiO $_3$  gate dielectric and nitrogen channel implantation. This study demonstrated a gate capacitance density of 410 nF/cm $^2$ , threshold voltage ( $V_{\rm TH}$ ) of 1.1 V, subthreshold slope (S.S.) of 200 mV/dec, field-effect mobility ( $\mu_{\rm FE}$ ) of 51 cm $^2$ /V-s, on/off current ratio ( $I_{\rm on}/I_{\rm off}$ ) over seven orders of magnitude, and robust reliability against hot carrier stress and positive bias temperature instability (PBTI). The proposed poly-Si TFT achieves excellent characteristics using only the conventional SPC, and is thus cost-effective and compatible to present flat-panel display manufacturing.

#### 2. Experimental procedures

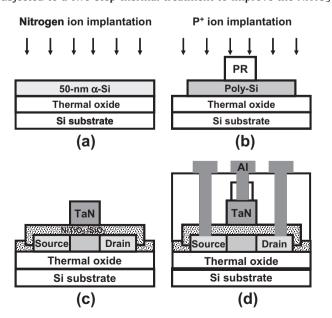

Fig. 1 illustrates the fabrication steps for the proposed poly-Si TFTs with the NiTiO<sub>3</sub> dielectric and nitrogen ion implantation. First, a 50-nm undoped amorphous silicon ( $\alpha$ -Si) layer was deposited on 550-nm SiO<sub>2</sub> by low-pressure chemical vapor deposition (LPCVD) at 550 °C. The nitrogen ions were implanted with a projected range at the middle of the  $\alpha$ -Si film and a dosage of  $5 \times 10^{13}$  cm<sup>-2</sup> [Fig. 1a]. The SPC and dopant activation of nitrogen ions were performed at 600 °C for 24 h in N<sub>2</sub> ambient. After patterning the active region by conventional lithography and dry etching, phosphorous ion implantation was performed at 20 keV with a dose of  $5 \times 10^{15}$  cm<sup>-2</sup> at the source/drain regions [Fig. 1b], followed by dopant activation annealing at 600 °C for 12 h. After the RCA clean process, a 3-nm SiO<sub>2</sub> layer was deposited on the poly-Si channel to improve the interface with the NiTiO  $_3$  gate dielectric by LPCVD using diluted tetraethyl orthosilicate (TEOS) of 10 sccm as the precursor at 30 m torr. The NiTiO<sub>3</sub> film was deposited on the SiO<sub>2</sub> layer using solgel spin-coating at 3000 rpm (rpm) for 30 s and then baked at 200 °C for 10 min to remove the solvent. The sol-gel solution was synthesized by dissolving nickel acetate tetrahydrate [Ni(OOCCH<sub>3</sub>)<sub>2</sub>·4H<sub>2</sub>O] and titanium isopropoxide  $Ti{OCH(CH_3)_2}_4$  in 2-methoxyethanol. The NiTiO<sub>3</sub> spin-coating processes were repeated three times to obtain a film thickness of approximately 50 nm. The sample was then subjected to a two-step thermal treatment to improve the NiTiO<sub>3</sub>

Fig. 1. Schematic diagrams of the process steps for the poly-Si  $NiTiO_3$  TFT with nitrogen channel implantation.

quality, first at 400 °C in  $O_2$  ambient for 20 min followed by additional rapid thermal annealing (RTA) at 500 °C in  $N_2$  ambient for 30 s. The TaN gate electrode with a thickness of 100 nm was defined using a lift-off process to prevent the plasma damage and over-etching using traditional dry etching [Fig. 1c]. After depositing a 300-nm  $SiO_2$  passivation layer using plasma-enhanced chemical vapor deposition at 300 °C, the contact holes were opened using a two-step wet etching process. A buffered oxide etch (BOE) solution and a HF: $H_2O = 50:1$  were used to etch  $SiO_2$  and  $NiTiO_3$ , respectively. Finally, a 400-nm Al film was deposited and patterned as metal pads [Fig. 1d]. No additional hydrogen plasma treatment or thermal sintering was performed after the Al pad patterning. For comparison, control poly-Si  $NiTiO_3$  TFTs without nitrogen implantation were also prepared using the same process flow.

#### 3. Results and discussion

#### 3.1. Material analyses

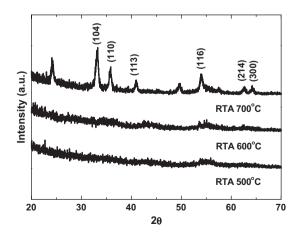

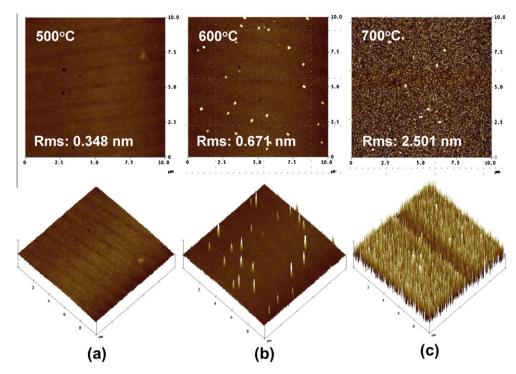

Fig. 2 presents the grazing incident X-ray diffraction (GI-XRD) spectra of the NiTiO<sub>3</sub> films annealed at various RTA temperatures. The samples remained amorphous at 500 °C and 600 °C, but crystallized at 700 °C with preferred orientations at (104), (111), (113), (116), (214), and (300). Fig. 3a–c illustrates the atomic force microscopy (AFM) images of NiTiO<sub>3</sub> films annealed at 500 °C, 600 °C, and 700 °C. The root-mean-square (rms) values of the surface roughness in the films annealed at 500 °C, 600 °C, and 700 °C were 0.348 nm, 0.671 nm, and 2.501 nm, respectively. The polycrystalline NiTiO<sub>3</sub> shows rough surface morphology that may cause high leakage current [11] and adhesion problems with the TaN metal gate. Therefore, the RTA temperature of 500 °C was chosen to fabricate our TFT devices.

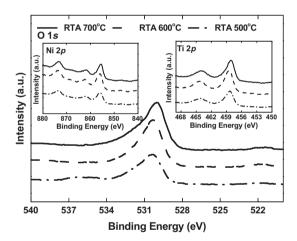

The chemical composition of the NiTiO<sub>3</sub> gate dielectric was determined using X-ray photoelectron spectroscopy (XPS), as shown in Fig. 4. The oxygen 1s spectrum included two different metal-oxygen bonds, Ni-O and Ti-O, with binding energy near 530.5 eV. After background removal using the Shirley method, the atomic ratio of Ni:Ti:O was estimated at 1:1:3 by integrating the intensity from 854 eV to 880 eV for the nickel 2p spectrum, from 453 to 468 eV for the titanium 2p spectrum, and from 526 to 535 eV for the oxygen 1s spectrum.

#### 3.2. Gate dielectric integrity of NiTiO<sub>3</sub>

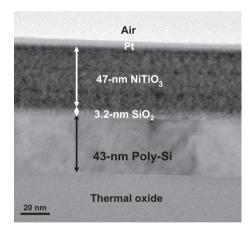

Fig. 5 shows the cross-sectional transmission electron microscopy (TEM) micrograph of the proposed poly-Si TFT with the Ni-

Fig. 2. GI-XRD spectra of spin-coating  $NiTiO_3$  films annealed at various RTA temperatures.

Fig. 3. AFM images of NiTiO<sub>3</sub> films annealed at (a) 500 °C, (b) 600 °C, and (c) 700 °C. The corresponding RMS values of the surface roughness are 0.348 nm, 0.671 nm, and 2.501 nm, respectively.

Fig. 4. XPS spectra of the Ni 2p, Ti 2p, and O 1S core levels for the  $\rm NiTiO_3$  gate dielectric.

${

m TiO_3}$  gate dielectric. The physical thicknesses of the NiTiO<sub>3</sub> gate dielectric and the poly-Si channel were approximately 47 nm and 43 nm, respectively, with a 3.2-nm  ${

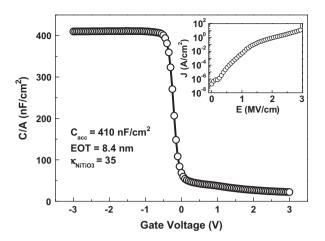

m SiO_2}$  interfacial layer in between. Fig. 6 shows a typical capacitance-voltage (C-V) characteristic at 1 MHz with an 8.4-nm equivalent-oxide thickness (EOT) extracted from the accumulation gate capacitance of 410 nF/cm². The C-V was measured from a NiTiO<sub>3</sub> metal-oxide-semiconductor (MOS) capacitor fabricated on the Si wafers using the identical NiTiO<sub>3</sub> deposition process. The dielectric constant of NiTiO<sub>3</sub> was estimated at 35, comparable to that in the sputtered NiTiO<sub>3</sub> [10], using the following equation:

$$EOT = T_{SiO_2} + (\kappa_{SiO_2}/\kappa_{NiTiO_3}) \times T_{NiTiO_3}$$

(1)

where  $\kappa_{\rm NiTiO3}$  and  $\kappa_{\rm SiO2}$  are the dielectric constants of NiTiO<sub>3</sub> and SiO<sub>2</sub>, respectively, and T<sub>NiTiO3</sub> and T<sub>SiO2</sub> are the physical thicknesses of these two films. Furthermore, the inset in Fig. 6 shows the gate current density versus the electric field (*J–E*) characteristic of the

**Fig. 5.** Cross-sectional TEM micrograph of the proposed poly-Si NiTiO₃ TFT. The top Pt capping layer was deposited for the purpose of TEM imaging only.

NiTiO<sub>3</sub> gate dielectric. The J–E characteristic was measured by applying gate voltage and grounding the source and drain of the TFT device. The breakdown field  $E_{\rm bd}$  of 3 MV/cm was close to other high- $\kappa$  dielectrics with similar dielectric constant using the empirical relation [18] as follows:

$$E_{bd} = 35 \times \kappa^{-0.64} \tag{2}$$

The high gate capacitance density and dielectric breakdown field suggest that the NiTiO<sub>3</sub> is a promising high- $\kappa$  gate-dielectric to replace SiO<sub>2</sub> in poly-Si TFTs.

### 3.3. Device characteristics

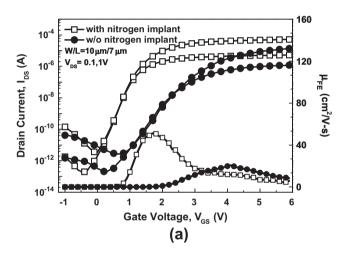

Fig. 7a illustrates the transfer characteristics ( $I_{\rm DS}-V_{\rm GS}$ ) of the poly-Si NiTiO $_3$  TFTs with and without nitrogen implantation at  $V_{\rm DS}=0.1~\rm V$  and 1 V. The channel width (W) and channel length

**Fig. 6.** C–V curve of the NiTiO $_3$  MOS capacitor. Inset is the gate current density versus the electric field (J–E) characteristic of the poly-Si NiTiO $_3$  TFT. The electric field is defined by the applied voltage divided by the physical film thickness.

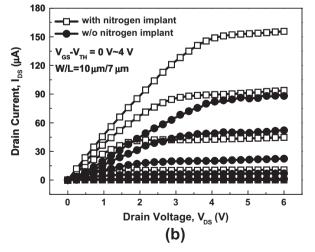

**Fig. 7.** (a) Transfer characteristics and (b) output characteristics of the poly-Si NiTiO<sub>3</sub> TFTs with and without nitrogen channel implantation.

(L) were 10  $\mu$ m and 7  $\mu$ m, respectively. The  $V_{TH}$ , S.S., and  $\mu_{FE}$  were extracted at  $V_{DS}$  = 0.1 V. The  $V_{TH}$  was defined as the gate voltage with a normalized drain current of (W/L)  $\times$  100 nA. The  $I_{on}/I_{off}$  was defined as the ratio of the maximum on-state current to the minimum off-state leakage current at  $V_{DS}$  = 1 V. The  $V_{TH}$ , S.S., and

$I_{\rm on}/I_{\rm off}$  were 3 V, 353 mV/dec, and 5.2  $\times$  10<sup>6</sup> for the device without implantation; and 1.1 V, 200 mV/dec, and 1.6  $\times$  10<sup>7</sup> for the device with implantation. The electrical characteristics of the poly-Si Ni-TiO<sub>3</sub> TFTs with nitrogen implantation were significantly improved, as compared with those without nitrogen implantation. Additionally, the maximum field-effect electron mobilities of the poly-Si Ni-TiO<sub>3</sub> TFTs with and without nitrogen implantation were 51 and 21 cm<sup>2</sup>/V s, respectively, as shown in Fig. 7a. The output characteristics ( $I_{\rm DS}$ – $V_{\rm DS}$ ) of poly-Si NiTiO<sub>3</sub> TFTs with and without nitrogen implantation are shown in Fig. 7b. The driving current of the poly-Si NiTiO<sub>3</sub> TFT using nitrogen implantation shows 80% improvement, as compared with that without implantation at  $V_{\rm GS}$ – $V_{\rm TH}$  = 4 V because of the superior electron mobility. Table 1 summarizes the critical TFT device parameters obtained in this study.

Interface trap states and grain boundary traps have been reported to dominate the electrical characteristics of poly-Si TFTs. where the deep trap states at grain boundaries mainly affected  $V_{\rm TH}$ , and the deep interface trap states degraded S.S. [19,20]. Previous analysis of secondary ion mass spectrometry (SIMS) on TFTs with channel nitrogen implantation revealed that substantial nitrogen piled up at the interface of gate dielectric and poly-Si channel and also diffused deeply into the bulk poly-Si film [16]. The significant improvement on the TFT characteristics has been attributed to the nitrogen passivation effect on the interface states of the gate dielectric/poly-Si channel interface and the Si dangling bonds at the grain boundaries of the poly-Si channel. The formation of Si-N bonds has been postulated to be responsible for the effective passivation [16,17,21]. Although difference in grain size may also explain the improved TFT characteristics, we presume that the grain size was not significantly altered by the nitrogen channel implantation because the projected range of implantation at the middle of the  $\alpha$ -Si film is difficult to interfere with the nucleation process at the  $\alpha$ -Si/bottom SiO<sub>2</sub> interface [22].

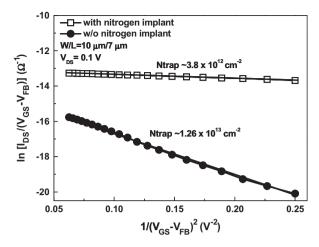

#### 3.4. Trap-state density

The effective grain-boundary trap state density  $(N_{\rm trap})$  was calculated using the grain-boundary trapping model proposed by Levinson and Proano [23,24]. Fig. 8 exhibits the  $\ln[(I_{\rm DS}/(V_{\rm GS}-V_{\rm FB})]^2$  versus  $1/(V_{\rm GS}-V_{\rm FB})^2$  at  $V_{\rm DS}=0.1$  V and high gate voltage for the poly-Si NiTiO<sub>3</sub> TFTs with and without nitrogen ion implantation, where  $V_{\rm FB}$  is the flatband voltage.  $N_{\rm trap}$  can be calculated from the square root of the slope in Fig. 8. The  $N_{\rm trap}$  in the devices with and without nitrogen ion implantation were  $3.8 \times 10^{12}$  cm<sup>-2</sup> and  $1.26 \times 10^{13}$  cm<sup>-2</sup>, respectively. This result indicates that the nitrogen incorporation can effectively passivate the trap states in the grain boundaries, in excellent agreement with the improved device performance.

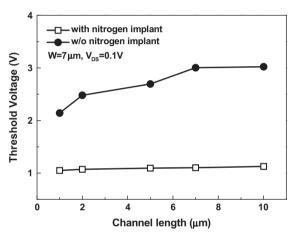

#### 3.5. Short-channel effect

The  $V_{\rm TH}$  as a function of channel length is shown in Fig. 9. The channel width was fixed at 10 µm. Noticeable  $V_{\rm TH}$  roll-off was observed in the poly-Si TFTs without nitrogen implantation, but not in those with nitrogen implantation. In the undoped poly-Si TFT,  $V_{\rm TH}$  was governed by the grain boundary traps. The  $V_{\rm TH}$  roll-off in

**Table 1**Extracted device parameters for the poly-Si NiTiO<sub>3</sub> TFTs with and without nitrogen implantation.

| Poly-Si NiTiO <sub>3</sub> TFT | $V_{\mathrm{TH}}\left(V\right)$ | S.S. (mV/dec.) | $\mu_{FE}$ (cm <sup>2</sup> /V-s) | <sup>I</sup> on/ <sup>I</sup> off ratio                               |

|--------------------------------|---------------------------------|----------------|-----------------------------------|-----------------------------------------------------------------------|

| With nitrogen                  | 1.1                             | 200            | 51                                | $\begin{array}{c} 1.6 \times 10^{7} \\ 5.2 \times 10^{6} \end{array}$ |

| W/O nitrogen                   | 3                               | 353            | 21                                |                                                                       |

Fig. 8. Effective trap state densities of the poly-Si  $NiTiO_3$  TFTs with and without nitrogen channel implantation.

Fig. 9. Threshold-voltage roll-off characteristics of the poly-Si  $\rm NiTiO_3$  TFTs with and without nitrogen channel implantation.

the scaled poly-Si TFTs was attributed to the reduced number of grain boundaries in the poly-Si channel and less grain-boundary trap states [25,26]. In the nitrogen-implanted poly-Si TFT,  $V_{\rm TH}$  was less susceptible to the poly-Si grain boundary because of the nitrogen passivation effect, as evidenced by the much lower  $V_{\rm TH}$ . Therefore, the  $V_{\rm TH}$  roll-off became less significant even the grain size was presumed to be comparable to that in the undoped channel.

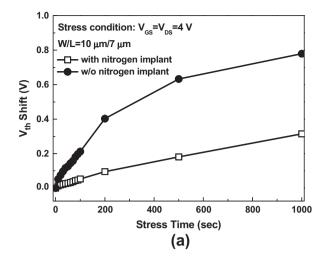

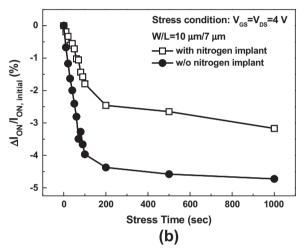

#### 3.6. Device reliability

Hot-carrier stress at room temperature under  $V_{\rm GS}$  = 4 V and  $V_{\rm DS}$  = 4 V was performed to investigate the reliability of the poly-Si NiTiO<sub>3</sub> TFTs with and without nitrogen implantation. The accelerated stress condition allowed TFT on-current higher than that required for the use condition of AM-OLED applications [27]. Fig. 10a and b shows the  $V_{\rm TH}$  shift ( $\Delta V_{\rm TH}$ ) and on-current degradation ( $\Delta I_{\rm on}$ ) as a function of the hot-carrier stress time. The  $\Delta V_{\rm TH}$  and  $\Delta I_{\rm on}$  were defined as  $V_{\rm TH}$ , stressed- $V_{\rm TH}$ , initial and ( $I_{\rm on}$ , stressed- $I_{\rm on}$ , initial)/ $I_{\rm on}$ , initial × 100%, respectively, where initial and stressed indicated the extracted values before and after stress. The poly-Si NiTiO<sub>3</sub> TFTs with nitrogen implantation show smaller  $\Delta V_{\rm TH}$  (0.31 V versus 0.78 V) and  $\Delta I_{\rm on}$  (3.2% versus 4.7%) as compared with the control sample after 1000 s stress. Note that  $\Delta I_{\rm on}$

**Fig. 10.** (a) Threshold-voltage shift and (b) on-current degradation versus hot-carrier stress time for the poly-Si NiTiO<sub>3</sub> TFTs with and without nitrogen channel implantation.

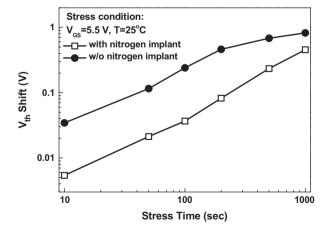

**Fig. 11.** Threshold-voltage shift versus PBTI stress time for the poly-Si NiTiO<sub>3</sub> TFTs with and without nitrogen channel implantation.

in an industrial standard  $\alpha$ -Si TFT for AM-LCD backplanes was reported to be 5% after 1 h DC stress [27]. The device degradation due to the hot-carrier stress may be attributed to the following two reasons: the interface state generation at the gate dielectric/

poly-Si interface and the formation of Si dangling bonds by breaking weak Si–H bonds with a bond energy of 70 kcal/mol [29] in the poly-Si channel [15]. The improvement on the immunity against hot-carrier stress using nitrogen implantation correlated with the larger bond energy of 106 kcal/mol [28] of Si–N bonds [16,17]. Further research is necessary to confirm the formation of the robust Si–N bonds in place of the weak Si–H bonds.

Positive bias temperature instability (PBTI) is another critical reliability concern for n-channel TFT devices with high- $\kappa$  gate dielectrics.  $V_{\rm GS}$  = 5.5 V was applied to study the PBTI of the poly-Si NiTiO<sub>3</sub> TFTs at 25 °C, as shown in Fig. 11. The electrons accelerated by the applied positive gate voltage may break the weak bonds at the grain boundaries of the poly-Si channel and the gate dielectric/poly-Si interface to generate the trap states, resulting in significant  $\Delta V_{\rm TH}$  during the PBTI stress [30]. Therefore, the poly-Si NiTiO<sub>3</sub> TFTs with nitrogen implantation exhibited superior immunity against PBTI because of the nitrogen passivation effect.

#### 4. Conclusion

This study is the first to demonstrate high-performance poly-Si TFTs, utilizing nitrogen channel implantation and a spin-coating NiTiO<sub>3</sub> gate dielectric. High gate capacitance density of 410 nF/cm<sup>2</sup> was achieved using a 47-nm NiTiO<sub>3</sub> gate dielectric with a dielectric constant of 35 and a TaN metal gate. Additionally, nitrogen channel implantation improved the threshold voltage, subthreshold swing, field-effect mobility, and on/off current ratio because of the passivation of trap states in the poly-Si film and at the gate dielectric/poly-Si interface. Nitrogen channel implantation also improves the immunity against hot-carrier stress and positive bias temperature instability. Therefore, the proposed poly-Si TFTs requiring no expensive phase crystallization techniques is a highly promising candidate for system-on-panel applications and high-speed active-matrix addressing.

## Acknowledgements

The authors would like to acknowledge the support of National Nano Device Laboratories (NDL) on the device fabrication and the financial support by the National Science Council (NSC) under Contact No. NSC 98-2221-E-009-004.

#### References

- Serikawa T, Shirai S, Okamoto A, Suyama S. Low-temperature fabrication of high-mobility poly-Si TFTs for large-area LCDs. IEEE Trans Electron Dev 1989;36:1929–33.

- [2] Meng Z, Wong M. Active-matrix organic light-emitting diode displays realized using metal-induced unilaterally crystallized polycrystalline silicon thin-film transistors. IEEE Trans Electron Dev 2002;49:991–6.

- [3] Aoyama T, Kawachi G, Konishi N, Suzuki T, Okajima Y, Miyata K. Crystallization of LPCVD silicon films by low temperature annealing. J Electrochem Soc 1989:136:1169–73.

- [4] Takami A, Ishida A, Tsutsumi J, Nishibe T, Ibaraki N. Threshold voltage shift under the gate bias stress in low-temperature poly-silicon TFT with the thin gate oxide film. In: Proceedings of international workshop AM-LCD; 2000. p. 45–8

- [5] You HC, Ko FH, Lei TF. Physical characterization and electrical properties of sol-gel-derived zirconia films. J Electrochem Soc 2006;153:F94-9.

- [6] You HC, Hsu TH, Ko FH, Huang JW, Lei TF. Hafnium silicate nanocrystal memory using sol-gel-spin-coating method. IEEE Electron Dev Lett 2006;27:644-6.

- [7] Yang YH, Sydney, Yang S, Kao CY, Chou KS. Chemical and electrical properties of low-temperature solution-processed In–Ga–Zn–O thin-film transistors. IEEE Electron Dev Lett 2010;31:329–31.

- [8] Jin Z, Kwok HS, Wong M. High-performance polycrystalline SiGe thin-film transistors using Al<sub>2</sub>O<sub>3</sub> gate insulators. IEEE Electron Dev Lett 1998;19:502–4.

- [9] Um MY, Lee SK, Kim HJ. Characterization of thin film transistor using Ta<sub>2</sub>O<sub>5</sub> gate dielectric. In: Proceedings of international workshop AM-LCD; 1998. p. 45–6

- [10] Pan TM, Lei TF, Chao TS. Comparison of ultrathin CoTiO $_3$  and NiTiO $_3$  high- $\kappa$  gate dielectrics. J Appl Phys 2001;89:3447–52.

- [11] Wu SC, Yen RC, Deng CK, Chao TS, Chuang SH, Lei TF. Characterization of polycrystalline silicon thin-film transistors with nickel-titanium oxide gate dielectric coating by sol-gel method. In: International conference on solid state devices and materials; 2009: p. 583-4.

- [12] Guist GK, Sigmon TW. High-performance thin-film transistors fabricated using excimer laser processing and grain engineering. IEEE Trans. Electron Dev 1998;45:925–32.

- [13] Wu IW, Huang TY, Jackson WB, Lewis AG, Chiang A. Passivation kinetics of two types of defects in polysilicon TFT by plasma hydrogenation. IEEE Electron Dev Lett 1991;12:181–3.

- [14] Wu IW, Jackson WB, Huang TY, Lewis AG, Chiang A. Mechanism of device degradation in n- and p-channel polysilicon TFT's by electrical stressing. IEEE Electron Dev Lett 1990;11:167–70.

- [15] Hack M, Lewis AG, Wu IW. Physical models for degradation effects in polysilicon thin-film transistors. IEEE Trans Electron Dev 1993;40:890–7.

- [16] Yang CK, Lei TF, Lee CL. Characteristics of top-gate thin-film transistors fabricated on nitrogen-implanted polysilicon films. IEEE Trans Electron Dev 1995;42:2163–9.

- [17] Deng CK, Chang HR, Chiou BS. Electrical properties of high-κ praseodymium oxide polycrystalline silicon thin-film transistors with nitrogen implantation. Jpn J Appl Phys 2008;47:853–6.

- [18] McPherson JW, Kim J, Shanware A, Mogul H, Rodriguez J. Trends in the ultimate breakdown strength of high dielectric-constant materials. IEEE Trans Electron Dev 2003;50:1771–8.

- [19] Farmakis FV, Brini J, Kamarinos G, Dimitriadis CA. Anomalous turn-on voltage degradation during hot-carrier stress in polycrystalline silicon thin-film transistors. IEEE Electron Dev Lett 2001;22:74–6.

- [20] Kimura M, Yasuhara T, Harada K, Abe D, Inoue S, Shimoda T. The study of oxide-interface and grain-boundary traps in poly-Si TFT characteristics and its application to fabrication process diagnosis. J Soc Inf Disp 2005;13:1027–33.

- [21] Cheng HC, Wang FS, Huang CY. Effects of NH<sub>3</sub> plasma passivation on n-channel polycrystalline silicon thin-film transistors. IEEE Trans Electron Dev 1997;44:64–8.

- [22] Yang CK, Lei TF, Lee CL. Characteristics of top-gate polysilicon thin-film transistors fabricated on fluorine-implanted and crystallized amorphous silicon films. J Electrochem Soc 1996;143:3302–7.

- [23] Levinson J, Shepherd FR, Scanlon PJ, Westwood WD, Este G, Rider M. Conductivity behavior in polycrystalline semiconductor thin film transistors. J Appl Phys 1982;53:1193–202.

- [24] Proano RE, Misage RS, Ast DG. Development and electrical properties of undoped polycrystalline silicon thin-film transistors. IEEE Trans Electron Dev 1989;36:1915–22.

- [25] Lewis AG, Huang TY, Wu IW, Bruce RH, Chiang A. Physical mechanisms for short channel effects in polysilicon thin film transistors. IEDM Tech Dig 1989:349–52.

- [26] Wang H, Chan M, Jagar S, Poon VMC, Qin M, Wang Y, et al. Super thin-film transistor with SOI CMOS performance formed by a novel grain enhancement method. IEEE Trans Electron Dev 2000:47:1580–6.

- [27] Sturm JC, Hekmatshoar B, Cherenack K, Wagner S. Amorphous silicon TFT's with 100-year lifetimes in a clear plastic compatible process for AMOLEDs. In: Society for information display; 2009: p. 979–82.

- [28] Kazor A, Jeynes C, Boyd IW. Fluorine enhanced oxidation of silicon at low temperature. Appl Phys Lett 1994;65:1572–4.

- [29] Pauling L. The nature of the chemical bond. 3rd ed. Ithaca, NY: Cornell University Press; 1960.

- [30] Ma MW, Chen CY, Wu WC, Su CJ, Kao KH, Chao TS, et al. Reliability mechanisms of LTPS-TFT with HfO<sub>2</sub> gate dielectric: PBTI, NBTI, and hotcarrier stress. IEEE Trans Electron Dev 2008;55:1153-60.