## Abnormal interface state generation under positive bias stress in TiN/HfO2 p-channel metal-oxide-semiconductor field effect transistors

Wen-Hung Lo, Ting-Chang Chang, Jyun-Yu Tsai, Chih-Hao Dai, Ching-En Chen, Szu-Han Ho, Hua-Mao Chen, Osbert Cheng, and Cheng-Tung Huang

Citation: Applied Physics Letters 101, 133505 (2012); doi: 10.1063/1.4752456

View online: http://dx.doi.org/10.1063/1.4752456

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/101/13?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Investigation of abnormal negative threshold voltage shift under positive bias stress in input/output n-channel metal-oxide-semiconductor field-effect transistors with TiN/HfO2 structure using fast I-V measurement Appl. Phys. Lett. **104**, 113503 (2014); 10.1063/1.4868532

Abnormal threshold voltage shift under hot carrier stress in Ti1xNx/HfO2 p-channel metal-oxide-semiconductor field-effect transistors

J. Appl. Phys. 114, 124505 (2013); 10.1063/1.4822158

Abnormal sub-threshold swing degradation under dynamic hot carrier stress in HfO2/TiN n-channel metal-oxidesemiconductor field-effect-transistors

Appl. Phys. Lett. 103, 022106 (2013); 10.1063/1.4811784

Charge trapping induced drain-induced-barrier-lowering in HfO2/TiN p-channel metal-oxide-semiconductor-field-effect-transistors under hot carrier stress

Appl. Phys. Lett. 100, 152102 (2012); 10.1063/1.3697644

Bulk and interface trap generation under negative bias temperature instability stress of p-channel metal-oxide-semiconductor field-effect transistors with nitrogen and silicon incorporated HfO 2 gate dielectrics Appl. Phys. Lett. **98**, 063504 (2011); 10.1063/1.3541879

## Abnormal interface state generation under positive bias stress in TiN/HfO<sub>2</sub> p-channel metal-oxide-semiconductor field effect transistors

Wen-Hung Lo,<sup>1</sup> Ting-Chang Chang,<sup>1,2,a)</sup> Jyun-Yu Tsai,<sup>1</sup> Chih-Hao Dai,<sup>3</sup> Ching-En Chen,<sup>4</sup> Szu-Han Ho,<sup>4</sup> Hua-Mao Chen,<sup>5</sup> Osbert Cheng,<sup>6</sup> and Cheng-Tung Huang<sup>6</sup>

Department of Physics, National Sun Yat-Sen University, Kaohsiung, Taiwan

(Received 31 May 2012; accepted 30 August 2012; published online 27 September 2012)

This Letter studies positive bias stress-induced abnormal interface state on TiN/HfO<sub>2</sub> p-channel metal-oxide-semiconductor field effect transistors. It can be found that the degradation is associated with electron trapping, resulting in  $V_{th}$  shift but without subthreshold slope degradation. However, charge pumping current ( $I_{CP}$ ) shows a significant degradation after stress. Accordingly, the impact ionization-induced  $N_{it}$  located  $HfO_2/SiO_2$  is proposed to demonstrate the  $I_{CP}$  degradation. The AC stress with several frequencies is used to evidence the occurrence of impact ionization. Further, the device with additional pre-existing  $N_{it}$  located  $SiO_2/Si$  has insignificant degradation due to reduction in stress electric field. © 2012 American Institute of Physics. [http://dx.doi.org/10.1063/1.4752456]

The physical limitation of the silicon dioxide (SiO<sub>2</sub>) as gate insulator has achieved the point where its thickness is approaching to a few atomic layers thick. 1,2 Below the physical thickness 12 Å, the significant gate leakage current results in a volume active power consumption, leading a worse reliability of metal-oxide semiconductor field effect transistors (MOSFETs). To avoid this serious issue, high-k dielectrics have been introduced as hafnium (Hf)-base, zirconium, aluminum oxides<sup>3-6</sup> and heavily investigated as a replacement for conventional SiO<sub>2</sub> gate insulator. However, metal gate/high-k stack has to face many critical issues such as defects in high-k material, which can lead to undesired transport through the dielectrics and trapping-induced instabilities such as negative bias temperature instability (NBTI), positive bias temperature instability (PBTI), and time-depended dielectric breakdown (TDDB), and hot carrier injection (HCI) in metal gate/high-k devices to realize the influence of high-k dielectric characteristics on devices under electric stress. 7-13 However, for p-FETs, the behavior of off-state stress on gate/high-k devices has not yet been studied. Therefore, this Letter investigates the phenomenon for TiN/HfO<sub>2</sub> p-MOSFETs under positive bias stress (PBS). And we found that the stress-induced N<sub>it</sub> is generated at interface between high-k layer and buffer oxide, instead of channel interface.

The TiN/HfO<sub>2</sub> p-MOSFETs were studied in this paper based on the high-performance 28-nm CMOS technology. Both devices were fabricated using a conventional self-aligned transistor flow through the gate first process. For the gate first process devices, 10 Å and 30 Å of high quality thermal oxide were, respectively, grown on a (100) Si substrate as buffer oxide layers. After standard cleaning procedures, 30 Å of HfO<sub>2</sub> films were sequentially deposited by atomic layer

deposition. Next, 10 nm of TiN films were deposited by radio frequency physical vapor deposition, followed by poly-Si deposition as a low resistance gate electrode. The dopant profile is  $\sim\!10^{20}\,\rm cm^{-3}$  and  $\sim\!10^{18}\,\rm cm^{-3}$  for source/drain and channel, respectively, and activation were performed at 1025 °C. And the doping concentration of poly gate is  $\sim\!10^{20}\,\rm cm^{-3}$ . In this study, the dimensions of the selected devices were 10  $\mu m$  and 1  $\mu m$  in width and length, respectively. The device with buffer thickness of 10 Å was subjected to the positive gate voltage (V<sub>G</sub>) condition with 2V+flatband voltage (V<sub>FB</sub>). The stress was briefly interrupted to measure the drain current-gate voltage (I<sub>D</sub>-V<sub>G</sub>) and charge pumping current (I<sub>CP</sub>). All experimental data were measured using an Agilient B1500/B1530A semiconductor parameter analyzer.

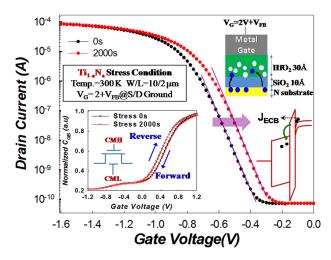

Figure 1 shows the PBS-induced drain current (I<sub>D</sub>)-gate voltage (V<sub>G</sub>) characteristic under semi-logarithmic scale of TiN/HfO<sub>2</sub> p-MOSFETs (device A). The stress condition V<sub>G</sub> was selected 2 V, adding V<sub>FB</sub> to be a correction term. As the result, the degradations on device during PBS show positive shift and decrease in threshold voltage (V<sub>th</sub>) and drain current (ID), respectively. The subthreshold slope (SS) is extracted by  $I_D$  ranges  $10^{-7}$ A to  $10^{-9}$  A. In addition, the  $I_D$ -V<sub>G</sub> under semi-logarithmic scale shows a parallel shift at subthreshold region without stretch out, indicating invariant of SS after PBS. This is because the PBS-induced charge trapping is associated with amount of traps and stress electric field. As carriers could rely on tunneling or/and thermal emission to cross oxide barrier height, charge trapping behavior should occur and no damaging interface state at Si/SiO2 (Nit, Si/SiO2), especially for ultra-thin buffer oxide. 10,11 Additionally, the C-V curve also shows the occurrence of electron trapping at high-k layer as shown in the inset of Figure 1. It can be seen that the capacitance of gate terminal to body terminal versus gate voltage (C<sub>GB</sub>-V<sub>G</sub>) curve exhibits a hysteresis window as V<sub>G</sub> implements a dual-sweep (forward and reverse) before and

<sup>&</sup>lt;sup>2</sup>Advanced Optoelectronics Technology Center, National Cheng Kung University, Taiwan

<sup>&</sup>lt;sup>3</sup>Department of Photonics, National Sun Yat-Sen University, Kaohsiung, Taiwan

<sup>&</sup>lt;sup>4</sup>Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan

<sup>&</sup>lt;sup>5</sup>Department of Photonics & Institute of Electro-Optical Engineering, National Chiao Tung University, Hsinchu, Taiwan

<sup>&</sup>lt;sup>6</sup>Device Department, United Microelectronics Corporation, Tainan Science Park, Taiwan

a) Author to whom correspondence should be addressed. Electronic mail: tcchang@mail.phys.nsysu.edu.tw.

FIG. 1.  $I_D$ - $V_G$  transfer characteristic curves of TiN/HfO<sub>2</sub> p-MOSFETs before and after PBS stress. The inset shows normalized  $C_{GB}$ - $V_G$  curve before and after stress and corresponding energy band diagram for stress condition.

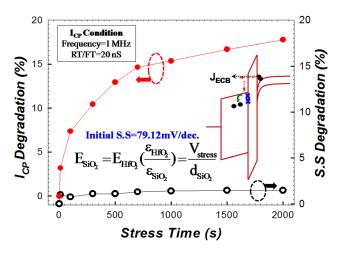

after PBS. According to experimental data, the window size seems to be invariant after PBS (red triangle). This behavior illustrates that stress condition did not result in additional bulk traps in high-k layer. However, charge pumping current  $(I_{CP})$ , which is another method to examine N<sub>it, Si/SiO2</sub> has an inconsistent result with SS. Figure 2 shows the I<sub>CP</sub> shift for TiN/ HfO<sub>2</sub> p-MOSFETs under PBS and the SS degradation is also shown for comparison. The gate pulse frequency (f) with 1 MHz is selected as I<sub>CP</sub> was measured. It can be seen that the shift of I<sub>CP</sub> is more significant than SS. According to the previous, I<sub>CP</sub> measurement with high frequency (<1 MHz) is difficult to examine the deep defects in high-k bulk due to insufficient charging time. The measurement condition of I<sub>CP</sub> with f = 1 MHz we selected is mainly bounded to detect interfacial defects, instead of deep bulk traps. 14,15 And then, C<sub>GB</sub> has shown that there are not additional stress-induced deep defects in high-k layer as shown in the inset of Fig. 1. Accordingly, I<sub>CP</sub> signal must reflect the defects located at somewhere. Based on those results, we would like to propose that interfacial defects could be generated under PBS located at HfO<sub>2</sub>/ SiO<sub>2</sub> interface (N<sub>it, SiO2/HfO2</sub>). Due to the buffer SiO<sub>2</sub> layer is  $\sim 10$  Å, the pumping carriers come from source and drain

FIG. 2. The PBS-induced  $I_{CP}$  and SS degradation for TiN/HfO<sub>2</sub> p-MOSFETs. The inset shows the equation for partial voltage for SiO<sub>2</sub> and initial SS value.

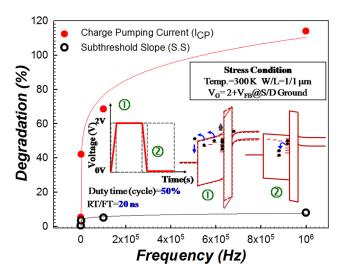

(S/D) have a probability to tunnel buffer oxide to approach HfO<sub>2</sub>/SiO<sub>2</sub> interface as I<sub>CP</sub> was measured. Therefore, N<sub>it. SiO2</sub>/ HfO2 could be detected by I<sub>CP</sub> with 1 MHz. To illustrate by energy diagram, the electrons could tunnel from conduction band (ECB) into high-k layer, then gaining potential energy to impact interface of HfO<sub>2</sub>/SiO<sub>2</sub>, generating non-recovery broken bonds near that. According to continuity boundary conditions and the property of direct tunneling, we estimate the depth carriers could reach under stress voltage roughly as shown in the inset of Fig. 2. The result demonstrates that the stress condition can make carriers cross through  $\sim 14$  Å for SiO<sub>2</sub> dielectric layer under direct tunneling mechanism, showing the consistency of assumption we mentioned. Since HfO<sub>2</sub>/SiO<sub>2</sub> interface owns more incomplete or weak bonds between high-k and buffer oxide, the stress condition could induce more additional Nit, SiO2/HfO2, instead of Nit, Si/SiO2. In order to verify the impact-induced N<sub>it, SiO2/HfO2</sub> under PBS, we introduce AC voltage into experiment. Under AC stress,  $N_{it,\ SiO2/HfO2}$  should be degraded seriously as well as the amount of  $N_{it,\ SiO2/HfO2}$  could be increased as stress frequency increases. The stress condition was fixed  $V_G = 2V + V_{FB}$  for frequency range of 1 kHz~1 MHz to assure the corresponding result. Figure 3 shows the SS and I<sub>CP</sub> degradation for TiN/ HfO<sub>2</sub> p-MOSFETs under PBS with different frequencies. Obviously, the I<sub>CP</sub> degradation becomes more significant as frequency increases, but SS degradation seems to be invariant regardless of modulating frequencies.

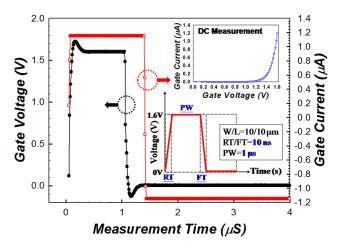

This is because under AC stress, carrier could be accelerated and released repeatedly to enhance the probability of collision at  $HfO_2/SiO_2$  interface, and the reduction of stress electric field due to interfacial ( $N_{it, SiO2/HfO2}$ ) trapping is insignificant than that under DC stress. Figure 4 shows  $I_G$  measurement by single pulse with period width (PW) 1  $\mu$ s (0.5 MHz). It can be found that the corresponding gate current forms a rectangular wave with 1.3  $\mu$ A. To compare gate current with the DC measurement as shown in the inset of Fig. 4, it shows a consistent value at gate voltage = 1.6 V, proving that electrons can transport from substrate to gate

FIG. 3. The PBS-induced  $I_{CP}$  and SS degradation for TiN/HfO<sub>2</sub> p-MOSFETs were plotted as a function of AC stress frequency ranging of 0 Hz, 1 kHz, 100 kHz, and 1 MHz. The inset shows the corresponding energy band diagram for AC and DC stress condition.

FIG. 4.  $I_G$ - $V_G$  pulse characteristic curves of TiN/HfO<sub>2</sub> p-MOSFETs. The inset shows the pulse configuration and  $I_G$ - $V_G$  characteristic curves under DC measurement.

under AC voltage, and without current decrease. Further, showing that impact ionization under AC stress is possible.

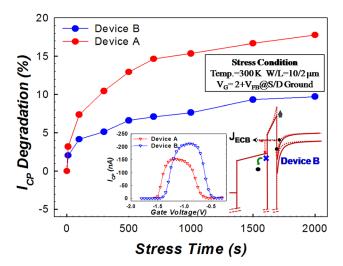

In detail, electrons can transport continuously from  $E_C$ to gate dielectric and result in electron trapping. After that, electron could be caught by N<sub>it, SiO2/HfO2</sub>, influencing in the energy band near SiO2 as shown in the peak voltage (+2V) in inset of Fig. 3. Due to transport continuously, interfacial electron trapping (Nit, SiO2/HfO2) could occur constantly, even though electric field makes electrons tends toward gate by Poole-Frenkel emission. However, there is a transform of trapping behavior from interfacial states to deep states for AC condition, since AC stress exhibits peak (+2V) and base voltage (0V). For peak voltage, the behavior on device is identical to DC condition. As application of stress voltage goes through base voltage, trapped electrons in Nit. SiO2/HfO2 have sufficient time to enter deep traps as shown in the inset of Fig. 3. During long time term, reduction of electric field for DC stress condition is more significant than that for AC. 10 Thus, significant degradation should be under AC stress. Additionally, due to possible conduction of electron, worse degradation occurs under high frequency, meaning more amount of pulse induces significant impact ionization. To combine those two causes, I<sub>CP</sub> under AC stress shows more obvious degradation than that under DC. Besides, since the direct tunneling mechanism does not influence channel interface, thereby SS shows an insignificant degradation under AC PBS. Furthermore, we also compare the degradation mechanism of I<sub>CP</sub> under PBS for TiN/HfO<sub>2</sub> p-MOSFETs with more pre-existing N<sub>it, Si/SiO2</sub> (device B) as shown in Figure 5. It could be seen that I<sub>CP</sub> decay curve of device B is more insignificant than that of device A under PBS, indicating that device B has less pre-Nit, Si/SiO2. However, stress condition V<sub>G</sub> is given a correction term to achieve identical stress field, therefore the result should be consistent. But the experimental data are not consistent with this assumption. According to that, the stress electric field for device B is lower than device A is suggested. Clearly to explain, device B has a field screen by pre-N<sub>it. Si/SiO2</sub> to decrease stress electric field. As electrons are accelerated toward gate by stress electric field, pre-N<sub>it. Si/SiO2</sub> could trap carriers randomly, reducing stress electric field as shown in

FIG. 5. The PBS-induced  $I_{CP}$  and SS degradation for TiN/HfO<sub>2</sub> p-MOSFETs with different SiO<sub>2</sub>/Si  $N_{it}$  under PBS (devices A and B). The inset shows the corresponding energy band diagram for device B under stress and the  $I_{CP}$  curve versus  $V_G$  before stress with measurement condition f=5 MHz.

the inset of Fig. 5. Because of that, it can results in insignificant impact ionization, also leading less  $N_{\rm it,\ SiO2/HfO2}$  in device B.

This Letter investigates the degradation of TiN/HfO<sub>2</sub> p-MOSFETs under off-state stress. Clearly, electron trapping behavior dominates the characteristic of device, including positive V<sub>th</sub> shift, decrease in I<sub>D</sub> but without SS. However, I<sub>CP</sub> measurement shows an inconsistent result with SS, and we believe that the signal reflect the defect generation at HfO<sub>2</sub>/SiO<sub>2</sub> due to impact ionization. According to simple estimation, carriers can result impact near HfO<sub>2</sub>/SiO<sub>2</sub> interface. And we found that I<sub>CP</sub> degradation increases as frequency of AC voltage increases. This is because increase probability of collision at HfO2/SiO2 interface, and then the behavior of electric field lowering is insignificant. Therefore, the degradation increases with frequency increases, supporting the model we proposed. Further, the influence of preexisting  $N_{it,\ SiO2/HfO2}$  under PBS was discussed. The pre- $N_{it,\ }$ Si/SiO2 can screen the stress field to reduce degradations of device due to interfacial charge trapping.

Part of this work was performed at United Microelectronics Corporation. The work was supported by the National Science Council under Contract NSC99-2120-M-110-001 and NSC-97-2112-M-110-009-MY3.

<sup>&</sup>lt;sup>1</sup>D. A. Buchanan, IBM J. Res. Dev. **43**, 245 (1999).

<sup>&</sup>lt;sup>2</sup>G. Ribes, J. Mitard, M. Denais, S. Bruyere, F. Monsieur, C. Parthasarathy, E. Vincent, and G. Ghibaudo, IEEE Trans. Device Mater. Reliab. 5, 5 (2005).

<sup>&</sup>lt;sup>3</sup>Y. Kim, G. Gebara, M. Freiler, J. Barnett, D. Riley, J. Chen, K. Torres, J. E. Lim, B. Foran, F. Shaapur, A. Agarwal, P. Lysaght, G. A. Brown, C. Young, S. Borthakur, H. J. Li, B. Nguyen, P. Zeitzoff, G. Bersuker, D. Derro, R. Bergmann, R. W. Murto, A. Hou, H. R. Huff, E. Shero, C. Pomarede, M. Givens, M. Mazanec, and C. Werkhoven, Tech. Dig. - Int. Electron Devices Meet. **2001**, 455.

<sup>&</sup>lt;sup>4</sup>C. Hobbs, H. Tseng, K. Reid, B. Taylor, L. Dip, L. Hebert, R. Garcia, R. Hegde, J. Grant, D. Gilmer, A. Franke, V. Dhandapani, M. Azrak, L. Prabhu, R. Rai, S. Bagchi, J. Conner, S. Backer, F. Dumbuya, B. Nguyen, and P. Tobin, Tech. Dig. - Int. Electron Devices Meet. 2001, 651.

<sup>&</sup>lt;sup>5</sup>M. Casse, L. Thevenod, B. Guillaumot, L. Tosti, F. Martin, J. Mitard, O. Weber, F. Andrieu, T. Ernst, G. Reimbold, T. Billon, M. Mouis, and F. Boulanger, IEEE Trans. Electron Devices 53, 759 (2006).

- <sup>6</sup>E. P. Gusev, in *The Physics and Chemistry of SiO*<sub>2</sub> and the Si-SiO<sub>2</sub> Interface 4 (Electrochemical Society, 2000), p. 477.

- S. Zafar, A. Callegari, E. Gusev, and M. V. Fischetti, J. Appl. Phys. 93, 9298 (2003).

- <sup>8</sup>C. H. Dai, T. C. Chang, A. K. Chu, Y. J. Kuo, W. H. Lo, S. H. Ho, C. E. Chen, J. M. Shih, H. M. Chen, B. Shan Dai, G. Xia, O. Cheng, and C. T. Huang, Appl. Phys. Lett. 98, 092112 (2011).

- <sup>9</sup>C. H. Dai, T. C. Chang, A. K. Chu, Y. J. Kuo, Y. C. Hung, W. H. Lo, S. H. Ho, C. E. Chen, J. M. Shih, W. L. Chung, H. M. Chen, B. S. Dai, T. M. Tsai, G. Xia, O. Cheng, C. T. Huang, Thin Solid Film 520, 1511 (2011).

- <sup>10</sup>W. H. Lo, T. C. Chang, J. Y. Tsai, C. H. Dai, C. E. Chen, S. H. Ho, H. M. Chen, O. Cheng, and C. T. Huang, Appl. Phys. Lett. **100**, 152102 (2012).

- <sup>11</sup>C. H. Dai, T. C. Chang, A. K. Chu, Y. J. Kuo, S. H. Ho, T. Y. Hsieh, W. H. Lo, C. E. Chen, J. M. Shih, W. L. Chung, B. S. Dai, H. M. Chen, G. Xia, O. Cheng, and C. T. Huang, Appl. Phys. Lett. 99, 012106 (2011).

- <sup>12</sup>S. H. Ho, T. C. Chang, C. W. Wu, W. H. Lo, C. E. Chen, J. Y. Tsai, H. P. Luo, T. T. Tseng, O. Cheng, C. T. Huang, and Simon M. Sze, Appl. Phys. Lett. **101**, 052105 (2012).

- <sup>13</sup>C. H. Dai, T. C. Chang, A. K. Chu, J. Y. Kuo, S. H. Ho, T. Y. Hsieh, W. H. Lo, C. E. Chen, J. M. Shih, W. L. Chung, B. S. Dai, H. M. Chen, G. Xia, O. Cheng, and C. T. Huang, J. Electrochem. Soc. 15(6), H211–H214 (2012).

- <sup>14</sup>W. H. Wu, B. Y. Tsui, M. C. Chen, Y. T. Hou, Y. Jin, H. J. Tao, S. C. Chen, and M. S. Liang, IEEE Trans. Electron Device 54(6), 1330 (2007).

- <sup>15</sup>M. B. Zahid, R. Degraeve, M. Cho, L, Pantisano, D. R. Aguado, J. V. Houdt, G. Groeseneken, and M. Jurczak, in 47th IEEE IRPS (2009), pp. 21–25.