# A Novel Approach to Compact Model Parameter Extraction for Excimer Laser Annealed Complementary Thin Film Transistors

### YIMING LI

Department of Communication Engineering, National Chiao Tung University, Hsinchu 300, Taiwan; Microelectronics and Information Systems Research Center, National Chiao Tung University, Hsinchu 300, Taiwan

ymli@faculty.nctu.edu.tw

#### SHAO-MING YU

Department of Computer and Information Science, National Chiao Tung University, Hsinchu 300, Taiwan

**Abstract.** A unified physical-based model parameter extraction technique for excimer laser annealed lower temperature polycrystalline silicon (LTPS) complementary thin film transistors (TFTs) is for the first time proposed. For two well-known compact models of LTPS TFT, Rensselaer Polytechnic Institute (RPI) V1 and V2 models, our approach sequentially optimizes the model parameters in the regions of linear, subthreshold, saturation, and leakage. Compared with the measured results, the extracted  $I_D - V_G$ ,  $I_D - V_D$ , transconductance, and output conductance are within 3% of accuracy. The agreement with the experimental data is excellent for the n- and p-type LTPS TFTs with different length and width. This extraction technique bridges the fabrication of LTPS TFTs and the design of complementary system on panel circuits.

**Keywords:** LTPS TFT, compact model, RPI V1 and V2 models, parameter extraction technique, optimization

### 1. Introduction

Excimer laser annealing technique has recently been proposed in the fabrication of LTPS TFTs, in particular for active matrix liquid crystal display (AMLCD) [1–7] and system on panel (SOP). Equivalent circuit models, such as RPI V1 and V2 models [4–6] are important for designing the embedded driving circuits in LCDs with laser annealed LTPS TFTs. The RPI V1 model involves piecewise functions and the RPI V2 model has improved some nonphysical effects. Any computationally effective and physical-based extraction techniques will benefit the semiconductor display industry. Unfortunately, it is still lacking a unified, robust, and accurate optimization technique to extract RPI TFT models' parameters.

In this paper, we successfully develop a unified model parameter extraction technique for the parameter extraction of LTPS TFTs. Based on the physical properties of the LTPS TFTs and the mathematical behaviors of the RPI compact models [7-9], our approach sequentially optimizes the model parameters in the regions of linear, subthreshold, saturation, and leakage. For a set of given measured data, extraction of  $I_D - V_G$ ,  $I_D - V_D$ , transconductance  $(G_m)$ , and output conductance  $(G_{ds})$  is simultaneously performed with numerical optimization technique [9]. Compared with the measured results, the extraction is within 3% of accuracy. Extraction of several fabricated n- and p-type LTPS TFTs with different dimensions is verified with the proposed method. Optimization experience shows this approach is robust and accurate for the parameter extraction of RPI V1 and V2 models. This method can be implemented in electronic computer aided design (ECAD) tool for TFT model parameter extraction, and therefore can provide the necessary parameters for AMLCD product design and SOP circuit simulation.

This article is organized as follows. Section 2 states the extraction procedure of the RPI V1 and V2 models for LTPS TFTs. Section 3 shows the extraction results of LTPS TFTs. Section 4 draws conclusions.

# 2. The Parameter Extraction Technique

The drain to source current, used in the RPI V1 and V2 models [4–6], is given by  $(\frac{I_a \times I_{\text{sub}}}{I_a + I_{\text{sub}}} + I_{\text{leak}}) \times (1 + \Delta \text{kink})$ . When the gate bias is greater than the threshold voltage,  $I_a$  becomes significant. Similarly, the leakage and subthreshold regions can be identified separately. According to this observation, the proposed extraction technique consists of the following several steps to complete the model parameter extraction. A set of mobility parameters is firstly optimized for the linear region of  $I_D - V_G$  curves. The optimization kernel is with the Levenberg-Marquardt algorithm [9]. It is a trust-region modification of the Gauss-Newton algorithm. We then extract the threshold regions of  $I_D - V_G$  curves by choosing the parameters of zero bias threshold voltage and subthreshold. For the parameters of saturation, DIBL and kink effect, we thirdly extract the saturation region of  $I_D - V_D$  curves. Finally, we optimize the leakage region of  $I_D - V_G$  in the log scale. All notations and physical meanings follow [6]. To run a complete extraction, there are more than 200 I-V points have to be optimized, simultaneously. A programming procedure corresponding to the extraction technique is shown below.

# The Proposed Extraction Procedure Begin

Load(measurement data) Select(model:RPI V1 or V2 model) For linear region of  $I_D - V_G$  curves Extract(mobility parameters: MMU and MU0) End For For subthreshold region of  $I_D - V_G$  curves Extract(zero bias threshold voltage and subthreshold parameters:

```

VTO and ETA)

End For

For saturation region of I_D - V_D

curves

Extract(saturation and DIBL

parameters: ASAT, VST, VSI

and VST (for V1 model)

ASAT and VMAX (for V2 model))

Extract(kink effect parameters:

VKINK)

End For

For leakage region of I_D - V_G

curves

Extract(leakage region parameters:

IO, IOO, DD and DG)

End For

Output(extracted parameters)

End The Proposed Extraction Procedure

```

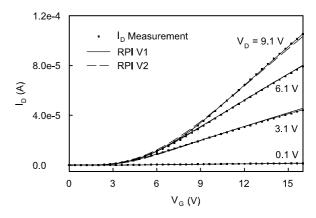

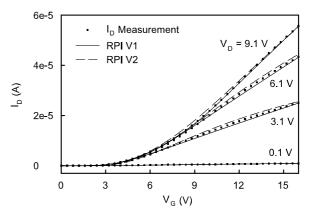

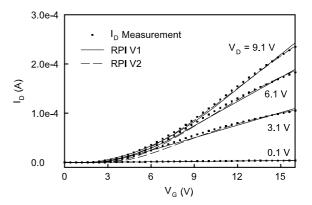

Figure 1.  $I_D - V_G$  characteristics of the *n*-type sample.

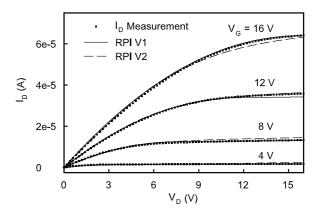

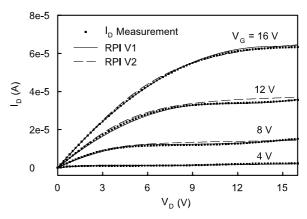

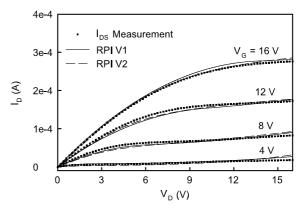

Figure 2.  $I_D - V_D$  characteristics of the *n*-type sample.

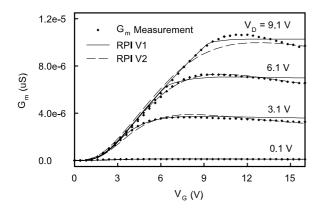

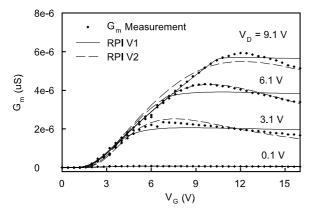

Figure 3. Transconductance of the *n*-type sample.

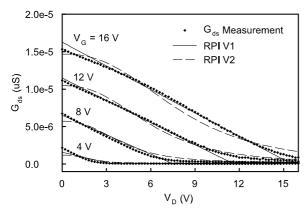

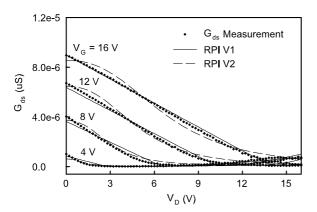

Figure 4. Output conductance of the *n*-type sample.

### 3. Results and Discussion

The length and width of fabricated n- and p-type laser annealed LTPS TFTs are equal to 6  $\mu$ m and the oxide thickness is equal to 100 nm.  $I_D - V_G$ ,  $I_D - V_D$ ,  $G_m$ , and  $G_{ds}$  are examined with respect to the n- and p-type samples. Figures 1–8 show the comparison among measurement, extraction with RPI V1 model, and extraction with RPI V2 model, where dots are the measurement, lines are the result of RPI V1 model, and dashes are the outcome of RPI V2 model, respectively. Comparisons show that the maximum RMS error of extracted physical quantities is less than 3%. Comparison confirms that the RPI V2 model does have more accurate prediction of the LTPS TFTs' characteristics. Figures 1–4 are the results of the fabricated and measured *n*-type LTPS TFT, respectively.

For the fabricated *p*-type LTPS TFT, the current-voltage, transconductance, and output conductance are

Figure 5.  $I_D - V_G$  characteristics of the p-type sample.

Figure 6.  $I_D - V_D$  characteristics of the p-type sample.

shown in Figs. 5–8, respectively. For  $I_D - V_G$  and  $I_D - V_D$ , comparison among three results are with good accuracy. However, compared with the results of n-type sample,  $G_m$  of p-type LTPS TFT, shown in Fig. 7, is much poor due to the intrinsic limitation of the RPI TFT model. One of reason is that the RPI mobility function fails at the high gate bias conditions [7]. Therefore,  $G_m$  calculated by the RPI V1 and V2 models with their associated mobility function loses the accuracy at the high gate biased condition. The error is increased when the drain bias is increased.

The RPI TFT model overestimates the current level at the high gate biases and underestimates drain current at the low gate bias conditions. The RPI V2 model has improvement in the pare, but we believe that a physical-based mobility model is still necessary for LTPS TFTs' simulation [7]. To verify the validity of the extraction technique, we also test the extraction for the LTPS TFT with different dimensions. Figures 9 and 10 show the

Figure 7. Transconductance of the *p*-type sample.

Figure 8. Output conductance of the *p*-type sample.

extracted  $I_D - V_G$  and  $I_D - V_D$  curves of the *p*-type LTPS TFT. The second sample is with W/L = 8/4 [ $\mu$ m/ $\mu$ m], respectively.

# 4. Conclusions

A unified physical-based model parameter extraction technique for LTPS TFTs has been successfully developed. By investigating the RPI V1 and V2 models, we have compared the simulation results with the measured data. After our optimization, the RPI V1 and V2 models have shown their accuracy. It has been found that the accuracy of the LTPS TFT models can be further improved. This extraction technique can be incorporated into ECAD tool for display industry and is useful in complementary SOP circuit simulation. For multi LTPS TFTs, development of advanced compact model and corresponding parameter optimization technique are the most important issues. We are currently

Figure 9.  $I_D - V_G$  characteristics of the second p-type sample.

Figure 10.  $I_D - V_D$  characteristics of the second p-type sample.

working on intelligent optimization algorithms [8,9] for LTPS TFT parameter extraction.

### Acknowledgments

This work is supported in part by TAIWAN national science council (NSC) under contract No. NSC-93-215-E-429-008, NSC-93-2752-E-009-002-PAE, and the grant of the Ministry of Economic Affairs, Taiwan under contracts No. 92-EC-17-A-07-S1-0011 and No. 93-EC-17-A-07-S1-0011. Authors also thank research grants in years 2004–2005 from the Toppoly optoelectronics Corp. in Miao-Li, Taiwan.

## References

- S. Jagar et al., "A SPICE model for thin-film transistors fabricated on grain-enhanced polysilicon film," *IEEE Trans. Electron Devices*, 50, 1103 (2003).

- 2. A. Wang and K.C. Saraswat, "A strategy for modeling of variations due to grain size in polycrystalline

- thin-film transistors," *IEEE Trans. Electron Devices*, **47**, 1035 (2000).

- G.A. Armstrong et al., "Modeling of laser-annealed polysilicon TFT characteristics," *IEEE Electron Device Letters*, 18, 315 (1997).

- M.S. Shur et al., "Modeling and scaling of a-Si:H and poly-Si Thin Film transistors," in *Material Research Society Pro*ceeding, Amorphous and Microcrystalline Silicon Technology, (1997) vol. 467.

- 5. B. Iniguez et al., "Unified model for short-channel poly-Si TFTs," *Solid-State Electronics*, **43**, 1821 (1999).

- "TFT ProTractor User's Manual," SeveTek Inc., 1.1.0, 58 (2004).

- H.-Y. Lin et al., "A unified mobility model for excimer laser annealed complementary thin film transistors simulation," *Tech. Proc. NSTI Nanotech. Conf.*, 2, 13 (2004).

- Y. Li et al., "A genetic algorithm approach to InGaP/GaAs HBT parameters extraction and RF characterization," *Jpn. J. Appl. Phys.*, 42, 2371 (2003).

- Y. Li et al., "Intelligent BSIM4 model parameter extraction for Sub-100 nm MOSFETs era," *Jpn. J. Appl. Phys.*, 43, 1717 (2004).