# Novel 2-Bit/Cell Wrapped-Select-Gate SONOS TFT Memory Using Source-Side Injection for NOR-Type Flash Array

Kuan-Ti Wang, Fang-Chang Hsueh, Yu-Lun Lu, Tsung-Yu Chiang, Yi-Hong Wu, Chia-Chun Liao, Li-Chen Yen, and Tien-Sheng Chao

Abstract—This letter is the first to successfully demonstrate the 2-bit/cell wrapped-selected-gate (WSG) SONOS thin-film transistor (TFT) memory using source-side injection (SSI). Because of the higher programming efficiency of SSI, a memory window of approximately 3 V can be easily achieved in 10  $\mu$ s and 30 ms for the program and erase modes, respectively. In addition, we performed an excellent 2-bit/cell distinguish margin for 3-V memory window in WSG-SONOS TFT memory. The optimal reliability of the endurance and data retention tests can be executed by adjusting the applied voltage appropriately.

Index Terms—Source-side injection (SSI), thin-film transistor memory, two-bit/cell, wrapped-selected-gate (WSG)-SONOS.

# I. INTRODUCTION

THE advantage of polycrystalline silicon (poly-Si) thinfilm transistors (TFTs) is that it can integrate additional functionality into system-on-glass (SOG) and systemon-chip (SOC) [1], including driver electronics, peripheral circuits, and memory devices. A poly-Si memory device with high performance on a multifunction system plays a vital role because embedded memory is used to assist the logic function and microcontroller. In addition, the 2-bit/cell application of SONOS TFT memory device is also a widely used method to effectively increase 2× density without increasing the device area [2]. This letter presents a TFT nonvolatile memory device using a wrapped-select-gate (WSG) structure to accomplish the 2-bit/cell with high performance requirements of the embedded memory device. This letter is also the first to verify that sourceside injection (SSI) can be achieved in a WSG-SONOS TFT memory device [3].

## II. EXPERIMENTAL

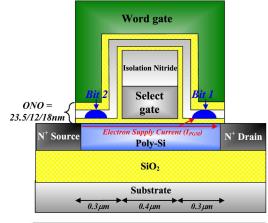

Fig. 1 shows the cross section of WSG-SONOS TFT memory with 2-bit/cell operation. It shows that the WSG gate is wrapped around isolated nitride and oxide to achieve a physically separated 2-bit and SSI program method in the

Manuscript received February 12, 2012; accepted March 19, 2012. Date of publication May 3, 2012; date of current version May 18, 2012. This work was supported in part by the National Science Council of Taiwan under Contract NSC-95-2221-E-009-272 and in part by MOE-ATU. The review of this letter was arranged by Editor M. Jurczak.

The authors are with the Department of Electrophysics, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: tschao@mail.nctu.edu.tw).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2012.2192090

| WSG-SONOS TFT Memory (2 Bit/Cell) |         |                            |                           |                |          |  |  |

|-----------------------------------|---------|----------------------------|---------------------------|----------------|----------|--|--|

| Bit 1<br>operation                | Mode    | $\mathbf{v}_{\mathbf{wL}}$ | $\mathbf{v}_{\mathbf{D}}$ | $\mathbf{V_S}$ | $V_{SG}$ |  |  |

| Program                           | SSI     | 18V                        | 8V                        | 0V             | 0.6V     |  |  |

| Erase                             | втвтнн  | -8V                        | 18V                       | 0V             | 0V       |  |  |

| Read                              | Reverse | 0~8V                       | <b>0V</b>                 | 6V             | 4V       |  |  |

Fig. 1. Cross section with SSI operation scheme under 2-bit/cell mode of WSG-SONOS TFT memory.

proposed device. First, the device was fabricated on a silicon wafer with 5500-Å wet oxide, which is used to simulate glass substrate. Subsequently, a 500-Å amorphous Si (a-Si) film for the channel region was deposited at 500 °C by low-pressure chemical vapor deposition. After patterning, the deposited a-Si films were crystallized by solid-phase crystallization at 600 °C for 24 h. To form the embedded assistant gate, we deposited 180-Å TEOS oxide, 1000-Å in situ N<sup>+</sup> poly-Si layer, and 1000-Å isolated nitride, which is used to isolate select the gate and word gate. After WSG patterning, the thin-film thickness of the tunnel oxide, nitride trapping layer, and blocking oxide (ONO) stacks was deposited by horizontal furnace with 180, 120, and 235 Å, respectively. Followed by the 2000-Å word gate poly-Si deposition and pattern, the gate and source/drain regions were formed by the self-alignment implant technique. After source/drain activation, passivation oxide and back-end processes were performed. The WSG-SONOS TFT memory channel length and width were 1 and 10  $\mu$ m, respectively. The length of the WSG was 0.4  $\mu$ m. The threshold voltage of the device was defined by the constant current method  $(10^{-7} \text{ A})$  in the reverse read mode.

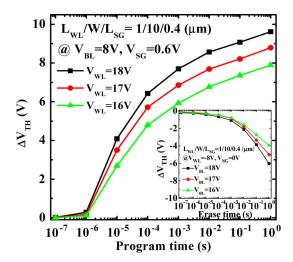

Fig. 2. High program speed of 2-bit/cell WSG-SONOS TFT memory in SSI mode. The inset figure shows erase speed. In our proposed method,  $V_{\rm TH}$  of WSG-SONOS TFT memory is extracted by the constant current method (0.1  $\mu$ A) with reverse read mode.

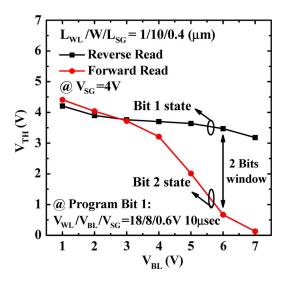

Fig. 3. SSI operation of 2-bit/cell characteristics of WSG-SONOS TFT memory under forward read and reverse read, respectively.

# III. RESULTS AND DISCUSSIONS

SSI was used to accomplish TFT 2-bit/cell operation in the program mode. The programming characteristic of the WSG-SONOS TFT memory is shown in Fig. 2. A  $\Delta V_{\rm TH}=3$  V can be achieved by  $V_{\rm WL}=18$  V,  $V_{\rm BL}=8$  V, and  $V_{\rm SG}=0.6$  V in 10  $\mu \rm s$ . In addition, the higher word gate voltage can also improve programming speed because of its higher electric field in the neutral gap region [4]. It indicates that the charge density of the inversion layer may be formed higher to pass  $V_{\rm BL}$  to stride across the neutral region easily. The inset figure also shows the erasing characteristic dependence on  $V_{\rm BL}$ . We used band-to-band-tunneling hot holes to recombine the electrons stored in the nitride trapping layer.  $\Delta V_{\rm TH}=3$  V can be also easily achieved by applying  $V_{\rm WL}=-8$  V,  $V_{\rm BL}=18$  V, and  $V_{\rm SG}=0$  V in 30 ms.

Fig. 3 shows the 2-bit/cell operation characteristics with a different  $V_{\rm BL}$ . The reverse read was widely used in 2-bit/cell operation to electrically separate the 2 bit. The charge screen effect can be gradually increased in conjunction with the bit-

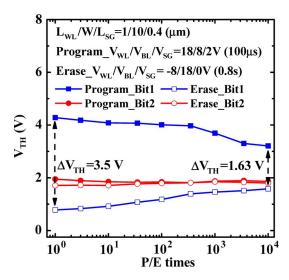

Fig. 4. Endurance characteristics with 2-bit/cell operation of WSG-SONOS TFT memory, including bit 1 and bit 2, and cycling up to  $10^4 \times$ . The memory window of bit 1 can still maintain at 1.6 V even after  $10^4$  cycling stress, almost no variation at bit 2.

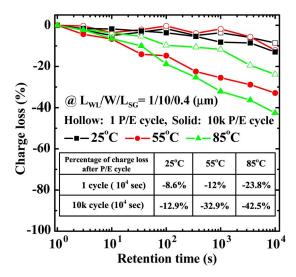

Fig. 5. Data retention characteristics with SSI operation under different baking temperatures from 25  $^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$ , respectively. The cells are uncycled and  $10^4$  cycled, respectively.

line voltage because of reverse bias application on p-n junction (substrate to source/drain). The result indicates that our WSG-SONOS TFT accomplished 2-bit/cell operation in 10  $\mu$ s with 3-V difference memory windows.

Fig. 4 shows the endurance characteristics up to  $10^4 \times$ , including bit 1 and bit 2. The erase state of bit 1 increased with repeated cycling up to  $10^4 \times$ , indicating incomplete erasure [5], or more interfacial state generation in the bottom oxide [6]. Conversely, the program state of bit 1 decreased while increasing the P/E cycling test. The memory window maintained more than 1.6 V even after  $10^4$  cycles. In addition, the program and erase states of bit 2 exhibited almost no variation even after  $10^4$  cycling tests of bit 1. This verified that our WSG-SONOS TFT structure exhibited excellent electrical characteristics to separate two physical bits.

Fig. 5 shows the data retention characteristics after  $10^4$  s with programming state after  $10^4$  P/E cycles at 25 °C, 55 °C, and 85 °C baking temperatures. The charge loss behavior of the

| TABLE I                                                |

|--------------------------------------------------------|

| COMPARISON TABLE OF ADVANCED TFT TECHNOLOGIES INCLUDES |

| TFT AND BULK WSG-SONOS MEMORY DEVICE                   |

| TFT<br>Structure                | Program<br>mode                                    | Erase<br>mode                        | Memory<br>window    | Charge<br>Lost   | Cycle<br>Test                     |

|---------------------------------|----------------------------------------------------|--------------------------------------|---------------------|------------------|-----------------------------------|

| SOHOS<br>Memory<br>Ref. [8]     | V <sub>G</sub> =12V<br>V <sub>D</sub> =12V<br>1ms  | $V_G$ =-10V<br>$V_D$ =10V<br>10ms    | 3V<br>2 bit/cell    | 43%<br>@ 85°C    | ~1.87V<br>@10 <sup>4</sup> cycles |

| Nanowire<br>Memory<br>Ref. [9]  | V <sub>G</sub> =18V<br>1ms                         | V <sub>G</sub> =-18V<br>1s           | 3.5V<br>1 bit/cell  | 31.25%<br>@ 85°C | ~1.5V<br>@10 <sup>6</sup> cycles  |

| SLS<br>Memory<br>Ref. [10]      | V <sub>G</sub> =18V<br>V <sub>D</sub> =12V<br>10ms | $V_G$ =-8V<br>$V_D$ =20V<br>10ms     | 2.22V<br>1 bit/cell | N/A              | N/A                               |

| WSG-<br>SONOS<br>(This Paper)   | $V_G=18V$ $V_D=8V$ $100\mu s$                      | $V_{G}$ =-8V<br>$V_{D}$ =18V<br>0.8s | 3.5V<br>2 bit/cell  | 42.5%<br>@ 85°C  | ~1.6V<br>@10 <sup>4</sup> cycles  |

| Bulk WSG-<br>SONOS<br>Ref. [11] | $V_{ m G}$ =9-11V<br>$V_{ m D}$ =4V<br>10 $\mu$ s  | $V_G$ =-4V<br>$V_D$ =6V<br>5ms       | 1-3V<br>4 bit/cell  | 3%<br>@ 85°C     | 1-3V<br>@10 <sup>4</sup> cycles   |

storage layer of WSG-SONOS TFT was considerable after 10<sup>4</sup> cycling test with 85 °C baking temperature. The higher baking temperature can assist the electrons to overcome the activation energy to discharge from the nitride trapping layer [7]. The interface state and tunneling oxide traps can also help discharge the electrons by the trap-assist tunneling mechanism, particularly for the devices after 10<sup>4</sup> P/E cycles stress [6]. The inset table in Fig. 5 shows the percentage of charge loss with various baking temperatures under unity P/E cycle and 10<sup>4</sup> P/E cycles after 10<sup>4</sup> s. It indicates that the quality of tunneling/blocking oxide plays a vital role in reliability issues of the WSG-SONOS TFT memory device for providing optimal stress immunity. The reliability of the WSG-SONOS TFT memory device can be improved once the strength of the tunneling/blocking oxide or embedded silicon dots are effectively increased in the nitride trapping layer. Table I shows the comparison to the other advanced TFT memory technologies, i.e., bulk and TFT WSG-SONOS memory devices [8]-[11]. It verifies that this WSG-SONOS TFT memory with good electrical characteristic has a high potential for embedded memory application on SOG.

# IV. CONCLUSION

We have first demonstrated a 2-bit/cell operation WSG-SONOS TFT memory device using SSI and band-to-band-tunnel hot-hole erasing. The fast program/erase speed can be achieved in  $10~\mu\text{s}/30~\text{ms}$  for a memory window that is equal to 3 V. Moreover, the memory window can maintain more

than 1.6 V even after  $10^4$  P/E endurance tests. In addition, the percentage of charge loss was lower than 13% even after  $10^4$  s with  $10^4$  P/E endurance tests at 25 °C. Consequently, the WSG-SONOS TFT memory device is a potential candidate for future SOG or SOC systems because of its excellent performance and reliability.

### ACKNOWLEDGMENT

The authors would like to thank the National Nano Device Laboratories for procedural support, as well as the Nano Facility Center of National Chiao Tung University.

#### REFERENCES

- [1] T. Nishibe and H. Nakamura, "Value-added circuit and function integration for SOG (system-on-glass) based on LTPS technology," *SID Symp. Dig. Tech. Papers*, vol. 37, no. 1, pp. 1091–1094, 2006.

- [2] B. Eitan, P. Pavan, I. Bloom, E. Aloni, A. Frommer, and D. Finzi, "NROM: A novel localized trapping 2-bit nonvolatile memory cell," *IEEE Electron Device Lett.*, vol. 21, no. 11, pp. 543–545, Nov. 2000.

- [3] A. T. Wu, T. Y. Chan, P. K. Ko, and C. Hu, "A novel high-speed, 5-volt programming EPROM structure with source-side injection," in *IEDM Tech. Dig.*, 1986, pp. 584–587.

- [4] K. T. Wang, T. S. Chao, T. Y. Chiang, W. C. Wu, P. Y. Kuo, Y. H. Wu, Y. L. Lu, C. C. Liao, W. L. Yang, C. H. Lee, T. M. Hsieh, J. C. Liou, S. D. Wang, T. P. Chen, C. H. Chen, C. H. Lin, and H. H. Chen, "Physical mechanism of high programming efficiency dynamic threshold source side injection (DTSSI) in wrapped-select-gate SONOS (WSG-SONOS) for NOR-type flash memory," *IEEE Electron Device Lett.*, vol. 30, no. 11, pp. 1206–1208, Nov. 2009.

- [5] M. K. Cho and D. M. Kim, "Simultaneous hot-hole injection at drain and source for efficient erase and excellent endurance in SONOS flash EEPROM cells," *IEEE Electron Device Lett.*, vol. 24, no. 4, pp. 260–262, Apr. 2003.

- [6] J. Bu and M. H. White, "Retention reliability enhanced SONOS NVSM with scaled programming voltage," in *Proc. IEEE Aerosp. Conf.*, 2002, vol. 5, pp. 5-2383–5-2390.

- [7] Y. Yang and M. H. White, "Charge retention of scaled SONOS nonvolatile memory devices at elevated temperatures," *Solid State Electron.*, vol. 44, no. 6, pp. 949–958, Jun. 2000.

- [8] Y. H. Lin, C. H. Chien, T. H. Chou, T. S. Chao, and T. F. Lei, "Low temperature polycrystalline silicon thin film flash memory with hafnium silicate," *IEEE Trans. Electron Devices*, vol. 54, no. 3, pp. 531–536, Mar. 2007.

- [9] S. H. Chen, T. C. Chang, P. T. Liu, Y. C. Wu, P. S. Lin, B. H. Tseng, J. H. Shy, S. M. Sze, C. Y. Chang, and C. H. Lien, "A novel nanowire channel poly-Si TFT functioning as transistor and nonvolatile SONOS memory," *IEEE Electron Device Lett.*, vol. 28, no. 9, pp. 809–811, Sep. 2007.

- [10] S. İ. Hsieh, H. T. Chen, Y. C. Chen, C. L. Chen, and Y. C. King, "MONOS memory in sequential laterally solidified low-temperature Poly-Si TFTs," IEEE Electron Device Lett., vol. 27, no. 4, pp. 272–274, Apr. 2006.

- [11] W. C. Wu, T. S. Chao, W. C. Peng, W. L. Yang, J. C. Wang, J. H. Chen, C. S. Lai, T. Y. Yang, C. H. Lee, T. M. Hsieh, and J. C. Liou, "High reliable multilevel and 2 Bit/Cell operation of wrapped select gate (WSG) SONOS memory," *IEEE Electron Device Lett.*, vol. 28, no. 3, pp. 214–216, Mar. 2007.