ELSEVIER

Contents lists available at SciVerse ScienceDirect

## Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

# The effects of oxygen annealing on the electrical characteristics of hydrothermally grown zinc oxide thin-film transistors

Jyh-Liang Wang a,\*, Po-Yu Yang b, Tsang-Yen Hsieh a, Chuan-Chou Hwang a, Der-Chi Shye a, I-Che Lee b

## ARTICLE INFO

Article history:

Available online 3 July 2012

Keywords: Zinc oxide (ZnO) Hydrothermal growth (HTG) Thin-film transistors (TFTs) Oxygen annealing Lateral-grain growth

## ABSTRACT

High-performance transparent zinc oxide (ZnO) thin-film transistors (TFTs) with location-controlled lateral-grain growth were fabricated by hydrothermal method. The ZnO active channel was laterally grown with aluminum-doped ZnO (AZO) seed layer underneath the Ti/Pt film. Compare to the unannealed ZnO TFTs, the annealed devices reveal the high-quality ZnO layer with the compensated structural defects in the channel region after oxygen ambient annealing at 400 °C. Therefore, the superior device performances (i.e. the excellent filed-effect mobility of 9.07 cm²/V s, positive threshold voltage of 2.25 V, high on/off current ratio of  $\sim 10^6$ , and low gate leakage current of <1 nA) of hydrothermally grown ZnO TFTs can be achieved with oxygen ambient annealing.

© 2012 Elsevier Ltd. All rights reserved.

## 1. Introduction

Lately, zinc oxide (ZnO) has been attracting particular interest as a result of its remarkably optical and electronic properties. Its significantly optical transparency combined with an excellent electrical conductivity made ZnO as a promise material for the fabrication of optoelectronic devices [1-4]. ZnO is an n-type II-VI compound semiconductor, and it possesses a direct energy widebandgap (i.e. ~3.37 eV) at room temperature, a large exciton binding energy (i.e. ~60 meV), good photoelectric and piezoelectric properties, and high optical transparency for visible light [1]. ZnO has been investigated as an active channel layer for transparent thin film transistor (TFT) [2-4] and compared with organic TFTs [5–7] and amorphous silicon TFTs [8,9]. Essentially, the organic TFTs may degrade in atmospheric conditions [10,11] and amorphous silicon TFTs have been demonstrated for some limitations of optical applications, such as light sensitivity, light degradation and opaqueness [12]. On the contrary, ZnO TFTs disclose not only the high transparency within the visible-light spectra but also the relatively high field effect mobility, less light sensitivity, and excellent chemical and thermal stability [13], indicating the potentials of ZnO-based thin films applied in TFTs. The ZnO-based thin films have been prepared by various vacuum-based deposition techniques, for instance pulsed laser deposition (PLD) [2], sputtering [3], atomic layer deposition [4], and chemical vapor deposition (CVD) [14], which usually suffer the issues of expensive facilities, low throughput, complicated operating conditions and high energy

consumption. In contrast, a solution-based hydrothermal method has the advantages of low reaction temperature, low-cost facility, capabilities of large-area and uniform fabrication, and environmental friendliness [15]. Nevertheless, the low-temperature fabrication of hydrothermal ZnO thin films generally contain enormous structural defects (i.e. oxygen vacancies, oxygen interstitials, zinc vacancies, and zinc interstitials) [16]. The structural defects of metal oxide produce potential wells that can trap and affect the movement of carriers, and degrade device performances. Therefore, a post-annealing in oxygen ambience should be considered for device fabrication to inhibit the structural defects formed in processes [17–19]. In this work, a simple hydrothermal method was adopted for the ZnO thin film growth. The annealing effects and related devices performances of hydrothermally grown (HTG) ZnO TFTs are also addressed.

## 2. Experimental details

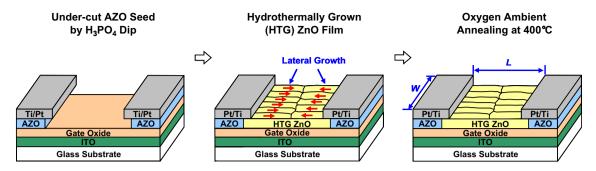

Fig. 1 illustrates the schematic fabrication of HTG ZnO TFTs with the technique of location-controlled nucleation. A 200 nm-thick sputtered indium—tin—oxide (ITO) film was sputtered as the gate electrode on the glass substrate. After cleaning, a 200 nm-thick tetraethylorthosilicate silicon dioxide (TEOS-SiO<sub>2</sub>) layer was deposited as gate dielectric by a plasma-enhanced chemical vapor deposition (PECVD) at 350 °C. Sputtered aluminum-doped ZnO (AZO) film (200 nm) and Ti (100 nm)/Pt (50 nm) films were sequentially deposited at room temperature and patterned by lift-off process. The sputtered AZO film can act as seed layer for ZnO growth during hydrothermal method. The samples were dipped in 0.001 M  $_{\rm H_3PO_4}$  to under-cut the AZO seed layer and then

<sup>&</sup>lt;sup>a</sup> Department of Electronics Engineering, Ming Chi University of Technology, New Taipei 24301, Taiwan

<sup>&</sup>lt;sup>b</sup> Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 30010, Taiwan

<sup>\*</sup> Corresponding author. Tel.: +886 2 29089899x4861; fax: +886 2 29085247. E-mail address: joewang@mail.mcut.edu.tw (J.-L. Wang).

Fig. 1. Schematic illustration for the fabrication of hydrothermal grown (HTG) ZnO TFTs with post-annealing at 400 °C for 1 h in oxygen ambience.

immersed in the mixed hydrothermal solution to grow the lateral ZnO film. The growth solution was prepared by mixing with 0.25 M zinc nitrate hexahydrate (Zn(NO<sub>3</sub>)<sub>2</sub>· 6H<sub>2</sub>O) with 0.25 M hexamethylenetetramine (HMTA) in deionized water at 85 °C for 3 h. Subsequently, the samples were thoroughly rinsed with deionized water in order to eliminate the residual salts and dried in air at room temperature. Finally, some of the samples were annealed in oxygen ambience to evaluate the annealing effects. The oxygen ambient annealing was executed in a tube furnace with the parameters as oxygen gas flow rate of 60 sccm, process pressure of  $\sim\!\!1$  atm, and annealing temperature of 400 °C for 1 h duration.

After TFTs formation, an automatic measurement system that combines IBM PC/AT, semiconductor parameter analyzer (4156C, Agilent Technologies) and a probe station were used to measure the I–V characteristics. The surface morphologies were observed by a field-emission scanning electron microscopy (FE-SEM, Hitachi S-4700I). The optical emission properties were analyzed by photoluminescence (PL) spectra with He–Cd laser (i.e.  $\lambda$  = 325 nm) excitation. An analytical field-emission transmission electron microscopy (JEM-2100FX, JEOL Ltd.) was employed to reveal the cross-sectional image and microstructure of the HTG ZnO layer in the channel region of ZnO TFTs. The samples of cross-sectional TEM were prepared by focused-ion-beam (FIB) technique (Nova 200, FEI Company), which can exactly locate and capture the channel region of ZnO TFTs.

## 3. Results and discussion

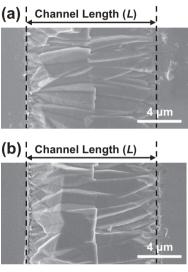

Fig. 2a and b gives the FE-SEM images for the channel morphology of HTG ZnO TFTs without or with annealing at 400 °C for one hour in oxygen ambience. The images of unannealed and annealed HTG ZnO TFTs reveal similar channel morphology. The ZnO growth only existed between the sputtered Ti/Pt electrodes and no ZnO thin film is observed on the electrodes. The location-controlled lateral growth started from the edges of AZO seed layer beneath the Ti/Pt films, and extended toward the middle of the channel from opposite both sides. The achievable distance of lateral growth using this hydrothermal method is about half channel length ( $\sim\!5~\mu m$ ) while the distance between source and drain is 10  $\mu m$ .

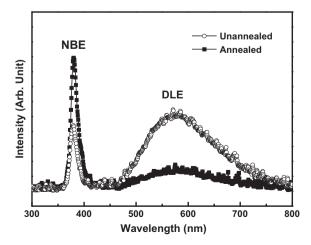

An analytical TEM technique was also conducted to display the cross-sectional image and microstructure in the channel region of annealed HTG ZnO layer, shown in Fig. 2c. The capping oxide layer was used to protect device structure from the bombardment damage induced by FIB during TEM sample preparation. The growth of HTG ZnO from opposite sides impinged with each other at the middle of the channel region above the gate oxide. The thickness of ZnO layer is not uniform and roughly estimated as 0.15–0.2 µm in the central channel region after 3 h HTG. The inset presents the selected area electron diffraction (SAED) pattern and corresponding high-resolution TEM (HRTEM) image for the selected district in HTG ZnO channel. Spot pattern of SAED indicates that HTG

**Fig. 2.** The FE-SEM images show the channel morphology of HTG ZnO TFTs (a) without or (b) with annealing at 400 °C for 1 h in oxygen ambience (c) cross-sectional TEM image reveals the vertical gain boundary cross to the channel of HTG ZnO TFTs. The inset presents the SAED pattern and corresponding HRTEM image for the selected district in HTG ZnO channel.

ZnO grains in the channel regions were single-crystalline wurtzite structure. Moreover, HRTEM image clearly reveals a well-resolved lattice image with an orientation along the [001] direction (c-axis of ZnO crystal) which is the fastest growth direction of ZnO crystals. It is evident that the location-controlled lateral grains grew from the opposite direction and collided at the middle of channel, resulting in nearly a single vertical grain boundary cross to the channel direction. In brief, the hydrothermally lateral-grain growth can be artificially controlled in the desired location and the vertical grain boundary perpendicular to the current flow in the channel region can be reduced to single one as a result of the proper design of source/drain structure with under-cut AZO seed layer. The localized potential barriers of grain boundaries could retard the transportation of carriers from grain to grain [20]. The presence of vertical grain boundary perpendicular to the current flow in the channel region of ZnO TFTs has a dramatic influence on the electrical characteristics. Thus, only single vertical grain boundary in channel region can be expected to make the advanced device performance of ZnO TFTs.

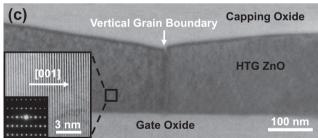

Fig. 3 shows the PL emission spectra of the unannealed and annealed HTG ZnO TFTs. The PL emission spectra are distinguished into two components: one is the UV emission owing to the near band-edge emission (NBE) [21], and the other is the deep level emission (DLE) in the visible region due to the existence of structural defects (i.e. oxygen vacancies, oxygen interstitials, zinc vacancies, and zinc interstitials) [22-24]. It is observed that the DLE intensity decreased and quenched after the annealing in oxygen ambience. The zinc interstitials can be rearranged and its number will be reduced by annealing process [17]. The oxygen vacancies also can be inhibited and compensated with oxygen ambience in thermal process [18]. As well, the increased NBE intensity can associate to the reduced structural defects. Hence, the relative PL intensity ratio of NBE intensity to DLE intensity  $(I_{NBE}/I_{DLE})$  was extracted to evaluate the structural defects and structural quality of HTG ZnO layers [23]. The values of  $I_{NRE}/I_{DLE}$ were calculated as 0.8 and 5.03 according to the unannealed and annealed samples. The higher  $I_{NBE}/I_{DLE}$  of annealed ZnO TFTs reflected the fewer structural defects [22,23], which usually links to the better crystal quality. As the reported study [24], the crystallinity of hydrothermal ZnO nanostructures was evidently enhanced after 400 °C oxygen ambient annealing. Therefore, the weaker DLE and stronger NBE intensities recommend the fewer structural defects and better crystal quality in annealed ZnO TFTs, which may lead to an improved electric characteristics.

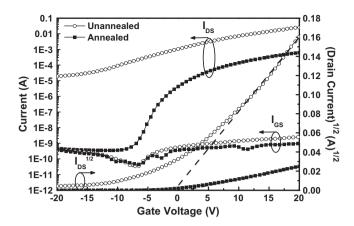

Fig. 4 depicts the drain current vs. gate voltage (the plots of  $I_{DS}$  vs.  $V_{CS}$  and  $I_{DS}^{1/2}$  vs.  $V_{CS}$ ) of transfer characteristics and gate leakage current ( $I_{CS}$ ) for the unannealed and annealed HTG ZnO TFTs with channel width (W) of 250 µm and channel length (L) of 10 µm at the drain voltage ( $V_{DS}$ ) of 20 V. The threshold voltage ( $V_{TH}$ ) and field-effect mobility ( $\mu_{FE}$ ) were calculated with a line fitting of the square root of drain current vs. gate voltage, defined by the current formula of saturated regions [25]:

$$I_{DS,SAT} = \frac{\mu W C_{OX}}{2I} (V_{GS} - V_{TH})^2, \tag{1}$$

where  $I_{DS,SAT}$  is the saturated drain current, and  $C_{OX}$  is the capacitance per unit area of gate insulator, respectively. The unaneled HTG ZnO TFTs indicate the  $V_{TH}$  and on/off current ratio as  $-0.55 \, \text{V}$  and  $1.32 \times 10^3$ , respectively. The calculated  $\mu_{FE}$  is about hundreds of cm²/V s and shows meaningless due to the extremely huge  $I_{DS}$ , while the unaneled ZnO film loses its semiconductor behaviors

**Fig. 3.** Room-temperature PL emission spectra of the unannealed and annealed HTG ZnO TFTs.

**Fig. 4.** Transfer characteristics ( $I_{DS}$ – $V_{GS}$  and  $I_{DS}^{1/2}$ – $V_{GS}$ ) and gate leakage current ( $I_{GS}$ ) of the unannealed and annealed HTG ZnO TFTs with channel width (W) of 250  $\mu$ m and channel length (I) of 10  $\mu$ m at the drain voltage ( $V_{DS}$ ) of 20 V.

and presents approximately conductive property. Contrarily, the annealed ZnO TFTs reveal the distributions of  $V_{TH}$  and  $\mu_{FE}$  in the ranges of 1.25–3 V and 6–12 cm<sup>2</sup>/V s with the measurement of twenty annealed devices. The extracted superior device performances of annealed ZnO TFTs from the  $I_{DS}$ – $V_{GS}$  and  $I_{DS}^{1/2}$ – $V_{CS}$  curves, the excellent  $\mu_{FE}$  of 9.07 cm<sup>2</sup>/V s, positive  $V_{TH}$  of 2.25 V, and high on/off current ratio (i.e. above 10<sup>6</sup>), which can be linked to the high-quality ZnO layer with the compensated structural defects in the

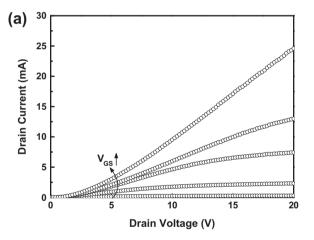

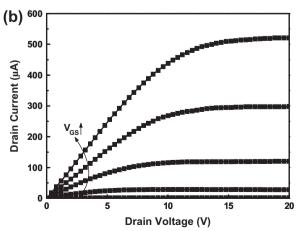

**Fig. 5.** Output characteristics ( $I_{DS}$ – $V_{DS}$ ) of the (a) unannealed and (b) annealed HTG ZnO TFTs under the gate voltage ( $V_{GS}$ ) of 0–20 V with the step of 5 V.

**Table 1**Comparisons of electrical characteristics for the annealed HTG ZnO TFTs in this work and the other solution-based ZnO TFTs in literatures.

| Preparation method              | This study<br>Hydrothermal<br>method | [26]<br>Sol-gel<br>method | [27]<br>Chemical bath<br>method | [28]<br>Sol-gel and chemical bath<br>deposition combined method | [29]<br>Facile sonochemical<br>method |

|---------------------------------|--------------------------------------|---------------------------|---------------------------------|-----------------------------------------------------------------|---------------------------------------|

| Max. process temperature (°C)   | 400                                  | 500                       | 100                             | 230                                                             | 525                                   |

| Threshold voltage (V)           | 2.25                                 | 16.1                      | ~18                             | 6                                                               | 11.7                                  |

| Mobility (cm <sup>2</sup> /V s) | 9.07                                 | 1.16                      | 0.248                           | 0.67                                                            | 0.7                                   |

| On/off current ratio            | $1.75\times10^6$                     | $8.1\times10^7$           | 10 <sup>5</sup>                 | 10 <sup>7</sup>                                                 | $3.2\times10^5$                       |

channel region after oxygen ambient annealing. The positive gate voltage was applied to turn-on TFTs, suggesting the behavior of n-channel enhancement-mode devices. Furthermore, the gate leakage current ( $I_{CS}$ ) of annealed ZnO TFTs is less than 1 nA and far lower than that of unannealed ones. Therefore, the superior device performances (i.e. the excellent  $\mu_{FE}$ , high on/off current ratio, and low gate leakage current) of HTG ZnO TFTs can be made with oxygen ambient annealing.

Fig. 5 shows the drain current-drain voltage ( $I_{DS}$  vs.  $V_{DS}$ ) plot of output characteristics for unannealed and annealed HTG ZnO TFTs under the gate voltage  $(V_{GS})$  of 0-20 V with the step of 5 V. It is demonstrates that annealed ZnO TFTs exhibit the higher driving current than that of unannealed ZnO TFTs under the same bias condition, which is related to the high field effect mobility. The drain current of annealed ZnO TFTs increased linearly with drain voltage at lower values and saturation behavior was observed at high drain voltages due to pinch-off effect by accumulation layer. On the contrast, it obviously indicates the non-saturated curves of  $I_{DS}-V_{DS}$  for unannealed devices. Additionally, the major electrical characteristics of the annealed HTG ZnO TFTs in this work can be comparable to those of the other solution-based ZnO TFTs in literatures [26-29], listed in Table 1. This experimental result recommends that the proposed HTG ZnO TFTs with oxygen ambient annealing at 400 °C can achieve the superior electrical characteristics (i.e. the relatively smaller threshold voltage and higher mobility) than those of the other solution-based ZnO TFTs prepared at higher temperatures. The relatively lower field effect mobilities of the reported solution-based ZnO TFTs may be connected to the result of more grain boundaries, poorer crystallinity, and film porosity. The results suggest that the hydrothermally grown ZnO TFTs with oxygen ambient annealing can contribute excellent device performances (i.e. the excellent  $\mu_{FE}$ , small positive  $V_{TH}$ , high on/off current ratio, and low gate leakage current).

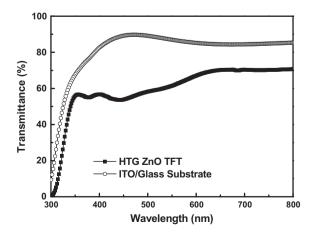

Fig. 6 points out the optical transmission spectra vs. wavelength for the ITO/glass substrate and entire structure of annealed HTG  $\,$

Fig. 6. Optical transmission spectra for the ITO/glass substrate and entire structure of HTG ZnO TFTs.

ZnO TFTs. The optical transmittances in the visible portion for the ITO/glass substrate and entire structure of HTG ZnO TFTs are 85–90% and 53–71%, separately. The reduced transmission of the entire structure is considered with the reflection of Ti/Pt electrodes and absorption coming from gate oxide/HTG ZnO layers owing to the existence of structural defects. The use of smaller Ti/Pt electrodes and superior crystal quality of ZnO layer can further improve the transparency.

#### 4. Conclusion

The hydrothermally grown (HTG) transparent ZnO TFTs has been fabricated on the glass substrates at 85 °C. The location-controlled lateral-grain growth started from the edges of aluminumdoped ZnO (AZO) seed layer beneath the Ti/Pt films, and extended toward the middle of channel from the opposite directions, resulting in only single grain boundary perpendicular to the channel direction. The few vertical grain boundaries in channel region can be expected to make the advanced device performance of ZnO TFTs. After oxygen ambient annealing at 400 °C, the weaker deep level emission (DLE) and stronger band-edge emission (NBE) intensities of annealed ZnO TFTs reflected the better crystal quality and fewer structural defects compared to the unannealed devices. The positive gate voltage was applied to turn-on TFTs, suggesting the behavior of n-channel enhancement-mode devices. Consequently, the superior device performances (i.e. the excellent filed-effect mobility of 9.07 cm<sup>2</sup>/V s, positive threshold voltage of 2.25 V, high on/off current ratio of  $\sim 10^6$ , and low gate leakage current of <1 nA) of HTG transparent ZnO TFTs can be made with an oxygen post-annealing.

## Acknowledgments

Thanks are due to the Center for Thin Film Technologies and Applications (CTFTA) in Ming Chi University of Technology, the Nano Facility Center (NFC) in National Chiao Tung University, and the National Nano Device Laboratory (NDL) for the technical supports.

## References

- [1] Lim SJ, Kwon S, Kim H. ZnO thin films prepared by atomic layer deposition and rf sputtering as an active layer for thin film transistor. Thin Solid Films 2008:516:1523–8.

- [2] Kao CJ, Kwon YW, Heo YW, Norton DP, Pearton SJ, Ren F, et al. Comparison of ZnO metal-oxide-semiconductor field effect transistor and metalsemiconductor field effect transistor structures grown on sapphire by pulsed laser deposition. J Vac Sci Technol B 2005;23:1024-8.

- [3] Navamathavan R, Choi CK, Yang EJ, Lim JH, Hwang DK, Park SJ. Fabrication and characterizations of ZnO thin film transistors prepared by using radio frequency magnetron sputtering. Solid-State Electron 2008;52:813–6.

- [4] Carcia PF, McLean RS, Reilly MH. High-performance ZnO thin-film transistors on gate dielectrics grown by atomic layer deposition. Appl Phys Lett 2006;88:123509–11.

- [5] Islam MN, Mazhari B. Comparative analysis of unity gain frequency of top and bottom-contact organic thin film transistors. Solid-State Electron 2009;53:1067–75.

- [6] Tsamados D, Cvetkovic NV, Sidler K, Bhandari J, Savu V, Brugger J, et al. Double-gate pentacene thin-film transistor with improved control in sub-threshold region. Solid-State Electron 2010;54:1003–9.

- [7] Chou DW, Huang CJ, Su CM, Yang CF, Chen WR, Meen TH. Effect of rapid thermal annealing on pentacene-based thin-film transistors. Solid-State Electron 2011:61:76–80.

- [8] Kim SH, Kim EB, Choi HY, Kang MH, Hur JH, Jang J. A coplanar hydrogenated amorphous silicon thin-film transistor for controlling backlight brightness of liquid-crystal display. Solid-State Electron 2008;52:478–81.

- [9] Tang Z, Park MS, Jin SH, Wie CR. Drain bias dependent bias temperature stress instability in a-Si:H TFT. Solid-State Electron 2009;63:225–33.

- [10] Hyung GW, Park J, Kim JH, Koo JR, Kim YK. Storage stability improvement of pentacene thin-film transistors using polyimide passivation layer fabricated by vapor deposition polymerization. Solid-State Electron 2010;54:439–42.

- [11] Katz HE, Johnson J, Lovinger AJ, Li W. Naphthalenetetracarboxylic diimidebased n-channel transistor semiconductors: structural variation and thiolenhanced gold contacts. J Am Chem Soc 2000;122:7787.

- [12] Staebler DL, Wronski CR. Reversible conductivity changes in dischargeproduced amorphous Si. Appl Phys Lett 1977;31:291.

- [13] Tsay CY, Fan KS, Chen SH, Tsai CH. Preparation and characterization of ZnO transparent semiconductor thin films by sol-gel method. J Alloy Compd 2010;495:126–30.

- [14] Natsume Y, Sakata H, Hirayama T. Low-temperature electrical conductivity and optical absorption edge of ZnO films prepared by chemical vapour deposition. Phys Status Solidi A 1995;148:485–95.

- [15] Li C, Li Y, Wu Y, Ong BS, Loutfy RO. ZnO field-effect transistors prepared by aqueous solution-growth ZnO crystal thin film. J Appl Phys 2007;102:076101-

- [16] Yang PY, Wang JL, Tsai WC, Wang SJ, Lin JC, Lee IC, et al. Photoresponse of hydrothermally grown lateral ZnO nanowires. Thin Solid Films 2010:518:7328–32.

- [17] Lim J, Shin K, Kim HW, Lee C. Effect of annealing on the photoluminescence characteristics of ZnO thin films grown on the sapphire substrate by atomic layer epitaxy. Mater Sci Eng B 2004;107:301–4.

- [18] Meng X, Lin B, Gu B, Zhu J, Fu Z. A simple growth route towards ZnO thin films and nanorods. Solid State Commun 2005;135:411–5.

- [19] Bong H, Lee WH, Lee DY, Kim BJ, Cho JH, Cho K. High-mobility low-temperature ZnO transistors with low-voltage operation. Appl Phys Lett 2010:96:192115-3.

- [20] Hossain FM, Nishii J, Takagi S, Ohtomo A, Fukumura T, Fujioka H, et al. Modeling and simulation of polycrystalline ZnO thin-film transistors. J Appl Phys 2003;94:7768–77.

- [21] Kong YC, Yu DP, Zhang B, Fang W, Feng SQ. Ultraviolet-emitting ZnO nanowires synthesized by a physical vapor deposition approach. Appl Phys Lett 2001:78:407-9.

- [22] Wang RC, Liu CP, Huang JL, Chen SJ. Single-crystalline AlZnO nanowires/ nanotubes synthesized at low temperature. Appl Phys Lett 2006;88:023111-3.

- [23] Yang PY, Wang JL, Tsai WC, Wang SJ, Lin JC, Lee IC, et al. Field-emission characteristics of Al-doped ZnO nanostructures hydrothermally synthesized at low temperature. J Nanosci Nanotechnol 2011;11:6013–9.

- [24] Yang PY, Wang JL, Tsai WC, Wang SJ, Lin JC, Lee IC, et al. Oxygen annealing effect on ultraviolet photoresponse of p-NiO-nanoflowers/n-ZnO-nanowires heterostructures. J Nanosci Nanotechnol 2011;11:5737–43.

- [25] Hsieh HH, Wu CC. Scaling behavior of ZnO transparent thin-film transistors. Appl Phys Lett 2006;89:041109-3.

- [26] Jones GAC, Xiong G, Anderson D. Fabrication of nanoscale ZnO field effect transistors using the functional precursor zinc neodecanoate directly as a negative electron beam lithography resist. J Vac Sci Technol B 2009;27:3164-8.

- [27] Cheng HC, Chen CF, Lee CC. Thin-film transistors with active layers of zinc oxide (ZnO) fabricated by low-temperature chemical bath method. Thin Solid Films 2006;498:142–5.

- [28] Cheng HC, Chen CF, Tsay CY. Transparent ZnO thin film transistor fabricated by sol-gel and chemical bath deposition combination method. Appl Phys Lett 2007:90:012113-3.

- [29] Oh JY, Park J, Kang SY, Hwang CS, Shim HK. Room temperature fabrication of ZnO nanorod films: synthesis and application as a channel layer of transparent thin film transistors. Chem Commun 2009:4545–7.