# Freewheel charge-pump controlled single-inductor multiple-output step-up DC-DC converter

Chia-Min Chen · Kai-Hsiu Hsu · Chung-Chih Hung

Received: 22 May 2012/Revised: 26 October 2012/Accepted: 6 November 2012/Published online: 15 November 2012 © Springer Science+Business Media New York 2012

**Abstract** This paper presents a freewheel-charge-pumpcontrolled design for a single-inductor multiple-output (SIMO) DC-DC Converter. By applying the freewheelcharge-pump-controlled (FCPC) technique, the freewheel switching time is reused, and two extra charge-pump outputs are provided by time recycling, with no cost in time sequences. The converter has two step-up outputs and two charge-pump outputs that can be higher or lower than the input supply. The converter utilizes a 1 µH inductor, 4.7 μF charge-pump capacitors and 33 μF output capacitors at a frequency of 1 MHz. The proposed converter shows low cross-regulation and achieves a maximum loading current of 70 mA. Fabricated in a 0.18-µm CMOS process, the proposed circuit occupies  $1.3 \times 1.3 \text{ mm}^2$ . Experimental results demonstrate that the converter successfully generates four well-regulated outputs with a single inductor. The supply voltage ranged from 1.6 to 2.5 V and the load regulation performance was 0.08, 0.05, 1.7, and 1.9 mV/mA for  $V_{O1}$ ,  $V_{O2}$ ,  $V_{O3}$  and  $V_{O4}$ , respectively.

**Keywords** Freewheel-charge-pump-controlled (FCPC) · Freewheel switching · Charge-pump regulator · Pseudo-continuous conduction mode (PCCM) · Single-inductor multiple-output (SIMO) converter

C.-M. Chen · K.-H. Hsu · C.-C. Hung (☒)

Analog Integrated Circuit Laboratory, Department of Electrical Engineering, National Chiao Tung University, Hsinchu, Taiwan e-mail: cchung@mail.nctu.edu.tw

C.-M. Chen

e-mail: jeremy.cm97g@g2.nctu.edu.tw

K.-H. Hsu

e-mail: asdx27@gmail.com

## 1 Introduction

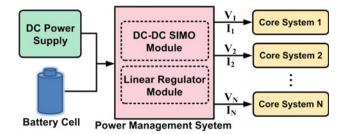

Power management systems have become increasingly important with rapid growth in the popularity of battery-operated products such as MP3 players, cellular phones and digital cameras. The power management system of such devices provides individual voltages or currents to each core system, as shown in Fig. 1. DC–DC converters are an essential component of power management systems. Multiple output DC–DC converters are able to provide several regulated supply voltages for a variety of electronic applications, which may require different supply voltages for different function modules.

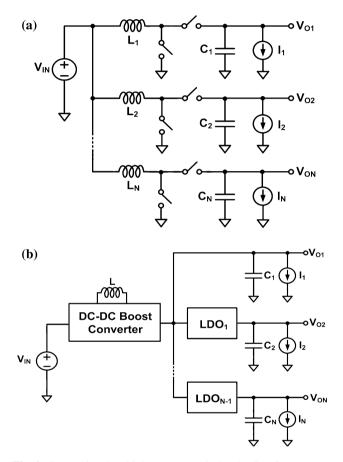

Multiple-output converters are traditionally classified into two categories: isolated converters and non-isolated converters. Isolated converters use individual secondary windings to convert voltage [1]. However, isolated converters do not provide outputs with precise control, and the multiple windings add cost to the design. Non-isolated converters with N output voltages either consist of N independent single-output conventional DC-DC converters or employ a single boost converter and N-1 low dropout (LDO) regulators. As shown in Fig. 2, the former approach requires N inductors, increasing the system cost and complexity of the PCB board design. The latter approach inherits the advantages of the LDO, which include a simple design and low output voltage ripple, but also the disadvantage of low efficiency. Several single-inductor multipleoutput (SIMO) switching converters have been proposed in recent research [2-8]. SIMO converters use only one inductor and a single control loop to generate multiple outputs. This architecture has the advantages of lower cost and simpler PCB board design. SIMO converters have been utilized in many LCD/OLED and power management applications [9-12].

Fig. 1 Application of the multiple-output DC-DC converter

Fig. 2 Conventional multiple-output non-isolated DC-DC converters

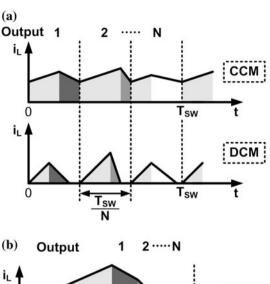

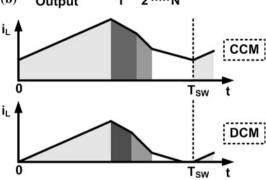

SIMO converters can be divided into two types according to the operation of the energy flow: (1) multiple energy storage cycles per switching period and (2) a single energy storage cycle per switching period [13]. The converter proposed in [14–16] divides a switching period  $T_{SW}$  into N segments, as shown in Fig. 3(a), and stores and releases energy sequentially to each of the N outputs. This type of converter can operate in both continuous-conduction mode (CCM) and discontinuous-conduction mode (DCM). The advantage of this converter is less cross-regulation. Instead of storing energy to the inductor N times, the converters proposed in [10] store energy to the inductor only once in every switching period  $T_{SW}$ . As shown in

Fig. 3 Operation of energy flow in SIMO converters

Fig. 3(b), the inductor in the converter has enough energy for all loads at the end of the charge time and delivers energy to all outputs sequentially. This type also provides both CCM and DCM operation. Compared to the first-type converter, the second-type converter has a smaller output voltage ripple.

In this paper, we introduce a new type of single-inductor multiple-output (SIMO) DC-DC converter. By applying the freewheel-charge-pump-controlled (FCPC) technique, we are able to reuse the freewheel switching time and increase the number of outputs with no extra time sequence cost. In Sect. 2, a brief review of the typical architecture of the SIMO converter and a discussion about its cross-regulation effect are presented. Section 3 analyzes the operation and circuit implementation of the proposed converter. Experimental results are presented and discussed in Sect. 4. Section 5 presents our conclusions.

# 2 Topology of typical SIMO DC-DC converter

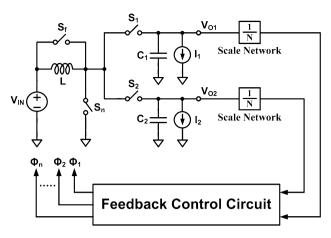

A SIMO DC–DC converter is usually composed of an offchip inductor, off-chip capacitors, on-chip switches (power transistors), scale networks, and feedback control circuits, as shown in Fig. 4 [17]. The topology of a SIMO converter

Fig. 4 Topology of a typical SIMO DC-DC converter

is set up as a closed loop. The scale networks adjust the output voltage and the feedback control circuit detects the target voltage to control the power transistors. The feedback control circuit generates the control phases for power transistors, producing a stable output voltage. Because power transistors must be capable of handling high load currents, they are typically large-area devices, with dimensions on the order of 10<sup>4</sup> µm [18]. Unlike the conventional single output converter, the outputs of the SIMO converter may affect each other because the outputs share an inductor and the feedback control circuit. This effect, known as cross-regulation, causes variation in the output current and voltage, which are affected by the other outputs. Cross-regulation can be avoided for multiple-output converters that generate each output in its individual time interval.

In terms of energy flow management, relying on multiple energy storage cycles per switching period more effectively prevents cross-regulation than using a single energy storage cycle per switching period. In the latter approach, the outputs are not separated in CCM/DCM situations, whereas the former approach operates in the DCM, and thus solves the cross-regulation problem. However, DCM operation is only suitable for applications involving a small load current.

The single-inductor converter with five outputs presented in [10] employs an ordered power-distributive control, where each output is related to others in the converter. This design provides poor cross-regulation and a small loading current. A time-multiplexing control method in discontinuous conduction mode eliminates the cross-regulation effect [14]. The SIMO converter presented in [15] works in both the pseudo-continuous conduction mode (PCCM) and DCM. With freewheel switching control, this converter can work in PCCM to handle a large loading current and demonstrate minimal cross-regulation; the same converter can also operate in DCM to minimize cross-regulation. Moreover,

PCCM operation can drive larger load currents than can DCM operation. However, during power conversion, the time used in freewheel switching is wasted. In addition, with an increased number of outputs, the total period of freewheel switching and the output voltage ripple will also increase. Importantly, the outputs are idle during the freewheel period and therefore this time is wasted. This paper presents a new single-inductor multiple-output DC–DC converter. The proposed design applies the freewheel-charge-pump-controlled (FCPC) technique to reuse the time periods consumed by freewheel switching in order to increase the number of outputs without an extra time sequence.

## 3 Proposed FCPC SIMO converter

## 3.1 Power stages of the proposed converter

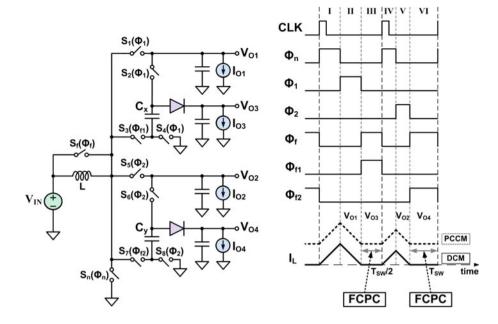

Figure 5 shows the architecture of the power stage and the timing diagram of the proposed FCPC SIMO converter. The converter can operate in DCM under a light load and PCCM under a heavy load. Compared to a previous design [15], the proposed FCPC SIMO converter provides two additional outputs without needing an extra switching phase during each clock period. The approach for generating the V<sub>O1</sub> and V<sub>O2</sub> outputs is similar to that of a conventional SIMO converter, and the two outputs are generated during phase II and phase V, respectively. The proposed design uses freewheel charge-pump control to generate outputs  $V_{\rm O3}$  and  $V_{\rm O4}$  at phase III and phase VI, respectively. A previous design [15] proposed keeping the inductor current constant by shorting the inductor during the freewheel switching phases (III and VI). Under this approach, the converter is idle and only consumes power during the freewheel switching phases. The proposed design reuses the freewheel phases to provide multiple charge-pump outputs by time and power recycling.

The detailed operation of the proposed converter is described in the next subsection and the overall architecture of the converter is presented in Sect. 3.3. Section 3.4 introduces the circuit of the freewheel arbitrator, which determines the start and end of freewheel switching, and addresses how the converter controls the charging and discharging of the inductor. Section 3.5 describes the current detector, which senses and limits the peak charging current of the inductor. The soft start circuit, discussed in Sect. 3.6, ensures the normal operation of the circuit during the start-up of the power supply.

## 3.2 Operation of the proposed converter

Figure 6 depicts the operation sequences. Switch  $S_n$  is turned on and the power supply stores energy to the

**Fig. 5** Power stage of the proposed FCPC SIMO converter and its timing diagram

inductor in phase I. Next, Switch S<sub>n</sub> is turned off. S<sub>1</sub>, S<sub>2</sub> and S<sub>4</sub> are then turned on, and the inductor delivers energy to output V<sub>O1</sub> and capacitor C<sub>x</sub> in phase II. During freewheel switching, the  $C_x$  top plate is charged from  $V_{O1}$  to  $V_{O1} + V_{IN}$  to provide  $V_{O3}$  in phase III. During this phase,  $S_f$  and  $S_3$  are switched on and other switches are off.  $S_n$  is switched on in phase IV, and the inductor stores energy again, as in phase I. However, unlike phase II, the inductor then delivers energy to output V<sub>O2</sub> and capacitor C<sub>v</sub> in phase V. In this phase,  $S_n$  is off and  $S_5$ ,  $S_6$  and  $S_8$  are on.  $S_f$ and S<sub>7</sub> are switched on during the freewheel switching period to charge the  $C_v$  top plate from  $V_{O2}$  to  $V_{O2} + V_{IN}$  to generate V<sub>O4</sub> in phase VI. By repeating the six phases, the FCPC SIMO DC-DC converter can generate two step-up outputs and two charge-pump outputs. The charge-pump outputs  $V_{O3}$  and  $V_{O4}$  can be obtained from Eqs. (1) and (2) below.

$$V_{O3} \cong V_{IN} + V_{O1} - (2V_{SD(on)} + V_F + V_{PAR} + V_{REG3}) \eqno(1)$$

$$V_{O4} \cong V_{IN} + V_{O2} - (2V_{SD(on)} + V_F + V_{PAR} + V_{REG4}) \eqno(2)$$

where  $V_{\rm IN}$  is the supply voltage,  $V_{\rm SD(on)}$  is the source-drain voltage of the power transistor while turned on,  $V_{\rm F}$  is the forward voltage of the Schottky rectifier diode (approximately 0.8 V), and  $V_{\rm PAR}$  represents the voltage drop on all the parasitic resistance caused by the metal wire inside the chip, bond wire, lead frame, and the copper trace of the PCB (approximately 0.01 V).  $V_{\rm REG3}$  represents the maximum difference of output voltage  $V_{\rm O3}$  during load regulation (approximately 0.034 V) and  $V_{\rm REG4}$  represents the maximum difference of output voltage  $V_{\rm O4}$  during load

regulation (approximately 0.038 V). By utilizing the free-wheel-charge-pump-controlled technique, the converter not only inherits the advantages of cross-regulation suppression and the ability to provide large current at heavy load, but also increases the number of outputs through phase reuse by time recycling.

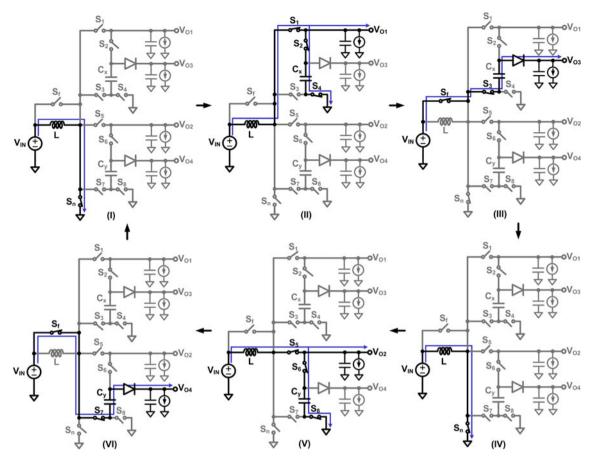

## 3.3 Architecture of the proposed converter

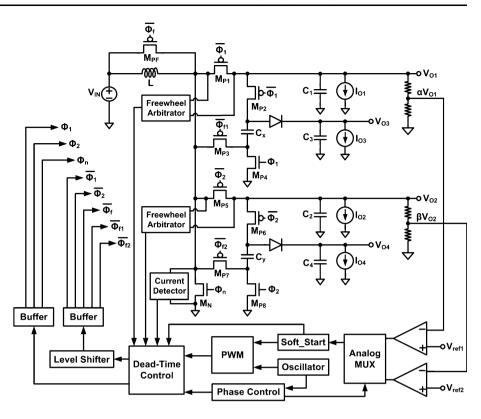

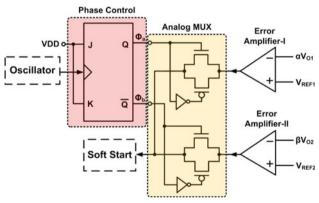

Figure 7 shows the block diagram of the proposed SIMO converter. The SIMO converter generates four outputs:  $V_{O1}$ ,  $V_{O2}$ ,  $V_{O3}$  and  $V_{O4}$ . The first two outputs,  $V_{O1}$  and V<sub>O2</sub>, are typical step-up outputs with pulse-width modulation (PWM) control. Therefore, the general compensation network can be used in the feedback loop.  $V_{\rm O3}$  and  $V_{\rm O4}$  are charge-pump outputs with freewheel-charge-pump-control. Feedback resistors scale the  $V_{\rm O1}$  and  $V_{\rm O2}$  outputs to  $\alpha V_{\rm O1}$ and  $\beta V_{O2}$  and the error amplifier detects and amplifies the difference between the feedback voltage and the reference voltage. Analog MUX circuits can alternatively select error amplifier-I or error amplifier-II to generate the output signal by controlling the selection using a phase control block as shown in Fig. 8. The phase control block consists of the JK flip-flop logic circuit, which generates two opposite clock phases  $\Phi_a$  and  $\Phi_b$  to turn switches on or off in the analog MUX. When both J and K inputs are at logic "high" simultaneously during the rising edge of the input clock, the circuit will toggle from the original "SET" state to a "RESET" state, or vice versa. For example, if the output of error amplifier-I is sent to the soft start circuit during this clock period, in the next clock period the output of error amplifier-II will be sent to the soft start circuit. The PWM circuit generates control signals based on the output signal

Fig. 6 Operation sequences of the proposed FCPC SIMO converter

of the analog MUX circuit. The dead-time control circuit turns the power transistors on and off in accordance with the PWM signal and current signals generated by freewheel arbitrators and the current detector. The freewheel arbitrators decide when to turn the freewheel switch  $M_{\rm f}$  on and off. The current detector detects the inductor current during charge up and prevents excessive power transistor current. The proposed freewheel-charge-pump-controlled block consists of power transistors  $M_{\rm P2}$ ,  $M_{\rm P3}$ ,  $M_{\rm P4}$ ,  $M_{\rm P6}$ ,  $M_{\rm P7}$  and  $M_{\rm P8}$  and capacitors  $C_x$  and  $C_y$ . The control block reuses existing control signals in PWM control and directly applies them to the FCPC block. Thus, the FCPC SIMO converter does not require an extra control circuit.

# 3.4 Freewheel arbitrator

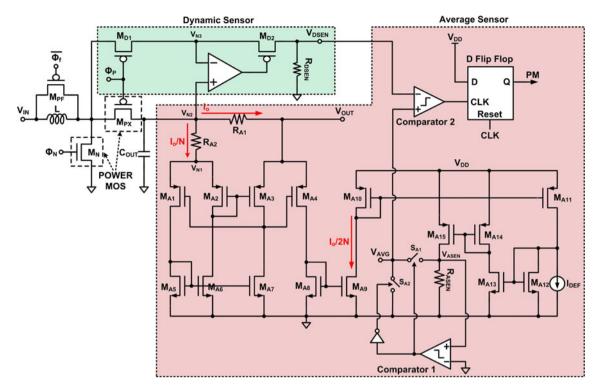

A freewheel arbitrator detects the inductor current that flows through the power PMOS  $M_{PX}$ , and decides when to activate the freewheel mechanism. The freewheel arbitrator is comprised of the circuit blocks of the average sensor and dynamic sensor, as shown in Fig. 9.

The average sensor calculates the average current of output loading, which helps determine when the converter should start freewheel switching. The average current can be sensed by transistors  $M_{A1}$ – $M_{A10}$ . For  $R_{A1}$  to be able to sense the average current, RA1 should be placed between C<sub>OUT</sub> and the load. A negative feedback loop is formed by an amplifier connected as a unity-gain buffer. The amplifier is comprised of transistors M<sub>A1</sub>-M<sub>A3</sub> and M<sub>A5</sub>-M<sub>A7</sub> with the inputs at V<sub>N1</sub> and V<sub>OUT</sub>. Therefore, the negative feedback loop locks  $V_{N1}$  and  $V_{OUT}$  at the same voltage. When  $V_{N1} = V_{OUT}$ , the aspect ratios of transistors  $M_{A1}$ – $M_{A4}$  are designed to be the same, as is the case for  $M_{A5}$ – $M_{A8}$ . Thus, the same current flows into  $M_{A1}$ ,  $M_{A2}$ ,  $M_{A3}$  and  $M_{A4}$ . The resistance of  $R_{A2}$  is designed to be N times the resistance of  $R_{A1}$ . Since  $V_{N1}$  is forced to be the same as  $V_{OUT}$ , the current through  $R_{A1}$  is N times the current through R<sub>A2</sub>. As a result, if the current though R<sub>A1</sub> is  $I_O$ , the current through  $R_{A2}$  will be  $I_O/N$ . Therefore, all current through M<sub>A1</sub>, M<sub>A2</sub>, M<sub>A3</sub> and M<sub>A4</sub> is equal to I<sub>O</sub>/2N, and the current flowing through  $M_{A9}$  is also  $I_O/2N$ .

This sensing current  $I_O/2N$  is used to deduct a default current  $I_{\rm DEF}$ , resulting in a difference current through resistor  $R_{\rm ASEN}$  that produces voltage  $V_{\rm ASEN}$ . As the input pair of comparator 1 is designed with asymmetric transistors, when  $V_{\rm ASEN}$  is close to zero, the comparator output

**Fig. 7** Architecture of the proposed FCPC SIMO converter

Fig. 8 Analog MUX and phase control circuits

will become logical low. When  $V_{ASEN}$  is significantly larger than zero, the comparator will generate logical high, implying that the difference current is a positive value and that there is a large loading current. When the output of comparator 1 becomes high to turn  $S_{A1}$  on and  $S_{A2}$  off,  $V_{AVG}$  is equal to  $V_{ASEN}$ . As the dynamic sensor monitors the inductor current to discharge to the value of the average loading current, the converter starts the freewheel switching of the PCCM. When current  $I_{MA11}$  is less than  $I_{DEF}$ , implying that the loading current is small, the current flowing through resistor  $R_{ASEN}$  becomes zero, and therefore the voltage  $V_{ASEN}$  is approximately zero. As the input pair of comparator 1 is designed by asymmetric transistors, the output of the comparator goes low,  $S_{A2}$  turns on and

$S_{A1}$  turns off and  $V_{AVG}$  is shorted to ground. When the current  $I_{MA11}$  is less than  $I_{DEF}$ ,  $V_{AVG}$  becomes zero. When the dynamic sensor senses that the inductor current has discharged to zero, the converter starts the freewheel switching of the DCM operation.

The dynamic sensor is used for sensing the inductor current during discharge. When the inductor current is discharged to the DC current level during freewheel, the following comparator and D flip-flop will generate control signals to switching operation to freewheel. The function of the dynamic sensor is to sense the dynamic current of  $M_{PX}$ . When the POWER MOS  $M_{PX}$  is turned on,  $M_{D1}$  is also turned on simultaneously. Due to the closed loop formed by the error amplifier and  $M_{D2}$ , the drain terminals  $V_{N2}$  and  $V_{N3}$  of  $M_{PX}$  and  $M_{D1}$  are locked to the same voltage. Since the drain, source, and gate voltages of transistors M<sub>D1</sub> and M<sub>PX</sub> are all the same, their current ratio depends on the transistor size ratio. Therefore, the dynamic sensor senses the current through R<sub>DSEN</sub> to produce V<sub>DSEN</sub> proportional to the inductor current, in order to obtain the ratio of the inductor discharge current. Comparator 2, designed with an asymmetric input pair, compares two sensing signals V<sub>DSEN</sub> and V<sub>AVG</sub>. When the inductor current discharges to be less than the average load current ( $V_{DSEN} < V_{AVG}$ ), the comparator output goes high and the D flip-flop produces a signal PM to control the dead-time control circuit and to activate the FCPC mechanism (PCCM), which turns on the freewheel switch S<sub>f</sub> (M<sub>PF</sub>) and turns off the lower-side power switch S<sub>n</sub> (M<sub>N</sub>). The magnitude of the loading

Fig. 9 Freewheel arbitrator

current affects when the freewheel mechanism starts, and the mechanism stops when the rising edge of the next clock arrives. Thus, the duration of freewheel switching depends on the loading current. When the next rising edge of the clock arrives and resets the D flip-flop, the signal PM will control the dead-time control circuit to turn off the freewheel switch. Then,  $\Phi_N$  becomes high to turn on  $M_N$ , and the input voltage V<sub>IN</sub> charges the inductor again. The feedback loop of the converter or the current detector will control the dead-time control circuit to determine the duration of  $\Phi_N$  = high, which represents the charging time of the inductor. When there is a heavy load, the charging time is longer and as the inductor is charged to the required value or the maximum default value,  $\Phi_N$  will become low and  $\Phi_{\rm P}$  will turn high. Thus, the inductor starts to discharge current to the load, and the freewheel arbitrator detects when the freewheel switch needs to be turned on again to begin a new cycle. The input pairs of comparator 1 and comparator 2 in the freewheel arbitrator are designed as slightly asymmetric architectures, so when the converter operates in the DCM mode, the reverse inductor current can be avoided and the power losses caused by the reverse inductor current can be minimized as well.

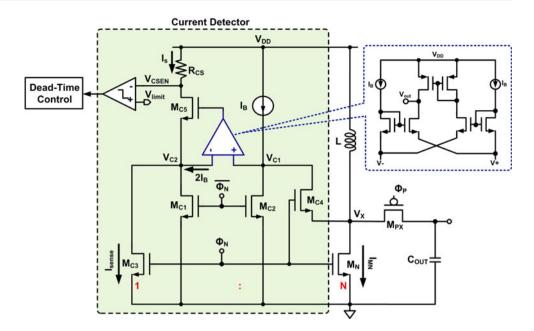

## 3.5 Current detector

The current detector senses the current of the lower-side Power MOS  $M_N$ , which is used to prevent the inductor

current from becoming too large. For the current detector to sense the dynamic inductor current, the utilized amplifier requires larger bandwidth so as to accurately sense the current and reduce the timing delay for the following control circuits. Figure 10 shows the proposed current detection circuit, which uses an improved error amplifier. The proposed amplifier only consumes 17 µW power. The unity-gain bandwidth is 13.1 MHz when load capacitance is 1 pF, which is fast enough for a SIMO converter operating at 1 MHz. The DC gain is 42.2 dB at  $V_{DD} = 1.8 \text{ V}$ , which corresponds to less than 2 % error for both V<sub>C1</sub> and V<sub>C2</sub>. On the other hand, for the general voltage amplifier, under the same power consumption, only a unity-gain bandwidth of 9.05 MHz can be obtained when load capacitance is also 1 pF. Our proposed amplifier has increased 44.7 % of the bandwidth.  $V_{C1}$  is equal to  $V_{C2}$ because of the negative feedback loop formed by the amplifier and  $M_{C5}$ . When  $\Phi_N$  is high,  $M_{C1}$  and  $M_{C2}$  turn off and transistor  $M_{C4}$  turns on; thus  $V_{C1}$  is equal to  $V_X$ . The aspect ratio of transistor M<sub>N</sub> is N times that of transistor  $M_{C3}$ . As  $V_{C2}$  is equal to  $V_X$ , the current  $I_{MN}$  is N times the current  $I_{sense}$ . When  $\Phi_N$  is low,  $M_{C3}$  and  $M_N$  turn off, and transistors M<sub>C1</sub> and M<sub>C2</sub> turn on to keep the current amplifier active.

In this circuit,  $I_B$  was designed to be small. As a result  $I_S$  is almost equal to  $I_{sense}$ . Current  $I_S$  flows through  $R_{CS}$  to generate voltage  $V_{CSEN}$ . A comparator compares  $V_{CSEN}$  with a preset voltage  $V_{limit}$ . When  $V_{CSEN}$  is lower than

Fig. 10 Current detector

$V_{limit}$ —in other words, when the inductor current is larger than the preset value—the comparator output will control the dead-time control circuit to pull  $\Phi_N$  to low, in order to turn off  $M_N$ . The sensing current is very small relative to the inductor charging current; this can reduce the quiescent current and reduce power consumption, achieving high conversion efficiency. The power loss due to the sensing resistor  $R_{CS}$  is reduced N times.

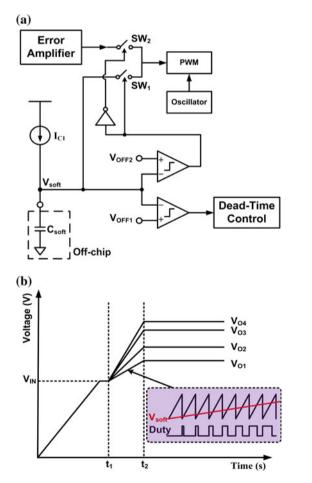

## 3.6 Soft start

In the initial power-on state, if there is no soft start circuit, the output of the converter is directly connected to the inductor. Because the output voltage is lower than input voltage, the input voltage will charge the inductor until the output voltage reaches the target value. As the inductor charges faster than the rate at which output voltage increases, the initial fast charging effect often damages the power transistors or the inductor. Therefore, a soft start is used to prevent the duty cycle from being too long, which can result in too large of an inductor current when the power supply initially turns on. The soft start is even more important for the step-up converter. Different from the traditional soft start design, the proposed soft start circuit block is placed between the PWM controller and the error amplifier. Because the SIMO converter has several error amplifiers, when the proposed design is used, it will not be necessary to include several soft start circuits so as to save the chip area, which is more suitable for the application of the SIMO converter design. In this design, the soft start occurs in three stages, as shown in Fig. 11. The traditional soft start circuit has only the last two stages. The advantage of adding the first stage is that after the power supply is

Fig. 11 a Soft start circuit. b Output voltage during the soft start

turned on, the four output voltages will be charged to the level of supply voltage directly, which has largely reduce the initial boosting time for the outputs of the PWM boost

converter. During the first stage  $(0-t_1)$ , the supply starts up, current  $I_{C1}$  charges capacitor  $C_{soft}$  and  $V_{soft}$  is smaller than  $V_{OFF1}$ ; therefore the low-side comparator sends a control signal to the dead-time control circuit to turn on switches  $S_f(M_{PF})$ ,  $S_1(M_{P1})$ ,  $S_2(M_{P2})$ ,  $S_4(M_{P4})$ ,  $S_5(M_{P5})$ ,  $S_6(M_{P6})$  and  $S_8(M_{P8})$  shown in Figs. 5 and 7. The four outputs connect to the power supply through the freewheel switch  $S_f$ , and the four outputs are directly charged to the supply voltage  $V_{IN}$ . Thus, the second stage begins with all output voltages equal to the supply voltage  $V_{IN}$ . During the second stage  $(t_1-t_2)$ ,  $V_{soft}$  is charged to a value between  $V_{OFF1}$  and  $V_{OFF2}$  and the output of the low-side comparator turns off freewheel switch  $S_f$   $(M_{PF})$ . However, switch  $SW_1$  in Fig. 11(a) is still on and  $SW_2$  is still off.  $V_{soft}$  directly controls the duty cycle of the pulse width modulation

Fig. 12 Die microphotograph

Fig. 13 Measured waveforms when the four outputs operate in stepup mode

(PWM) output. Therefore, the duty cycle increases slowly with  $V_{soft}$  and the four output voltages increase to their target voltage. Soft start ends at  $t_2$  when—since  $V_{soft}$  is larger than  $V_{OFF2}$ —SW $_1$  turns off and SW $_2$  turns on. During the final stage, output voltages  $V_{O1}$  and  $V_{O2}$  go into typical PWM control and  $V_{O3}$  and  $V_{O4}$  enter the previously described freewheel-charge-pump-control, as shown in Fig. 11(b).

#### 4 Measurement results

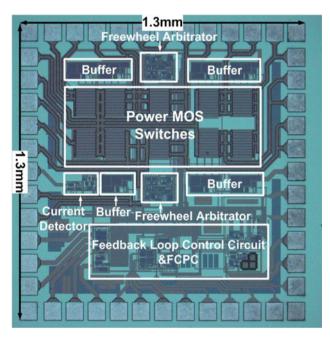

The proposed SIMO DC–DC converter was implemented in a TSMC 1P6M 0.18- $\mu m$  CMOS process. Figure 12 shows the die microphotograph of the converter. The die area, including the pads, is  $1.3 \times 1.3 \text{ mm}^2$ . The DC–DC converter has two step-up outputs and two charge-pump outputs which can be higher or lower than the input supply. The converter uses a 1- $\mu H$  inductor, 4.7  $\mu F$  charge-pump capacitors and 33  $\mu F$  output capacitors at a frequency of 1 MHz. The two outputs ( $V_{O1}$  and  $V_{O2}$ ) are set by the reference voltage and range from 2.1 to 2.5 V. The two

Fig. 14 Measured line transient responses

Fig. 15 Measured load transient responses

Table 1 Performance summary

|                                                  | -                                              |                       |                       |                       |

|--------------------------------------------------|------------------------------------------------|-----------------------|-----------------------|-----------------------|

| Technology                                       | TSMC 1P6M 0.18-µm CMOS                         |                       |                       |                       |

| Chip area                                        | $1.3 \times 1.3 \text{ mm}^2$ (including pads) |                       |                       |                       |

| Supply voltage (V)                               | 1.8 (range: 1.6–2.5)                           |                       |                       |                       |

| Inductor/ESR                                     | 1 μH/200 mΩ                                    |                       |                       |                       |

| Oscillator frequency (MHz)                       | 1                                              |                       |                       |                       |

| Output voltages (V)                              | V <sub>01</sub> (2.1)                          | V <sub>02</sub> (2.5) | V <sub>03</sub> (2.4) | V <sub>04</sub> (2.8) |

| Output ripple (mV)                               | 13                                             | 15                    | 4                     | 5                     |

| Load current (max.) (mA)                         | 70                                             | 60                    | 20                    | 20                    |

| Load regulation (mV/mA)                          | 0.08                                           | 0.05                  | 1.7                   | 1.9                   |

| Line regulation (mV/V)                           | 21                                             | 12                    | N/A                   | N/A                   |

| Filtering capacitor ( $\mu$ F)/ ESR( $m\Omega$ ) | 33/85                                          | 33/85                 | 33/85                 | 33/85                 |

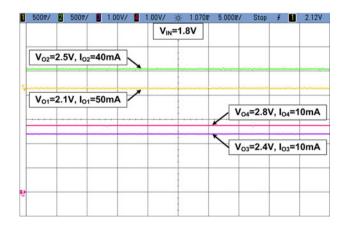

charge-pump output voltages ( $V_{O3}$  and  $V_{O4}$ ) are dependent on the loading current. Figure 13 shows the measured waveforms of the four boost outputs.

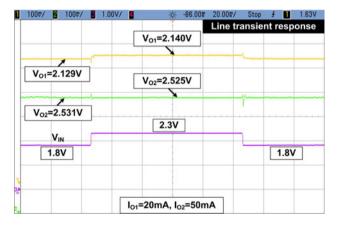

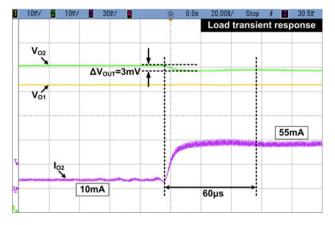

A supply voltage pulsating between 1.8 and 2.3 V was applied to serve as the input to characterize the line transient response, and its influence on the output was measured. Figure 14 shows the results. The line regulations were 21 and 12 mV/V for V<sub>O1</sub> and V<sub>O2</sub>, respectively. While the V<sub>O2</sub> loading current was rapidly pulsed from 10 to 55 mA, the V<sub>O1</sub> loading current stayed unchanged, demonstrating the load transient response and cross-regulation. The maximum transient output variation of  $V_{O2}$  is 3 mV while  $V_{O1}$  remains the same, as shown in Fig. 15. Experimental results confirm that the proposed converter achieves low cross-regulation. Table 1 summarizes the FCPC SIMO DC-DC converter performance.

## 5 Conclusion

The FCPC SIMO DC-DC converter proposed in this paper provides complete control to generate four low crossregulation outputs without increasing the switching time. The converter has two step-up outputs and two chargepump outputs which can be higher or lower than the input supply. The two charge-pump outputs  $(V_{O3} \text{ and } V_{O4})$  can also be regulated by including them inside feedback loops. The converter applies the freewheel-charge-pump-controlled technique, inheriting the advantages of cross-regulation suppression and the ability to provide large current at heavy load, while also providing more outputs by phase reuse through time recycling.

Acknowledgments The authors would like to thank the National Chip Implementation Center for supporting the chip fabrication. This research was sponsored by the National Science Council.

#### References

- 1. Tacca, H. E. (1998). Single-switch two-output flyback-forward converter operation. IEEE Transactions on Power Electronics, 13(5), 903-911.

- 2. Lee, Y.-H., Yang, Y.-Y., Wang, S.-J., Chen, K.-H., Lin, Y.-H., Chen, Y.-K., et al. (2011). Interleaving energy-conservation mode (IECM) control in single-inductor dual-output (SIDO) stepdown converters with 91% peak efficiency. IEEE Journal of Solid-State Circuits, 46(4), 904-915.

- 3. Dancy, A. P., Amirtharajah, R., & Chandrakasan, A. P. (2000). High-efficiency multiple-output DC-DC conversion for low-voltage systems. IEEE Transactions on VLSI Systems, 8(3), 252–263.

- 4. Su, W., Li, Y., Gong, X., Hong, Z., & Killat, D. (2010). A dualmode single-inductor dual-output switching converter with small ripple. IEEE Transactions on Power Electronics, 25(3), 614–623.

- 5. Sharma, A., & Pavan, Y. S. (2006). A single inductor multiple output converter with adaptive delta current mode control. In IEEE International Symposium on Circuits and Systems (ISCAS), pp. 5643-5646, May 2006.

- 6. Belloni, M., Bonizzoni, E., Kiseliovas, E., Malcovati, P., Maloberti, F., Peltola, T., & Teppo, T. (2008). A 4-output singleinductor DC-DC buck converter with self-boosted switch drivers and 1.2 A total output current. In IEEE ISSCC Digest of Technical Papers, pp. 444-626, February 2008.

- 7. Trevisan, D., Mattavelli, P., & Tenti, P. (2008). Digital control of single-inductor multiple-output step-down DC-DC converters in CCM. IEEE Transactions on Industrial Electronics, 55(9), 3476-3483.

- 8. Jing, X., Mok, P. K. T., & Lee, M. C. (2009). A wide-load-range single-inductor dual-output boost regulator with minimized crossregulation by constant-charge-auto-hopping (CCAH) control. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), pp. 299–302, September 2009.

- 9. TPS65120: Single-Inductor Quadruple-Output TFT LCD Power Supply. 2004, Texas Instruments Incorporated.

- 10. Le, H.-P., Chae, C.-S., Lee, K.-C., Wang, S.-W., Cho, G.-H., & Cho, G.-H. (2007). A single-inductor switching DC-DC converter with five outputs and ordered power-distributive control. IEEE Journal of Solid-State Circuits, 42(12), 2706-2714.

- 11. Chae, C.-S., Le, H.-P., Lee, K.-C., Cho, G.-H., & Cho, G.-H. (2009). A single-inductor step-up DC-DC switching converter with bipolar outputs for active matrix OLED mobile display panels. IEEE Journal of Solid-State Circuits, 44(2), 509-524.

- 12. Hoon, S. K. Culp, N. Chen, J., & Maloberti, F. (2005). A PWM dual-output DC/DC boost converter in a 0.13 µm CMOS technology for cellular-phone backlight application. In Proceedings of the European Solid-State Circuits Conference, pp. 81-84, September 2005.

- 13. Kwon, D., & Rincón-Mora, G. A. (2009). Single-inductor-multiple-output switching DC-DC converters. IEEE Transactions on Circuits and Systems—II: Express Briefs, 56(8), 614-618.

- 14. Li, T. (2000). Single inductor multiple output boost regulator. U.S. Patent 6075295, June 2000.

- 15. Ma, D., Ki, W. H., & Tsui, C. Y. (2003). A pseudo-CCM/DCM SIMO switching converter with freewheel switching. IEEE Journal of Solid-State Circuits, 38(6), 1007–1014.

- 16. Huang, M.-H., & Chen, K.-H. (2009). Single-inductor multioutput (SIMO) DC-DC converters with high light-load efficiency and minimized cross-regulation for portable devices. IEEE Journal of Solid-State Circuits, 44(4), 1099-1111.

- 17. Huang, M.-H., Tsai, Y.-N., & Chen, K.-H. (2010). Sub-1V singleinductor dual-output (SIDO) DC-DC converter with adaptive load-tracking control (ALTC) for single-cell-powered systems. IEEE Transactions on Power Electronics, 25, 1713-1724.

Bonizzoni, E., Borghetti, F., Malcovati, P., Maloberiti, F., & Niessen, B. A 200 mA 93% peak efficiency single-inductor dualoutput DC-DC buck converter. In *IEEE ISSCC Digest of Technical Papers*, pp. 526–527, February 2007.

Chia-Min Chen received the M.S. degree in electrical engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2006. He is currently working toward the Ph.D. degree at the Department of Electrical Engineering, National Chiao Tung University, Hsinchu, Taiwan. His research interests include mixed-signal integrated circuits, power management integrated circuits, and energy-efficient integrated circuits and systems.

Kai-Hsiu Hsu received the M.S. degree in electrical engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2010. In fall 2010, he joined Himax Inc., where he is currently designing mixed-signal ICs for power management. His research interests include DC–DC switching converters and mixed-signal integrated circuits.

Chung-Chih Hung received the B.S. degree in electrical engineering from National Taiwan University, Taipei, Taiwan, in 1989, and the M.S. and Ph.D. degrees in electrical engineering from The Ohio State University, Columbus, Ohio, in 1993 and 1997, respectively. From 1997 to 2003, he worked for several IC design companies in San Jose, CA and San Diego, CA, where he held analog circuit design manager and director positions. Since 2003, he has

been with National Chiao Tung University, Hsinchu, Taiwan, where he is currently an Associate Professor in the Department of Electrical Engineering. His research interests include the design of analog and mixed-signal integrated circuits for communication and high-speed applications.